# 行政院國家科學委員會專題研究計畫成果報告

- 2.4GHz CMOS 射頻前端電路設計(II)---2.4GHz 混波器

- 2.4GHz CMOS RF Front-end Circuits Design(II) ---

- 2.4GHz Mixer

計畫編號: NSC 89-2213-E-009-055 執行期限: 88年08月01日至89年07月31日 主持人: 高曜煌 交通大學電信研究所教授

電話: 5712121-54541 傳真: 5710116 E-mail: yhkao@cc.nctu.edu.tw

計劃撰寫者:林哲煜 電信碩士班研究生

## 一、中文摘要(及關鍵字)

在本篇論文中提出一個2.4GHz金氧半混波器,其架構為吉爾伯特乘法器,佈線及選擇偏壓點對於頻寬,動態範圍以及低電壓供應有決定性影響。模擬結果如下:輸入之射頻為2.4GHz,本地振盪頻率為2.3GHz時,中頻輸出為100MEG,轉換增益為-2.07dB,輸入三階截距點為+4.7dBm,輸入-1dB功率飽和點為-4.89dBm,以及雜訊指數為10.69dB,提供低電壓2V作為電源供應。

**關鍵字**:混波器,轉換增益,射頻,本機 振盪,中頻

#### **Abstract**

A differential mixer using CMOS technology is designed for 2.4 GHz wireless application. The architecture is Gilbert Cell. The layout and dc bias are specially designed to extend the frequency bandwidth, dynamic range, and low dc power supply. The goals are aimed at a conversion gain of -2.07 dB, a  $P_{-1dB}$  compression point referred to input of 4.7 dBm, a IIP3 of -4.89 dBm, and NF of 10.69 dB at RF:2.4 GHz, LO:2.3 GHz, and IF:100 MHz.

**Keyword:** mixer, conversion gain, RF, LO, IF.

## 二、計劃緣由與目的

金氧半製程由於具有低功率,高 密度,並且在基頻之技術已相當成熟, 故相當適合無線通訊應用上。近幾年 來,製程技術不斷進步,金氧半通道長 度已可以小至微米以下,使得金氧半 技術可以適用於射頻前端[1-3]。在 [4]中評估0.5微米金氧半製程中,N通 道之截止頻率可達20十億赫茲,自振 頻率則可達37十億赫茲,在本篇報告 中,將利用0.5微米金氧半製程技術來 設計混波器,工作條件為低電壓(2伏 特),高工作頻率(2.4十億赫茲),以及 高的動態範圍。混波器的特性可以由 下列參數定義:轉換增益,輸入一分貝 壓縮點,輸入三階截距點,雜訊指數, 本機振盪功率,以及直流功率消耗; 在 設計混波器時,這些參數都要加以折 衷。混波器對於前端電路之動態範圍 具有決定性[5],設計原則是,其雜訊 指數不超過前置放大電路的增益,一 般混波器的輸入三階截距點大約為-18毫瓦分貝[6]。金氧半通常具有較低 的交互調變及互調變,這是因為金氧 半汲極電流與閘極源極偏壓是呈二次 方關係,不過,值得注意的是雖然在更 小微米的場效電晶體中,電流跟偏壓 不在是二次方關係,但卻具有更高的 截止頻率及自振頻率。

由於吉爾伯特乘法器具有轉換增益,低本機振盪功率,低偏移電壓,固有的埠對埠隔絕以及良好的時脈壓抑等優點,在這裡我們採用吉爾伯特乘法器來設計混波器。針對動態範圍與低電壓考慮上,設計過程著重在選擇電晶體大小與偏壓點上。而在此我們會將重心擺在轉換增益上。目前為止,利用金氧半製程來設計達到2.4十億赫茲之混波器可以說是第一次嘗試,在1十億赫茲到2.2十億赫茲之間,但有達到2.4十億赫茲只有升頻轉換[5]。我們有信心絕對可以利用0.5微米金氧半製程來製作可達2.4十億赫茲之混波器。

## 三、研究方法

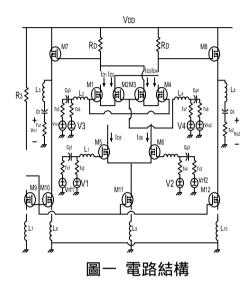

圖一為整個電路結構。在佈局中,可能的寄生都必須考慮清楚,所有的內部接線皆採用金屬層以避免寄生電阻,線寬則折衷於電流載量與寄生電容,線長必須越短越好以避免寄生電感,另外避免線與線交錯而過,電晶體採用"多指"結構,所有主動元件皆用 $\rho^+$ 那一層包起來,降低基板雜訊。

電路基本上分為三部分:中心部 分吉爾伯特乘法器,M1~M6,輸出緩衝 器,M7~M8,以及鏡電流源,M9~M12。 M1~M6大小為135微米/0.5微米,這個 大小的取決折衷於電路電流大小與寄 生電容。值得注意的是,在本電路中差 動放大級並未採用源極退化,採用源 極退化雖然可以增加一點線性度,但 卻會造成增益大量損失,進而嚴重影 響雜訊指數,因此,線性度與雜訊指數 之間有"斟酌"的關係。在此,轉換增益 與雜訊指數作最佳化。為了達到高頻. 所有電晶體全部採用N通道,中頻負載 RD則採用poly這層,以避免採用P通道 作負載所寄生的電容效應[3],射頻端 級本機振盪端皆經過10千歐姆電阻偏 壓。

核心部分,M1~M4,偏壓在臨界電 壓附近[5],如此一來,僅須要一個小 功率的本機振盪就能使電晶體工作有如開關一般;對於低電壓方面,只要保持 $V_{cs} > V_{gs} - V_{\tau}$ ,壓降可以被降低。電晶體 $M5\sim M6$ 偏壓在歐姆區以保持線性度,電感 $L1\sim L10$ 模擬打線的寄生,其中, $L1\sim 2$ 和 $L3\sim 4$ 可以用來做輸入阻抗匹配。

在此,[9]提供一些公式計算雜訊 指數,如下:

$$F = \sum_{1} \frac{\left\langle v_{out}^{2} \right\rangle}{kT_{0}G_{1}r_{cd}} + \sum_{2} \frac{\left\langle v_{out}^{2} \right\rangle}{kT_{0}r_{cd}} + 1$$

其中, $\sum_1$ 和 $\sum_2$ 分別表示來自電壓轉電流級與其他級的雜訊, $G_1$ 表示轉換增益, $V_{out}$ 表示由混波器自身所產生而傳送到中頻的輸出雜訊電壓。上式為單邊帶雜訊指數,忽略鏡頻(LO+IF)。我們可以利用Hspice來模擬輸出雜訊電壓,再利用上式估算雜訊指數。

## 四、成果

測試的方法是將晶片載在洗好的電路板子上,利用打線連接,而射頻,本機振盪及中頻都須要一個平衡-不平衡電路將單端訊號轉成差動訊號。 為了測試的目的,所有的埠都必須做好阻抗匹配,而方法是利用打線調整。

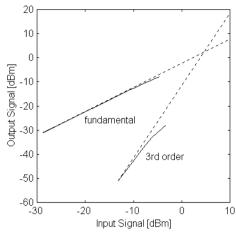

表一列出模擬與量測的結果,其中量測到的轉換增益為-2.3分貝,如圖二所示,中頻輸出為-32.1毫瓦分貝,當輸入的功率為-30毫瓦分貝;如圖三所示,輸入一分貝壓縮點P-1dB約為-5.1毫瓦分貝,而輸入三階截距點為4.5毫瓦分貝;雜訊指數為12.5分貝,所需本機振盪功率為-1.9毫瓦分貝,而總共所須的直流功率為34.6毫瓦,電壓供應2伏特。

#### 四、結論與討論

在本篇報告中,設計一個工作在2.4十億赫茲,以吉爾伯特乘法器為基

本架構的混波器,高頻的特性必須仔細考慮任何有可能的寄生效應,轉換增益最佳化則選擇電晶體的寬長財態範圍最佳化則選擇獨為2.3十億赫茲,本機振盪為2.3十億赫茲,中頻為100百萬赫茲;量別則則與為2.4十億赫茲,本機振盪為2.3十億的數學,與增益為-2.3分員,輸入一分員,所需本機振盪为員,而指數是別數學。表一所示模擬和量別數學。表一所示模擬和量別數學。表一所示模擬和量別數學。表一所示模擬和量別數學。表一所示模擬和量別數學。表一所示模擬和量別數學。

#### **REFERENCES**

- [1] Paul Davis et al., "Wireless Transceivers and Receivers," *ISSCC* 97/Session 18/February 8, 1997/Salon 7, pp. 299-311.

- [2] J. Sevenhans et al., "An Analog Radio Front-end Chip Set for a 1.9GHz Mobile Radio Telephone Application," ISSCC 94/Session 2/Wireless Communications/Paper WP 2.8, pp. 44-45.

- [3] A. Rofougaran et al., "A 1 GHz CMOS Front-End IC for a Direct-Conversion Wireless Receiver," *IEEE Journal of Solid-State Circuits,* vol. 31, no. 7, pp. 880-889, July 1996.

- [4] P. Voinigescu et al.," An Asseaament of the State-of-theArt 0.5um Bulk CMOS Technology for RF Applications," *IEEE IEDMC Dig.Tech. Paper*, pp. 712-724 Dec. 1995.

- [5] P. J. Sullivan et al.," Low Voltage Performance of a Microwave CMOS Gilbert Cell Mixer," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 7, JULY 1997.

- [6] J. Fenk," RF-heterodyne receiver design technique for digital cellular wireless systems," in Workshop on Low-Power Low-Voltage and RF IC for Wireless Communication Systems, Switzerland, 1995.

- [7] P. J. Sullivan et al.," Active Doubly Balanced Mixers for CMOS RFICs," *Microwave Journal*, pp. 22-38, October 1997.

- [8] Shuo-Yuan Hsiao, Chung-Yu Wu," A Parallel Structure for CMOS Four-Quadrant Analog Multipliers and Its

- Application to a 2-GHz RF Downconversion Mixer," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 6, JUNE 1998.

- [9] Rick Poore," Accurate Simulation of Mixer Noise and Oscillator Phase Noise in Large RFICs," Hewlett-Packard Company, Advanced Techniques for Communication Signal Path Design, October, 1997.

REF -10.0 dBm ATT 10 dB A\_write B\_blank 10dB/

MARKER 100.009 MHz -32.09 dBm

RBW 100 kHz VBW 30 kHz

圖二 中頻頻譜當輸入為-30毫瓦分貝

圖三 量測到的輸入功率與輸出功率之轉換函數

Down-Converter Performance at RF=2.4 GHz, IF=100MHz

| Parameter               | Simulated | Measured |

|-------------------------|-----------|----------|

| Supply Voltage          | 2 V       | 2V       |

| LO Power (2.3 GHz)      | -1.9 dBm  | -1.9 dBm |

| SSB NF (50 $\Omega$ )   | 10.69 dB  | 12.5 dB  |

| Conversion Gain         | -2.07 dB  | -2.3 dB  |

| Input IP3               | +4.7 dBm  | +4.5 dBm |

| Input -1 dB Compression | -4.89 dBm | -5.1 dBm |

| Current used in Mixer   | 3.1 mA    | 3.2 mA   |

| Current used in Buffer  | 13.6 mA   | 14.1 mA  |

| Output Bandwidth        | 170 MHz   | 155 MHz  |

表一混波器模擬和量測結果