# Effect of Fin Angle on Electrical Characteristics of Nanoscale Round-Top-Gate Bulk FinFETs

Yiming Li, Member, IEEE, and Chih-Hong Hwang

Abstract—In this brief, electrical characteristics of 25-nm round-top-gate fin-typed field-effect transistors (FinFETs) on silicon wafers are numerically explored. With an ideal fin angle (i.e.,  $\theta=90^\circ$ ), the FinFETs with doped and undoped (for this case, the device has a metal gate) channels that was fabricated on silicon and silicon-on-insulator wafers are simulated and compared. With a 3-D quantum-correction-transport simulation, characteristic comparison shows that bulk FinFETs with the undoped channel possess promising electrical characteristics. By considering different short-channel effects, dependence of the device performance on the nonideal fin angle and fin height is further investigated. Optimal structure configuration for the round-top-gate bulk FinFETs is thus drawn to show the strategy of fabrication in sub-25-nm MOSFET devices.

Index Terms—Bulk fin-typed field-effect transistors (FinFETs), fin angle, manufacturability, metal gate, modeling and simulation, round-top gate.

# I. INTRODUCTION

FIELD-EFFECT transistors (FETs) with multiple-gate structures such as fin two EET. structures, such as fin-type FETs (FinFETs) [1]-[8], have been of great interest for potential sub-32-nm technology application. Excellent controlling ability of carriers in the device's channel is observed on FinFETs, where the short-channel effects (SCEs) are suppressed. Channel doping for adjusting the threshold voltage is still necessary in nowadays manufacturing process. However, heavily doped channel leads to some drawbacks, such as mobility degradation induced by impurity scattering and unexpected dispersion in electrical characteristics. It becomes worse when the feature size of sub-65-nm MOSFETs is continuously scaled. On the other hand, multiplegate MOSFETs with undoped channel have been extensively studied. At the same time, instead of polysilicon gate, a metal gate is alternatively chosen to substitute in obtaining the proper threshold voltage. The device performance is thus improved by eliminating polysilicon depletion and reducing the gate leakage [6]. In fabricating the nanoscale FinFETs, the minimum

Manuscript received August 14, 2007. This work was supported in part by the Taiwan National Science Council (NSC) under Contracts NSC-96-2221-E-009-210 and NSC-96-2752-E-009-003-PAE, by the MoE ATU Program under a 2006–2007 Grant, and by the Taiwan Semiconductor Manufacturing Company, Ltd. (TSMC) under a 2004–2008 Grant. The review of this brief was arranged by Editor M. J. Kumar.

The authors are with the Department of Communication Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymli@faculty.nctu.edu.tw; ymli@mail.nctu.edu.tw).

Color versions of one or more of the figures in this brief are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2007.908908

dimension of the device has transferred from the gate length to the fin thickness. Top of the fin is formed to a round shape naturally [2], [3], [7], and the fin bottom is not actually rectangular for the lithography and silicon-etching processes. These nonideal processes will result in a wider fin bottom with respect to the fin top; thus, it leads to a slanted edge of the channel fin [2], [3], [7], [8]. Such geometric derivation degrades device performance and raises serious SCEs, such as a large subthreshold swing (SS), low ratio of the ON- and OFF-state currents, and large drain-induced barrier lowering (DIBL). Many studies concerning design guideline and consideration and simulation have been reported for studying multiple-gate devices [9]–[16]. However, effects of geometry aspect ratio of the silicon fin and its fin angle on electrical characteristics for scaled bulk FinFETs have not been clearly explored yet.

In this brief, we numerically explore electrical characteristics of the doped and undoped channel for round-top-gate FinFETs on the silicon and silicon-on-insulator (SOI) wafers. A 3-D device simulation with solving a set of density-gradientbased drift-diffusion equations is adopted and performed to account for quantum-mechanical effects (see, for instance, [5] and references therein). For a device with an ideal fin angle (i.e.,  $\theta = 90^{\circ}$ ), we examine electrical characteristics for 25-nm FinFETs with doped and undoped channels on the silicon and SOI wafers. Among the devices, the bulk FinFETs with an undoped channel exhibit good performance. Particularly, dependence of the round-top undoped bulk FinFETs' performance on nonideal fin angle and the fin height is further investigated, which is subject to different SCEs. By varying the fin angle, in 3-D device simulation, an optimal configuration of structure for the explored round-top-gate bulk FinFETs is drawn, according to manufacturability.

This brief is organized as follows. In Section II, we report and discuss the simulation results. Finally, we draw conclusions.

# II. SIMULATION RESULTS AND DISCUSSION

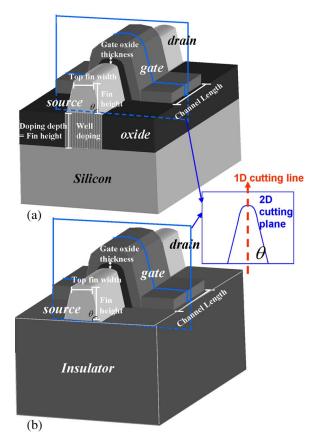

Electrical characteristics of a 25-nm FinFET with the silicon and SOI substrates, as shown in Fig. 1, are examined first, where the oxide thickness, the fin width, and the fin height are fixed at 1.2, 20, and 50 nm, respectively. The physical settings and simulation results are summarized in Table I. We notice that the parameters are adjusted so that the four explored devices have very similar threshold voltage, and the examination is simply assumed that the simulated devices are with a flat-top gate, where the ideal fin angle of 90° is fixed.

Fig. 1. Three-dimensional schematic plots for the (a) bulk and (b) SOI FinFETs. The symbol  $\theta$  is the fin angle, and the inset shows a 2-D cutting-plane extracting from the center of the channel.

We observe that the metal-gate device (for this case, the device is with an undoped channel) on silicon bulk wafer exhibits better performance than others with and without heavily doped channel on different wafers. For the round-top-gate FinFETs to be explored as follows, we have performed the same investigation and obtained similar tendency. We further investigate the effect of fin angle on the electrical characteristics for the 25-nm round-top-gate bulk FinFET with the undoped channel, where the work function is 4.45 eV. Different angle of the fin taper is examined subject to the aforementioned electrical characteristics of the device.

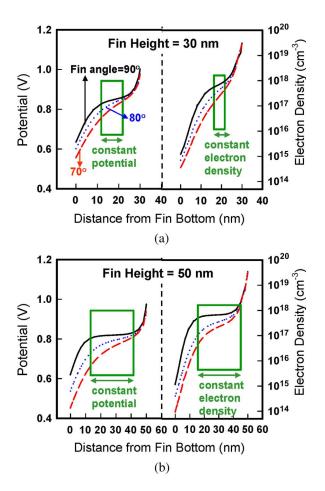

For the drain voltage of 1.0 V and the gate voltage of 1.0 V, the distributions of potential and electron density for the device with the fin height = 30 nm [Fig. 2(a)] and 50 nm [Fig. 2(b)] are extracted according to the 1-D cutting line, as shown in the inset of Fig. 1. The plots are devices with three different angles of fin taper as follows: 70°, 80°, and 90°. Nonuniform distributions of the potential and electron density along the longitudinal direction are observed. We notice that all plots of 1-D cutting lines start near the interface of silicon and silicon dioxide. This is a direct result of a donor's and the bias' impacts on the channel along the direction of the fin top to bottom. The potential attains the minimum value at the fin bottom, which increases rapidly toward the fin top. For the same distance, the larger potential associated with the larger fin taper angle is perceived from the fin bottom. The electron density is reduced when the distance (from the top fin) is broadened; similarly, it

#### TABLE I

PHYSICAL PARAMETERS USED IN THE DEVICE SIMULATION AND THE RESULTS WITH DOPED AND UNDOPED CHANNELS ON SILICON AND SOI WAFERS. THE BULK METAL MEANS THAT THE DEVICE WITH UNDOPED CHANNEL ON SILICON WAFER. THE BULK POLY-SI IS THE DEVICE WITH DOPED CHANNEL ON SILICON WAFER. FOR SOI METAL AND SOI POLY-SI, WE SIMILARLY INDICATE THAT THE DEVICES ARE FABRICATED ON THE SOI WAFER. WE NOTICE THAT THE SLIGHTLY DIFFERENT VALUES OF THE PARAMETERS HAVE BEEN ADOPTED, WHICH ARE MAINLY FOR ADJUSTING VERY SIMILAR THRESHOLD VOLTAGE AMONG DEVICES

|                                           | Bulk                          | Bulk                          | SOI Metal                     | SOI Poly-                     |

|-------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

|                                           | Metal                         | Poly-Si                       |                               | Si                            |

| Gate workfunction (eV)                    | 4.45                          | 4.17                          | 4.505                         | 4.17                          |

| Well doping (cm <sup>-3</sup> )           | 10 <sup>18</sup>              | 10 <sup>18</sup>              | 0                             | 0                             |

| Source / Drain doping (cm <sup>-3</sup> ) | 10 <sup>20</sup>              | 10 <sup>20</sup>              | 10 <sup>20</sup>              | 10 <sup>20</sup>              |

| Channel doping (cm <sup>-3</sup> )        | 10 <sup>16</sup>              | 4.68x10 <sup>18</sup>         | 10 <sup>16</sup>              | 4.6x10 <sup>18</sup>          |

| Background doping (cm <sup>-3</sup> )     | 1x10 <sup>15</sup>            | 1x10 <sup>15</sup>            | 1x10 <sup>15</sup>            | 1x10 <sup>15</sup>            |

| DIBL (mV)                                 | 37                            | 82                            | 56                            | 66                            |

| SS (mA / mV)                              | 71.83                         | 81.48                         | 76.75                         | 78.3                          |

| Ion / Ioff                                | 3.08 <b>x</b> 10 <sup>7</sup> | 3.35 <b>x</b> 10 <sup>6</sup> | 5.06 <b>x</b> 10 <sup>7</sup> | 6.82 <b>x</b> 10 <sup>6</sup> |

has the minimum value at the fin bottom. For the device with the fin height = 30 nm, as shown in the left plot of Fig. 2(a), we find that the case of 90° (i.e., the solid lines) exhibits the most uniform distribution of the potential in the center of the channel. The potential decreases more quickly with a more slanted fin angle, which leads to a stronger longitudinal electric field and may degrade the device performance. Similar results can be observed for the cases with a fin height of 50 nm. Moreover, it is found that the variation of potential almost keeps constant within the longest distance inside the channel region. The potential variation is significant when the fin angle is decreased, and the case of  $70^{\circ}$  (the dashed lines) possesses the largest potential variation among the three angles. The variation is even more appreciable when the fin height is increased. For the different fin angles and fin heights, the right plots of Fig. 2(a) and (b) disclose the variation of the electron density versus the distance from the fin bottom. The variation of this physical quantity predicts the same trend as depicted earlier. It is found that the device with an approximately ideal fin angle (i.e., the fin angle approaches to 90°) has the most uniform distribution of the examined physical quantities within the device channel.

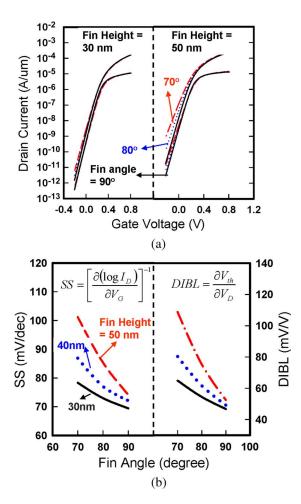

Plots of the drain-current versus the gate voltage for the three fin angles and two fin heights are shown in Fig. 3(a). The case for the fin height of 30 nm, as shown in the left plot of Fig. 3(a), allows a larger variation of the fin angle, compared with the result of the fin height = 50 nm. It means that the fin height of 30 nm maintains the highest ratio of the ON- and OFF-state currents and implies better performance. The parameters of SCE versus the fin angle are calculated accordingly, as shown in Fig. 3(b). We notice that a larger taper angle is necessary for fabrication of nanoscale bulk FinFETs

Fig. 2. Plots of 1-D cutting lines of the potential and electron density at the center of the channel. The device is with the fin height of (a) 30 and (b) 50 nm, where the solid line is the result for the  $90^{\circ}$ , the dotted line is for the  $80^{\circ}$ , and the dashed line is for the  $70^{\circ}$ . The circled windows indicate the regimes where nearly constant potential and electron density occurred in the device channel.

to obtain robust electrical characteristics. Besides, Fig. 3(b) implies that a smaller fin height is essential for the device of 25-nm gate length. The calculated SS suggests that an increase of the fin angle will result in better SS; in particular, for those silicon fins with higher fin height, which improve the SCE remarkably. Similarly, we also find the evidence for the DIBL. Consequently, for the cases with a small fin angle, the device may not have an acceptable performance. In addition, for the bulk FinFET with a high fin height, the situation is getting worse simultaneously. For this reason, we summarize that the fin height and the fin angle are the two critical limiting factors when the dimension of the bulk FinFET is continuously scaled down. In a word, they are the most important parameters that have to be optimized according to the fabrication point of view. A structure of bulk FinFET with a nearly rectangular configuration leads to better electrical characteristics. If the ratio between the fin height and the top-fin width (i.e., the fin height/the top-fin width) is greater than one, then the fin taper angle improves the device characteristics significantly. Therefore, for the device with a large ratio between the fin height and the top-fin width, the controllability of manufacturing the fin taper angle is exceptionally important, and much more effort on processing should be made.

Fig. 3. (a) Characteristics of the drain–current versus the gate voltage for the device with respect to different fin angles and heights. The solid lines are the result for the  $90^{\circ}$ , the dotted lines are for the  $80^{\circ}$ , and the dashed lines are for the  $70^{\circ}$ . (b) Results of (the left plot) SS and (the right one) DIBL versus the fin angle, where the solid lines are the result for the 30 nm, the dotted lines are for the 40 nm, and the dashed lines are for the 50 nm.

## III. CONCLUSION

In this brief, electrical characteristics of nanoscale bulk Fin-FET have been numerically studied by using a 3-D densitygradient drift-diffusion simulation. For the studied 25-nm bulk FinFET, the ON-state current, the SS, the DIBL, the distribution of electrostatic potential, and the distribution of electron density have been calculated with respect to different fin taper angles. The SCEs are degraded due to slant of the sideward wall of silicon fin. Nonrectangular structure of fin leads to current crowding and deteriorates the performance of a device. Consequently, we can conclude that fin height and the fin angle of a device are the two most important parameters in optimizing the fabrication processes. A nearly rectangular-shaped fin is only crucial for the device with a higher fin height. The critical angles for the case of SS < 75 mV/dec and DIBL < 75 mV/V are summarized in Table II. We can find the critical angles when fin height/top-fin width = 1.5, 2, and 2.5, and the critical angles are 71.9°, 79.3°, and 87°, respectively. Therefore, with a larger fin height/top-fin width, the critical angle becomes larger and approaches 90° (the most severe limitation), which means that an ideal rectangular shape of fin is necessary for good electrical characteristics.

TABLE II

LIST OF THE SUGGESTED DESIGNING PARAMETERS FOR

FABRICATION OF NANOSCALE BULK FINFETS

| Fin height (nm)            | 30   | 40   | 50   |

|----------------------------|------|------|------|

| Fin height / Top fin width | 1.5  | 2.0  | 2.5  |

| Critical angle (degree)    | 71.9 | 79.3 | 87.4 |

## ACKNOWLEDGMENT

The authors would like to thank J.-R. Hwang and F.-L. Yang of the Taiwan Semiconductor Manufacturing Company for supplying devices and helpful discussions. They would also like to thank the reviewers for providing constructive comments, which were very helpful in revising this brief.

#### REFERENCES

- [1] J. A. Choi, K. Lee, Y. S. Jin, Y. J. Lee, S. Y. Lee, G. U. Lee, S. H. Lee, M. C. Sun, D. C. Kim, Y. M. Lee, S. G. Bae, J. H. Yang, S. Maeda, N. I. Lee, H. K. Kang, and K. P. Suh, "Large scale integration and reliability consideration of triple gate transistors," in *IEDM Tech. Dig.*, Dec. 13–15, 2004, pp. 647–650.

- [2] T. Park, S. Choi, D. H. Lee, J. R. Yoo, B. C. Lee, J. Y. Kim, C. G. Lee, K. K. Chi, S. H. Hong, S. J. Hynn, Y. G. Shin, J. N. Han, I. S. Park, U. I. Chung, J. T. Moon, E. Yoon, and J. H. Lee, "Fabrication of body-tied FinFETs (Omega MOSFETs) using bulk Si wafers," in VLSI Tech. Symp. Dig., 2003, pp. 135–136.

- [3] H. Lee, L.-E. Yu, S.-W. Ryu, J.-W. Han, K. Jeon, D.-Y. Jang, K.-H. Kim, J. Lee, J.-H. Kim, S.-C. Jeon, G. S. Lee, J. S. Oh, Y. C. Park, W. H. Bae, H. M. Lee, J. M. Yang, J. J. Yoo, and Y.-K. Choi, "Sub-5 nm all-around gate FinFET for ultimate scaling," in VLSI Tech. Symp. Dig., 2006, pp. 58–59.

- [4] F. L. Yang, D. H. Lee, H. Y. Chen, C. Y. Chang, S. D. Liu, C. C. Huang, T. X. Chung, H. W. Chen, C. C. Huang, Y. H. Liu, C. C. Wu, C. C. Chen, S. C. Chen, Y. T. Chen, Y. H. Chen, C. J. Chen, B. W. Chan, P. F. Hsu, J. H. Shieh, H. J. Tao, Y. C. Yeo, Y. Li, J. W. Lee, P. Chen, M. S. Liang, and C. Hu, "5 nm-gate nanowire FinFET," in VLSI Tech. Symp. Dig., 2004, pp. 196–197.

- [5] Y. Li, H.-M. Chou, and J.-W. Lee, "Investigation of electrical characteristics on surrounding-gate and omega-shaped-gate nanowire FinFETs," *IEEE Trans. Nanotechnol.*, vol. 4, no. 5, pp. 510–516, Sep. 2005.

- IEEE Trans. Nanotechnol., vol. 4, no. 5, pp. 510–516, Sep. 2005.

[6] J. Kedzierski, M. Ieong, T. Kanarsky, Y. Zhang, and H.-S. P. Wong, "Fabrication of metal gated FinFETs through complete gate silicidation with Ni," IEEE Trans. Electron Devices, vol. 51, no. 12, pp. 2115–2120, Dec. 2004.

- [7] X. Wu, P. C. H. Chan, and M. Chan, "Impacts of nonrectangular fin cross section on the electrical characteristics of FinFET," *IEEE Trans. Electron Devices*, vol. 52, no. 1, pp. 63–68, Jan. 2005.

- [8] T.-H. Hsu, H.-Y. Lue, Y.-C. King, J.-Y. Hsieh, E.-K. Lai, K.-Y. Hsieh, R. Liu, and C.-Y. Lu, "A high-performance body-tied FinFET bandgap engineered SONOS (BE-SONOS) for NAND-type flash memory," *IEEE Trans. Electron Devices*, vol. 28, no. 5, pp. 443–445, May 2005.

- [9] H.-J. L. Gossmann, A. Agarwal, T. Parrill, L. M. Rubin, and J. M. Poate, "On the FinFET extension implant energy," *IEEE Trans. Nanotechnol.*, vol. 2, no. 4, pp. 285–290, Dec. 2003.

- [10] Y.-X. Liu, K. Ishii, T. Tsutumi, M. Masahara, T. Sekigawa, K. Sakamoto, H. Takashima, and E. Suzuki, "Electrical property to ideal rectangular Si-fin channel double-gate MOSFETs," in *Proc. Abstract Silicon Nanoelectronics Workshop*, 2003, pp. 64–65.

- [11] S.-I. Chang, J. Lee, and H. Shin, "A tri-gate MOSFET with gate-to-source/drain non-overlapped structure," in *Proc. Abstract Silicon Nanoelectronics Workshop*, 2003, pp. 32–33.

- [12] J. Kavalieros, B. Doyle, S. Datta, G. Dewey, M. Doczy, B. Jin, D. Lionberger, M. Metz, W. Rachmady, M. Radosavljevic, U. Shah, N. Zelick, and R. Chau, "Tri-gate transistor architecture with high-κ gate dielectrics, metal gates and strain engineering," in VLSI Tech. Symp. Dig., 2006, pp. 50–51.

- [13] A. Kranti and G. A. Armstrong, "Device design considerations for nanoscale double and triple gate FinFETs," in *Proc. IEEE SOI Conf.*, Oct. 3–6, 2005, pp. 96–98.

- [14] H. J. Cho, J. D. Choe, M. Li, J. Y. Kim, S. H. Chung, C. W. Oh, E.-J. Yoon, D.-W. Kim, D. Park, and K. Kim, "Fin width scaling criteria of body-tied FinFET in sub-50 nm regime," in *Proc. Device Res. Conf.*, Jun. 21–23, 2004, vol. 1, pp. 209–210.

- [15] E. Gnani, S. Reggiani, M. Rudan, and G. Baccarani, "A quantum-mechanical analysis of the electrostatics in multiple-gate FETs," in *Proc. SISPAD*, Sep. 2005, pp. 291–294.

- [16] M. Kondo, R. Katsumata, A. Hideaki, T. Hamamoto, S. Ito, N. Aoki, and T. Wada, "A FinFET design based on three-dimensional process and device simulations," in *Proc. SISPAD*, Sep. 2005, pp. 179–182.

Yiming Li (M'02) received the B.S. degrees in applied mathematics and electronics engineering, the M.S. degree in applied mathematics, and the Ph.D. degree in electronics from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, R.O.C., in 1996, 1998, and 2001, respectively.

In 2001, he was with the National Nano Device Laboratories (NDL), Hsinchu, as an Associate Researcher, and with the Microelectronics and Information Systems Research Center (MISRC), NCTU, as an Assistant Professor, where was engaged in

the field of computational science and engineering, particularly in modeling, simulation, and optimization of nanoelectronics and very large scale integration (VLSI) circuits. In the fall of 2002, he was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst. From 2003 to 2004, he was the Research Consultant of the System on a Chip (SOC) Technology Center, Industrial Technology Research Institute, Hsinchu. From 2003 to 2005, he was the Director of the Departments of Nanodevice and Computational Nanoelectronics, NDL. From 2004 to 2005, he was an Associate Professor with the MISRC, NCTU. Since the fall of 2005, he has been an Associate Professor with the Department of Communication Engineering, NCTU. He is also currently the Deputy Director of the Modeling and Simulation Center, NCTU, and also currently conducts the Parallel and Scientific Computing Laboratory, NCTU. His current research areas include computational electronics and physics, physics of semiconductor nanostructures, device modeling, parameter extraction, VLSI circuit simulation, development of technology computer-aided design (TCAD) and electronic CAD (ECAD) tools and SOC applications, bioinformatics and computational biology, advanced numerical methods, parallel and scientific computing, optimization techniques, and computational intelligence. He has authored or coauthored over 120 research papers appearing in international book chapters, journals, and conferences. He has served as a Reviewer, Guest Associate Editor, Guest Editor, Associate Editor, and Editor for many international journals. He has organized and served on several international conferences and was an Editor for proceedings of international conferences.

Dr. Li is a member of Phi Tau Phi, Sigma Xi, American Physical Society, American Chemical Society, Association for Computing Machinery, Institute of Electronics, Information and Communication Engineers of Japan, and Society for Industrial and Applied Mathematics, and is included in Who's Who in the World. He has served as a Reviewer for the IEEE Transactions on Nanotechnology, the IEEE Transactions on Microwave Theory and Techniques, the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, the IEEE Electron Device Letters, and the IEEE Transactions on Electron Devices. He was the recipient of the 2002 Research Fellowship Award presented by the Pan Wen-Yuan Foundation, Taiwan and the 2006 Outstanding Young Electrical Engineer Award from the Chinese Institute of Electrical Engineering, Taiwan.

Chih-Hong Hwang received the B.S. degrees from the Department of Engineering and System Science and the Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan, R.O.C., in 2001 and 2003, respectively. He is currently working toward the Ph.D. degree in the Department of Communication Engineering of National Chiao Tung University, Hsinchu.

His research interests focus on modeling and simulation of semiconductor nanodevices and intrinsic parameter fluctuations in ultrasmall nano-CMOS devices.