# HfLaON n-MOSFETs Using a Low Work Function $HfSi_x$ Gate

C. F. Cheng, C. H. Wu, N. C. Su, S. J. Wang, S. P. McAlister, *Senior Member*, and Albert Chin, *Senior Member*

Abstract—At a 1.2-nm equivalent oxide thickness,  $HfSi_x/Hf_{0.7}La_{0.3}ON$  n-MOSFETs showed an effective work function of 4.33 eV, a low threshold voltage of 0.18 V, and a peak electron mobility of 215 cm<sup>2</sup>/(V · s). These self-aligned and gate-first  $HfSi_x/Hf_{0.7}La_{0.3}ON$  n-MOSFETs were processed using standard ion implantation and 1000-°C rapid thermal annealing, making them fully compatible with current very large scale integration fabrication lines.

Index Terms—HfLaON, HfSi, n-MOSFETs.

## I. INTRODUCTION

**M** ETAL GATES and high- $\kappa$  gate dielectrics are necessary for complementary MOSFETs at the 45-nm nodes and beyond [1]-[15] to reduce the dc power consumption from the gate current and continue the very large scale integration (VLSI) scaling. This poses a difficult technological challenge in that the large threshold voltage  $V_t$  that results from Fermilevel pinning is opposite to the trend needed for device scaling. To avoid this, it requires appropriate choices of the metal-gate work function and high- $\kappa$  dielectric—to reduce the pinning to achieve the required low  $V_t$ . Previously, we have shown that Fermi-level pinning can be reduced, even after surface plasma nitridation, by adding  $La_2O_3$  to HfO<sub>2</sub> to produce the gate dielectric Hf<sub>0.5</sub>La<sub>0.5</sub>ON at 1.6-nm equivalent oxide thickness (EOT). Thus, a relatively low  $V_t$  can be achieved with a conventional TaN gate [15]. Here, we report the use of a low work function fully silicided (FUSI)  $HfSi_x$  gate for  $Hf_{0.7}La_{0.3}ON$ n-MOSFETs at a scaled EOT of 1.2 nm and reduced La composition of 30%. This gate yields a more negative flatband voltage  $V_{\rm fb}$  than does a TaN gate. The resulting MOSFETs show a  $V_t$  of 0.18 V, a low leakage current of  $9.2 \times 10^{-4}$  A/cm<sup>2</sup> at 1 V above  $V_{\rm fb}$ , and 1.2-nm EOT, with an electron mobility of 215 cm<sup>2</sup>/(V  $\cdot$  s). These devices can endure a rapid thermal annealing (RTA) temperature of 1000 °C, which is common in current poly-Si gate technology.

Manuscript received July 24, 2007; revised August 28, 2007. This work was supported in part by National Science Council 95-2221-E-009-275 and Technology Development Program for Academia, Department of Industrial Technology, Ministry of Economic Affairs 94-EC-17-A-01-S1-047 of Taiwan. The review of this letter was arranged by Editor B. Yu.

C. F. Cheng and A. Chin are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: albert\_achin@hotmail.com).

C. H. Wu, N. C. Su, and S. J. Wang are with the Institute of Microelectronics, Department of Electrical Engineering, National Cheng Kung University, Tainan 701, Taiwan, R.O.C.

S. P. McAlister is with the National Research Council of Canada, Ottawa, ON K1A 0R6, Canada.

Digital Object Identifier 10.1109/LED.2007.909843

### **II. EXPERIMENTAL PROCEDURE**

We used the 4-in p-type Si wafers in these experiments. After a standard RCA clean, the Hf<sub>0.7</sub>La<sub>0.3</sub>O was deposited on Si wafers by physical vapor deposition (PVD). Then, the Hf<sub>0.7</sub>La<sub>0.3</sub>O surface was exposed to a nitrogen plasma to form the Hf<sub>0.7</sub>La<sub>0.3</sub>ON gate dielectric. Amorphous Si of 5-nm thickness was deposited on Hf<sub>0.7</sub>La<sub>0.3</sub>ON followed by a PVD of 20-nm-thick Hf. To prevent Hf oxidation, a 30-nm-thick Mo was subsequently deposited above the Hf/Si/Hf<sub>0.7</sub>La<sub>0.3</sub>ON to form n-MOS capacitors. For n-MOSFETs, an additional 150-nm-thick amorphous Si was deposited to avoid ion implantation damage through the gate. The n<sup>+</sup> source-drain regions were formed by using a 35-keV phosphorus ion implantation (at a  $5 \times 10^{15}$  cm<sup>-2</sup> dose) followed by RTA activation at 1000 °C for 5 s. (Note that the FUSI HfSi<sub>x</sub> gate was formed at a high RTA temperature, similar to Ir<sub>3</sub>Si [14], which is different from a conventional low-temperature salicide process.) For comparison, TaN gates were also deposited on Hf<sub>0.7</sub>La<sub>0.3</sub>ON to form the n-MOS capacitors. The fabricated devices were characterized by C-V and I-V measurements using an HP4284A precision inductance-capacitance-resistance meter and HP4156 semiconductor parameter analyzer, respectively.

## **III. RESULTS AND DISCUSSION**

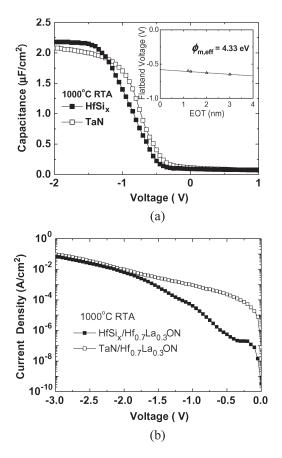

In Fig. 1(a) and (b), we show the C-V and J-V characteristics of HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON and control TaN/Hf<sub>0.7</sub>La<sub>0.3</sub>ON capacitors, respectively. For comparison, the characteristics of a capacitor with a TaN gate on Hf<sub>0.7</sub>La<sub>0.3</sub>ON are included. The FUSI HfSix gate without poly-Si depletion-as formed by Hf deposition on thin 5-nm amorphous Si at 1000-°C RTA-produces devices with a high capacitance density close to those using a TaN gate. However, the  $V_{\rm fb}$  of the  $HfSi_x$  gate is more negative than for the TaN gate, which is needed for low  $V_t$  operation. An EOT of 1.2 nm was found using a quantum-mechanical C-V simulation. A low  $\phi_{m\text{-eff}}$  of 4.33 eV was obtained from a  $V_{\text{fb}}$ -EOT plot for the  $HfSi_x/Hf_{0.7}La_{0.3}ON$  devices, making them suitable for n-MOS applications. The leakage current of  $9.2 \times 10^{-4}$  A/cm<sup>2</sup> (at 1 V beyond  $V_{\rm fb}$ ) is about five orders-of-magnitude lower than that of SiO<sub>2</sub> at a 1.2-nm EOT. This low leakage current is due to the high- $\kappa$  Hf<sub>0.7</sub>La<sub>0.3</sub>ON, highlighting the good thermal stability of the HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON gate structure after a 1000-°C RTA. The higher leakage current at low voltages using TaN gate than that of  $HfSi_x$  may be due to the sputter-induced damage to the Hf<sub>0.7</sub>La<sub>0.3</sub>ON gate dielectric. Thus, low  $\phi_{m-\text{eff}}$

Fig. 1. (a) C-V and (b) J-V characteristics of the HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON *n*-MOS capacitors, after a 1000-°C RTA. The inserted figure is a  $V_{\rm fb}$ -EOT plot.

and low gate dielectric leakage current can be achieved in  $HfSi_x/Hf_{0.7}La_{0.3}ON$  MOS capacitors.

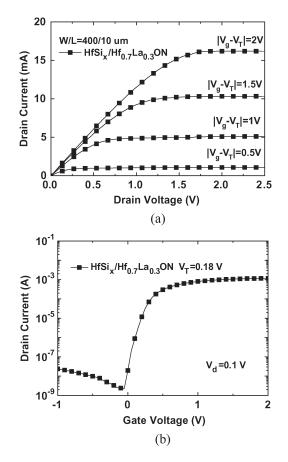

Fig. 2(a) and (b) shows the  $I_d-V_d$  and  $I_d-V_g$  transistor characteristics of the 1.2-nm EOT HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON n-MOSFETs. A small  $V_t$  of only 0.18 V was measured from the linear  $I_d-V_g$  plot—this is due to the low  $\phi_{m-\text{eff}}$  of 4.33 eV found from the C-V measurements.

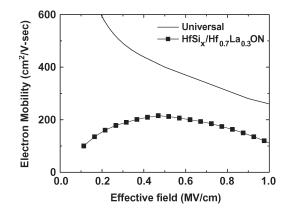

The electron mobility as a function of effective electric field for the HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON n-MOSFETs is shown in Fig. 3, where the data were derived from measured  $I_d-V_g$  curves. High peak electron mobility of 215 cm<sup>2</sup>/(V · s) is obtained at a small EOT of 1.2 nm. In Table I, we summarize and compare the important transistor characteristics for various metal-gate/ high- $\kappa$  n-MOSFETs. The merits of the HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON n-MOSFETs are the small EOT of 1.2 nm, a low  $V_t$  of 0.18 V, a good peak mobility of 215 cm<sup>2</sup>/(V · s), and simple hightemperature FUSI processing.

## **IV. CONCLUSION**

We have found good performance in terms of  $V_t$  and mobility for Hf<sub>0.7</sub>La<sub>0.3</sub>ON n-MOSFETs at 1.2-nm EOT using a low work-function and high-temperature-stable HfSi<sub>x</sub> gate. The self-aligned and gate-first HfSi<sub>x</sub>/HfLaON n-MOSFETs have the advantages of simple high-temperature FUSI processing and compatibility with current VLSI lines.

Fig. 2. (a)  $I_d-V_d$  and (b)  $I_d-V_g$  characteristics of the HfSi<sub>x</sub>/Hf<sub>0.7</sub>La<sub>0.3</sub>ON n-MOSFETs.

Fig. 3. Electron mobility versus effective electric field for the  $HfSi_x/Hf_{0.7}La_{0.3}ON$  n-MOSFETs.

TABLE I

COMPARISON OF DEVICE PARAMETERS FOR METAL-GATE/HIGH- $\kappa$

N-MOSFETS

| High-κ      | Metal Gate         | EOT (nm) | $V_t(\mathbf{V})$ | Process Temp.  |

|-------------|--------------------|----------|-------------------|----------------|

| HfLaON      | HfSix              | 1.2      | 0.18              | 1000°C         |

| This work   |                    |          |                   |                |

| HfLaON [15] | TaN                | 1.6      | 0.18              | 1000°C         |

| HfAlON [11] | Yb <sub>x</sub> Si | 1.7      | 0.1               | Low Temp. FUSI |

| HfTaO [10]  | TaN                | 1.6      | -                 | 1000°C         |

| HfSiON [13] | TaC                | 1.2      | ~0.4              | 1000°C         |

| HfSiON [12] | NiSi               | 1.5      | 0.5               | Low Temp. FUSI |

| HfSiON [9]  | NiSi <sub>2</sub>  | 1.7      | 0.47              | Low Temp. FUSI |

#### REFERENCES

- [1] H.-H. Tseng, C. C. Capasso, J. K. Schaeffer, E. A. Hebert, P. J. Tobin, D. C. Gilmer, D. Triyoso, M. E. Ramón, S. Kalpat, E. Luckowski, W. J. Taylor, Y. Jeon, O. Adetutu, R. I. Hegde, R. Noble, M. Jahanbani, C. El Chemali, and B. E. White, "Improved short channel device characteristics with stress relieved pre-oxide (SRPO) and a novel tantalum carbon alloy metal gate/HfO<sub>2</sub> stack," in *IEDM Tech. Dig.*, 2004, pp. 821–824.

- [2] B. Tavel, T. Skotnicki, G. Pares, N. Carrière, M. Rivoire, F. Leverd, C. Julien, J. Torres, and R. Pantel, "Totally silicided (CoSi<sub>2</sub>) polysilicon: A novel approach to very low-resistive gate (~2Ω/□) without metal CMP nor etching," in *IEDM Tech. Dig.*, 2001, pp. 815–828.

[3] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goollgweon, and

- [3] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goollgweon, and M. R. Lin, "Transistors with dual work function metal gate by single full silicidation (FUSI) of polysilicon gates," in *IEDM Tech. Dig.*, 2002, pp. 367–370.

- [4] C. H. Huang, D. S. Yu, A. Chin, W. J. Chen, C. X. Zhu, M.-F. Li, B. J. Cho, and D. L. Kwong, "Fully silicided NiSi and germanided NiGe dual gates on SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Ge-On-Insulator MOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 319–322.

- [5] C. Y. Lin, D. S. Yu, A. Chin, C. Zhu, M. F. Li, and D. L. Kwong, "Fully silicided NiSi gate on La<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 24, no. 5, pp. 348–350, May 2003.

- [6] C. S. Park, B. J. Cho, and D. L. Kwong, "Thermally stable fully silicided Hf-silicide metal-gate electrode," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 372–374, Jun. 2004.

- [7] A. Veloso, K. G. Anil, L. Witters, S. Brus, S. Kubicek, J.-F. de Marneffe, B. Sijmus, K. Devriendt, A. Lauwers, T. Kauerauf, M. Jurczak, and S. Biesemans, "Work function engineering by FUSI and its impact on the performance and reliability of oxynitride and Hf-silicate based MOSFETs," in *IEDM Tech. Dig.*, 2004, pp. 855–858.

- [8] M. Koyama, Y. Kamimuta, T. Ino, A. Kaneko, S. Inumiya, K. Eguchi, M. Takayanagi, and A. Nishiyama, "Careful examination on the asymmetric V<sub>fb</sub> shift problem for Poly-Si/HfSiON gate stack and its

solution by the Hf concentration control in the dielectric near the Poly-Si interface with small EOT expense," in *IEDM Tech. Dig.*, 2004, pp. 499–502.

- [9] K. Takahashi, K. Manabe, T. Ikarashi, N. Ikarashi, T. Hase, T. Yoshihara, H. Watanabe, T. Tatsumi, and Y. Mochizuki, "Dual workfunction Ni-silicide/HfSiON gate stacks by phase-controlled fullsilicidation (PC-FUSI) technique for 45 nm-node LSTP and LOP devices," in *IEDM Tech. Dig.*, 2004, pp. 91–94.

- [10] X. Yu, C. Zu, X. P. Wang, M.-F. Li, A. Chin, A. Y. Du, W. D. Wang, and D. L. Kwong, "High mobility and excellent electrical stability of MOS-FETs using a novel HfTaO gate dielectric," in *VLSI Symp. Tech. Dig.*, 2004, pp. 110–111.

- [11] D. S. Yu, A. Chin, C. H. Wu, M.-F. Li, C. Zhu, S. J. Wang, W. J. Yoo, B. F. Hung, and S. P. McAlister, "Lanthanide and Ir-based dual metalgate/HfAION CMOS with large work-function difference," in *IEDM Tech. Dig.*, 2005, pp. 649–652.

- [12] T. Hoffmann, A. Veloso, A. Lauwers, H. Yu, H. Tigelaar, M. Van Dal, T. Chiarella, C. Kerner, T. Kauerauf, A. Shickova, R. Mitsuhashi, I. Satoru, M. Niwa, A. Rothschild, B. Froment, J. Ramos, A. Nackaerts, M. Rosmeulen, S. Brus, C. Vrancken, P. P. Absil, M. Jurczak, S. Biesemans, and J. A. Kittl, "Ni-based FUSI gates: CMOS integration for 45 nm node and beyond," in *IEDM Tech. Dig.*, 2006, pp. 269–272.

- [13] P. F. Hsu, Y. T. Hou, F. Y. Yen, V. S. Chang, P. S. Lim, C. L. Hung, L. G. Yao, J. C. Jiang, H. J. Lin, J. M. Chiou, K. M. Yin, J. J. Lee, R. L. Hwang, Y. Jin, S. M. Chang, H. J. Tao, S. C. Chen, M. S. Liang, and T. P. Ma, "Advanced dual metal gate MOSFETs with high-k dielectric for CMOS application," in VLSI Symp. Tech. Dig., 2006, pp. 11–12.

- [14] C. H. Wu, B. F. Hung, A. Chin, S. J. Wang, F. Y. Yen, Y. T. Hou, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang, "HfSiON n-MOSFETs using low work function HfSi<sub>x</sub> gate," *IEEE Electron Device Lett.*, vol. 27, no. 9, pp. 762–764, Sep. 2006.

- [15] C. H. Wu, B. F. Hung, A. Chin, S. J. Wang, W. J. Chen, X. P. Wang, M.-F. Li, C. Zhu, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang, "High temperature stable [Ir<sub>3</sub>Si-TaN]/HfLaON CMOS with large work-function difference," in *IEDM Tech. Dig.*, 2006, pp. 617–620.