# Improved High-Temperature Leakage in High-Density MIM Capacitors by Using a TiLaO Dielectric and an Ir Electrode

C. H. Cheng, H. C. Pan, H. J. Yang, C. N. Hsiao, C. P. Chou, S. P. McAlister, *Senior Member, IEEE*, and Albert Chin, *Senior Member, IEEE*

Abstract—We have fabricated high- $\kappa$  TaN/Ir/TiLaO/TaN metal-insulator-metal capacitors. A low leakage current of  $6.6 \times 10^{-7}$  A/cm² was obtained at 125 °C for 24-fF/ $\mu$ m² density capacitors. The excellent device performance is due to the combined effects of the high- $\kappa$  TiLaO dielectric, a high workfunction Ir electrode, and large conduction band offset.

Index Terms—High- $\kappa$ , Ir, metal–insulator–metal (MIM), TiLaO.

## I. Introduction

THERE is a continuing demand to increase the capacitance density  $(\varepsilon_0 \kappa/t_\kappa)$  of the metal–insulator–metal (MIM) capacitors [1]-[16]. To achieve this, the MIM devices have evolved by using higher  $\kappa$  dielectrics such as SiN [3], [4], Al<sub>2</sub>O<sub>3</sub> [6], [7], Ta<sub>2</sub>O<sub>5</sub> [5], HfO<sub>2</sub> [8]–[10], Nb<sub>2</sub>O<sub>5</sub> [11], TiTaO [12], [13], and SrTiO<sub>3</sub> (STO) [14]–[16]. Unfortunately, increasing the  $\kappa$  value usually decreases the conduction band offset  $(\Delta E_C)$  with respect to the metal electrode. For STO [17],  $\Delta E_C$ can even be slightly negative. A low  $\Delta E_C$  leads to unwanted leakage current for a MIM device at high temperatures [16], where such increase in the operational temperature is unavoidable due to the increased circuit density and higher power dissipation. Although STO shows higher  $\kappa$  values and good device characteristics, a higher process temperature > 450 °C for nanocrystal formation and thicker thickness to reduce leakage are necessary. This exceeds the maximum temperature (400 °C) permitted for backend integration [14]–[16].

Here, we report low thermal leakage TiLaO MIM capacitors using a high work-function Ir electrode, which are processed at 400 °C. We measured leakage currents of  $1\times10^{-7}$  and  $6.6\times10^{-7}~\text{A/cm}^2$  at 1 V at 25 °C and 125 °C, respectively; these

Manuscript received August 16, 2007; revised September 26, 2007. This work was supported in part by NSC 95-2221-E-009-275 of Taiwan. The review of this letter was arranged by Editor A. Wang.

- C. H. Cheng and C. P. Chou are with the Department of Mechanical Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

- H. C. Pan and C. N. Hsiao are with the Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu, Taiwan, R.O.C.

- H. J. Yang and A. Chin are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: albert\_achin@hotmail.com; achin@cc.nctu.edu.tw).

- S. P. McAlister is with the National Research Council of Canada, Ottawa, ON K1A 0R6, Canada.

- Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2007.909612

currents are lower than those in the previously reported TiTaO and 400 °C-processed STO capacitors.

# II. EXPERIMENTAL PROCEDURE

The high- $\kappa$  TiLaO MIM capacitors were fabricated on standard Si wafers. To permit VLSI backend integration, the process began with depositing a 2-\mu m-thick SiO<sub>2</sub> isolation layer on the Si substrates. Then, a 50-nm TaN was deposited on a 200-nm Ta layer by sputtering and used as the lower capacitor electrode. The TaN surface was then given a plasma treatment to increase the oxidation resistance before the high- $\kappa$  deposition and postdeposition annealing (PDA) [5], [6]. A 15-nm-thick  $Ti_x La_{1-x}O$  (x ~ 0.67) film was deposited by PVD, followed by a 400-°C PDA in an oxygen ambient to reduce the defects and the leakage current [3] (the TiLaO thickness was later measured by cross-sectional transmission electron microscopy). Finally, 20-nm Ir and/or 50-nm TaN were deposited and patterned to form the top electrode. A large capacitor size of 100  $\mu$ m  $\times$ 100  $\mu$ m was chosen to avoid any variations in dimensions arising from lithography. The devices were characterized by C-V and J-V measurements.

#### III. RESULTS AND DISCUSSION

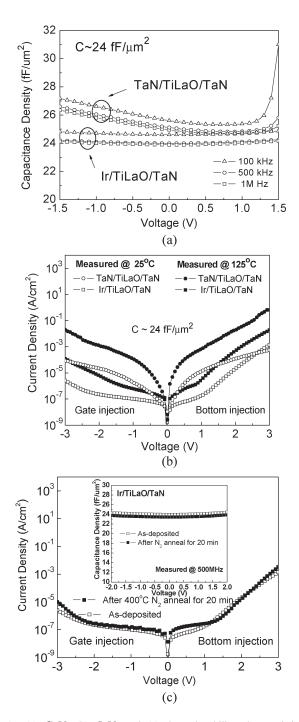

In Fig. 1, we show the C-V, J-V, and thermal-stability characteristics of TaN/TiLaO/TaN and TaN/Ir/TiLaO/TaN devices. A comparison with other data is summarized in Table I. A high capacitance density of 24–24.5 fF/ $\mu$ m<sup>2</sup> was measured for the TiLaO MIM devices, which gives a high- $\kappa$  value of  $\sim$ 45 for the TiLaO dielectric. A leakage current of  $2.2 \times 10^{-6}$  A/cm<sup>2</sup> at -1 V was measured for the TaN/TiLaO/TaN MIM capacitor close to that of an Ir/TiTaO/TaN device (Table I) with a slightly lower capacitance density. Since the work function of the TaN on TiLaO is  $\sim 0.7$  V lower than that of Ir on TiTaO, the comparable leakage current indicates that the TiLaO is a better choice for MIM capacitors than TiTaO. This is confirmed by the five times lower leakage current of  $1 \times 10^{-7}$  A/cm<sup>2</sup> in the TaN/Ir/TiLaO/TaN device compared with the Ir/TiTaO/TaN capacitor. This improved leakage current, at a comparable capacitance density, is due to the higher  $\Delta E_C$  between metal and high- $\kappa$  interface, which lowers the leakage current exponentially. A similar lower leakage current was also reported by adding higher  $\Delta E_C$  Al<sub>2</sub>O<sub>3</sub> into HfO<sub>2</sub> MIM capacitor [9]. The

Fig. 1. (a) C-V, (b) J-V, and (c) thermal-stability characteristics of TaN/TiLaO/TaN and TaN/Ir/TiLaO/TaN MIM capacitors measured at various frequencies, at 25 °C and 125 °C. The thermal-stability test was performance at 400 °C for 20 min in an ambient N<sub>2</sub>.

small changes of J-V and C-V, after 400-°C  $N_2$  annealing, indicate that the thermal stability is acceptable. Note that good thermal stability was reported for metal-gate/high- $\kappa$  pMOS for Ir on HfAlON at Rapid Thermal Anneal (RTA) temperatures up to 900 °C [17].

A larger  $\Delta E_C$  at the metal/high- $\kappa$  interface is very important at 125 °C, which is a temperature required for both DRAM and nonvolatile memory [18]. This is shown in the comparison with STO: The leakage current (at -1 V) of a 400 °C-formed Ni/STO/TaN capacitor increased from  $2 \times 10^{-7}$  to  $5 \times 10^{-7}$

TABLE I

COMPARISON OF MIM CAPACITORS WITH VARIOUS

DIELECTRICS AND METAL ELECTRODES

|                                    | HfO <sub>2</sub><br>[8]    | ${ m Tb}	ext{-} \\ { m HfO}_2 \\ [10]$ | Al <sub>2</sub> O <sub>3</sub> -<br>HfO <sub>2</sub><br>[9] | TiTaO<br>[12]-[13]         | STO<br>[16]                                              | STO<br>[14]                | TiLaO                        |                                                              |

|------------------------------------|----------------------------|----------------------------------------|-------------------------------------------------------------|----------------------------|----------------------------------------------------------|----------------------------|------------------------------|--------------------------------------------------------------|

| Process<br>Temp. (°C)              | 400                        | 400                                    | 400                                                         | 400                        | 400                                                      | 450                        | 400                          |                                                              |

| Top<br>Electrode                   | Та                         | Та                                     | TaN                                                         | Ir                         | Ni                                                       | TaN                        | TaN                          | Ir                                                           |

| Work-function<br>(eV)              | 4.2                        | 4.2                                    | 4.6                                                         | 5.27                       | 5.1                                                      | 4.6                        | 4.6                          | 5.27                                                         |

| C Density<br>(fF/µm <sup>2</sup> ) | 13                         | 13.3                                   | 12.8                                                        | 23                         | 25.2                                                     | 28                         | 24.5                         | 24                                                           |

| J (A/cm²)<br>@25°C                 | 6×10 <sup>-7</sup><br>(2V) | 1×10 <sup>-7</sup><br>(2V)             | (2V)                                                        | 2×10 <sup>-5</sup><br>(2V) | 2×10 <sup>-7</sup><br>(1V)<br>8×10 <sup>-6</sup><br>(2V) | 3×10 <sup>-8</sup><br>(2V) | 2.2×10 <sup>-6</sup><br>(1V) | 2.3×10 <sup>-7</sup><br>(2V)                                 |

| J (A/cm <sup>2</sup> )<br>@125°C   | 2×10 <sup>-6</sup><br>(1V) | 2×10 <sup>-7</sup><br>(2V)             | 6×10 <sup>-9</sup><br>(1V)<br>5×10 <sup>-8</sup><br>(2V)    | -                          | 5×10 <sup>-6</sup> (1V)                                  | -                          | 1.3×10 <sup>-4</sup>         | 6.6×10 <sup>-7</sup><br>(1V)<br>6.7×10 <sup>-6</sup><br>(2V) |

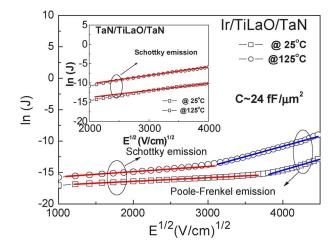

Fig. 2. Measured and simulated  $J-E^{1/2}$  of an Ir/TiLaO/TaN capacitor. A TaN/TiLaO/TaN device is shown, for comparison, in the inset.

$10^{-6}$  A/cm<sup>2</sup>, from 25 °C to 125 °C (Table I), whereas in the TaN/Ir/TiLaO/TaN capacitor, it only increased from  $1 \times 10^{-7}$  to  $6.6 \times 10^{-7}$  A/cm<sup>2</sup>. Although the work function of the Ir electrode (5.27 eV) is slightly higher than Ni (5.1 eV), the improved 125-°C leakage current can be attributed to the large  $\Delta E_C$ . We note that La<sub>2</sub>O<sub>3</sub> has the highest  $\Delta E_C$  with respect to Si (2.3 eV) compared with HfO<sub>2</sub> (1.5 eV), ZrO<sub>2</sub> (1.4 eV), Ta<sub>2</sub>O<sub>5</sub> (0.3 eV), and STO (-0.1 eV) [19].

To investigate the current conduction mechanism we plot, in Fig. 2,  $\ln(J)$  versus  $E^{1/2}$  for the TaN/Ir/TiLaO/TaN MIM capacitors

$$J \propto \exp\left(\frac{\gamma E^{1/2} - V_b}{kT}\right) \tag{1}$$

$$\gamma = \left(\frac{e^3}{\eta \pi \varepsilon_0 K_\infty}\right)^{1/2}.$$

(2)

Here,  $K_{\infty}$  is the high-frequency dielectric constant (=  $n^2$ ). The refractive index n is 2.57 or 1.9 for TiO<sub>2</sub> or La<sub>2</sub>O<sub>3</sub> [20],

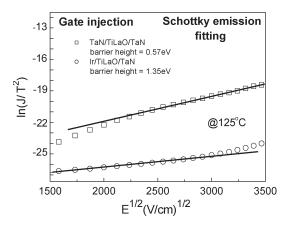

Fig. 3.  $J/T^2\hbox{-}E^{1/2}$  plots of TaN/TiLaO/TaN and TaN/Ir/TiLaO/TaN MIM capacitors.

and  $\eta$  is 1 or 4 for Schottky emission (SE) or Frenkel–Poole (FP) conduction, respectively. The data fitting suggests that the current conduction mechanism of the TaN/Ir/TiLaO/TaN device changes from SE at low electric fields to FP at higher fields. In contrast, the TaN/TiLaO/TaN devices fit an SE description at both low and high fields.

The SE barrier height  $(V_b)$  at 125 °C was determined from  $J/T^2-E^{1/2}$  plots (Fig. 3). Values for  $V_b$  were 0.57 and 1.35 eV for TiLaO devices at 125 °C with TaN and Ir top electrodes, respectively. The large  $V_b$  difference explains the reduced leakage current and the weaker temperature dependence in the TaN/Ir/TiLaO/TaN devices. Thus, a low leakage current at high temperature can be obtained in MIM capacitors by combining a high- $\kappa$  dielectric, having a high  $\Delta E_C$ , with a high work-function metal electrode.

### IV. CONCLUSION

A high capacitance density and low leakage current at 125 °C have been achieved in Ir/TiLaO/TaN MIM capacitors. The device-processing temperature of 400 °C would enable them to be integrated into the VLSI backend technology and be used in multiple functions associated with system-on-a-chip.

# REFERENCES

- [1] The International Technology Roadmap for Semiconductors: Semicond. Ind. Assoc., 2005. [Online]. Available: www.itrs.net

- [2] C.-M. Hung, Y.-C. Ho, I.-C. Wu, and K. O, "High-Q capacitors implemented in a CMOS process for low-power wireless applications," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, 1998, pp. 505–511.

- [3] J. A. Babcock, S. G. Balster, A. Pinto, C. Dirnecker, P. Steinmann, R. Jumpertz, and B. El-Kareh, "Analog characteristics of metal-insulatormetal capacitors using PECVD nitride dielectrics," *IEEE Electron Device Lett.*, vol. 22, no. 5, pp. 230–232, May 2001.

- [4] C. H. Ng, K. W. Chew, and S. F. Chu, "Characterization and comparison of PECVD silicon nitride and silicon oxynitride dielectric for MIM capacitors," *IEEE Electron Device Lett.*, vol. 24, no. 8, pp. 506–508, Aug. 2003.

- [5] T. Ishikawa, D. Kodama, Y. Matsui, M. Hiratani, T. Furusawa, and D. Hisamoto, "High-capacitance Cu/Ta<sub>2</sub>O<sub>5</sub>/Cu MIM structure for SoC applications featuring a single-mask add-on process," in *IEDM Tech. Dig.*, 2002, pp. 940–942.

- [6] S. B. Chen, J. H. Lai, A. Chin, J. C. Hsieh, and J. Liu, "High-density MIM capacitors using Al<sub>2</sub>O<sub>3</sub> and AlTiO<sub>x</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 23, no. 4, pp. 185–188, Apr. 2002.

- [7] S. B. Chen, J. H. Lai, K. T. Chan, A. Chin, J. C. Hsieh, and J. Liu, "Frequency-dependent capacitance reduction in high-k AlTiO<sub>x</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics from IF to RF frequency range," *IEEE Electron Device Lett.*, vol. 23, no. 4, pp. 203–205, Apr. 2002.

- [8] X. Yu, C. Zhu, H. Hu, A. Chin, M. F. Li, B. J. Cho, D.-L. Kwong, P. D. Foo, and M. B. Yu, "A high-density MIM capacitor (13 fF/μm²) using ALD HfO<sub>2</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 24, no. 2, pp. 63–65, Feb. 2003.

- [9] H. Hu, S. J. Ding, H. F. Lim, C. Zhu, M. F. Li, S. J. Kim, X. F. Yu, J. H. Chen, Y. F. Yong, B. J. Cho, D. S. H. Chan, S. C. Rustagi, M. B. Yu, C. H. Tung, A. Du, D. My, P. D. Fu, A. Chin, and D. L. Kwong, "High performance HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate MIM capacitors by ALD for RF and mixed signal IC applications," in *IEDM Tech. Dig.*, 2003, pp. 379–382.

- [10] S. J. Kim, B. J. Cho, M.-F. Li, C. Zhu, A. Chin, and D. L. Kwong, "HfO<sub>2</sub> and Lanthanide-doped HfO<sub>2</sub> MIM capacitors for RF/mixed IC applications," in *VLSI Symp. Tech. Dig.*, 2003, pp. 77–78.

- [11] S. J. Kim, B. J. Cho, M. B. Yu, M.-F. Li, Y.-Z. Xiong, C. Zhu, A. Chin, and D. L. Kwong, "High capacitance density (> 17 fF/\(\mu\mathrm{m}^2\))Nb<sub>2</sub>O<sub>5</sub>-based MIM capacitors for future RF IC applications," in VLSI Symp. Tech. Dig., 2005, pp. 56–57.

- [12] K. C. Chiang, A. Chin, C. H. Lai, W. J. Chen, C. F. Cheng, B. F. Hung, and C. C. Liao, "Very high-κ and high density TiTaO MIM capacitors for analog and RF applications," in VLSI Symp. Tech. Dig., 2005, pp. 62–63.

- [13] K. C. Chiang, C. H. Lai, A. Chin, T. J. Wang, H. F. Chiu, J. R. Chen, S. P. McAlister, and C. C. Chi, "Very high density (23 fF/μm²) RF MIM capacitors using high-κ TiTaO as the dielectric," *IEEE Electron Device Lett.*, vol. 26, no. 10, pp. 728–730, Oct. 2005.

- [14] K. C. Chiang, C. C. Huang, A. Chin, W. J. Chen, H. L. Kao, M. Hong, and J. Kwo, "High performance micro-crystallized TaN/SrTiO<sub>3</sub>/TaN capacitors for analog and RF applications," in VLSI Symp. Tech. Dig., 2006, pp. 126–127.

- [15] K. C. Chiang, C. C. Huang, A. Chin, G. L. Chen, W. J. Chen, Y. H. Wu, A. Chin, and S. P. McAlister, "High performance SrTiO<sub>3</sub> MIM capacitors for analog applications," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2312–2319, Sep. 2006.

- [16] K. C. Chiang, C. H. Cheng, H. C. Pan, C. N. Hsiao, C. P. Chou, A. Chin, and H. L. Hwang, "High-temperature leakage improvement in Metal-Insulator-Metal capacitors by work-function tuning," *IEEE Electron Device Lett.*, vol. 28, no. 3, pp. 235–237, Mar. 2007.

- [17] D. S. Yu, A. Chin, C. H. Wu, M.-F. Li, C. Zhu, S. J. Wang, W. J. Yoo, B. F. Hung, and S. P. McAlister, "Lanthanide and Ir-based dual metalgate/HfAlON CMOS with large work-function difference," in *IEDM Tech. Dig.*, 2005, pp. 649–652.

- [18] C. H. Lai, A. Chin, H. L. Kao, K. M. Chen, M. Hong, J. Kwo, and C. C. Chi, "Very low voltage SiO<sub>2</sub>/HfON/HfAIO/TaN memory with fast speed and good retention," in VLSI Symp. Tech. Dig., 2006, pp. 54–55.

- [19] J. Robertson, "Band offsets of wide-band-gap oxides and implications for future electron devices," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 18, no. 3, pp. 1785–1791, May 2000.

- [20] F. C. Chiu, H. W. Chou, and J. Y.-M. Lee, "Electrical conduction mechanisms of metal/La<sub>2</sub>O<sub>3</sub>/Si structure," *J. Appl. Phys.*, vol. 97, no. 10, pp. 103 503-1–103 503-5, May 2005.