##

計畫主持人:黃調元 交通大學電子工程系教授協同研究人員:林鴻志 國科會毫微米實驗室研究員

本成果報告包括以下應繳交之附件:

□赴國外出差或研習心得報告一份

□赴大陸地區出差或研習心得報告一份

□出席國際學術會議心得報告及發表之論文各一份

□國際合作研究計畫國外研究報告書一份

執行單位:國立交通大學電子工程系

中華民國89年10月30日

### 行政院國家科學委員會專題研究計畫成果報告

深次微米多晶矽鍺閘極金氧半電晶體之研製

# Fabrication and Charazterization of Deep Submicron MOS Transistor with Poly-SiGe Gate

計畫編號: NSC 89-2215-E-009-038

執行期限:88年8月1日至89年7月31日

主持人:黃調元 國立交通大學電子工程系教授

協同研究人員:林鴻志 國家毫微米元件實驗室研究員

#### 一、中文摘要

本計畫成功的研製以多晶矽鍺做為閘極之 N 型金氧半電晶體。計畫中調整沈積溫度及變化氣體源中含鍺原子濃度以達適當之鍺原子莫耳數。元件特性方面,多晶矽鍺與傳統之多晶矽具有相當的次臨界電流特性與飽和電流。而金屬鎳與多晶矽鍺形成之矽化金屬為高。

關鍵詞:多晶矽鍺,矽化金屬

#### Abstract

In this project, we have successfully fabricated MOSFET with n- type poly-SiGe gate by LPCVD using SiH<sub>4</sub> and GeH<sub>4</sub> as gaseous source. The deposition temperature and Ge concentration in gaseous source were varied to optimize the Ge mole fraction . Sheet resistance of Nickle germanosilicide was also studied.

**Keywords**: poly-SiGe, silicide

#### 二、緣由與目的

CMOS 製程中,為提高元件積成度及 特性,持續的降低閘極氧化層厚度是必然 趨勢。然而,氧化層變薄隨之而來的是 gate depletion 及硼穿透現象,對元件特性劣化 造成嚴重影響。文獻中顯示,應用多晶矽 鍺可改善上述缺失。

多晶矽鍺(poly-SiGe)是近來極受重視的另一種材料。它的主要優點為: $(1)n^+$  poly-SiGe 在 Ge 含量約為 20%時,載子活化率明顯較  $n^+$  poly-Si 高,可改善 poly depletion 現象[1]。 $(2)p^+$  poly-SiGe 載子活化率隨 Ge 含量增加而上昇,同樣可改善 poly

depletion 現象[1-2]。(3)p<sup>+</sup> poly-SiGe 的硼穿透現象減輕,除了減少  $V_{th}$  飄移外,氧化層特性,如崩潰電荷量及電應力導致的漏電流 (stress-induced leakage current or SILC) 均有顯著的改善。(4)載子活化溫度較 poly-Si低且時間可進一步減少,符合未來低溫化製程。(5)可以傳統 LPCVD 技術製備,且與一般 poly-Si 製程相容,無需耗費大量機台與製程研發成本。因為上述優點,很多公司將之視為  $130\,$  nm 乃至  $100\,$ nm 以下元件主要的閘極技術。

poly-SiGe 能隙(energy bandgap)隨著 Ge 含量增加而減少,但無論含量多寡,其 conduction band edge 和 poly-Si 的 conduction band edge 都差不多,所以主要 的變化在於 valence band 位置[3]。因此 n+ poly-SiGe 調整臨界電壓的能力與 n<sup>+</sup> poly-Si 相當,而p<sup>+</sup> poly-SiGe 則可籍由改變 Ge 含量來調整臨界電壓。對於一 p+poly-SiGe 材料而言,其費米能位約在矽基板能除的 中間,近似 mid-gap 功函數的材料。有人 嘗試以高 Ge 含量的 poly-SiGe 作為 single poly 的閘極(如[4]的 100%及[5]的 74%),可 得到近似對稱的臨界電壓特性,惟其問題 仍為前所述的臨界電壓值過高的限制。至 於 dual poly 方面的應用,考量 n<sup>+</sup> poly-SiGe 的活化性質, Ge 含量的最佳值約在 20% 左 右[1]。

poly-SiGe 主要問題在於 salicide 製程時熱穩定性劣化,其成因為過程中形成的金屬鍺化物(germanide)融點低,在低溫下就很容易團塊化(agglomeration),造成片電阻上揚[6]。一般解決方法,係在 poly-SiGe上多沈積一 poly-Si 覆蓋層,以作為 salicide 反應用,以避免上述問題。但此 poly-Si 的

存在造成後續高溫程序時,Ge 外擴散(out diffusion)的現象[2],影響 Ge 的含量及臨界電壓的精準控制。因此,對於金屬鎳而言,其 salicide 形成溫度較 Co 或 Ti 為低,且製程溫度範圍(process window)廣,可直接應用於 poly-SiGe 之上,改善其熱穩定性劣化之缺失[7]。

#### 三、實驗方法

#### (a)、POLY-Si<sub>1-x</sub>Ge<sub>x</sub> 薄膜特性

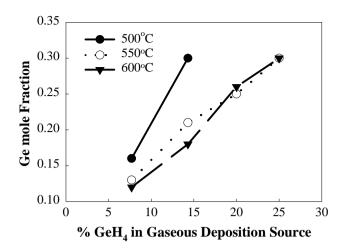

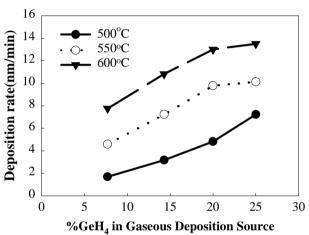

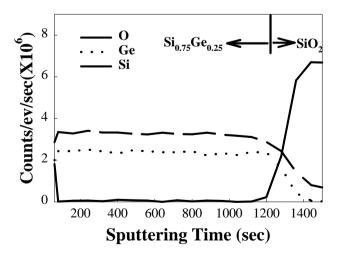

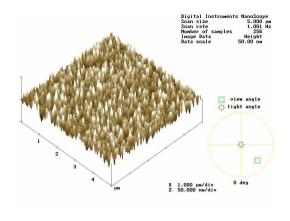

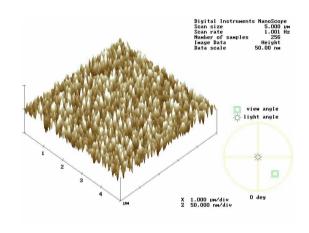

針對 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 薄膜的製備上,於一 般低壓系統下,調整沈積溫度並改變 SiH4 與 GeH4 的比例,以達到適當的鍺原子莫耳 數. 從圖一可看出在沈積薄膜 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 時,Ge 莫耳數(x)隨著氣體源中含Ge 之濃 度及溫度而變化。大致上, Ge 莫耳數與氣 體源中含 Ge 之濃度成一線性關係。圖二 為不同溫度下 poly-SiGe 沈積速率與氣體 源中含 Ge 之濃度之關係,其中 SiH4 流量 保持在 60sccm。為求達到元件操作最佳效 能,我們選擇 Ge 莫耳數、X=0.25 做為元 件閘極使用。圖三為在 600℃下, GeH<sub>4</sub>:SiH<sub>4</sub>=15 sccm: 60 sccm , 沈積壓力 約 110 mtorr 下的歐傑電子縱深圖。圖中可 看出 poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 薄膜中, Ge 的分佈相 當均勻,這對於 poly-SiGe 用來製作閘極材 料而言是相當重要的。因為 Ge 原子分佈的 均勻性將直接影響元件臨界電壓之穩定 性。此外,我們比較 poly-SiGe 與 poly-Si 表面粗糙程度。圖四(a),(b) 分別為 600°C下 poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 與 620°C下 poly-Si 表面之 AFM 圖形。poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 表面粗 糙之方均根(RMS)值為 6.2 nm 較 poly-Si 3.9 nm 大些。

#### (b)、元件製作過程

圖五為摻雜 n-type 之 poly- $Si_{0.75}Ge_{0.25}$  金氧半電晶體之研製過程。元件製作於 6 吋 p-type 方向為(100)矽晶片上。過程如下:先使用局部氧化(LOCOS)將製作元件隔離區,接著成長閘極氧化層 4.8 nm(經由 C-V 量測法),再沈積 poly- $Si_{0.75}Ge_{0.25}$  薄膜 200 nm。用  $Cl_2/HBr$  氣體蝕刻閘極。接著進行閘/源/汲極離子佈植(能量:35 keV,計量: $5\times$   $10^{15}$ cm<sup>-2</sup> 並進行離子活化,最後定義接觸孔,及金屬化製程完成電晶體製

作。

#### 四、結果與討論

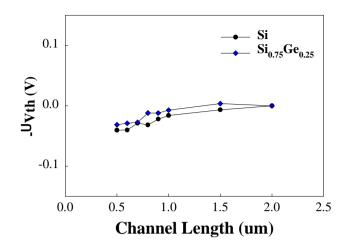

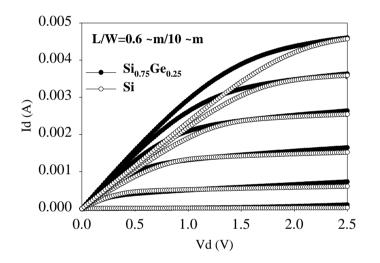

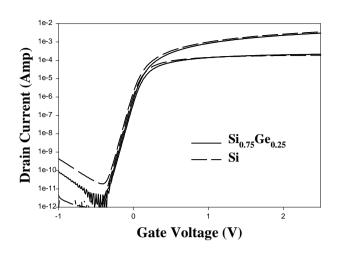

圖六為臨界電壓變動量與通道長度之關係。由此看出 n<sup>+</sup> poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 與 n<sup>+</sup> poly-Si 特性相當,並未有較差之短通道效應。圖七為 poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 與 poly-Si 電晶體之 Id-Vd 圖形,兩者飽和電流均相當。至於其次臨界電流特性與傳統 poly-Si 元件相當。圖八為兩電晶體之次臨界 Id-Vg 之特性,

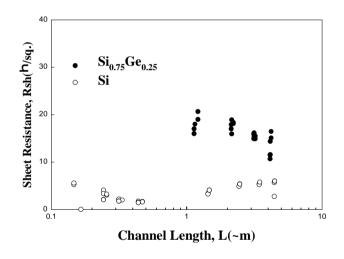

圖九為比較鎳矽化金屬製程之閘極片電阻與線寬之關係。製程條件為550℃,時間60秒之快速退火爐。圖中顯示poly-Si<sub>0.75</sub>Ge<sub>0.25</sub>材質之片電阻較poly-Si為大,其成因有可能為poly-Si<sub>0.75</sub>Ge<sub>0.25</sub>表面較poly-Si 為粗糙,平坦程度較差,所以形成salicide特性並未如預期與poly-Si 一般。

#### 五、結論

本實驗成功的研製 N 型多晶矽鍺閘極之金氧半電晶體。元件特性與傳統製程相近。與此外我們使用一般的低壓爐管探討poly-Si<sub>1-x</sub>Ge<sub>x</sub>的薄膜特性,包括沈積溫度,Ge 原子的莫耳數,及沈積速率等相互關係,已達成本計畫之重要目標,未來就是探討 p 型多晶矽鍺閘極之金氧半電晶體對元件的影響。

#### 六、参考文獻

- [1] W. C. Lee et al., Symp. VLSI Technolo. pp. 190-191 (1998).

- [2] Y. V. Ponomarev et al, IEDM Tech. Digest, pp. 829-832 (1997).

- [3] 林鴻志,"深次微米閘極工程技術發展" 電子月刊第 40 期第 68-84 頁(1998 年 11 月).

- [4] J. Alieu et al., Symp. VLSI Technolo. pp. 192-193 (1998).

- [5] V. Z-Q. Li et al., IEEE Tech. Digest, pp.833-836 (1997).

- [6] Z. Wang et al., Thin Solid Films, 270, pp. 555 (1995).

- [7] Ja-Hum Ku et al., Symp. VLSI Tech. pp. 114-115, (2000).

圖一、不同溫度下,沈積薄膜 poly-Si<sub>1-x</sub>Gex 中的 Ge 莫耳數與氣體源中含 Ge 之濃度之

圖二、不同溫度下, $poly-Si_{1-x}Ge_x$  沈積速率與氣體源中含 Ge 之濃度之關係 $(SiH_4$  保持在 60sccm)。

圖三為在 600℃下, GeH<sub>4</sub>:SiH<sub>4</sub>=15 sccm: 60 sccm , 沈積壓力約 110 mtorr 下的歐傑電子縱深圖。

圖四(a)沈積溫度 600°C 下 poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 表面之 AFM 圖形。

圖四(b)沈積温度 620℃下 poly-Si 表面 2 AFM 圖形。

- LOCOS Isolation

- Gate Oxide Growth (4.8 nm)

- Poly-Si <sub>0.75</sub> Ge <sub>0.25</sub> or Poly-Si deposition

- Gate pattern

- S/D implant

- E: 35 KeV, D: 5E15 cm<sup>-2</sup>

- > RTA:1000°C, 10 sec

- Contact hole

- Metallization

圖五、摻雜 n-type 之 poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 金 氧半電晶體之製造流程。

圖六為臨界電壓變動量與通道長度之關係。

圖七為 poly- $Si_{0.75}Ge_{0.25}$ , 與 poly-Si 電晶體 之 Id-Vd 特性比較。

圖八為 n-type poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> 與 poly-Si 電晶體之次臨界 Id-Vg 之特性。

圖九為比較鎮矽化金屬製程之閘極片電 阻與線寬之關係。