# 行政院國家科學委員會研究計畫成果報告

計畫題目: 矽鍺非應力層在高速電晶體及射頻元件的應用

計畫編號: NSC 89-2215-E-009-044 執行期限: 88年8月1日至 89年7月31日

主持人: 荊鳳德 教授 執行單位: 交通大學電子工程系 學生: 梁竹欣

# 中文摘要

本計畫主研究成長於矽化鍺合金上氧 化層之可靠度。氧化層的介面捕捉密度及 內部電荷密度皆可達到非常低的值。這是 由於高溫製程之矽鍺合金,其表面已非常 平滑,且經過九百度西氧化作用後,其內 部應力亦已平復之故。

關鍵詞: 矽化鍺合金、氧化層可靠度分析

#### Abstract

We have investigated the gate oxide integrity of thermal oxides direct grown on high temperature formed  $Si_{0.3}Ge_{0.7}$ . Good oxide integrity is evidenced by the low interface-trap density of  $5.9 \times 10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup>, low oxide charge density of  $-5.6 \times 10^{10}$  cm<sup>-2</sup>, and the small stress-induced leakage current after 3.3V stress for 10,000s. The good gate oxide integrity is due to the high temperature formed and strain-relaxed  $Si_{0.3}Ge_{0.7}$  that has a original smooth surface and stable after subsequent high temperature process.

#### keywords: SiGe, oxide reliability

#### 一、簡介

Gate oxide integrity [1]-[6] is one of the most important factors for process integration. Although SiGe channel p-MOSFETs [5]-[11] has improved current-drive capability, operation speed, and package density of CMOS circuits, the gate oxide integrity is still unexamined. To prevent strain relaxation and defect generation, low temperature (T<800 ) processing is necessary for SiGe p-MOSFET. Unfortunately, both gate oxide integrity and junction leakage are

much degraded at the limited low temperature [12], and also obstacles further process integration with modern high-K gate dielectric [13]-[14]. Recently, we developed a new SiGe formation process using deposited amorphous Ge followed by rapid thermal annealing (RTA) [15]. Because SiGe is formed by solid phase epitaxy at high temperatures similar to silicide formation [16], better thermal stability can be expected. High hole mobility of 250 cm<sup>2</sup>/Vs and low source-drain p<sup>+</sup>n junction leakage are obtained using high temperature (950°C) RTA of B<sup>+</sup> implanted damages [17]. In this paper, we have further investigated the gate oxide integrity of oxide directly grown temperature formed SiGe. Good oxide integrity is evidenced by low interface-trap density, smooth surface and small stress-induced leakage current (SILC), which is attributed to the high SiGe forming temperature and no rough surface pinholes [9]-[11] are formed during subsequent device processing.

### 二、實驗方法

Standard 4-in (100) Si wafers were used in this work. In addition to SiGe oxides, Si control oxides were also fabricated as references. After device isolation, ~120Å amorphous Ge layer is deposited on\_active region. A HF-vapor passivation is used to suppress the native oxide formation before Ge deposition [3], [14]-[17]. A 200Å Si<sub>0.3</sub>Ge<sub>0.7</sub> with good crystalline quality was then formed by RTA at 900°C as measured by cross-sectional TEM and Si<sub>0.3</sub>Ge<sub>0.7</sub> by X-ray diffraction. More detailed material characterization can be found in our previous study [16]-[17]. Gate oxides of 50Å were then grown by dry O<sub>2</sub> at 900°C for both Si<sub>0.3</sub>Ge<sub>0.7</sub> and

Si control sample. Gate capacitors were formed after a 3000Å poly-Si deposition and subsequent patterning.

## 三、結論與討論

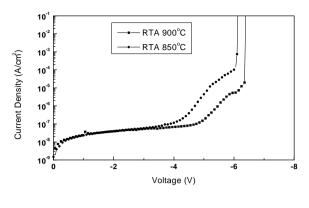

Fig. 1 shows I-V characteristics of thermal oxides grown on 850 and 900°C RTA formed Si<sub>0.3</sub>Ge<sub>0.7</sub>, respectively. Note that oxide grown on 850 °C RTA SiGe has lower breakdown electric field as compared to that grown on 900 °C SiGe. The degraded oxide property as decreasing SiGe formation temperature may be due to either strain relaxation or higher defect density by lower temperature. However, formation mechanism may be a fundamental limitation of gate oxide integrity using low temperature MBE or CVD grown SiGe. A breakdown electric field of 11 MV/cm is obtained from thermal oxide grown on 900 °C formed SiGe that is still lower than conventional SiO<sub>2</sub>. Possible reason may be due to the presence of weaker GeO2 inside the SiO<sub>2</sub> matrix as\_confirmed by SIMS measurement and similar to literature report [18]. However, the Ge peak decreases by an order of magnitude within 10Å from interface and most part of this oxide is primarily SiO<sub>2</sub> form.

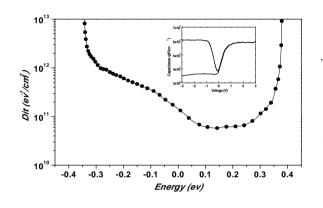

Oxide charge and interface trap density is other important factors for gate oxide integrity, which are directly related to low frequency device noise [19]. Fig. 2 shows the interface-trap density obtained from the insert C-V curves. A substrate doping concentration of ~5x10<sup>15</sup>cm<sup>-3</sup> is extracted from C-V measurement that is consistent with the measured sheet resistivity on this wafer. A low interface-trap density of 5.9 x 10<sup>10</sup> eV<sup>-1</sup>cm<sup>-2</sup> and a oxide charge density of -5.6 x 10<sup>10</sup> cm<sup>-2</sup> are obtained that are the lowest reported values on direct thermally oxidized SiGe. The low concentration of oxide traps further explains the measured high interface hole mobility and current drive capability reported previously [17]. The negative oxide charge is believed to be due to the electron traps formed in SiGe oxide.

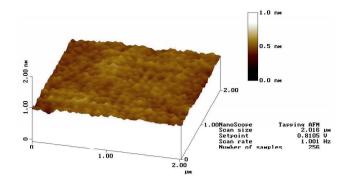

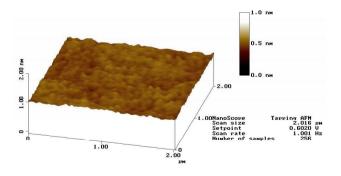

To further understand the low oxide traps, we have also measured the surface roughness using atomic force microscopy (AFM). Figs. 3(a) and (b) show the AFM images of Si<sub>0.3</sub>Ge<sub>0.7</sub> surface before and after oxidation, respectively. RMS roughness values of 1.55 and 1.60Å are measured on respective Si<sub>0.3</sub>Ge<sub>0.7</sub> surface and oxide that indicates the oxidation process did not

roughen the initial SiGe surface. It is also important to notice that the surface smoothness of Si<sub>0.3</sub>Ge<sub>0.7</sub> is comparable to standard Si surface. The smooth Si<sub>0.3</sub>Ge<sub>0.7</sub> surface may be due to the similar solid phase epitaxy as CoSi<sub>2</sub> formation [16]. In contrast to previous reports, no rough surface or pinholes are observed even for a high Ge composition up to 70% [9]-[11]. This may be due to the high temperature formed Si<sub>0.3</sub>Ge<sub>0.7</sub> that is already strained relaxed as confirmed by the very sharp XRD linewidth after oxidation with near identical peak position and linewidth to as formed Si<sub>0.3</sub>Ge<sub>0.7</sub>.

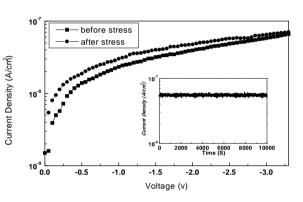

Reliability is another important issue for practical process integration of SiGe gate oxide. We have also investigated the reliability using a constant voltage stress. Fig. 4 shows the SILC effect from the insert figure after a -3.3V stress for 10,000s. The small SILC indicates excellent gate oxide reliability that is attributed to the smooth oxide surface and related uniform electric field distribution over oxide area [3]. The good reliability also suggests that the high temperature strain relaxed and stable Si<sub>0.3</sub>Ge<sub>0.7</sub> is the essential factor to achieve good oxide integrity.

Good oxide integrity is obtained from direct thermally oxidized  $Si_{0.3}Ge_{0.7}$ . This is evidenced by low oxide-trap density, smooth surface, and small SILC. The good gate oxide integrity is due to the high temperature formed and strain-relaxed  $Si_{0.3}Ge_{0.7}$  that has a very smooth surface and stable after subsequent high temperature process.

#### 四、參考文獻

- [1] J. Ahn, W. Ting, T. Chu, S. Lin, and D. L. Kwong, "High quality thin gate oxide prepared by annealing low-pressure chemical vapor deposited SiO<sub>2</sub> in N<sub>2</sub>O," *Appl. Phys. Lett.*, vol. 59, no. 3, pp. 283-285, 1991.

- [2] C. T. Liu, Y. Ma, J. Becerro, S. Nakahara, D J. Eaglesham, and S. J. Hillenius, "Light nitrogen implant for preparing thin-gate oxides," *IEEE Electron Device Lett.*, vol. 18, no 3, pp. 105-107, 1997.

- [3] A. Chin, B. C. Lin, W. J. Chen, Y. B. Lin, and C. Tsai, "The Effect of Native oxide on Thin Gate Oxide Integrity," IEEE Electron Device Lett., vol. 19, no. 11, pp. 426-428 (1998).

- [4] S. Mahapatra, V. R. Rao, K. N. ManjulaRani, C. D. Parikh, J. Vasi, B. Cheng, M. Khare, and J. C. S. Woo, "100nm channel length MNSFET using a jet vapor deposited ultra-thin silicon nitride gate dielectric," in *Symp. on VLSI Tech.*, 1999, pp. 79-80.

- [5] D. K. Nayak, K. Kamjoo, J. S. Park, J. C. S. Woo, and K. L. Wang, "Wet oxidation of GeSi strained layers by rapid thermal processing," *Appl. Phys. Lett.*, vol. 57, no. 23, pp. 369-371, 1990.

- [6] P. W. Li, E. S. Yang, Y. F. Yang, J. O. Chu, and B. S. Meyson, "SiGe pMOSFET's with gate oxide fabricated by microwave electron cyclotron resonance plasma processing," *IEEE Electron Device Lett.*, vol. 15, no. 10, pp. 402-405, 1994.

- [7] M. A. Armstrong, D. A. Antoniadis, A. Sadek, K. Ismail, and F. Stern, "Design of Si/SiGe heterojunction complementary metal-oxide-semiconductor transistors," in *IEDM Tech. Dig.*, 1995, pp. 761-764.

- [8] G. Ternent, A. Asenov, I. G. Thayne, D. S. MacIntyre, S. Thoms, C. D. W. Wilkinson, E. H. C. Parker, and A. M. Gundlach, "SiGe p-channel MOSFETs with tungsten gate," *Electron Lett.*, vol. 35, no. 5, pp. 430-431, 1999.

- [9] S. Verdonckt-Vandebroek, E. F. Crabbe, B. S. Meyerson, D. L. Harame, P. J. Restle, J. M. C. Stork, and J. B. Johnson, "SiGe-channel heterojunction p-MOSFET's," *IEEE Trans. Electron Devices*, vol. 41, no. 1, pp. 90-101, 1994.

- [10] R. S. Prassad, T. J. Thornton, S. Kanjanachuchai, J. Fernandez, and A. Matsumura, "Mobility degradation in gated Si:SiGe quantum wells with thermally grown oxide," *Electron Lett.*, vol. 31, no. 21, pp. 1876-1878, 1995.

- [11] K. Goto, J. Murota, T. Maeda, R. Schutz, K. Aizawa, R. Kircher, K. Yokoo, and S. Ono, "Fabrication of a Si<sub>1-x</sub>Ge<sub>x</sub> channel metal-oxide-semiconductor field-effect transistor (MOSFET) containing high Ge fraction layer by low-pressure chemical vapor deposition," Jpn. J. Appl. Phys., vol. 32, no. 1B, pp. 438-441, 1993.

- [12] Y. Taur and T. K. Ning, Fundamental Modern VLSI Devices, (1998) p. 286.

- [13] S. C. Song, H. F. Luan, C. H. Lee, A. Y. Mao, S. J. Lee, J. Gelpey, S. Marcus, and D. L. Kwong, "Ultra thin high quality stack

- nitride/oxide gate dielectrics prepared by *insitu* rapid thermal N<sub>2</sub>O oxidation of NH<sub>3</sub>-nitrided Si," in *Symp. on VLSI Tech.*,1999, p.137-138.

- [14] Albert Chin C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and reliability of high-K Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in *Symp. on VLSI Tech.*, 1999, p.135-136.

- [15] Y. H. Wu, W. J. Chen, A. Chin, and C. Tsai, "The effect of native oxide on epitaxial SiGe from deposited amorphous Ge on Si," Appl. Phys. Lett., vol. 74, no. 4, 528-530 (1999).

- [16] Y. H. Wu, W. J. Chen, S. L. Chang, A. Chin, S. Gwo, and C. Tsai, "Improved Electrical characteristics of CoSi<sub>2</sub> Using HF-Vapor Pretreatment," IEEE Electron Device Lett., vol. 20, no. 5, pp. 200-202 (1999).

- [17] Y. H. Wu, W. J. Chen, A. Chin, and C. Tsai, "Electrical and structure characterization of single crystalline SiGe formed by Ge deposition and RTP," in 41<sup>st</sup> Electronic Materials Conf., 1999, Santa Barbara, CA.

- [18] H. K. Liou, P. Mei, U. Gennser, and E. S. Yang, "Effect of Ge concentration on SiGe oxidation behavior," *Appl. Phys. Lett.*, vol. 10, no. 9, pp. 1200-1202, 1991.

- [19] H. Kimijima, T. Ohguro, B. Evans, B. Acker, J. Bloom, H. Mabuchi, D. L. Kwong, E. Morifuji, T. Yoshitomi, H. S. Momose, M. Kinugawa, Y. Katsumata, and H. Iwai, "Improvement of 1/f noise by using VHP (vertical high pressure) oxynitride gate insulator for deep-sub micron RF and analog CMOS," in *Symp. on VLSI Tech.*,1999, p.119-120.

# **Figure Captions:**

- Fig. 1.I-V characteristics of 50Å thermal oxides grown on 850 and 900°C RTA formed Si<sub>0.3</sub>Ge<sub>0.7</sub>.

- Fig. 2. Interface-trap density of 50Å thermal oxide as a function of energy obtained from the insert quasi-static and high frequency C-V curves.

- Fig. 3. AFM images of 50Å thermal oxide grown on Si<sub>0.3</sub>Ge<sub>0.7</sub> surface (a) before and (b) after oxidation.

- Fig. 4. SILC effect after -3.3V stress for 10,000s on 50Å thermal oxide grown on Si<sub>0.3</sub>Ge<sub>0.7</sub>. The insert figure is the current density during the stress.

Fig. (1)

Fig. 3 (b)

Fig. (2)

Fig. (4)

Fig 3 (a)