## Pi-shape gate polycrystalline silicon thin-film transistor for nonvolatile memory applications

Shih-Ching Chen, Ting-Chang Chang, Po-Tsun Liu, Yung-Chun Wu, Chin-Cheng Ko, Sidney Yang, Li-Wei Feng, S. M. Sze, Chun-Yen Chang, and Chen-Hsin Lien

Citation: Applied Physics Letters 91, 213101 (2007); doi: 10.1063/1.2813621

View online: http://dx.doi.org/10.1063/1.2813621

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/91/21?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Gate-all-around polycrystalline-silicon thin-film transistors with self-aligned grain-growth nanowire channels Appl. Phys. Lett. **100**, 093501 (2012); 10.1063/1.3691184

High-performance gate-all-around polycrystalline silicon nanowire with silicon nanocrystals nonvolatile memory Appl. Phys. Lett. **98**, 162108 (2011); 10.1063/1.3582925

Two-bit effect of trigate nanowires polycrystalline silicon thin-film-transistor nonvolatile memory with oxide/nitride/oxide gate dielectrics

Appl. Phys. Lett. 92, 163506 (2008); 10.1063/1.2910460

Nonvolatile polycrystalline silicon thin-film-transistor memory with oxide/nitride/oxide stack gate dielectrics and nanowire channels

Appl. Phys. Lett. 90, 122111 (2007); 10.1063/1.2715443

High-performance polycrystalline silicon thin-film transistor with multiple nanowire channels and lightly doped drain structure

Appl. Phys. Lett. 84, 3822 (2004); 10.1063/1.1745104

# Pi-shape gate polycrystalline silicon thin-film transistor for nonvolatile memory applications

## Shih-Ching Chen

Department of Physics, National Sun Yat-Sen University, Kaohsiung, 804 Taiwan, Republic of China

## Ting-Chang Chang<sup>a)</sup>

Department of Physics and Institute of Electro-Optical Engineering and Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung, 804 Taiwan, Republic of China

#### Po-Tsun Liu

Department of Photonics and Display Institute, National Chiao Tung University, Hsin-Chu, 300 Taiwan, Republic of China

## Yung-Chun Wu

Department of Engineering and System Science, National Tsing-Hua University, Hsin-Chu, 300 Taiwan, Republic of China

## Chin-Cheng Ko and Sidney Yang

Institute Photonics of Technologies, National Tsing-Hua University, Hsin-Chu, 300 Taiwan, Republic of China

## Li-Wei Feng, S. M. Sze, and Chun-Yen Chang

Institute of Electronics, National Chiao Tung University, Hsin-Chu, 300 Taiwan, Republic of China

#### Chen-Hsin Lien

Institute of Electronics Engineering, National Tsing Hua University, Hsin-Chu, 300 Taiwan, Republic of China

(Received 28 August 2007; accepted 26 October 2007; published online 19 November 2007)

In this work, we studied a pi-shape gate polycrystalline silicon thin-film transistor (poly-Si TFT) with silicon-oxide-nitride-oxide-silicon (SONOS) layers and nanowire channels for the application of electric driver and nonvolatile memory. The proposed pi-gate TFT-SONOS has superior transfer characteristics and its output characteristic also exhibits the high driving current and the suppression of the kink effect. For memory application, the device can provide high program/erase efficiency and large threshold voltage shift under adequate bias operation. The enhanced performance for the pi-gate TFT-SONOS is attributed to the larger effective channel width and the number of channel corners. © 2007 American Institute of Physics. [DOI: 10.1063/1.2813621]

In recent years, polycrystalline silicon thin-film transistors (poly-Si TFTs) have attracted much attention for activematrix liquid crystal displays since they can be integrated on display panel as peripheral driving circuits. In addition, the further improvement of poly-Si TFT's performance can enable various functional devices, such as memory and controller, to be integrated on a glass panel to achieve system-onpanel (SOP) display.<sup>2,3</sup> Because SOP technology is primarily used for portable electronics, low power consumption is basically required to maintain a long battery life. It is well known that the nonvolatile memory is widely utilized for data storage in portable electronics system due to its properties of low-power consumption and nonvolatility. Compared with the conventional nonvolatile floating gate memory, silicon-oxide-nitride-oxide-silicon (SONOS)-type memory has become a promising candidate for SOP application due to its full compatibility with poly-Si TFTs process. Recently, various approaches have been proposed for poly-TFTs combined with nonvolatile SONOS memory (TFT-SONOS) on SOP applications.<sup>4,5</sup> In our previous study,<sup>6</sup> the TFT-SONOS with nanowire channels was demonstrated to exhibit superior

However, in complementary metal-oxide semiconductor technology, high performance nonplanar multiple-gate structures in silicon-on-insulator (metal-oxide-semiconductor field-effect transistor), such as double-gate, trigate, pi-gate, and gate-all-around structures, have been reported to present greater gate control over channel than a conventional single-gate structure device. Different from the double-gate or gate-all-around devices, the pi-gate device can be easily manufactured and also exhibits excellent electric characteristics. Thus, in this paper, we propose the nanowire TFT-SONOS with pi-shape gate structure to enhance electric performance for the applications of transistor and high program/erase speed nonvolatile memory.

In this work, the pi-gate structure was formed on nanowire poly-Si channels (PN) with a buried oxide overetching. In addition, a series of standard TFT-SONOS memories without the implementation of buffer oxide overetching were also fabricated for comparison. These standard TFT-SONOS memory devices were marked as SN with ten strips of multiple 65 nm nanowire, S5 with five strips of multiple 0.2  $\mu$ m channels, S2 with two strips of multiple 0.5  $\mu$ m channels, and S1 with a single 1  $\mu$ m of channel in width. The gate length of devices is kept 5  $\mu$ m. First, an undoped 45 nm

electrical performance for transistor and memory device due to good gate controllability.

a) Electronic mail: tcchang@mail.phys.nsysu.edu.tw

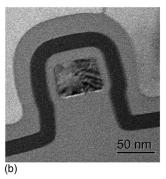

FIG. 1. Transmission electron microscopy of (a) the standard nanowire and (b) nanowire surrounded by pi-gate structures.

amorphous silicon (a-Si) was deposited on oxidized silicon wafers by low-pressure chemical vapor deposition (LPCVD) at 550 °C. Then, the deposited a-Si layer was recrystallized by solid-phase crystallization method at 600 °C for 24 h. After the active region patterning by electron beam lithography, for the pi-gate structure, the active layer and buried oxide were etched subsequently by reactive ion etching. The additional buried oxide overetching step can assure the vertical gate electrode extend over the bottom of nanowire. After the active region definition, an ONO multilayer gate dielectric with 15 nm tunnel oxide/20 nm silicon nitride/25 nm blocking oxide was deposited by LPCVD. Subsequently, a 150-nm-thick in situ  $n^+$  doped poly-Si layer was deposited and transferred to a gate electrode. After the formation of source/drain with self-aligned phosphorous implantation, a 300 nm oxide passivation layer was deposited and contact holes were patterned. Finally, Al metallization performed and the devices were sintered at 400 °C in nitrogen ambient for 30 min.

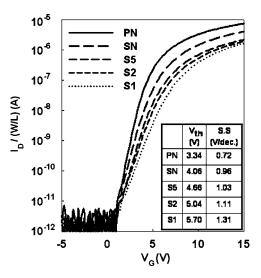

Figures 1(a) and 1(b) show the transmission electron microscope photography of the standard nanowire structure and pi-gate structure. Obviously, in pi-gate device, the nanowire channel is surrounded by the control gate and the gate electrode extends to 20 nm in depth into the buried oxide. In addition to the top and two sides channel regions, the bottom channel and two additional corner regions also can be controlled by the extended gate electrode. The physical width of nanowire channel and the thickness of ONO are also confirmed to be 65 and 60 nm, respectively. Figure 2 presents the typical  $I_D$ - $V_G$  curves of the PN and the standard devices with different channel width structures. The threshold voltages and subthreshold swing (SS) are also extracted in the insert tables. The result reveals that the PN device has superior performance than those of other devices, exhibiting the highest on-current, smallest threshold voltage  $(V_{th})$  and SS. For the standard devices, the electrical characteristics are improved as the channel width decreased. The gate fringing field crowding at the channel surface and corner regions can induce a larger electrical field as the channel width is scaling down. Hence, the standard devices with the decreased width will obtain the better gate control ability. For the PN device, compared to the SN device, the electrical performance is enhanced further due to the effective channel width and corner numbers are increased. In addition, the corner current can provide most of the total current as the device operated in subthreshold region.<sup>8</sup> The pi-gate device has most corner numbers, thus, it has the best subthreshold behavior.

FIG. 2. Comparison of typical  $I_D$ - $V_G$  characteristics of the pi-gate TFT-SONOS and the standard TFT-SONOSs with different channel width. The threshold voltages and SS of all devices are also extracted in the inset tables.

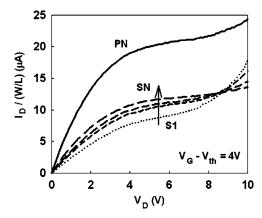

Figure 3 shows the typical output characteristics of standard and pi-gate devices. By comparing with all devices in this work, the pi-gate device has the highest driving current due to the larger effective channel width. Moreover, due to the presence of the abundant grain boundary trap states in poly-Si film, the conventional device will suffer from severe impact ionization, which causes the pronounced kink effect at high drain bias  $(V_D)$ . It is clearly found that the drain current becomes larger and the kink effect is less pronounced as the channel width is decreased. This result implies the device with narrower width can provide a better gate control ability to shield the electric field lines from the drain. The horizontal electrical field is thereby reduced and the output characteristic is improved. It is well known that the impactionization rate is also related to the current density. Hence, in pi-gate device, the increased current contributes to impactionization effect and results in the slightly kink effect.

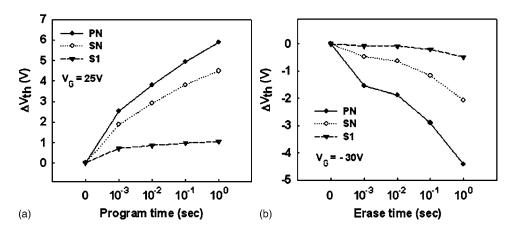

In addition to transistor application, the TFT-SONOS also can be functioned as a nonvolatile memory under adequate gate voltage operation. Tunneling current is mainly dominated by Fowler-Nordheim (FN) tunneling as the thickness of tunneling oxide is thicker than 5 nm. <sup>11</sup> In this work, therefore, the devices could be programed and erased by FN tunneling mechanism. Figures 4(a) and 4(b) show the programing and erasing characteristics of the S1, SN, and PN

FIG. 3. Output characteristics of the pi-gate TFT-SONOS and the standard TFT-SONOSs at  $(V_G - V_{th}) = 4 \text{ V}$ .

FIG. 4. (a) Programing and (b) erasing characteristics of the S1, SN, and PN devices. The devices with nanowire channels show that  $V_{\rm th}$  shift significantly increases comparing to S1 device.

devices. In general, for FN tunneling mechanism, the electrical field required for an apparent tunneling current is around 6 MV/cm. The effective oxide thickness of the stacked ONO multilayer is about 50 nm in this work. Thus, the program/erase efficiency of S1 device is very low even at the gate voltages of 25 and -30 V. However, for SN and PN devices, the electrical field at the corner region is much higher than that at noncorner region due to the corner effect. The results also reveal that the electrons mainly tunneled via the corner region and then were stored in nitride layer. Because there are four corners around the nanowire for pi-gate structure, the PN device has the superior program/erase efficiency and the larger threshold voltage shift comparing the SN device.

In summary, the pi-gate TFT-SONOS functioned as both transistor and nonvolatile memory is demonstrated in this work. The experimental results show that the pi-gate SONOS-TFT has the superior electrical characteristics due to the increased effective channel width and additional corner current induced by corner effect. In addition, the proposed device also exhibits memory characteristics with high program/erase speed under adequate bias operation (>20 or <-20 V). Thus, pixel transistor in display area and functional memory circuitry in the peripheral system area can be fabricated at the same time, and the functions of TFT-SONOS can be controlled by different bias operation (for pixel transistor application, the operated gate voltage should be below the FN tunneling threshold). Although the pi-gate TFT-SONOS cannot be easily fabricated using panel maker's existing manufacturing facilities, it is still an applicable technology for system-on-panel display in the future.

This work was performed at National Nano Device Laboratory and was supported by the National Science Council of the Republic of China under Contract Nos. NSC-96-2120-M-110-001 and 95-2221-E-009-316-MY2. This work was also partially supported by MOEA Technology Development for Academia Project.

<sup>1</sup>T. Aoyama, K. Ogawa, Y. Mochizuki, and N. Konishi, IEEE Trans. Electron Devices **43**, 701 (1996).

<sup>2</sup>Y. Nakajima, Y. Teranishi, Y. Kida, and Y. Maki, in *Proceeding of SID* 2006 (SID, San Jose, CA, 2006), pp. 1185–1188.

<sup>3</sup>Y. Nakajima, Y. Kida, M. Murase, Y. Toshihiko, and Y. Maki, in *Proceeding of SID* 2004 (SID, San Jose, CA, 2004), pp. 864–867.

<sup>4</sup>Y. H. Lin, C. H. Chien, T. H. Chou, T. S. Chao, and T. F. Lei, IEEE Trans. Electron Devices **54**, 531 (2007).

<sup>5</sup>H. T. Chen, S. I. Hsieh, C. J. Lin, and Y. C. King, IEEE Electron Device Lett. **28**, 499 (2007).

<sup>6</sup>S. C. Chen, T. C. Chang, P. T. Liu, Y. C. Wu, P. H. Yeh, C. F. Weng, S. M. Sze, C. Y. Chang, and C. H. Lien, Appl. Phys. Lett. **90**, 122111 (2007).

<sup>7</sup>K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, and Y. Arimoto, IEEE Trans. Electron Devices **40**, 2326 (1993).

<sup>8</sup>B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, in *Proceeding of the VLSI Technology Symposium* (IEEE, New York, 2003), pp. 133–134.

<sup>9</sup>J. T. Park and J. P. Colinge, IEEE Trans. Electron Devices **49**, 2222 (2002)

<sup>10</sup>S. Miyamoto, S. Maegawa, S. Maeda, T. Ipposhi, H. Kuriyama, T. Nishimura, and N. Tsubouchi, IEEE Trans. Electron Devices 46, 1693 (1999).

<sup>11</sup>E. M. Vogel, K. Z. Ahmed, B. Hornung, W. K. Henson, P. K. McLarty, G. Lucovsky, J. R. Hauser, and J. J. Wortman, IEEE Trans. Electron Devices 45, 1350 (1998).

<sup>12</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Device* (Wiley, New York, 2007), p. 438.