# Work Function Tunability of Refractory Metal Nitrides by Lanthanum or Aluminum Doping for Advanced CMOS Devices

Xin Peng Wang, Student Member, IEEE, Andy Eu-Jin Lim, Hong Yu Yu, Ming-Fu Li, Senior Member, IEEE, Chi Ren, Wei-Yip Loh, Chun Xiang Zhu, Member, IEEE, Albert Chin, Senior Member, IEEE, Alastair David Trigg, Yee-Chia Yeo, Member, IEEE, Serge Biesemans, Member, IEEE, Guo-Qiang Lo, and Dim-Lee Kwong, Senior Member, IEEE

Abstract—A lanthanum (La)-doped HfN is investigated as an n-type metal gate electrode on  $\mathrm{SiO}_2$  with tunable work function. The variation of La concentration in  $(\mathrm{Hf}_x\mathrm{La}_{1-x})\mathrm{N}_y$  modulates the gate work function from 4.6 to 3.9 eV and remains stable after high-temperature annealing (900 °C to 1000 °C), which makes it suitable for n-channel MOSFET application. An ultrathin high-k dielectric layer was formed at the metal/SiO2 interface due to the  $(\mathrm{Hf}_x\mathrm{La}_{1-x})\mathrm{N}_y$  and  $\mathrm{SiO}_2$  interaction during annealing. This causes a slight reduction in the effective oxide thickness and improves the tunneling current of the gate dielectric by two to three orders. We also report the tunability of TaN with Al doping, which is suitable for a p-type metal gate work function. Based on our results, several dual-gate integration processes by incorporating lanthanum or aluminum into a refractory metal nitride for CMOS technology are proposed.

Index Terms—High-k gate dielectric, metal gate, MOSFET, work function tuning,  $(Hf_xLa_{1-x})N_u$ ,  $(Ta_xAl_{1-x})N_u$ .

Manuscript received April 16, 2007; revised July 27, 2007. This work was supported in part by AMAT under Grant R263-000-385-720 and by Singapore A\*STAR under Grant R263-000-267-305. The review of this paper was arranged by Editor M. J. Kumar.

X. P. Wang, A. E.-J. Lim, and C. Ren are with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260, and also with the Institute of Microelectronics, Singapore 117685.

H. Y. Yu and S. Biesemans are with the Interuniversity MicroElectronics Center, 3001 Leuven, Belgium.

M.-F. Li is with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260, and also with the Department of Microelectronics, Fudan University, Shanghai 201203, China (e-mail: mfli@fudan.edu.cn).

W.-Y. Loh, A. D. Trigg, and G.-Q. Lo are with the Institute of Microelectronics, Singapore 117685.

C. X. Zhu is with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260.

A. Chin is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C., and also with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260.

Y.-C. Yeo is with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260, and also with the Agency for Science, Technology, and Research (A\*STAR), Singapore.

D.-L. Kwong is with the Institute of Microelectronics, Singapore 117685, and also with the National University of Singapore, Singapore 119260.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2007.907130

#### I. Introduction

S THE devices are aggressively scaled down for A sub-45-nm CMOSFET technology nodes, the polysilicon (poly-Si) gate depletion and boron penetration problems associated with conventional doped poly-Si gates need to be addressed. The metal gate is an attractive replacement for the poly-Si gate because it eliminates both gate depletion and boron penetration problems, and provides a lower gate sheet resistance [1]. It has been reported that metal gates with work functions close to the Si conduction and valence band edges are desired for the optimal design of bulk Si n- and p-MOSFETs, respectively [2]. Refractory metal nitrides  $(MN_x)$  such as TaN, TiN, HfN, and WN have been widely studied for gate electrode application [3], [4]. They are suitable to replace the poly-Si gate because of their thermal stability, excellent scalability, and compatibility with high-k dielectrics. Unfortunately, the work functions of most  $MN_x$  materials are close to the mid-gap position of Si after high-temperature annealing [5]. Possible reasons for this include Fermi level pinning [6], [7], the reaction between metal and dielectric, or the presence of oxygen vacancies at the metal gate/dielectric interface [8], [9]. In this paper, we report the work function tunability of  $MN_x$ (TaN and HfN) by incorporating lanthanum (La) and aluminum (Al). The compatibility of this work function tuning method with conventional high-temperature source/drain annealing is also investigated. Based on our results, we further propose several dual metal gate integration processes by incorporating lanthanide and aluminum into the gate stack with a refractory metal nitride gate electrode.

#### II. EXPERIMENTAL DETAILS

(100) n- and p-doped  $(6 \times 10^{15}~{\rm cm}^{-3})$  Si substrates were used in the MOS fabrication process. After active area definition and standard RCA clean, a thermal SiO<sub>2</sub> with four thicknesses (35 Å, 55 Å, 75 Å, and 95 Å) or a sputtered HfO<sub>2</sub> (50 Å) was deposited, wherein the thicknesses were evaluated by an ellipsometer. Subsequently, either  $({\rm Hf}_x {\rm La}_{1-x}){\rm N}_y$  or  $({\rm Ta}_x {\rm Al}_{1-x}){\rm N}_y$  gate, followed by an *in situ* TaN capping layer, was deposited to complete the gate stack. The concentration of La in  $({\rm Hf}_x {\rm La}_{1-x}){\rm N}_y$  was controlled by varying the sputter

# TABLE I PROCESS FLOW FOR MOS DEVICE FABRICATION

- \* Active area definition and RCA cleaning;

- \* Thermal oxidation  ${\rm SiO_2}$  with 4 thicknesses, or  ${\sim}50$  Å PVD HfO<sub>2</sub>;

- \* 500 Å ( $Hf_xLa_{1-x}$ ) $N_y$  or ( $Ta_xAl_{1-x}$ ) $N_y$  gate reactive co-sputtering; For ( $Hf_xLa_{1-x}$ ) $N_y$  case, different La% was obtained by changing DC power for HfLa target with fixed  $Ar/N_2$  flow rate (25/5 sccm) and DC power for Hf target (200 W); For ( $Ta_xAl_{1-x}$ ) $N_y$  case, different Al% was obtained by changing DC power for Al target with fixed flow rate of  $Ar/N_2$  (25/5 sccm) and DC power for Ta target (450 W).

- \* In-situ TaN capping layer (1000 Å);

- \* Gate patterning;

- \* PMA (900°C, 950°C 30 sec or 1000°C 2 sec in N<sub>2</sub> ambient);

- \* Forming gas anneal (FGA) 30 min @420°C.

power ratio between the HfLa target and the Hf target. It is noteworthy that a HfLa target (Hf: La = 1:1, atomic concentration) instead of a La target was used for (Hf $_x$ La $_{1-x}$ )N $_y$  deposition to reduce the moisture absorption of pure La [10]. For the (Ta $_x$ Al $_{1-x}$ )N $_y$  gate, the concentration of Al was controlled by varying the power ratio between the Ta target and the Al target. Post metallization annealing (PMA) splits were conducted by rapid thermal annealing at 900 °C to 1000 °C in N $_2$  ambient to study the thermal stability of the metal gates. The detailed process flow for this work is shown in Table I. The atomic concentrations of the ternary nitride gates were determined by X-ray photoelectron spectroscopy. Quantum-mechanical effects were taken into account when simulating the measured capacitance–voltage (C–V) curves for flatband voltage (V<sub>FB</sub>) and effective oxide thickness (EOT) extraction.

## III. EXPERIMENTAL RESULTS AND DISCUSSION

# A. Lathanide (LA) Doped $MN_x$ , $(M_xLa_{1-x})N_y$ , for n-MOS

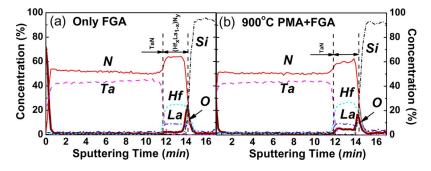

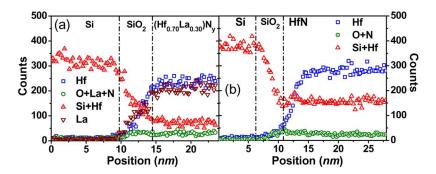

Fig. 1 shows the Auger electron spectroscopy (AES) analysis of  $(Hf_{0.70}La_{0.30})N_y$  composition in a MOS structure. There is an obvious difference in the N concentration at the TaN layer and the  $(Hf_{0.70}La_{0.30})N_y$  layer, which implies that N bonding with the HfLa alloy could be easier than that with the Ta metal. It is seen that an additional 900 °C anneal to the initial forming gas anneal (FGA) does not cause a significant change to the depth profile of the gate stack, highlighting the thermal stability of the gate stack at high annealing temperatures.

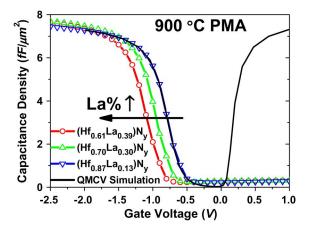

The modulation of  $V_{\rm FB}$  with varying La concentration in  $({\rm Hf}_x{\rm La}_{1-x}){\rm N}_y/{\rm SiO}_2/{\rm p}$ –Si capacitors is shown in Fig. 2. The  $V_{\rm FB}$  shifts toward the negative direction with the increase in La composition for  $({\rm Hf}_x{\rm La}_{1-x}){\rm N}_y$  gate electrodes. In addition, the excellent fit of the simulated C–V curve to the measured C–V curves confirms that the SiO $_2/{\rm Si}$  substrate interface quality was not degraded with La incorporation.

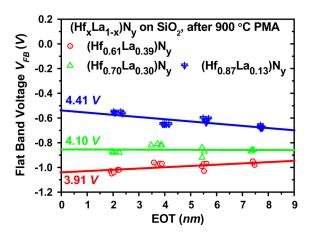

Fig. 3 shows the relationship between  $V_{\rm FB}$  and EOT, which was obtained from the C-V curves of  $({\rm Hf}_x{\rm La}_{1-x}){\rm N}_y/{\rm SiO}_2/{\rm p}$ –Si capacitors by varying the SiO $_2$  thicknesses. Based on the following equation:

$$\Phi_M = \Phi_{\rm Si} + V_{\rm FB} - \frac{Q_{\rm OX}}{C_{\rm OX}} \tag{1}$$

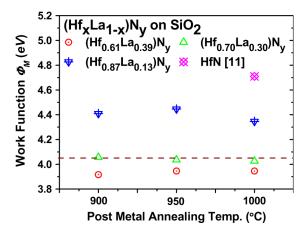

where  $\Phi_M$  and  $\Phi_{\rm Si}$  are the work functions of the metal gate and the Si substrate, respectively,  $Q_{\rm OX}$  is the equivalent oxide charge per unit area, and  $C_{\rm OX}$  is the oxide capacitance, the  $\Phi_M$ 's of  $({\rm Hf}_x{\rm La}_{1-x}){\rm N}_y$  with different La compositions were extracted and shown in Fig. 3. It can be seen that with the increase in La composition for the  $({\rm Hf}_x{\rm La}_{1-x}){\rm N}_y$  gate, the  $\Phi_M$  decreases continuously down to a value of 3.91 eV for the  $({\rm Hf}_{0.61}{\rm La}_{0.39}){\rm N}_y$  gate.

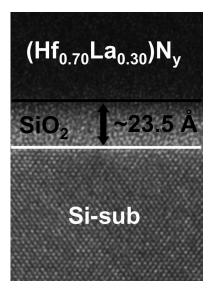

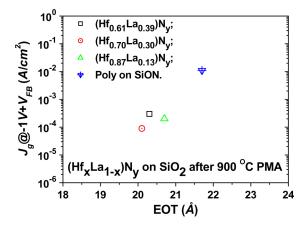

From the  $V_{\rm FB}$  versus EOT plot in Fig. 3, we found that the magnitude of  $Q_{OX}$  does not significantly change for  $(Hf_xLa_{1-x})N_y$  metal gates with different La compositions. However, the polarity of  $Q_{\rm OX}$  changes from positive to negative with increasing La composition. The extracted EOTs for all the gate stacks were also found to be thinner than the original SiO<sub>2</sub> thicknesses. Fig. 4 shows the cross-sectional transmission electron microscopy (TEM) for a (Hf<sub>0.70</sub>La<sub>0.30</sub>)N<sub>u</sub>/SiO<sub>2</sub>/Si gate stack after 900 °C 30-s PMA. It is seen that the formation of an interfacial layer occurred between the metal gate and the underlying SiO<sub>2</sub> after high-temperature anneal. In addition, the SiO<sub>2</sub> physical thickness ( $\sim$ 23.5 Å) after annealing was found to be thinner than the deposited SiO<sub>2</sub> thickness. The depth profile by energy-dispersive X-ray spectroscopy (EDX) for the same gate stack [Fig. 5(a)] shows the intermixing of La and Hf with the original SiO<sub>2</sub> layer. In contrast, Fig. 5(b) shows the HfN/SiO<sub>2</sub> gate stack, whereby no obvious Hf diffusion into the SiO2 layer was detected. Therefore, the interfacial layer formed was probably a metal silicate with a higher k value. This explains the reduction of EOT as extracted by C–Vcurves. In addition, the intermixing of La (or Hf) with SiO<sub>2</sub> may also be the root reason for the change of  $Q_{OX}$  polarity (as shown in Fig. 3) due to the introduction of negative charges in the dielectric layer. These phenomena were also observed when other lanthanide elements were incorporated into another refractory metal nitride, i.e., TaN [12]. Fig. 6 shows that La incorporation in  $(Hf_xLa_{1-x})N_y$  improves the leakage current by approximately two to three orders when compared with a conventional poly-Si/SiON stack. This was attributed to the increase in dielectric physical thickness due to the high-k layer formation (metal silicate) between the gate electrode and the SiO<sub>2</sub> layer.

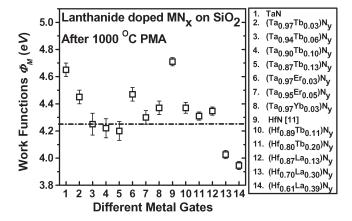

Fig. 7 summarizes the work function values of  $(Hf_xLa_{1-x})N_y$  metal gates with varying La composition under different annealing conditions. It can clearly be seen that the work function of the HfN metal gate is continuously modulated from 4.6 to 3.9 eV by changing the La composition in the  $(Hf_xLa_{1-x})N_y$  metal gate. This is stable after 900 °C to 1000 °C anneal, and the excellent thermal stability could be related to the enhanced N content in the  $(Hf_xLa_{1-x})N_y$  films. Fig. 8 compares the work function data from this paper and our previous work [13] for LA-doped refractory metal nitrides on a SiO<sub>2</sub> gate dielectric after a 1000 °C anneal. It can be seen that a wide work function tunability can be obtained by the incorporation of La into refractory metal nitride gates.

In addition to the investigation of work function tunability for  $(M_xLA_{1-x})N_y/SiO_2$  gate stacks, the work function modulation for a  $(M_xLA_{1-x})N_y/Hf$ -based high-k dielectric by lanthanide incorporation into TaN is also shown in Fig. 9.

Fig. 1. AES depth profiles of the  $TaN/(Hf_{0.70}La_{0.30})N_u/SiO_2$  gate stack. (a) FGA only. (b) 900 °C PMA for 30 s and FGA.

Fig. 2. Typical 100-kHz C-V curves of MOS capacitors with  $(\mathrm{Hf}_x\mathrm{La}_{1-x})\mathrm{N}_y$  grown on  $\mathrm{SiO}_2$  after 900 °C PMA annealing. With the increase of La% in  $(\mathrm{Hf}_x\mathrm{La}_{1-x})\mathrm{N}_y$ ,  $V_{\mathrm{FB}}$  shifts to a more negative direction.

Fig. 3.  $V_{\rm FB}$  versus EOT extracted from C--V curves for different La compositions in  $(\mathrm{Hf}_x\mathrm{La}_{1-x})\mathrm{N}_y$  metal gates after 900 °C annealing. The metal work function  $\Phi_M$  was extracted by extrapolating the line to eliminate the contribution of fixed oxide charges.

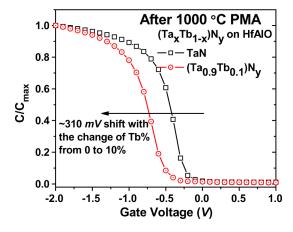

About 0.31 V  $V_{\rm FB}$  shift can be seen with the 10% Tb incorporation into TaN when using HfAlO as the gate dielectric, which is possibly due to the low bulk work function of Tb ( $\sim$ 3.1 eV). A similar work function tunability was also reported for  $(M_x L A_{1-x}) N_y / HfSiON$  gate stacks [12], which indicates the good compatibility of La-incorporated metal nitrides with high-k dielectrics.

Fig. 4. Cross-sectional TEM for  $({\rm Hf_{0.70}La_{0.30}}){\rm N_y/SiO_2/Si}$  gate stack after 900  $^{\circ}{\rm C}$  30-s PMA.

## B. Aluminum Doped $MN_x$ , $(M_xAl_{1-x})N_y$ , for p-MOS

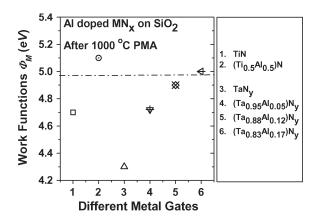

As previously reported, the doping of aluminum into  $MN_x$  could tune the work function to a p-type band edge on  $SiO_2$  dielectric [14], [15], and the key experimental results are summarized in Fig. 10. It is observed that with the increase of Al% in  $(M_xAl_{1-x})N_y$ , the work function is modulated toward the Si valence band edge and with good thermal stability up to 1000 °C.

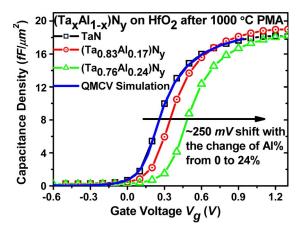

The compatibility of  $(M_xAl_{1-x})N_y$  work function tunability on a HfO<sub>2</sub> high-k dielectric is further investigated. Fig. 11 shows the typical C-V curves of  $(Ta_xAl_{1-x})N_y/HfO_2$  capacitors fitted with the simulated C-V curve. A positive  $V_{\rm FB}$  shift of  $\sim\!250$  mV was seen after 24% Al incorporation, which reflects the approximate effective work function change of the metal gate.

# C. Possible Dual Metal Gate Integration Processes for CMOS

The integration of metal gates with two different Si band edge work functions on high-k dielectrics has been a challenging task. Samavedam *et al.* reported the long channel device integration of TiN and TaSiN on HfO<sub>2</sub> [16]. The integration of TaSiN (nMOS) and Ru (pMOS) on HfO<sub>2</sub> by selectively

Fig. 5. EDX depth profile for (a)  $(Hf_{0.70}La_{0.30})N_y/SiO_2/Si$  gate stack and (b)  $HfN/SiO_2/Si$  gate stack. Intermixing of La and Hf with  $SiO_2$  was found in (a), while no Hf diffusion into  $SiO_2$  was detected in (b).

Fig. 6. Gate leakage current comparison of  $(Hf_xLa_{1-x})N_y/SiO_2$  gate stacks with poly-Si/SiON gate stack. A two- to three-order lower  $J_g$  at the same EOT was obtained for  $(Hf_xLa_{1-x})N_y/SiO_2$  gate stacks due to the formation of a high-k layer.

Fig. 7. Summary of the  $\Phi_M$  values for  $(Hf_xLa_{1-x})N_y/SiO_2$  capacitors with varying La composition under different annealing conditions. The  $\Phi_M$  of HfN can be continuously modulated from 4.6 to 3.9 eV by changing the La composition in  $(Hf_xLa_{1-x})N_y$  film.

wet etching TaSiN using a TEOS hard mask was also demonstrated [17]. However, in both schemes, the exposure of the high-k films to a series of wet chemical processes might degrade the integrity of the dielectric. Therefore, recent schemes demonstrate dual high-k and dual metal gate CMOSFETs to avoid the damage of a high-k layer during processes [18]. Here,

Fig. 8. Summary of  $\Phi_M$  for LA-doped MN $_x$  on SiO $_2$  after 1000 °C PMA. The effect of lanthanide on  $\Phi_M$  tunability is clearly seen.

Fig. 9. C-V curves of  $({\rm Ta}_x{\rm Tb}_{1-x}){\rm N}_y/{\rm HfAlO/Si}$  MOS capacitors with different Tb composition after 1000  $^{\circ}{\rm C}$  PMA. The  $V_{\rm FB}$  shift indicates the  $\Phi_M$  difference of the metal gates.

we propose several alternative integration processes for dual metal gate CMOS technology by incorporating lanthanide and aluminum into the gate stack with  $MN_x$  gate electrode. First, since the feasibility of implanting Al and other lanthanide ions has been recently demonstrated for Ni-based FUSI gate electrodes, respectively [19], [20], this would also bring the possibility to implement lanthanide and aluminum incorporation by ion implantation into a single  $MN_x$  gate electrode directly or thin  $MN_x$  layer involved in the metal-inserted poly-Si stack.

Fig. 10.  $\Phi_M$  summary for aluminum-doped MN $_x$  on SiO $_2$  after 1000  $^{\circ}$ C PMA from previous works. The effect of aluminum on  $\Phi_M$  tunability is clearly seen.

Fig. 11. C-V curves of  $({\rm Ta}_x{\rm Al}_{1-x}){\rm N}_y/{\rm HfO}_2/{\rm Si}$  MOS capacitors with different Al compositions after 1000 °C PMA.  $V_{\rm FB}$  shifts to a more positive direction with the incorporation of Al into TaN due to the  $\Phi_M$  difference among these metal gates.

In addition, the ion implantation process could be simplified by depositing the  $(M_xLa_{1-x})N_y$  [or  $(M_xAl_{1-x})N_y$ ] electrode on a whole wafer, followed by selectively implanting Al (or La) ions into the p- (or n-) MOS region. Also, the incorporation process can be implemented by previously reported technologies, such as single dielectric and dual metal gate [17] or dual dielectric and dual metal gate [18].

#### IV. CONCLUSION

In this paper, we have reported the work function tunability by incorporating lanthanum and aluminum into  $MN_x$  on both  $SiO_2$ - and  $HfO_2$ -based dielectrics with good thermal stability. Based on our results and previous data, we propose several integration processes for dual metal gate CMOS technology.

#### REFERENCES

- [1] International Technology Roadmap for Semiconductors (version 2005). [Online]. Available: http://www.itrs.net/

- [2] I. De, D. Johri, A. Śrivastava, and C. M. Osburn, "Impact of gate workfunction on device performance at the 50 nm technology node," *Solid State Electron.*, vol. 44, no. 6, pp. 1077–1080, Jun. 2000.

- [3] D.-G. Park, Z. J. Luo, N. Edleman, W. Zhu, P. Nguyen, K. Wong, C. Cabral, P. Jamison, B. H. Lee, A. Chou, M. Chudzik, J. Bruley, O. Gluschenkov, P. Ronsheim, A. Chakravarti, R. Mitchell, V. Ku, H. Kim, E. Duch, P. Kozlowski, C. D'Emic, V. Narayanan, R. Steegen, R. Wise, R. Jammy, R. Rengarajan, H. Ng, A. Sekiguchi, and C. H. Wann, "Thermally robust dual-work function ALD-MN<sub>x</sub> MOSFETs using conventional CMOS process flow," in VLSI Symp. Tech. Dig., 2004, pp. 186–187.

- [4] H. Y. Yu, J. F. Kang, J. D. Chen, C. Ren, Y. T. Hou, S. J. Whang, M.-F. Li, D. S. H. Chan, K. L. Bera, C. H. Tung, A. Du, and D.-L. Kwong, "Thermally robust high quality HfN/HfO<sub>2</sub> gate stack for advanced CMOS devices," in *IEDM Tech. Dig.*, 2003, pp. 99–102.

- [5] H. Y. Yu, C. Ren, Y.-C. Yeo, J. F. Kang, X. P. Wang, H. H. H. Ma, M.-F. Li, D. S. H. Chan, and D.-L. Kwong, "Fermi pinning induced thermal instability of metal gate work functions," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 337–339, May 2004.

- [6] S. B. Samavedam, L. B. La, P. J. Tobin, B. White, C. Hobbs, L. R. C. Fonseca, A. A. Demkov, J. Schaeffer, E. Luckowski, A. Martinez, M. Raymond, D. Triyoso, D. Roan, V. Dhandapani, R. Garcia, S. G. H. Anderson, K. Moore, H. H. Tseng, C. Capasso, O. Adetutu, D. C. Gilmer, W. J. Taylor, R. Hegde, and J. Grant, "Fermi level pinning with sub-monolayer MeOx and metal gates," in *IEDM Tech. Dig.*, 2003, pp. 13.1.1–13.1.4.

- [7] Y.-C. Yeo, T.-J. King, and C. Hu, "Metal-dielectric band alignment and its implications for metal gate complementary metal-oxide-semiconductor technology," *J. Appl. Phys.*, vol. 92, no. 12, pp. 7266–7271, Dec. 2002.

- [8] R. Jha, B. Lee, B. Chen, S. Novak, P. Majhi, and V. Misra, "Dependence of PMOS metal work functions on surface conditions of high-κ gate dielectrics," in *IEDM Tech. Dig.*, 2005, pp. 43–46.

- [9] E. Cartier, F. R. McFeely, V. Narayanan, P. Jamison, B. P. Linder, M. Copel, V. K. Paruchuri, V. S. Basker, R. Haight, D. Lim, R. Carruthers, T. Shaw, M. Steen, J. Sleight, J. Rubino, H. Deligianni, S. Guha, R. Jammy, and G. Shahidi, "Role of oxygen vacancies in V<sub>FB</sub>/V<sub>t</sub> stability of pFET metals on HfO<sub>2</sub>," in VLSI Symp. Tech. Dig., 2005, pp. 230–231.

- [10] Y. Zhao, M. Toyama, K. Kita, K. Kyuno, and A. Toriumi, "Moisture-absorption-induced permittivity deterioration and surface roughness enhancement of lanthanum oxide films on silicon," *Appl. Phys. Lett.*, vol. 88, no. 7, p. 072 904, Feb. 2003.

- [11] H. Y. Yu, H. F. Lim, J. H. Chen, M. F. Li, C. X. Zhu, C. H. Tung, A. Du, W. Wang, D. Chi, and D. L. Kwong, "Physical and electrical characteristic of HfN gate electrode for advanced MOS devices," *IEEE Electron Device Lett.*, vol. 24, no. 4, pp. 230–232, Apr. 2003.

- [12] H. R. Harris, H. Alshareef, H. C. Wen, S. Krishnan, K. Choi, H. Luan, D. Heh, C. S. Park, H. B. Park, M. Hussain, B. S. Ju, P. D. Kirsch, S. C. Song, P. Majhi, B. H. Lee, and R. Jammy, "Simplified manufacturable band edge metal gate solution for NMOS without a capping layer," in *IEDM Tech. Dig.*, 2006, pp. 1–4.

- [13] C. Ren, D. S. H. Chan, X. P. Wang, B. B. Faizhal, M.-F. Li, Y.-C. Yeo, A. D. Trigg, A. Agarwal, N. Balasubramanian, J. S. Pan, P. C. Lim, A. C. H. Huan, and D.-L. Kwong, "Physical and electrical properties of lanthanide-incorporated tantalum nitride for n-channel metal—oxide—semiconductor field-effect-transistors," *Appl. Phys. Lett.*, vol. 87, no. 7, pp. 073 506.1–073 506.3, Aug. 2005.

- [14] T.-H. Cha, D.-G. Park, T.-K. Kim, S.-A. Jang, I.-S. Yeo, J.-S. Roh, and J.-W. Park, "Work function and thermal stability of Ti<sub>1-x</sub>Al<sub>x</sub>N<sub>y</sub> for dual metal gate electrodes," *Appl. Phys. Lett.*, vol. 81, no. 22, pp. 4192–4194, Nov. 2002.

- [15] H. N. Alshareef, K. Choi, H. C. Wen, H. Luan, H. Harris, Y. Senzaki, P. Majhi, B. H. Lee, R. Jammy, S. Aguirre-Tostado, B. E. Gnade, and R. M. Wallace, "Composition dependence of the work function of Ta<sub>1-x</sub>Al<sub>x</sub>N<sub>y</sub> metal gates," *Appl. Phys. Lett.*, vol. 88, no. 7, pp. 072 108.1–072 108.3, Feb. 2006.

- [16] S. B. Samavedam, L. B. La, J. Smith, S. Dakshina-Murthy, E. Luckowski, J. Schaeffer, M. Zavala, R. Martin, V. Dhandapani, D. Triyoso, H. H. Tseng, P. J. Tobin, D. C. Gilmer, C. Hobbs, W. J. Taylor, J. M. Grant, R. I. Hegde, J. Mogab, C. Thomas, P. Abramowitz, M. Moosa, J. Conner, J. Jiang, V. Arunachalam, M. Sadd, B.-Y. Nguyen, and B. White, "Dual-metal gate CMOS with HfO<sub>2</sub> gate dielectric," in *IEDM Tech. Dig.*, 2002, pp. 433–436.

- [17] Z. B. Zhang, S. C. Song, C. Huffman, J. Barnett, N. Moumen, H. Alshareef, P. Majhi, M. Hussain, M. S. Akbar, J. H. Sim, S. H. Bae, B. Sassman, and B. H. Lee, "Integration of dual metal gate CMOS with TaSiN (NMOS) and Ru (PMOS) gate electrodes on HfO<sub>2</sub> gate dielectric," in VLSI Symp. Tech. Dig., 2005, pp. 50–51.

- [18] S. C. Song, Z. B. Zhang, M. M. Hussain, C. Huffman, J. Barnett, S. H. Bae, H. J. Li, P. Majhi, C. S. Park, B. S. Ju, H. K. Park, C. Y. Kang, R. Choi, P. Zeitzoff, H. H. Tseng, B. H. Lee, and R. Jammy, "Highly manufacturable 45 nm LSTP CMOSFETs using novel dual high-κ and dual metal gate CMOS integration," in VLSI Symp. Tech. Dig., 2006, pp. 13–14.

- [19] H. Y. Yu, J. A. Kittl, A. Lauwers, R. Singanamalla, C. Demeurisse, S. Kubicek, E. Augendre, A. Veloso, S. Brus, C. Vrancken, T. Hoffmann, S. Mertens, B. Onsia, R. Verbeeck, M. Demand, A. Rothchild, B. Froment, M. van Dal, K. De Meyer, M. F. Li, J. D. Chen, M. Jurczak, P. P. Absil, and S. Biesemans, "Demonstration of a new approach towards 0.25 V low-Vt CMOS using Ni-based FUSI," in VLSI Symp. Tech. Dig., 2006, pp. 98–99.

- [20] C. Cabral, Jr., J. Kedzierski, B. Linder, S. Zafar, V. Narayanan, S. Fang, A. Steegen, P. Kozlowski, R. Carruthers, and R. Jammy, "Dual workfunction fully silicided metal gates," in VLSI Symp. Tech. Dig., 2004, pp. 184–185.

Xin Peng Wang (S'06) received the B.Eng. and M.Eng. degrees in material science and engineering from Tsinghua University, Beijing, China, in 1999 and 2002, respectively. He is currently working toward the Ph.D. degree in the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore.

His current research interests include advanced gate stacks involving metal gates and high-k dielectrics for future CMOS application as well as their

applications in memory device technologies, such as NVM and DRAM.

**Andy Eu-Jin Lim** received the B.Eng. degree (Hons.) in electrical engineering from the National University of Singapore (NUS), Singapore, in 2004. He is currently working toward the Ph.D. degree in electrical engineering at NUS.

His current research topic focuses on the advanced gate stack technology, which includes metal gates, high-k dielectrics, and interface engineering for future CMOS applications.

Mr. Lim was the recipient of the Agency for Science, Technology and Research (A\*STAR)

Graduate Scholarship Award in 2004.

**Hong Yu Yu** received the B.Eng. degree from Tsinghua University, Beijing, China, the M.A.Sc. degree from the University of Toronto, Toronto, ON, Canada, and the Ph.D. degree from the National University of Singapore, Singapore.

Since 2004, he has been with the CMOS Device Research Department, Interuniversity Micro-Electronics Center (IMEC), Leuven, Belgium. He has authored or coauthored more than 100 papers in referred technical journals and conference proceedings in the area of semiconductor physics and

fabrication, including several invited papers. He also has approximately 15 U.S. patents published or being filed. His research interests center on frontend CMOS technologies and memory device technologies (NVM and DRAM).

**Ming-Fu** Li (M'91–SM'99) received the degree from Fudan University, Shanghai, China, in 1960.

In 1960, he was a Teaching Assistant and then a Lecturer with the University of Science and Technology of China (USTC), Hefei, China. He was with the Graduate School, Chinese Academy of Sciences, Beijing, China, in 1978 and became a Professor in 1986. He was also an Adjunct Professor with the Institute of Semiconductors, Chinese Academy of Sciences, and USTC, and Fudan University. He was a Visiting Scholar with the University of Illinois,

Urbana, from 1979 to 1981, and a Visiting Scientist with the University of California, Berkeley, from 1986 to 1987 and from 1990 to 1991. In 1991, he was with the National University of Singapore (NUS), Singapore, where he was a Professor in the Department of Electrical and Computer Engineering, and an Adjunct Senior Member of technical staff with the Institute of Microelectronics, Singapore. He is currently a Professor with the Microelectronics Department, Fudan University, and an Adjunct Professorial Fellow with NUS. He has published over 300 research papers and two books, including *Modern Semiconductor Quantum Physics* (World Scientific, 1994). His main research interests are CMOS device technology, reliability, and quantum modeling.

Prof. Li has served on several international program committees and advisory committees in semiconductor conferences in Canada, China, Germany, India, Japan, Singapore, Taiwan, China, and the U.S.

**Chi Ren** received the B.S. degree in microelectronics from Peking University, Beijing, China, in 2002 and the Ph.D. degree from the National University of Singapore, Singapore, in 2007.

In 2006, he was a Staff Engineer with the United Microelectronics Corporation, Hsinchu, Taiwan, R.O.C. He is currently with the National University of Singapore, and the Institute of Microelectronics, Singapore. He has authored or coauthored more than 20 journal and conference papers in the area of semiconductor physics and

fabrication. His research interests included metal gate electrode technology, high-k dielectric materials, and the process integration and reliability issues of sub-45-nm gate stack solutions.

**Wei-Yip Loh** received the B.Eng. and Ph.D. degrees in electrical engineering from the National University of Singapore (NUS), Singapore, in 1997 and 2004, respectively.

From 1997 to 2000, he was a Senior Engineer with the Yield Department, Chartered Semiconductor Manufacturing, Ltd., Singapore. From 2000 to 2004, he was with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, NUS, where he was engaged in the research of advanced CMOS processing and characterization

for Si-based device including quasi-breakdown, gate oxide reliability, and electrical characterization of silicon-based devices. Since 2004, he has been with the Institute of Microelectronics, A\*STAR, Singapore, where he is currently engaged in the research of Si-based CMOS devices and Si photonics. His current research interests include SiGe-based channel engineering and Schottky SD engineering for deep submicrometer CMOS devices, as well as in the fabrication and integration of Si-based photodetectors, modulators, and optical-passive devices.

Chun Xiang Zhu (S'97–M'02) received the B.Eng. and M.Eng. degrees in electrical engineering from Xidian University, Xi'an, China, in 1992 and 1995, respectively, and the Ph.D. degree in electrical engineering from The Hong Kong University of Science and Technology, Kowloon, Hong Kong, in 2001.

He is currently an Associate Professor with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore. He has authored or coauthored over 100 publications in refereed journals and conference proceedings. His

areas of research interests include high-*k* gate-stack technology on Si, Ge, and SiGe substrates for CMOS applications, high-*k* dielectrics for MIM capacitors in RF and mixed signal IC application, polysilicon thin-film transistors, and organic/polymeric electronics.

**Albert Chin** (SM'94) received the Ph.D. degree from the University of Michigan, Ann Arbor, in 1989

He was with AT&T-Bell Labs, Murray Hill, NJ, from 1989 to 1990, the Electronic Laboratory, General Electric, from 1990 to 1992, and the Semiconductor Process and Device Center, Texas Instruments Incorporated, from 1996 to 1997. He is currently a Professor with the National Chiao Tung University, Hsinchu, Taiwan, R.O.C., and a Visiting Professor with the Silicon Nano Device Laboratory,

Department of Electrical and Computer Engineering, National University of Singapore, Singapore. He has published more than 300 technical papers and presentations. His research interests include Si VLSI, RF, and III-V devices. He is a pioneer in high-k gate dielectric and metal-gate research (Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, LaAlO<sub>3</sub>, and HfLaON with NiGe, YbSi<sub>2</sub>, and Ir<sub>3</sub>Si metal gates) for low dc power consumption CMOS. He invented the Ge-on-insulator (GOI) CMOS to enhance the mobility, 3-D IC to solve the ac power consumption and able to extend the VLSI scaling, resonant cavity photodetector for high gain-bandwidth product, and high mobility strain-compensated HEMT. He is also the pioneer in high-k deep-energy trapping layer research (Al(Ga)N and HfON) for MONOS nonvolatile memory, where 100-μs-fast program/erase speed, large memory window, and good retention are simultaneously achieved at record low  $< \pm 5$  V write for SoC. The high-k TiTaO and STO MIM he developed with k = 45-150 can meet the ITRS requirement of analog capacitor to year 2018. He also developed the ion implantation method to convert VLSI-standard Si substrate into semi-insulating, where a much-improved RF device performance close to GaAs has been realized up to 100 GHz. He is currently working on quantum-trap nano MONOS memory, solar cells, highdensity MIM DRAM capacitor, metal-gate/high-k nano-CMOS, and RF Si technologies.

Dr. Chin has given invited talks at the International Electron Devices Meeting (IEDM) and other conferences in the US, Europe, Japan, Korea (Samsung Electronics), etc. He also served as a committee member in IEDM.

**Alastair David Trigg** received the B.Sc. degree from Exeter University, Exeter, U.K., in 1972 and the Ph.D. degree from London University, London, U.K., in 1978.

From 1975 to 1995, he was with the Hirst Research Centre, GEC Marconi, Wembley, U.K. From 1987 to 1990, he was the Deputy Director of the research initiative on silicon hybrids (MCMs) and subsequently became Project Leader for the manufacture of high-stability oscillators for space applications. Since 1995, he has been with the Institute of

Microelectronics, Singapore, where he has worked on infrared photoemission microscopy, surface analysis, failure analysis, and the development of MCMs. He is currently on a one-year secondment to Setsco Services, where he is helping build up their capabilities in providing analytical services for the electronics industry.

Dr. Trigg is the Chairman of the IEEE Singapore Rel/CPMT/ED Chapter. He was General Chair of the 12th and 13th International Symposia on the Physical and Failure Analysis of Integrated circuits (IPFA 2005–2006).

Yee-Chia Yeo (S'96–M'03) received the B.Eng. (First Class Honors) and M.Eng. degrees in electrical engineering from the National University of Singapore (NUS), Singapore, and the M.S. and Ph.D. degrees in electrical engineering and computer science from the University of California, Berkeley.

He had worked on optoelectronic devices at the British Telecommunications Laboratories, Ipswich, U.K., and on CMOS technology at Berkeley. In 2001–2003, he worked on exploratory transistor technologies at Taiwan Semiconductor Manufac-

turing Company (TSMC), Hsinchu, Taiwan, R.O.C. He is currently an Assistant Professor of electrical and computer engineering with NUS and a Research Program Manager with the Agency for Science, Technology, and Research (A\*STAR), Singapore. He leads research efforts in strained

transistor technologies and sub-30-nm device work at NUS, and manages a Nanoelectronics Research Program at  $A^*STAR$ . He has authored or coauthored more than 180 journals and conference proceedings, and a book chapter. He has 56 U.S. Patents.

Dr. Yeo served on the International Electron Devices Meeting subcommittee on CMOS devices in 2005–2006. He received the 1995 IEE Prize from the Institution of Electrical Engineers, U.K., the 1996 Lee Kuan Yew Gold Medal, the 1996 Institution of Engineers Singapore Gold Medal, 1997–2001 NUS Overseas Graduate Scholarship Award, the 2001 IEEE Electron Devices Society Graduate Student Fellowship Award, the 2002 IEEE Paul Rappaport Award, and 2003 TSMC Invention Awards. In 2006, he received the Singapore Young Scientist Award and the Singapore Youth Award in Science and Technology.

**Serge Biesemans** (S'96–A'98–M'04) received the Ph.D. degree from the Interuniversity MicroElectronics Center (IMEC), Leuven, Belgium, in 1998. His Ph.D. thesis was in the field of scaling CMOS devices to the sub-100-nm regime.

In 1998, he was with the IBM Microelectronics Division, East Fishkill, NY. In 2002, he was with the IBM 300-mm Manufacturing Organization. Since 2003, he has been the Director of the CMOS Technology R&D Group, IMEC, where he is responsible for the integration of emerging technologies for the 45-nm node and beyond.

**Guo-Qiang Lo** received the M.S. and Ph.D. degrees from the University of Texas, Austin, in 1989 and 1992, respectively, both in electrical and computer engineering.

He was with the Integrated Device Technology, Inc., both in San Jose, CA and Hillsboro, OR, where worked on Si semiconductor manufacturing areas in process and integration module research and development. Since 2004, he has been with the Institute of Microelectronics, Singapore. He has authored or coauthored more than 50 peer-reviewed journal and

conferences proceedings, and more than 15 granted patents. His interests are in novel semiconductor device and integration technology.

**Dim-Lee Kwong** (A'84–SM'90) received the B.S. degree in physics and the M.S. degree in nuclear engineering from the National Tsing Hua University, Taipei, Taiwan, R.O.C., in 1977 and 1979, respectively, and the Ph.D. degree in electrical engineering, with a Best Dissertation Award, from Rice University, Houston, TX, in 1982.

He was a Professor of electrical and computer engineering with the Microelectronics Research Center, University of Texas, Austin, from 1984 to 2006. He is currently the Executive Director of Institute of

Microelectronics (IME), Singapore, and a Professor of electrical and computer engineering with the National University of Singapore, Singapore. He is the author of more than 440 referred archival journals and 360 referred archival conference proceedings publications, has presented more than 60 invited talks at international conferences, and is the holder of more than 25 U.S. patents. He founded Rapro Technology in 1986 and the Micro Integration Corporation in 1988. He has been a consultant to semiconductor IC manufacturers, and materials and equipment suppliers in the U.S. and overseas. His current areas of research interests include Si narrow-wire-based CMOS nanodevices and applications, Si-based ultrasensitive biosensors and lab-on-chip, and Si microand nanophotonics technology. More than 52 students received their Ph.D. degrees under his supervision. As Executive Director of IME, he develops and implements IME's multidisciplinary and multifaceted R&D strategy and research programs, which are substantially driven by commercial applications as the end goal. He leads interdisciplinary teams of semiconductor processing, bioscience, RF and mixed-signal IC design, and advanced packaging/SiP technologies, together with strategic industrial partners, to develop leadingedge disruptive technologies for photonics, nanoelectronics, and bioelectronics applications.