# 行政院國家科學委員會補助專題研究計畫成果報告

創新微型呼拉圈式換能器設計與實現

子計畫三:呼拉圈式換能器之儲能電路設計與晶片實現(2/3)

計畫類別:□個別型計畫 ■整合型計畫

計畫編號: NSC 97-2221-E-009-086-MY3

執行期間: 97年08月01日至100年07月31日

計畫主持人:林錫寬 交通大學電機工程學系

計畫參與人員:邵啟意 陳緯達 交通大學電機工程學系

執行單位:國立交通大學電機工程學系

中 華 民 國 9 9 年 5 月 3 1 日

# 行政院國家科學委員會專題研究計畫成果報告

# 呼拉圈式換能器之儲能電路設計與晶片實現

#### Electronic Converter Design and Chip Implementation of a Hula Hoop Energy Harvester

計 畫 編 號: NSC 97-2221-E-009-086-MY3

執 行 期 限:98年08月01日至99年07月31日

主 持 人:林錫寬 國立交通大學電機工程學系

計畫參與人員:邵啟意 陳緯達 國立交通大學電機工程學系

## 一、 中文摘要

呼拉圈式換能器之系統轉換電路,係針 對前端微發電機所發出之微小能量加以收集 儲存,由於前端能量為週期或非週期性訊 號,因此在電路設計上必須要考量能量轉換 之匹配性,本年度已完成整體後端轉換電路 之設計、模擬,包含創新高速充電泵設計、 低壓降的穩壓器設計,並透過國家系統晶片 中心(CIC)成功下線,已完成初步量測。

關鍵字:儲能電路、低功率。

#### **Abstract**

This subproject is aimed to transform the output power of hula-hoop transducer to electrical power. This project designs a three-stage circuit which is based on high-speed charge pump, low-drop voltage regulator, and high efficient charger. This research collects the sinusoidal power which is from hundred scale of  $\mu$ W to several mW. An prototype IC was manufactured by submitting to CIC. Some experiments on the IC verified the design goal.

Keywords: energy harvesting circuit, low power

## 二、前言與目的

我們生活中的動作,像是揮手、上樓梯, 其實都可以藉由微發電機來產生電能,而要 如何將微發電機所產生的電能有效儲存起來 是我們第一個必須面對的課題。

本子計畫以設計後端儲能電路為目標, 針對前端微發電機所發出之微小能量加以收 集儲存,由於前端能量為週期或非週期性訊號,因此在電路設計上必須要考量能量轉換之匹配性,本年度已完成整體後端轉換電路之設計、模擬,包含創新高速充電泵設計等,包含創新為壓降的穩壓器設計以及充電電路設計等,於透過國家系統晶片中心(CIC)成功下線,已完成初步量測,待子計畫一、子計畫二整合完成後,搭配本子計畫所設計之儲能電路IC,整合成一創新微型高能量密度換能器。

## 三、研究成果

#### 3.1 儲能電路設計

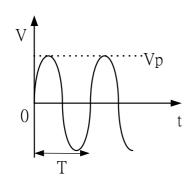

首先因應微型發電機輸出電壓與時間關 係如參考圖一所示,一般轉換能量的前端電 路是採取 dc to dc converter 的概念去收集能 量,但是若以電池輔助則電池消耗的能量也 許遠超過收集到的能量,因此考量前端換能 裝置實際輸出能量極小,約為2V以下之交流 訊號,因此採用電容式升壓結構,設計一新 型高速充電泵(Charge Pump),此電路能將輸 入微小之交流電壓訊號升壓並整流成直流訊 號,只需要一個週期即能達到升壓整流效 果,且無需外部控制訊號,相較於一般Dickson charge pump[1, 2], 此電路設計更能達到高速 低耗能之特性,接著後端設計低壓降穩壓電 路(LDO),透過此電路,降低負載效應,於後 端輸出穩定之 DC 電壓源提供給充電電路 (Battery Charger)使用,最後設計一充電電 路,將所轉換之能量儲存在電池或是大型儲

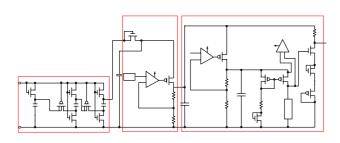

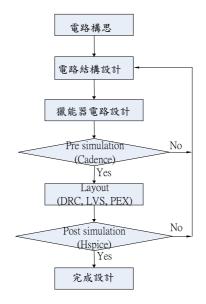

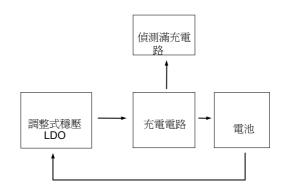

能裝置上,其整體電路如圖二所示,從一開始的整流、升壓、穩壓直到對後端儲能元件充電,皆無需外部電源供應,相較於一般 dc to dc converter 的架構[3],此種不需電池的低電壓前端轉換電路,更能達到高效率轉換,因為若以電池輔助則電池消耗的能量也許遠超過收集到的能量,整體電路設計流程如圖三所示,以下將針對各部分之電路原理以及設計做分析討論。

圖一、輸出電壓與時間關係圖

圖二、整體電路圖

圖三、設計流程圖

#### 3.2 新型高速充電泵

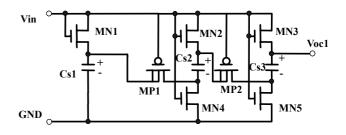

由於考慮到一般之 Dickson Charge Pump[1,2]需要外部訊號輸入,無法達成無源升壓,且需要數個週期才能升至目標電壓,因此設計無電池型的高速充電泵,其電路如圖四所示。

圖四、高速升壓充電泵

而簡單概念為:充電時對所有電容充 電,而當放電時所有電容一起放電,故可以 瞭解到此電路特性,沒有一絲能源消耗在不 該消耗的地方,所有能量皆由電容收集並由 電容輸出,沒有一個額外的電容儲存的能源 沒有應用到,故能量收集效率很高。分析步 驟如下:

第一步:當輸入訊號為 high 時,NMOS 皆導通但 PMOS 將截止如 NMOS MN1、MN2、MN3、MN4、MN5 將為"ON"狀態而 PMOS MP1、MP2 將為"OFF"狀態,故此時電容呈現並聯充電狀態所以輸入電壓將同時對所有電容充電至(Vin-V<sub>i</sub>)電壓。

第二步:之後當輸入電壓由 High 轉為 Low 的電壓時,所有 NMOS 將關閉也就是 NMOS MN1、MN2、MN3、MN4、MN5 將為"OFF" 狀態,所以沒有導通,且同時 PMOS 也因為 Gate 閘接收到 Low 的訊號所以形成導通,也就是 PMOS MP1、MP2 將為"ON"狀態,而因為 PMOS 是呈現導通狀態,所以此時電容因為變成串接形式,將電壓直接升壓出去,輸出電壓為  $3*(V_{in}-V_t)$ , 其輸出入相關公式為

$$v_{OC1} = 3\left(V_{in} - V_{t}\right) \tag{1}$$

其中  $V_{in}$  為輸入電壓  $,V_{t}$  為 MOS 之導通臨界

電壓。輸出效率公式為:

$$\eta = \frac{P_o}{P_i} = \frac{(V_{in} - V_t) \times K(V_{SG} - V_t)^2}{V_{in} \times I_{in}}$$

(2)

其中 $K(V_{SG}-V_t)^2$ 為 PMOS 輸出電流,所以我們可以由公式得知,當我們設計 PMOS 的驅動能力足以輸出與輸入電流相等時,也就是 $K(V_{SG}-V_t)^2=I_{in}$ ,則效率公式變成:

$$\eta = \frac{P_o}{P_i} = \frac{(V_{in} - V_t)}{V_{in}}$$

(3)

故當 $V_{i}\approx 0$  時,理想上可達接近 100%效率,而若當 $V_{i}=0.2$  時而輸入電壓 $V_{in}$ 為 0.8V,其效率變為 75%。

我們可以得知一開始未充電時,輸出  $V_{cs2}$ 的電壓為0 V,而當輸入為 $V_{in}$ 時,輸出馬上 被充至  $V_{\text{in}}$ - $V_{\text{t}}$  準位,之後當輸入電壓由 High 轉至 Low 時, $V_{cs2}$  輸出電壓馬上推升至  $2(V_{in}-V_t)$ ,同理  $V_{cs3}$  也被推升至  $3(V_{in}-V_t)$ 。所 以可以得到公式(1),因為所使用的 MOSFET 元件非常少所以消耗功率很少,且當充電時 為同時對電容充電,所以當中 NMOS 的 W/L 比不需逐級增大,因為驅動能力相同即可, 另一方面,當輸入電壓為 Low 時, PMOS 為 "ON"的狀態,電容串聯輸出電壓,因為電容 皆是與 PMOS 串聯形式,所以電流一樣故 PMOS 不需要逐級增加 W/L 比,所以不會因 為串接的級數增大而需逐級增加 NMOS 或 PMOS 的電流驅動能力來確保能夠推升電壓 的能力。因為一般 Dickson charge pump circuit 需要逐級增加 NMOS 的驅動能力,也就是逐 級增加 W/L 比例,所以越多的級數則面積將 越大, 所以傳統電路設計方面會有一定限制 存在,將因為串接多級升壓電路將造成效率 逐級下降,另一點是充電時間需要非常的 長,有五級則需要 5 個時間週期,但是新式 電路設計無論多少級只需要一個時間週期就 可以推升至所希望的電壓,所以以時間響應

速度來講速度遠勝於傳統 charge pump 電路,甚至效率遠超過一般傳統電路,故以積體電路設計微小化是非常具有價值性。

#### 3.3 低壓降的穩壓電路

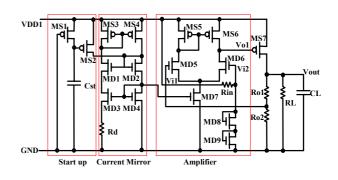

為了降低負載對前端微發電機之影響以 及提供後端穩定電壓源,設計一組低壓降的 穩壓電路,其穩壓電路如圖五所示。

圖五、LDO and regulator 電路

其設計概念為兩段式輸出,第一段為 LDO(Low Drop out),也就是輸出電壓將一直 隨著輸入電壓而變動,最主要為減低負載效 應,而第二段操作為 LDO regulator,將會穩 定輸出固定電壓而不再是隨著輸入電壓而變 動,其設計關鍵點為切換式偏壓點,所以可 以達成二段式電路操作,而第一段 LDO 可以 減輕因為接上負載後輸出電壓被降低的問 題,其設計為一 OP 接成比較器形式,負端  $V_{i2}$ 接輸入電壓而正端輸入 $V_{i1}$ 接輸出電壓 $V_{out}$ 所分壓回饋回來的電壓,一般而言,其 $R_{ol}$ 與  $R_{02}$  將設定為相同電阻如 1000k 歐姆,所以  $V_{i2}$  $= V_{i1} = V_{in} - V_{sg3} > V_{out}/2$ ,所以 OP 輸出  $V_{o1}$  永遠 呈現 Low 的準位,故 PMOS MS7 永遠啟動, 輸出電壓將幾乎等於 Vino 而其第二段概念也 為二段式控制概念的主要點也就是自動切換 為 LDO 或 LDO regulator,實際原理為當 LDO 電路啟動時輸出電壓一直持續追隨輸入電 壓,但輸入電壓若高於輸出電壓至1.8 V 所需 電壓準位時,則另外的穩壓電路將啟動,也 就是 MOSFET MD8 MD9 啟動,此時 Vi2 輸入 公式將不是  $V_{i2} = V_{i1} = V_{in} - V_{sg3}$ , 所以負端輸入

將不是極高電壓,舉例來說,假設此時負端輸入電壓  $V_{12}$  固定於一定值如 1.3 V,則當輸出電壓  $V_{out}$  為 2.6 V 時,則 OP 正端輸入  $V_{i1}$  為 1.3v,則此時  $V_{o1}$  將固定不動,而當輸出電壓越來越高時,因為比較器特性,所以正端輸入電壓  $V_{i1}$  電壓大於負端電壓  $V_{i2}$ ,故 op 輸出準位開始提昇,此時 PMOS MS7 所允許的導通電流將會因為其閘級準位提昇而減少。就是當輸出電壓變高則 OP 輸出電壓,所以PMOS 閘級電壓變高時 PMOS 導通電流便少,則輸出電壓將開始下降,呈現穩壓效果。我們可以得到其公式推導如下:當輸入電壓為 Vdd,OP 輸出電壓

$$V_{o1} = A_{v}(V_{i1} - V_{i2}) \tag{4}$$

$$V_{out} = \frac{V_{i2}}{\frac{R_{o2}}{R_{o1} + R_{o2}} - \frac{1}{A_{v}}}$$

(5)

由上式我們可以得知透過調整電阻  $R_{ol} \cdot R_{o2}$ , 所提議的穩壓電路是可行的, 而且可以穩定電壓輸出,並且不會消耗太多功率。

#### 3.4 充電電路設計

因應微型化與低耗能高效率的充電電路,提出一種新式快速充電法則,此法則特點有二:1.利用新設計的電壓補償效應使其充電路徑中 PMOS 不會因為電池電壓過高導致 PMOS 離開飽和區進入三極管區,消除其非預期的現象 2.採用偏壓調整方式故電流驅動能力比一般充電電路還強,並且在 CV(定電壓) 村民工下其電流將大於一般設計充電電流將大於一般設計充電電流將大於一般設計充電電流將大於一般設計充電電流將大於一般設計充電電流將大於一般電路在 CV 模式下充電電流機 所以相較於一般電路在 CV 模式下充電電流機 所提出的新式電路將不會有此問題,所以更可以加倍電流也就是加倍速率充電,這也是快速充電的原理之一,3.利用全類比電路設計達成最低耗電且微小電路需求。

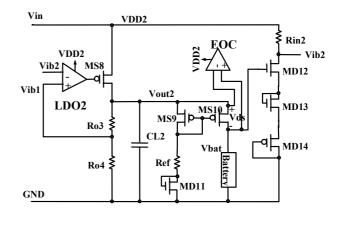

其系統架構如圖六所示,首先由調整式 穩壓LDO輸出穩定電壓至充電電路進行對電 池充電,而在充電電路方面將設計一不同以往的滿充偵測,用以微弱電流裝置來確認是否電池流經的電壓已經到達所謂的滿充額定電壓,若達滿充額定電壓則輸出 High 的訊號,若無則輸出 Low 的訊號,所以新設計的電路將有二點不同以往電路的設計準則,一為偏壓調整充電方式,二為利用公式轉換電壓電流數值達成偵測微弱電流。

圖六、充電系統架構圖

充電電路設計以電池之充電物理特性為考量,採用兩階段式充電,定電流充電以及定電壓充電,一開始電池尚未達到額定電壓,因此採用定電流充電(CC),此階段充電速度較快,用以縮短充電時間,待電池達到額定電壓之後,採用定電壓充電(CV),用以避免電池過充以及確保電池能充滿,透過兩階段充電,可以達到高速高效率充電。

圖七、充電電路圖

電路圖如圖七所示,首先電源經過LDO2 提供穩定電壓,而因為偏壓點採浮動設計, 故其輸出穩定電壓將隨著電池的電壓而有所

調整,簡單來說分為二段式,第一段尚未到 達額定電壓時,穩壓 LDO 輸出 5V 至充電器 電路使對電池充電電流極大,一般而言,普 通的充電電路輸出至充電器電路為 4.1V 定電 壓,因為採用 CC-CV 模式轉換關係,若穩壓 輸出至充電電路為5V則電池電壓有可能會過 充至5V,故一般而言將設計4.1V的鋰電池偏 壓穩壓輸出至充電器電路,但是此時在 CC-CV 模式轉換則會有相關問題,即為 CC-CV 模式切換時其曲線呈現緩慢充電,這 是因為電池電壓將因為充電時間長久而逐漸 上升,而當電壓上升至一定程度時,其充電 端電晶體 MS10,將由原本預期的操作在飽和 區提供定電流模式自然轉換為三極管區,故 此時提供電流能力將大幅下降,一般設計皆 無考慮電池電壓上升問題所造成的 PMOS 非 線性現象,故在此提出一新設計法來補償其 PMOS 非線性現象,也就是採用偏壓補償法。 此電路操作原理有二:1.定電流模式 2.定電 壓模式。假設電池電壓 Vbat 初始電壓為零,  $V_{GS} > V_t$ 且 $V_{DS} > V_{GS} - V_t$ ,此時電晶體 MS10 在 飽和區,其電流公式

$$I_d = K(V_{GS} - V_t)^2 (1 + \lambda V_{DS})$$

(6)

此時為定電流模式,而因  $I_d$ = $I_{bat}$ ,此時逐漸對電池充電,而因電池電壓上升,所以  $V_{DS}$ 電壓差逐漸減少,由飽和區電容公式,可以看出電流將成線性減少的趨勢,而因為三極管區公式條件為

$$V_{DS} < V_{GS} - V_t \tag{7}$$

且

$$V_{GS} > V_t$$

(8)

則電池電壓升到

$$V_{bat} > V_{out} - (V_{GS} - V_t) \tag{9}$$

,此時將進入三極管區,也就是電流為

$$I_{d} = K \left[ 2(V_{GS} - V_{t})V_{DS} - V_{DS}^{2} \right]$$

(10)

$$V_{ib2}$$

= $V_{DD2}$ ,所以 $V_{ib2} > V_{out2} \times \frac{Ro2}{Ro1 + Ro2}$ ,此時

前端的 LDO 電路輸出電壓為  $V_{out2}=V_{DD2}$ ,假設充電電池飽和電壓為 4.1V 而 IC 輸入電壓為 5V 則其 0.9V 電壓壓差可以確保其 PMOS 皆操作在飽和區,不會因為電池電壓上升而轉變至三極管區,而當電池電壓充電至電池飽和電壓時,此時 PMOS 與 NMOS 打開,所以此時電壓的偏壓點開始轉變,變成

$$V_{ib2} = V_{DD2} - I_{dmos} \times R_a \tag{11}$$

故此時

$$V_{ib2} < V_{out2} \times \frac{Ro2}{Ro1 + Ro2} \tag{12}$$

所以 LDO 輸出電壓開始下降至電池額定電壓 $V_{bsat}$ 。

#### 3.5 實驗結果

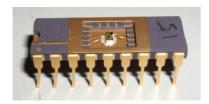

圖八為下線之 IC 實體圖,整體電路設計使用台積電 0.35u CMOS 製程,其功率消耗約 5.99uW,晶片所使用面積約 0.3025mm<sup>2</sup>。

圖八、IC 實體圖

而其測試電路如圖九所示,首先由訊號產生 器產生一交流訊號,模擬實際微發電機之輸 出訊號並輸入 IC,由示波器觀察各點之輸出 訊號,評估實際轉換效率,以及各子電路之 輸出效能。

圖九、測試電路

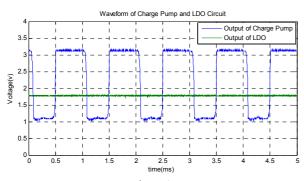

圖十所示為 Charge Pump 以及低壓降的穩壓電路實際量測輸出波形圖,由圖中可觀察出高速充電泵於電容放電階段時輸出電壓正確達到 3\* (Vin-V<sub>t</sub>),而另一方面,低壓降穩壓電路其輸出電壓為 1.8V 之 DC 電壓,能將前端輸入之不穩定訊號轉為穩定輸出,並降低後端之負載效應。

圖十、實際輸出波形圖

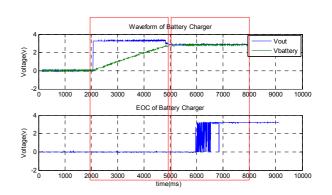

最後結合後端所設計新式高速充電電路 進行實際量測,其結果如圖十一所示。所設 計之充電電路以兩階段,定電流充電(CC)以 及定電壓充電(CV)對儲能元件進行充電,實際量測以一大電容串聯一小電阻來模擬充電電池之模型,一開始初始電位為 0 ,充電電流極大,此階段為定電流充電,其後充電電上升,直至額定電壓時,充電電壓快速轉態至額定電池面壓,此階段為定電壓充電,直至電池滿充為止,而所設計之 OP ,於電池滿充狀態時偵測並輸出高電位(EOC),由圖十一觀察得知,此電路能達到快速兩階段轉換以及正確充電之效果。

圖十一、充電電路波形圖

#### 四、結論

### 五、成果自評

已完成儲能電路之設計雛型,電路相關 公式推導,電路前模擬、後模擬、晶片設計、 佈局、下線以及量測,待前端微發電機之整 合,量測整合後之實際轉換輸出效率,以評 估整體電路之可靠性及實用性

六、參考文獻

- [1] J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," *Solid-State Circuits, IEEE Journal of,* vol. 11, pp. 374-378, 1976.

- [2] T. Tanzawa and T. Tanaka, "A dynamic analysis of the Dickson charge pump circuit," *Solid-State Circuits, IEEE Journal of,* vol. 32, pp. 1231-1240, 1997.

- [3] N. Mohan and T. Undeland, *Power electronics: converters, applications, and design*: Wiley-India, 2009.

- [4] S. Xu, et al., "Low frequency pulsed resonant converter for energy harvesting," *IEEE Transactions on Power Electronics*, vol. 22, pp. 63-68, 2007.

- [5] J. Wu and K. Chang, "MOS charge pumps for low-voltage operation," *IEEE Journal of Solid-State Circuits*, vol. 33, pp. 592-597, 1998.

- [6] M. Ker, *et al.*, "Design of charge pump circuit with consideration of gate-oxide reliability in low-voltage CMOS processes," *IEEE Journal of Solid-State Circuits*, vol. 41, pp. 1100-1107, 2006.

- [7] C. Wang and J. Wu, "Efficiency improvement in charge pump circuits," *IEEE Journal of Solid-State Circuits*, vol. 32, pp. 852-860, 1997.

- [8] C. Peters, et al., "A CMOS integrated voltage and power efficient AC/DC converter for energy harvesting applications," Journal of Micromechanics and Microengineering, vol. 18, p. 104005, 2008.

- [9] X. Cao, et al., "Electromagnetic energy harvesting circuit with feedforward and feedback DC¡VDC PWM boost converter for vibration power generator system," IEEE Transactions on Power

Electronics, vol. 22, pp. 679-685, 2007.

[10]

L. Chao, *et al.*, "A batteryless vibration-based energy harvesting system for ultra low power ubiquitous applications," 2007, pp. 1349-1352.