# BST 介電薄膜在 12 吋矽晶圓上快速熱回火製程中 熱物理性質及熱應力之研究(I)

Study on the Thermal Properties and Stresses of a 12-inch Silicon Wafer with Highdielectric BST Thin Films in Rapid Thermal Processing/Annealing (I)

計畫編號: NSC 89-2212-E-009-039

執行期限:88年8月1日至89年7月31日

整合型計畫主持人:

總計畫主持人: 林清發 國立交通大學機械系教授 子計畫主持人: 曲新生 國立交通大學機械系教授

# 中文摘要

本研究第一年主要提出一種逆向模式之數值演算法以便能計算快速熱製程(RTP)中使得晶圓上溫度均勻所需之晶圓邊緣的熱補償,進而降低過程中所產生的熱應力。考慮矽晶圓熱物理性質隨溫度而變化,並採用含未來溫度演算法的逆解熱傳方法。結果顯示,晶圓上溫度均勻所需的照射熱通量可直覺地、有效地經由此逆向模式評估計算出來。假若快速加熱系統能根據此逆向方法來動態控制晶圓上照射的熱通量,本文顯示晶圓上溫度的不均勻性將大大地降低。

由於快速熱製程的加熱光源系統只對矽晶片選擇性吸熱的特殊性,過程中改變晶圓片之輻射頻譜(例如,沈積或成長於晶片表面或背面之絕緣層或導電層),可能在晶圓上產生不均勻的溫度分佈。本研究第一年之實驗,應用 傅 氏轉 換 紅 外 線 頻 譜 儀 (FTIR)對 常溫中的矽晶圓以及具BST介電薄膜的矽晶圓,做其熱輻射性質的量測。

關鍵詞:快速熱製程,矽晶圓,溫度均勻,輻射性質

### **Abstract**

First year, a numerical inverse-modeling algorithm was developed in the present study which was able to calculate optimal edge-heat compensations on wafers sequentially during rapid thermal processing in order to obtain temperature uniformity across wafers. The temperature-dependent thermal properties of silicon and a future-time algorithm of inverse heat-transfer method are used. Our numerical results show that temperature uniformity can be efficiently achieved using inverse modeling and reveal that the thermal non-uniformity can be reduced considerably if the incident heat fluxes on the wafer can be dynamically controlled according to the results calculated by the inverse methods.

First year, measurements of spectral emissivity of silicon wafers were presented. The p-type and heavily doped silicon wafer with front side polished as well as (Ba,Sr)TiO<sub>3</sub> [BST] thin film on silicon wafer had been carried out using Bomem Michelson series MB-154 FTIR spectrometer at room temperature. The effects of BST thin film and oxide on silicon wafer were to reduce the transmittance significantly.

**Keywords**: rapid thermal processing (RTP), silicon wafer, temperature uniformity, thermal radiative properties

# 1. Introduction

As device dimension shrinks to the sub-micrometer range, reduction of thermal budget during microelectronic processing is becoming a crucial issue. Single wafer rapid thermal processing has become an alternative to the conventional furnace-based batch processing in many processes. Temperature uniformity across the wafer during all processing continues to be a main obstacle for full acceptance of RTP into manufacturing [1].

Many approaches including patterned susceptor [2] and model-based control [3-5] have been proposed for achieving temperature uniformity. Certain of these approaches rely largely on trial-and-error, which can be quite expensive and time-consuming. This study primarily deals with the determination of edge-heat compensations from heaters to eliminate radial temperature gradients across wafers [6-9] and presents an efficient way using inverse heat transfer method to determine edge-heat compensation intuitively to ensure temperature uniformity during RTP.

A change in spectral distribution of the radiative properties of the wafer is a source of temperature non-uniformity for RTP systems [10]. The details of the spectral features relevant in the design of RTP systems have been in the articles of Roozeboom [11]. The continuing development of RTP techniques requires a detailed understanding of the thermal radiative properties of semiconductor wafers. The most fundamental is the spectral emissivity. It is necessary to know the total hemispherical emissivity of the wafer to calculate the equilibrium temperature it will reach when irradiated with a given power density.

### 2. Analysis

# 2.1 Thermal Model

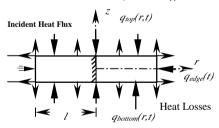

Consider the axially symmetrical wafer shown in Fig. 1. Let / and  $\nu$  be the radius and thickness, respectively.  $T_0$  is the initial temperature, and the ambient temperature is  $T_a$ . Usually, incoherent lights irradiate the wafer from both sides. The total incident heat fluxes on the top and the bottom surfaces are represented by  $q_{top}$  and  $q_{bottom}$ , respectively.  $q_{edge}$  denotes total lateral edge-heat compensations impinging on the edges. All surfaces incur radiant heat losses. The process is considered to operate in a vacuum so heat transfer due to convection can be ignored. Assume that the temperature is uniform through the wafer thickness. Thus a one-dimensional thermal model may be adopted.

The governing equation for an axially symmetric cylindrical coordinate system with its origin at the center is

$$\dots c(T) \frac{\theta T}{\theta t} = \frac{1}{r} \frac{\partial}{\partial r} \left[ k(T) r \frac{\theta T}{\theta r} \right] + \frac{1}{U} \left[ G_{top} + G_{bottom} \right], \quad 0 < r < l \ (1)$$

with

$$\begin{split} G_{lop} &= \varGamma_{lop} \; q_{lop}(r,t) - V_{lop} \; \dot{\mathcal{T}}_s(T^4 - T_a^4) \; , \\ G_{bottom} &= \varGamma_{bottom} \; q_{bottom}(r,t) - V_{bottom} \; \dot{\mathcal{T}}_s(T^4 - T_a^4) \; , \end{split}$$

where  $t_s = 5.672 \times 10^{-12} \text{ Wcm}^{-2}\text{K}^{-4}$  is the Stefan-Boltzmann constant, the temperature T is a function of radius r, and time t, and ..., k(T), c(T),  $r_{top}$ ,  $v_{top}$ ,  $r_{bottom}$ , and  $v_{bottom}$  are the density, thermal conductivity, specific heat capacity,

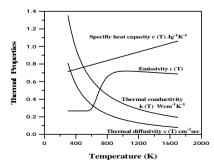

absorptivity of the top side, emissivity of the top side, absorptivity of the bottom side, and emissivity of the bottom side, respectively. Because of its large temperature variation during processing, the temperature dependence of the thermal conductivity as well as the specific heat capacity of silicon are considered as follows [1]:

considered as follows [1]:

$$k(T) = 802.99 \ T^{-1.12} \ (\text{W cm}^{-1} \ \text{K}^{-1}) \ 300\text{-}1683 \ \text{K} \ (2a)$$

$c(T) = 0.641 + 2.473 \times 10^{-4} \ T \ (\text{J g}^{-1} \ \text{K}^{-1}) \ > 300 \ \text{K} \ (2b)$

while the density is assumed to be constant and equal to 2.33 g cm<sup>-3</sup>. Since the disk is considered to be homogeneous, the dependence of k(T) on spatial position is addressed only implicitly by the spatial dependence of the temperature. Because k(T) is weakly dependent on temperature (see Fig. 2), spatial temperature variations across the disk at specific times are expected to be small enough ( $\leq 200$ K) so that spatial variations in thermal conductivity may be ignored [6]. Eq. (1) is thus reduced to

...

$$c(T) \frac{\theta T}{\theta t} = k(T) \left[ \frac{\partial^2 T}{\partial r^2} + \frac{1}{r} \frac{\theta T}{\theta r} \right] + \frac{1}{u} \left[ G_{top} + G_{bottom} \right]. \ 0 < r < l \ (3)$$

The initial and boundary conditions for the system mentioned above are

$$T(r,t) = T_0 at t = 0 (4)$$

$$\frac{\partial T}{\partial r} = 0 \qquad \text{at} \quad r = 0 \quad (5)$$

$$-k(T)\frac{\partial T}{\partial r} = r_{edge} q_{edge}(t) + v_{edge} r_s (T^4 - T_a^4), \text{ at } r = l$$

(6)

where  $r_{edge}$  and  $v_{edge}$  are the absorptivity and emissivity of the wafer edge, respectively. We may assume without loss of generality that the incident heat flux on both sides during processing are equal, i.e.  $q_{top}(r,t) = q_{bottom}(r,t) = q(r,t)$ , and that the absorptivities of all surfaces are the same as the emissivities of those surfaces. For simplicity, the emissivities of all surfaces are assumed to be the same and temperature-dependent only in as much as [12]:

ruch as [12]:

$$\Gamma_{top} = V_{top} = V_{bottom} = \Gamma_{bottom} = \Gamma_{edge} = V_{edge} = V(T)$$

$$= 0.2662 + 1.8591 T^{-0.1996} e^{\frac{1.0359 \times 10^{13}}{T^{1400}}} \qquad . (7)$$

Thus, Eqs. (3) and (6) may be written as, respectively,

$$\dots c(T)\frac{\theta T}{\theta t} = k(T) \left( \frac{\theta^2 T}{\theta r^2} + \frac{1}{r} \frac{\theta T}{\theta r} \right) + \frac{2}{u} \nu(T) \left[ q(r,t) - f_s(T^4 - T_a^4) \right]$$

0 < r < l (8)

and

$$-k(T)\frac{\partial T}{\partial r} = V(T)\left[q_{edge}(t) + f_s(T^4 - T_a^4)\right].$$

at  $r = I$  (9)

A central-difference representation of the space derivative and an implicit backward-difference representation of the time derivative are adopted. We can approximate the governing equation and the initial condition as well as the boundary conditions using  $T(r,t) = ((i-1)\Delta R, n\Delta t) = n''$ , with a p equidistant grid (the spatial coordinate increment  $\Delta R = l/p$ ) and the temporal coordinate increment  $\Delta t$ . After the nonlinear radiant fourth-power terms in Eqs. (8) and (9) have been simulated using a linear scheme and the SOR-by-lines method has been adopted, the unknowns in the subgroups to be modified simultaneously are set up such that the matrix of coefficients will be tridiagonal in form permitting use of the Thomas algorithm as follows:

$$b_{i'',i-1}^{n-n} + d_{i'',i}^{n-n} + d_{i'',i+1}^{n-n} = c_i^n.$$

(10)

The superscripts refer to the temporal grid and the subscripts

refer to the spatial grid.

#### 2.2 Inverse Heat Transfer Method

Without loss of generality, the total absorbed powers are assumed to be controlled such that the center of the wafer follows the center temperature trajectory calculated from the direct thermal model given above using uniform heat flux without any edge-heat compensation.

The finite-difference method in the thermal model above at  $f = f^m = m\Delta f$  was used to construct the following matrix equation [13]:

equation [13]:  $[F^m]_{\ell}^m = \{ e^{m-1} \} + \{ S^m \} + [V^m]_{\ell}^m \}, \qquad (11)$  where  $[F^m]$  ontains the coefficients  $a_i^m$ ,  $b_i^m$ , and  $d_i^m$  described in the thermal model above. The  $\{ S^m \}$  vector includes all known variables of the problem and the  $[V^m]$  matrix contains the coefficients for the edge-heat compensation vector  $\{ \ell^m \}$ .

The temperature distribution  $\{m''\}$  can then be derived from Eq. (11) as follows:

$$\begin{cases}

{}_{\ell}{}^{m} \} = \left[ F^{m} \right]^{-1} \left\{ \left\{ {}_{\ell}{}^{m-1} \right\} + \left\{ S^{m} \right\} \right\} + \left[ F^{m} \right]^{-1} \left[ V^{m} \right] \left\{ {}_{\ell}^{m} \right\} \\

= \left[ M^{m} \right] \left\{ \left\{ {}_{\ell}{}^{m-1} \right\} + \left\{ S^{m} \right\} \right\} + \left[ N^{m} \right] \left\{ {}_{\ell}^{m} \right\} \\

= \left[ M^{m} \right] \left\{ \left\{ {}_{\ell}{}^{m-1} \right\} + \left\{ S^{m} \right\} \right\} + \left[ N^{m} \right] \left\{ u_{\rho+1} \right\} \left\{ {}_{\rho+1}^{m} \right\} \\

\end{cases} , (12)$$

where  $[M^m] = [F^m]^{-1}$  and  $[N^m] = [F^m]^{-1}[V^m]$ . The vector  $\{p^m\}$ contains the p+1 values of the initial distribution or the temperature distribution at the preceding time step.  $\{u_{p+1}\}$  is a unit column vector with a unit at the (p+1)th component.  $f_{p+1}^m$  denotes the unknown edge-heat compensation required to achieve temperature uniformity during processing. By same means, for the next time step m+1 and at successive r future times [14],  $t = t^{m+r-1}$  we can also arrived. It was temporarily assumed that the edge-heat compensation was constant over rfuture time steps. The temperatures  $m_i^{m+k}$  at each i-spatial grid  $(i=1,2,\Lambda, p, p+1)$ for analysis interval  $k = 0, 1, 2, \Lambda$ , r-1 could then be derived [15]. Thus, we were able to construct the following matrix equation

$$\{f\}_{r(p+1)\bowtie l} = \{\Phi\}_{r(p+1)\bowtie l} f_{p+1}^m . \tag{13}$$

After the known temperature distributions were substituted into vector f, the unknown edge-heat compensation  $f_{p+1}^m$  could be found using the linear least-squares-error method. The inverse result was

$$\begin{cases} m \\ p+1 \end{cases} = (\Phi^T \Phi)^{-1} \Phi^T f .$$

(14)

### 3. Experiments

A Bomem Michelson series MB-154 FTIR spectrometer was used to collect the emission. In measuring the reflectance and transmittance of a wafer, an integrating sphere is used in the sample compartment of the FTIR system to collect all the reflecting or scattering light. For measuring transmittance, the wafer is put on the sample holder, and then locked between the incident light source and the integrating sphere. But for reflectance, the wafer is put beyond the integrating sphere. Spectra are then recorded from 1.1 to 5.5  $\mu m$  with a resolution of 4 cm $^{-1}$  resolution and in averaging of 20 scans.

# 4. Results and Discussion

## 4.1 Temperature Uniformity of Silicon Wafers during RTP

The sequential algorithms described above were employed in numerical experiments with 100-, 150-, 200- and 300-mm-diameter silicon wafers, respectively, 0.6-, 0.675-, 0.725- and 0.775 mm thick. A heating simulation from an initial

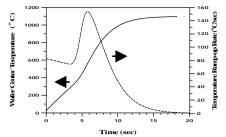

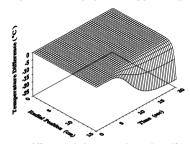

temperature of  $T_0 = 27^{\circ}\text{C}$  (300K) transitioning to a steady state of 1097°C (1370K) was demonstrated for an ambient temperature of  $T_a = 27^{\circ}\text{C}$  (300K) under a uniform incident heat flux from the kaleidoscopic light pipe of  $q(r,t) = 20 \text{ W/cm}^2$ . The center temperature and ramp-up rate of the 300-mmdiameter 0.775-mm-thick silicon wafer was calculated using the finite-difference scheme during this temperature transition without any edge-heat compensation, as shown in Fig. 3. Fig. 4 shows temperature differences across the 300-mm-diameter 0.775-mm-thick silicon wafer during this thermal processing. The greatest temperature difference during processing, 25°C occurred. Additional edge-heat compensation(s) may be required to eliminate radial temperature gradients across the wafer. The calculated temperature profile of the center shown in Fig. 3 was adopted as our desired uniform temperature track

Figs. 5(a) and 5(b) show the vertical and lateral edge-heat-compensation-scaling factor obtained from inverse method for 100-, 150-, 200- and 300-mm-diameter silicon wafer, respectively. In Fig. 5(a), the required vertical edge-heat-compensation ratios are increased from 1.0 initially to 1.60, 1.45, 1.37 and 1.26, respectively at the higher steady state periods for the 100-, 150-, 200- and 300-mm-diameter wafers. While in Fig. 5(b), the required lateral edge-heat-compensation ratios increased from zero initially to 1.0 at higher steady state periods for all four wafers.

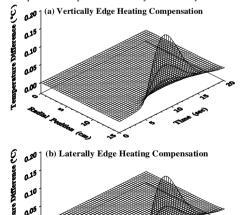

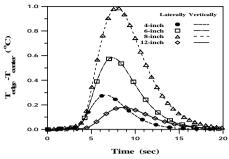

Figs. 6(a) and 6(b) show temperature difference calculated using inverse method of a 300-mm-diameter 0.775-mm-thick silicon wafer with vertical and lateral edge-heat compensation to control temperature uniformity. Comparing with Fig. 4, we see that the maximum temperature difference was reduced from 25°C to 0.178°C. Fig. 7 shows the temperature differences obtained by inverse method during thermal processing. The maximum temperature differences were 0.279, 0.583, 0.989 and 0.178°C for 100-, 150-, 200- and 300-mm-diameter silicon wafers, respectively.

## 4.2 Spectral Emissivity Measurement of Silicon Wafers

Fig. 8 show the measured results for reflectance, transmittance and emittance of 5 inches (0.78mm thickness) ptype, heavily doped silicon wafer with front side polished at room temperature in wavenumbers between 10000 and 2000 cm<sup>-</sup> <sup>1</sup>. It is found that reflectance and transmittance are always 40% and 50%, respectively, smaller than 8000 cm-1 in both wafers. So, the emittance exists only between 10000 and 8500 cm<sup>-1</sup> at room temperature. According to Sato's works [16], in the visible region, the emissivity is fairly high, since the direct and indirect of band-to-band transitions occur at this spectral region. And, at low temperatures, the wafer is transparent for the wavelengths longer than 1.2 µm (wavenumbers smaller than 8300 cm<sup>-1</sup>), hence the emissivity is very low in near infrared. Comparing to our measurement results, it reveals that the present results are principally in good agreement with the Sato's work. It also has the evidence in comparison to the measured works of a lighted n-type doped silicon wafer (polished both sides) at 30°C by Ravindra et al. (ref. in Fig. 3, [17]). Those measured reflectance, transmittance and emittance are close to our present measurement results.

High-dielectric-constant (Ba,Sr)TiO<sub>3</sub> (BST) has emerged as the preferred high permittivity thin film material for future generations of high-density Gb-scale DRAM products. The application of rapid thermal annealing (RTA) might increase the crystallinity of the BST films, which resulted in improved dielectric properties of the film [69]. Fig. 9 shows the measured results for reflectance, transmittance and emittance of 2241Å-thick (Ba $_{0.7}$ Sr $_{0.3}$ )TiO $_3$  (1433Å-thick SiO $_2$ ), thin film on silicon wafer with front side polished at room temperature in

wavenumbers between 10000 and 1000 cm<sup>-1</sup>. Comparing Fig. 9 with Fig. 8, the measured results reveal that the effects of BST thin film and oxide on silicon wafer are to reduce the transmittance significantly. It was similar to the measured works of 5124Å-thick SiO<sub>2</sub> on silicon wafer at 58°C by Ravindra et al. (ref. in Fig. 7, [17]). Those measured reflectance, transmittance and emittance for silicon wafer with thin films are close to our present measurement results.

#### References

- V. E. Borisenko, and P. J. Hesketh, Rapid Thermal Processing of Semiconductors, Plenum Press, New York, 1997.

- K.-C. Lee, H.-Y. Chang, H. Chang, J.-G. Hwu, and T.-S. Wung, The Effect of Patterned Susceptor on the Thickness Uniformity of Rapid Thermal Oxides, *IEEE Trans. Semiconduct. Manufact.*, vol. 12, pp. 340-344, 1999.

- A. Kersch, and T. Schafbauer, Thermal Modelling of RTP and RTCVD Processes, Thin Solid Films, vol. 365, pp. 307-321, 2000.

- K. S. Balakrishnan, and T. F. Edgar, Model-Based Control in Rapid Thermal Processing, *Thin Solid Films*, vol. 365, pp. 322-333, 2000.

- A. Theodoropoulou, E. Zafiriou, and R. A. Adomaitis, Inverse Model-Based Real-Time Control for Temperature Uniformity of RTCVD, *IEEE Trans. Semiconduct. Manufact.*, vol. 12, pp. 87-101, 1999.

- Manufact., vol. 12, pp. 87-101, 1999.

6. R. Kakoschke, E. Bubmann, and H. Foll, Modeling of Wafer Heating during Rapid Thermal Processing, Appl. Phys. A, vol. 50, pp. 141-150, 1990.

- F. Y. Sorrell, M. J. Fordham, and M. C. Ozturk, J.J. Wortman, Temperature Uniformity in RTP Furnaces, *IEEE Trans. Electron Devices*, vol. 39, pp. 75-79, 1992.

- R. H. Perkins, T. J. Riley, and R. S. Gyurcsik, Thermal Uniformity and Stress Minimization during Rapid Thermal Processes, *IEEE Trans. Semiconduct. Manufact.*, vol. 8, pp. 272-279, 1995.

- J. D. Stuber, I. Trachtenberg, and T. F. Edgar, Design and Modeling of Rapid Thermal Processing Systems, *IEEE Transact. Semiconduct. Manufact.*, vol. 11, pp. 442-457, 1998.

- P. J. Timans, The Role of Thermal Radiative Properties of Semiconductor Wafers in Rapid Thermal Processing, Mat. Res. Soc. Symp. Proc., vol. 429, pp.3-14, 1996.

- F. Roozeboom, in *Rapid Thermal Processing, Science and Technology* (Fair, R. B., editor), p. 349, Academic Press, New York, 1993.

- A. Virzi, Computer Modeling of Heat Transfer in Czochralski Silicon Crystal Growth, J. Cryst. Grow., vol. 112, pp. 699-722, 1991.

- K. Kurpisz, and A.J. Nowak, *Inverse Thermal Problems*, Computational Mechanics Publications. Boston, 1995.

- J. V. Beck, B. Blackwell, and C. R. St. Clair, Inverse Heat Conduction—Ill-posed Problem, Wiley, New York, 1985.

- C. Y. Yang, A Sequential Method to Estimate the Strength of the Heat Source Based on Symbolic Computation, *Int. J. Heat Mass Transfer*, vol. 41, pp. 2245-2252, 1998

- T Sato, Spectral Emissivity of Silicon, Jap. J. Appl. Phys., vol. 6, pp.339-347, 1967.

- N. M. Ravindra, S. Abedrabbo, W. Chen, F. M.. Tong, A. K. Nanda, and A. C. Speranza, Temperature-Dependent Emissivity of Silicon-Related Materials and Structures, *IEEE Trans. Semiconduct. Manufact.*, vol. 11, pp.30-39, 1998.

Fig. 1: Schematic representation of energy flux in a wafer under incident heat flux and radiant heat losses emitted from all surfaces

Fig. 2: Temperature-dependent thermal properties of silicon

Fig. 3 Center temperature and ramp-up rate during processing

Fig. 4 Temperature differences during processing under uniform heat fluxes without any edge-heat compensations

Fig. 5 (a) Vertical (b) Lateral edge-heat-compensation-scaling factor required for temperature uniformity calculated by inverse methods

Fig. 6 Temperature differences during processing with (a) vertical (b) lateral edge-heat compensations calculated by inverse methods

Fig. 7 Temperature differences between centers and edges during processing of 100-, 150-, 200- and 300-mm-diameter wafers with vertical and lateral edge-heat compensations calculated by inverse methods

Fig. 8 Measured results for reflectance, transmittance and emittance of 5 inches (0.78mm thickness) p-type, heavily doped silicon wafer with front side polished at room temperature.

Fig. 9 Measured results for reflectance, transmittance and emittance of  $2241\mbox{\normalfont\AA-thick}$  (Ba $_{0.7}Sr_{0.3})TiO_3$  (1433 $\mbox{\normalfont\AA-thick}$  SiO $_2$ ) silicon wafer with front side polished at room temperature.