# New Gate-Bias Voltage-Generating Technique With Threshold-Voltage Compensation for On-Glass Analog Circuits in LTPS Process

Jung-Sheng Chen, Student Member, IEEE, and Ming-Dou Ker, Senior Member, IEEE

Abstract—A new proposed gate-bias voltage-generating technique with threshold-voltage compensation for analog circuits in the low-temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) is proposed. The new proposed gate-bias voltage-generating circuit with threshold-voltage compensation has been successfully verified in an  $8-\mu m$  LTPS process. The experimental results have shown that the impact of TFT threshold-voltage variation on the biasing circuit can be reduced from 30% to 5% under a biasing voltage of 3 V. The new proposed gate-bias voltage-generating technique with threshold-voltage compensation enables the analog circuits to be integrated and implemented by the LTPS process on glass substrate for an active matrix LCD panel.

*Index Terms*—Analog circuit, biasing circuit, low-temperature polycrystalline silicon (LTPS), thin-film transistor (TFT), threshold-voltage compensation, threshold-voltage variation.

## I. INTRODUCTION

OW-TEMPERATURE polycrystalline silicon (LTPS) thin-film transistors (TFTs) have attracted a great deal of attention in the applications with the integrated on-panel peripheral circuits for active-matrix liquid crystal display (AMLCD) and active-matrix light-emitting diodes (AMOLEDs) [1]–[3]. Recently, LTPS AMLCDs integrated with driving and control circuits on glass substrate have been realized in some portable systems, such as mobile phones, digital cameras, and notebooks. In the near future, the AMLCD fabricated in the LTPS process is promising toward system-on-panel (SoP) or system-on-glass (SoG) applications, especially for achieving a compact, low-cost, and low-power display system [4].

The LCD data driver contains shifter registers, level shifters, digital-to-analog converters (DACs), and output buffers. The biasing circuit is a critical circuit block for analog circuits on the LCD panel to achieve low power consumption, high speed, and high resolution. However, the poly-Si TFT device suffers from significant variation in its threshold voltage, owing to the nature of crystal growth in the LTPS process. The threshold-voltage variation across a 2.7-in panel was about 300 mV [5]. The variation could even be as large as 1 V in some high-performance TFT devices across a large substrate area [6]. The threshold-

The authors are with the Nanoelectronics and Gigascale Systems Laboratory, Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: jschen@ieee.org; mdker@ieee.org).

Digital Object Identifier 10.1109/JDT.2007.900916

voltage variations of TFT devices will cause large mismatches on the biasing voltages and currents in analog circuits to result in nonuniformity of performances among analog circuits over the whole panel. The design with threshold-voltage compensation for analog circuits on glass substrate is a very important challenge for SoP applications. The design technique with switches and capacitors under multiphase clock operation were usually used to compensate for the threshold-voltage variation among TFT devices in LTPS AMLCDs [7]-[9]. Some design techniques with switch and capacitor under multiphase clock operation were used to reduce the offset voltage of the analog buffer in the LTPS process [7]. In LTPS technology, the on-panel output buffers with a pair of n-type and p-type TFT devices immune to the mismatch of threshold voltage were also reported [8], [9]. The mismatch of threshold voltage can be compensated by a holding capacitor or the mathematical product of voltage gain. Besides, the threshold-voltage-shift compensation technique was used to compensate for the threshold-voltage variation for differential amplifiers in analog circuits [10]. However, those techniques [7]–[10] only emphasize the impact of threshold-voltage variation on the offset voltage of the analog buffers on glass substrate. The biasing circuit with thresholdvoltage compensation for analog circuits in the LTPS process is not yet reported in the literature.

In this paper, a method to reduce the influence of thresholdvoltage variation on the gate-bias voltage-generating circuit for analog circuits on glass substrate is proposed. The experimental results have shown that the impact of TFT threshold-voltage variation on the biasing circuit can be reduced from 30% to 5% under a biasing voltage of 3 V. The new proposed biasing technique with threshold-voltage compensation enables the analog circuits to be integrated and implemented in the LTPS process for an AMLCD panel.

## II. IMPACT OF THRESHOLD-VOLTAGE VARIATION ON TFT *I–V* CHARACTERISTICS

In general, the TFT devices on glass substrate are usually designed in the saturation region for analog circuit applications. The small-signal gain and frequency response of analog circuits in the LTPS process are determined by transconductance  $(g_m)$ and output resistance  $(r_o)$  of TFT devices. The small-signal parameters of transconductance  $(g_m)$  and output resistance  $(r_o)$  in TFT devices can be expressed, respectively, as

$$g_m = \mu C_{\rm ox} \frac{W}{L} (V_{\rm GS} - V_{\rm TH}) = \frac{2I_D}{(V_{\rm GS} - V_{\rm TH})}$$

(1)

$$=\frac{V_A}{I_D}\tag{2}$$

$r_o$

Manuscript received November 29, 2006; revised February 14, 2007. This work was supported in part by the Chunghwa Picture Tubes (CPT), Ltd., Taiwan, R.O.C., and in part by the Ministry of Economic Affair, Technology Development Program for Academia, Taiwan, R.O.C., under Contract 95-EC-17-A-07-S1-046.

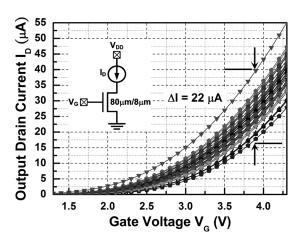

Fig. 1. Simulated waveforms of n-TFT drain current  $I_{\rm D}$  with 50% thresholdvoltage variation of Gaussian distribution under different gate voltages  $V_{\rm G}$  in an 8- $\mu$ m LTPS process.

where  $\mu$  is the mobility of carrier, L denotes the effective channel length, W is the effective channel width,  $C_{\text{ox}}$  is the gate oxide capacitance per unit area,  $V_{\text{TH}}$  is the threshold voltage of the TFT device,  $V_{\text{GS}}$  is the gate-to-source voltage of the TFT device,  $V_A$  is the Early voltage, and  $I_D$  is the drain current of the TFT device. Comparing (1) and (2), the drain current  $I_D$  is the major factor for analog circuits in the LTPS process. Therefore, the performances of analog circuits in the LTPS process are dominated by the drain current of the TFT device. The drain current  $I_D$  of the TFT device operated in the saturation region can be expressed as

$$I_{\rm D} = \frac{1}{2} \mu C_{\rm OX} \frac{W}{L} (V_{\rm GS} - V_{\rm TH})^2.$$

(3)

The channel-length modulation of the TFT device is not included in (3). The threshold voltage  $(V_{\rm TH})$  of the TFT device is an important parameter in (3), so the threshold-voltage variation among TFT devices will cause the variation on drain currents of TFT devices to degrade the circuit performances in analog circuits on glass substrate. How to design a stable biasing circuit with threshold-voltage compensation to reduce nonuniformity of performances in analog circuits over the whole panel in the LTPS process is an important design challenge.

The HSPICE with Monte Carlo analysis can be used to simulate and analyze the impact of threshold-voltage variation on drain current of the TFT device. The threshold-voltage variation of the TFT device on glass substrate can be modeled by Gaussian distribution. The simulated waveforms of n-TFT drain current  $I_D$  with 50% threshold-voltage variation of Gaussian distribution under different gate voltages  $V_G$  in an 8- $\mu$ m LTPS process is shown in Fig. 1. The dimension of n-TFT device is 8  $\mu$ m/8  $\mu$ m. The gate voltage is biased from 1.3 to 4.3 V. In order to confirm that the n-TFT device is operated in the saturation region, the drain voltage of the n-TFT device is also biased from 1.3 to 4.3 V to keep the gate-to-drain voltage of 0 V. The simulated result shows that the n-TFT device with 50% threshold-voltage variation of Gaussian distribution causes the drain current with a variation as large as 22  $\mu$ A in the LTPS

Fig. 2. Concept of the new proposed gate-bias voltage-generating technique with threshold-voltage compensation.

process. Therefore, the large variations on drain currents of TFT devices will cause large mismatches on the biasing voltages and currents in analog circuits to further result in nonuniformity of performances in analog circuits over the whole panel. For the SoP applications, reducing the impact of threshold-voltage variation on performance among analog circuits in the LTPS process is a very important design challenge.

III. NEW PROPOSED GATE-BIAS VOLTAGE-GENERATING TECHNIQUE WITH THRESHOLD-VOLTAGE COMPENSATION

#### A. Design Concept

The new proposed gate bias voltage generating technique with threshold-voltage compensation is illustrated in Fig. 2. The biasing current  $I_{D\_MC}$  is a small current used to bias the  $M_C$  device operated in weak inversion region. When the  $M_C$ device is operated in the weak inversion region, the gate control voltage  $V_{GC}$  can be written as

$$V_{\rm GC} \cong V_{\rm BIAS} + V_{\rm TH\_MC} \tag{4}$$

where  $V_{\text{TH}\_MC}$  is the threshold voltage of  $M_{\text{C}}$  device, and  $V_{\text{BIAS}}$  is the applied biasing voltage. The drain current  $I_{\text{D}\_MD}$  of  $M_{\text{D}}$  device can be expressed as

$$I_{\text{D}\_\text{MD}} = \frac{1}{2} \mu C_{\text{OX}} \left( \frac{W}{L} \right)_{\text{MD}} (V_{\text{GC}} - V_{\text{TH}\_\text{MD}})^2$$

$$= \frac{1}{2} \mu C_{\text{OX}} \left( \frac{W}{L} \right)_{\text{MD}}$$

$$\times (V_{\text{BIAS}} + V_{\text{TH}\_\text{MC}} - V_{\text{TH}\_\text{MD}})^2$$

(5)

where  $V_{\rm TH\_MD}$  is the threshold voltage of  $M_{\rm D}$  device. The  $M_{\rm C}$  and  $M_{\rm D}$  devices are drawn with the same device dimension. The threshold-voltage difference between  $M_{\rm C}$  and  $M_{\rm D}$  devices can be reduced as small as possible by symmetrical and compact layout in an adjacent location. Therefore, (5) can be further rewritten as

$$I_{\rm D\_MD} \cong \frac{1}{2} \mu C_{\rm OX} \left(\frac{W}{L}\right)_{\rm MD} (V_{\rm BIAS})^2.$$

(6)

The drain current  $I_{D_{\rm MD}}$  of  $M_{\rm D}$  device can become independent of the threshold voltage and dominated by the  $V_{\rm BLAS}$  voltage. The new proposed gate-bias voltage-generating technique with threshold-voltage compensation does not need any extra clock signal and capacitor to reduce the impact of

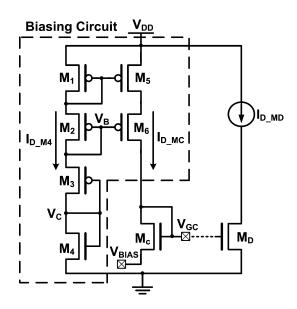

Fig. 3. Complete circuit of the proposed gate-bias voltage-generating circuit with threshold-voltage compensation for analog circuits in LTPS technology.

threshold-voltage variation on the biasing circuit for analog circuits in LTPS processes.

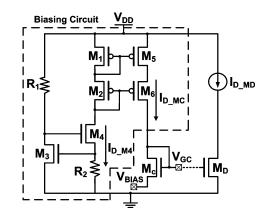

## B. Circuit Implementation

The complete circuit of the proposed gate-bias voltage-generating technique with threshold-voltage compensation for analog circuit applications in LTPS technology is shown in Fig. 3. The new proposed gate-bias voltage-generating circuit with threshold-voltage compensation is formed with  $M_1$ ,  $M_2$ ,  $M_3$ ,  $M_4$ ,  $M_5$ , and  $M_6$  devices. The  $M_1$ ,  $M_2$ ,  $M_5$ , and  $M_6$ devices form the current mirror. In order to reduce the power consumption and chip area of the new proposed gate-bias voltage-generating circuit, the  $M_3$  and  $M_4$  devices are used to realize the referenced current source. The  $M_3$  and  $M_4$  devices are operated in the saturation region to generate a biasing current through the current mirror of  $M_1$ ,  $M_2$ ,  $M_5$ , and  $M_6$ devices to bias  $M_C$  device operated in the weak inversion region. The voltage  $V_C$  can be expressed as

$$V_C = \frac{r \left( V_B - |V_{\text{TH}\_M3}| \right) + V_{\text{TH}\_M4}}{1 + r}$$

$$r = \sqrt{\frac{\mu_p \left( \frac{W}{L} \right)_{\text{M3}}}{\mu_n \left( \frac{W}{L} \right)_{\text{M4}}}}$$

(8)

where  $V_{\rm B}$  is the voltage at the source node of  $M_3$  device in proposed gate-bias generating circuit. The biasing current  $I_{\rm D_M4}$  and  $I_{\rm D_MC}$  can be written, respectively, as

$$I_{\rm D-M4} = \frac{1}{2} \mu C_{\rm OX} \left(\frac{W}{L}\right)_{\rm M4} (V_C - V_{\rm TH-M4})^2 \qquad (9)$$

$$I_{\rm D\_MC} = \left(\frac{1}{K}\right) I_{\rm D\_M1} \tag{10}$$

where the K is the dimension ratio of  $M_5$  and  $M_1$  in the current mirror. The K factor is especially designed much larger than one to reduce the impact of biasing current  $(I_{D_-M4})$  variation

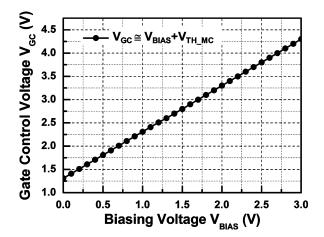

Fig. 4. Simulated gate control voltage  $V_{\rm GC}$  of the proposed gate-bias voltagegenerating circuit with threshold-voltage compensation under different biasing voltages  $V_{\rm BIAS}$ .

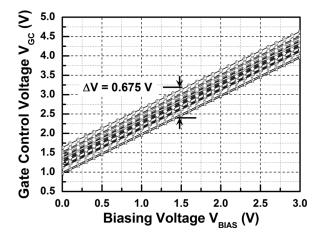

Fig. 5. Simulated gate control current  $V_{\rm GC}$  of the proposed gate-bias voltage-generating circuit with threshold-voltage compensation under the different biasing voltages  $V_{\rm BIAS}$  with the 50% threshold voltage variation (Gaussian distribution) on n-TFT and p-TFT devices.

on gate control voltage  $(V_{\rm GC})$  of the new proposed gate-bias voltage-generating circuit.

The simulated gate control voltage  $V_{GC}$  of the new proposed gate bias voltage generating circuit with threshold-voltage compensation under different biasing voltages  $V_{\text{BIAS}}$  is shown in Fig. 4. The typical threshold voltage of an n-TFT device in an 8- $\mu$ m LTPS process is approximately 1.3 V. The V<sub>BIAS</sub> voltage is biased from 0 to 3 V. The gate control voltage  $V_{\rm GC}$  is changed from 1.3 to 4.3 V. The gate control voltage  $V_{\rm GC}$  of the new proposed gate-bias voltage-generating circuit with threshold-voltage compensation is approximately  $V_{\rm BIAS} + V_{\rm TH-MC}$ . The HSPICE with Monte Carlo Analysis is used to verify the function of the new proposed gate-bias voltage-generating circuit with threshold-voltage compensation in LTPS technology. The simulated gate control current  $V_{\rm GC}$ of the new proposed gate-bias voltage-generating circuit with threshold-voltage compensation under the different biasing voltages  $V_{\text{BIAS}}$  with the 50% threshold voltage variation (Gaussian distribution) of n-TFT and p-TFT devices is shown in Fig. 5. The variation on gate control voltage  $V_{\rm GC}$ , which can be used to compensate the threshold-voltage variation of TFT

Fig. 6. Simulated drain current  $I_{D-MD}$  of the proposed gate-bias voltage-generating circuit with threshold-voltage compensation under different biasing voltages  $V_{BIAS}$  with the 50% threshold voltage variation (Gaussian distribution) of n-TFT and p-TFT devices.

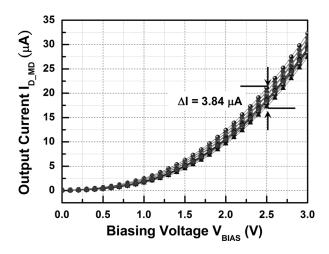

device in the LTPS process, is 0.675 V. The simulated drain current  $I_{D_{MD}}$  of the new proposed gate-bias voltage-generating circuit with threshold-voltage compensation under different biasing voltages  $V_{\rm BIAS}$  with the 50% threshold-voltage variation (Gaussian distribution) of n-TFT and p-TFT devices is shown in Fig. 6. The device dimension of  $M_{\rm D}$  device is  $80 \ \mu m/8 \ \mu m$ . The gate-to-drain voltage of  $M_D$  device is set to zero voltage to be operated in the saturation region. The simulated results show that the 50% threshold-voltage variation with Gaussian distribution of n-TFT and p-TFT devices causes only a variation of 3.84  $\mu$ A on the drain current  $I_{D-MD}$  in the new proposed gate-bias voltage-generating circuit with threshold-voltage compensation. Comparing the simulated results of Figs. 1 and 6, the new proposed gate-bias generating circuit with threshold-voltage compensation can effectively reduce the impact of threshold-voltage variation on the biasing circuit in the LTPS process.

## **IV. EXPERIMENTAL RESULTS**

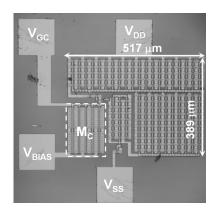

The new proposed gate-bias generating circuit with threshold-voltage compensation has been fabricated in an 8- $\mu$ m LTPS technology. Fig. 7 shows the chip photograph of the new proposed gate-bias generating technique with threshold-voltage compensation. The test chip size of the new proposed gate-bias generating circuit with threshold-voltage compensation circuit is 517 × 389  $\mu$ m<sup>2</sup> in 8- $\mu$ m LTPS technology. The averaged power consumption of the proposed gate-bias generating circuit with threshold-voltage compensation is only 47  $\mu$ W under the supply voltage of 10 V. In this study, the definitions of mean value and variation (%) of currents in these measured results are adopted as

Mean Value =

$$\frac{I_{D1} + I_{D2} + I_{D3} + I_{D4}}{4}$$

(11)

$$Variation(\%) = \frac{Mean Value - I_{D_{-}\#}}{Mean Value} \times 100\% \quad (12)$$

where  $I_{D1}$ ,  $I_{D2}$ ,  $I_{D3}$ , and  $I_{D4}$  are drain currents of sample1, sample2, sample3, and sample4 of four LPTS n-TFT devices

Fig. 7. Chip photograph of the proposed gate-bias generating technique with threshold-voltage compensation fabricated in an  $8-\mu$ m LTPS process.

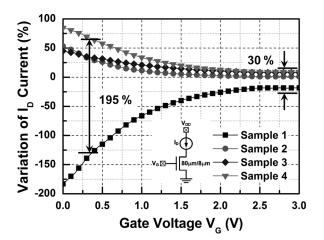

Fig. 8. Measured dependence of variation (%) on the gate voltage  $V_{\rm G}$  among four LTPS n-TFT devices in different panel locations.

in different panel locations, respectively, and the # is a sample number from 1 to 4. The power supply voltage  $V_{DD}$  is set to 10 V. Fig. 8 shows the measured dependence of variation (%) on the gate voltage V<sub>G</sub> under four LTPS n-TFT devices in different panel locations. The device dimensions of four n-TFT devices are kept at 80  $\mu$ m/8  $\mu$ m in an 8- $\mu$ m LTPS process. The gate voltages of these samples are biased from 1.3 to 4.3 V. The gate-to-drain voltage of the n-TFT device is set to 0 V to keep the n-TFT device operating in the saturation region. Because the gate-control voltage  $V_{GC}$  of the new proposed gate-bias generating circuit is  $V_{\text{BIAS}} + V_{\text{TH}}$ , the gate voltage from 1.3 to 4.3 V is normalized from 0 to 3 V. The variation (%) among four LPTS n-TFT devices in different panel locations is decreased from 195% to 30%, when the gate voltage is increased from 0 to 3 V. The measured results have confirmed that the variation (%) of four LPTS n-TFT devices in different panel locations under low gate voltage is large, but that under high gate voltage is low.

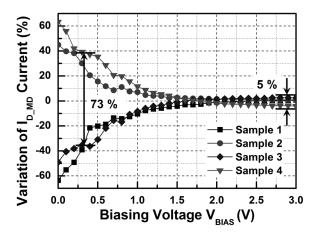

The measured dependence of variation (%) on the biasing voltage  $V_{\rm BIAS}$  among four LTPS test circuits of the new proposed gate-bias generating circuit with threshold-voltage compensation in different panel locations is shown in Fig. 9. The variation (%) among four LPTS test circuits in different panel locations is decreased from 73% to 5%, when the gate voltage is increased from 0 to 3 V. Comparing the measured results between Figs. 8 and 9, the new proposed gate-bias generating

Fig. 9. Measured dependence of variation (%) on the biasing voltage  $V_{\rm BIAS}$  among four LTPS test circuits of the new proposed gate-bias generating technique with threshold-voltage compensation in different panel locations.

technique with threshold-voltage compensation can effectively reduce the impact of threshold-voltage variation on the biasing current or biasing voltage for analog circuits in SoP or SoG applications.

#### V. DISCUSSION

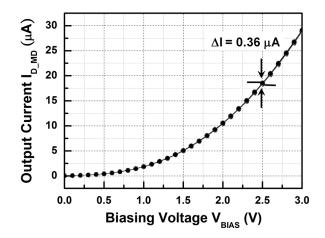

When the referenced current source  $I_{D_M4}$  is realized with an ideal referenced current source, the simulated results show that variation of  $I_{\text{D}_{-}\text{MD}}$  is only 0.27  $\mu$ A under 50% threshold-voltage variation (Gaussian distribution) of n-TFT and p-TFT devices. In order to achieve the low power consumption and small chip area, the referenced current source  $I_{D_M4}$  in the proposed gate-bias voltage-generating circuit with threshold-voltage compensation is realized by  $M_3$  and  $M_4$  devices. Because the voltage  $V_{\rm C}$  is dependent on threshold voltages of n-TFT and p-TFT devices, the threshold-voltage variation will cause some variations on the voltage  $V_{\rm C}$  and biasing current ( $I_{D_M4}$  and  $I_{D_MC}$ ) to degrade the performances of the proposed gate-bias voltage-generating circuit with threshold-voltage compensation. The variation of  $I_{D-MD}$ is finally increased from 0.27 to 3.84  $\mu$ A under 50% threshold voltage variation (Gaussian distribution) of n-TFT and p-TFT devices. In order to reduce the impact of referenced current  $I_{D_M4}$  variation on circuit performance, the  $M_3$  and  $M_4$  referenced current source can be further replaced by the modified n-TFT threshold-voltage referenced current source [11]. The complete circuit of the proposed gate-bias voltage-generating circuit with n-TFT threshold-voltage referenced current source for analog circuit applications in LTPS technology is shown in Fig. 10. When the referenced current source  $I_{D_M4}$  is realized with modified n-TFT threshold-voltage referenced current source, the simulated results show that the variation of  $I_{\rm D,MD}$  is only 0.36  $\mu$ A under 50% threshold-voltage variation (Gaussian distribution) of n-TFT and p-TFT devices, as shown in Fig. 11. Because the threshold voltages of n-TFT devices have the same variation trend in the local panel location, the biasing current  $I_{D_{MD}}$  with modified n-TFT threshold-voltage referenced current source can further reduce the variation on performance of the proposed circuit.

Fig. 10. Complete circuit of the proposed gate-bias voltage-generating circuit with modified n-TFT threshold-voltage referenced current source for analog circuits in LTPS technology.

Fig. 11. Simulated drain current  $I_{\rm D_-MD}$  of the proposed gate-bias voltage-generating circuit with modified n-TFT threshold-voltage referenced current source under different biasing voltages  $V_{\rm BIAS}$  with the 50% threshold voltage variation (Gaussian distribution) of n-TFT and p-TFT devices.

#### VI. CONCLUSION

A new gate-bias generating technique with threshold-voltage compensation has been presented to reduce the impact of threshold-voltage variation on analog circuit performance in LTPS technology. The new proposed gate-bias generating circuit with threshold-voltage compensation has been successfully verified in an  $8-\mu$ m LTPS process. The measured results have confirmed that the impact of threshold-voltage variation on drain current of the n-TFT device can be reduced from 30% to 5% under a biasing voltage of 3 V. The new proposed gate-bias generating technique with threshold-voltage compensation can be applied to realize analog circuits in the LTPS process for SoP or SoG applications.

#### REFERENCES

- H. G. Yang, S. Fluxman, C. Reita, and P. Migliorato, "Design, measurement and analysis of CMOS polysilicon TFT operational amplifiers," *IEEE J. Solid-State Circuits*, vol. 29, no. 6, pp. 727–732, Jun. 1994.

- [2] T. Matsuo and T. Muramatsu, "CG silicon technology and development of system on panel," in SID Tech. Dig., 2004, pp. 856–859.

- [3] Y. Matsueda, R. Kakkad, Y. S. Park, H. H. Yoon, W. P. Lee, J. B. Koo, and H. K. Chung, "2.5-in. AMOLED with integrated 6-bit gamma compensated digital data driver," in *SID Tech. Dig.*, 2004, pp. 1116–1119.

- [4] K. Yoneda, R. Yokoyama, and T. Yamada, "Development trends of LTPS TFT LCDs for mobile application," in *Symp. VLSI Circuits, Dig. Tech. Papers*, 2001, pp. 85–90.

- [5] R. M. A. Dawson, Z. Shen, M. G. Kanem, R. G. Stewart, C. N. King, P. J. Green, R. T. Flegal, S. Pearson, W. A. Barrow, E. Dickey, K. Ping, C. W. Tang, S. Van Slyke, F. Chen, J. C. Sturm, and M. H. Lu, "Design of an improved pixel for a ploy silicon active matrix organic light emitting diode display," in *SID Tech. Dig.*, 1998, pp. 11–14.

- [6] Y. Hashimoto, S. Saito, and K. Yoshida, "An LCD driver LSI for fullcolor and high resolution TFT-LCD," *NEC Res. Develop.*, vol. 35, pp. 30–37, 1994.

- [7] M.-D. Ker, C.-K. Deng, and J.-L. Huang, "On-panel design technique of threshold voltage compensation for output buffer in LTPS technology," *J. Display Technol.*, vol. 2, no. 2, pp. 153–159, Jun. 2006.

- [8] H.-J. Chung, S.-W. Lee, and C.-H. Han, "Poly-Si TFT push-pull analogue buffer for integrated data drivers of poly-Si TFT-LCDs," *Electron. Lett.*, vol. 37, no. 17, pp. 1093–1095, Aug. 2001.

- [9] C. Yoo, D.-J. Kim, and K.-L. Lee, "Threshold voltage and mobility mismatch compensated analogue buffer for driver-integrated poly-Si TFT LCDs," *Electron. Lett.*, vol. 41, no. 2, pp. 65–66, Jan. 2005.

- [10] P. Madeira and R. Hornsey, "Analog circuit design using amorphous silicon thin film transistors," in *Proc. IEEE Canad. Conf. Elect. Comput. Eng.*, 1997, pp. 633–636.

- [11] P. R. Gray, P. J. Hurst, S. H. Lewis, and P. G. Meyer, Analysis and Design of Analog Integrated Circuits. New York: Wiley, 2001, pp. 307–313.

circuit reliability.

Jung-Sheng Chen (S'03) received the B.S. degree in electronics engineering from the National Taiwan University of Science and Technology, Taipei, Taiwan, R.O.C., in 2000, and the M.S. degree in engineering and system science from National Tsing-Hua University, Hsinchu, Taiwan, R.O.C., in 2002. He is currently working toward the Ph.D. degree in electrical engineering at National Chiao-Tung University, Hsinchu.

His current research interests include analog circuit design, mixed-signal circuit design, and

**Ming-Dou Ker** (S'92–M'94–SM'97) received the B.S. degree from the Department of Electronics Engineering and the M.S. and Ph.D. degrees from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 1986, 1988, and 1993, respectively.

In 1994, he joined the VLSI Design Department, Computer and Communication Research Laboratories (CCL), Industrial Technology Research Institute (ITRI), Taiwan, R.O.C., as a Circuit Design Engineer. In 1998, he was the Department Manager with the

VLSI Design Division, CCL/ITRI. Now, he is a Full Professor with the Department of Electronics Engineering, National Chiao-Tung University. In the field of reliability and quality design for CMOS integrated circuits, he has published over 290 technical papers in international journals and conferences. He has proposed many inventions to improve reliability and quality of integrated circuits, with 120 U.S. patents and 132 R.O.C. (Taiwan) patents granted. His current research topics include reliability and quality design for nanoelectronics and gigascale systems, high-speed and mixed-voltage I/O interface circuits, and on-glass circuits for system-on-panel applications in TFT LCD display. He has been invited to teach or to consult reliability and quality design for integrated circuits by hundreds of design houses and semiconductor companies in the Science-Based Industrial Park, Hsinchu, Taiwan, R.O.C., Silicon Valley, San Jose, CA, Singapore, Malaysia, and mainland China.

Dr. Ker has served as member of the Technical Program Committee and Session Chair of numerous international conferences. He was selected as the Distinguished Lecturer of the IEEE Circuits and Systems Society for 2006–2007. He has also served as an Associate Editor of the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. He was elected as the President of Taiwan ESD Association in 2001. In 2003, he was selected as one of the Ten Outstanding Young Persons in Taiwan by the Junior Chamber International (JCI). In 2005, one of his patents on ESD protection design has been awarded with the National Invention Award in Taiwan.