200713836

# 發明專利說明書

200713836

(本說明書格式、順序及粗體字，請勿任意更動，※記號部分請勿填寫)

※申請案號：94132003

※申請日期：

94.9.16

※IPC分類：H03M 1/10 (2006.01)

一、發明名稱：(中文/英文)

於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路

二、申請人：(共1人)

姓名或名稱：(中文/英文)

國立交通大學

代表人：(中文/英文) 張俊彥

住居所或營業所地址：(中文/英文)

新竹市大學路1001號

國籍：(中文/英文) 中華民國 TW

三、發明人：(共1人)

姓名：(中文/英文)

洪浩喬

國籍：(中文/英文)

中華民國 TW

**四、聲明事項：**

主張專利法第二十二條第二項第一款或第二款規定之事實，其事實發生日期為： 年 月 日。

申請前已向下列國家（地區）申請專利：

【格式請依：受理國家（地區）、申請日、申請案號 順序註記】

有主張專利法第二十七條第一項國際優先權：

無主張專利法第二十七條第一項國際優先權：

主張專利法第二十九條第一項國內優先權：

【格式請依：申請日、申請案號 順序註記】

主張專利法第三十條生物材料：

須寄存生物材料者：

國內生物材料 【格式請依：寄存機構、日期、號碼 順序註記】

國外生物材料 【格式請依：寄存國家、機構、日期、號碼 順序註記】

不須寄存生物材料者：

所屬技術領域中具有通常知識者易於獲得時，不須寄存。

## 五、中文發明摘要：

本發明提出一種於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，係以電容、類比開關及數位電路作為數位輸入介面來測試混合訊號電路，因此可利用價格便宜的數位測試平台完成電路測試，解決傳統上需要使用高成本的混合模式測試機台和極嚴苛的測試環境條件的問題，因而改善可測性及降低測試成本，從而加速設計流程及縮短產品上市時間的限制。

## 六、英文發明摘要：

200713836

七、指定代表圖：

(一)、本案代表圖為：第二圖

(二)、本案代表圖之元件代表符號簡單說明：

11、12、11'、12' 電容組

15、16、17、18 類比多工選擇器

八、本案若有化學式時，請揭示最能顯示發明特徵的化學式：

## 九、發明說明：

### 【發明所屬之技術領域】

本發明係有關一種可重新規劃（Reconfigurable）切換電容（Switched-Capacitor）輸入電路，特別是有關一種於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路。

### 【先前技術】

在所有的電子電器廠商進入家庭客廳娛樂市場的同時，使得語音晶片市場將大幅成長，具切換電容式電路的電路元件，如三角積分調變器（Sigma-Delta Modulator），其測試亦越來越重要，且隨著積體電路製程的演進使得 IC 的結構愈趨複雜化，測試成本佔生產成本的比重越來越高，而測試成本太高的問題對於混合訊號電路更是嚴重，因混合訊號電路測試需要使用昂貴的混合訊號測試機台，如 Agilent 94000，並且由於無法平行測試類比與數位電路造成測試時間很長，對於產品的成本與上市時間產生不利的變動因素。

習知美國專利 US5132685 “Built-in self test for analog to digital converters” 使用額外之內建式高準確度三角波產生器作為激發源，其硬體成本高且無法做全速測試，測試準確度取決於增加之三角波產生器。

習知另一美國專利 US5305003 “Test device of analog/digital converter” 只能測試類比/數位轉換器之數位電路，而無法測試類比電路。

又一習知美國專利 US5659312 “Method and apparatus for testing

digital to analog and analog to digital converters” 使用額外之內建式數位類比轉換器作為激發源，硬體成本高，測試準確度取決於所增加之數位類比轉換器。

又一習知美國專利 US6333706 “Built-in self-test for analog to digital converter” 使用額外之內建式任意波產生器作為激發源，硬體成本高且無法做全速測試，測試準確度取決於所加入之任意波產生器。

有鑑於此，本發明係針對上述之問題，提出一種於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，以降低類比電路測試成本並維持一定之測試精準度。

### 【發明內容】

本發明之主要目的，係在提供一種於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其係利用數位激發訊號測試混合訊號電路，可以降低測試成本及生產成本。

本發明之另一目的，係在測試模式與正常工作模式下共用主要電路元件，使得主要電路元件負載相同，可得到高測量準確度、高錯誤覆蓋度、及全速度測試的優點。

本發明之再一目的，係在提供一種於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其係利用可重構式電路設計，可適用各種混合訊號架構的電路，加速設計流程及縮短產品上市時間。

根據本發明，其係一種於類比測試中可接收數位測試激發訊號之可重新規劃（Reconfigurable）切換電容（Switched-Capacitor）輸入電路，

其係應用於具有切換電容式輸入電路的數位可測試架構，可重新規劃切換電容輸入電路包括：一類比輸入訊號具有正相電壓訊號及負相電壓訊號；數個直流電壓源包括：一第一直流電壓源、一第二直流電壓源、一第三直流電壓源、以及一第四直流電壓源；一運算放大器具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，運算放大器將第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於第一放大器輸出端與第二放大器輸出端之間；至少二切換電容組，每一切換電容組係由第一電容、第二電容及數個類比訊號開關器組合在一起，每一電容具有一個接收端與一個輸出端，且每一切換電容組具有一相對應之數位激發訊號，每一數位激發訊號係為一經過數位三角積分調變之數位激發位元流(Sigma-Delta modulated digital stimulus bit-stream)；以及一數位開關訊號產生器至少接收一數位模式訊號，一時脈訊號，數位激發訊號，並產生數個開關訊號控制切換電容組之類比訊號開關器，且數位模式訊號，具有兩個邏輯狀態，包括正常狀態及測試狀態，時脈訊號係用以產生至少二不重疊之時脈相位(clock phases)包括第一時脈相位及第二時脈相位。

另外，一種於類比測試中可接收數位測試激發訊號之可重新規劃(Reconfigurable)切換電容(Switched-Capacitor)輸入電路，其係應用於具有切換電容式輸入電路的數位可測試架構，可重新規劃切換電容輸入電路包括：一類比輸入訊號具有正相電壓訊號及負相電壓訊號；數個直流電壓源包括：一第一直流電壓源、一第二直流電壓源、以及一第三直流

電壓源；一運算放大器具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，運算放大器將第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於第一放大器輸出端與第二放大器輸出端之間；至少一切換電容組，其係由第一電容、第二電容及數個類比訊號開關器組合在一起，第一電容及第二電容具有一個接收端與一個輸出端，切換電容組具有一相對應之數位激發訊號，數位激發訊號係為一經過數位三角積分調變之數位激發位元流（Sigma-Delta modulated digital stimulus bit-stream）；以及一數位開關訊號產生器至少接收一數位模式訊號，一時脈訊號，數位激發訊號，並產生數個開關訊號控制切換電容組之類比訊號開關器，且數位模式訊號具有兩個邏輯狀態，包括正常狀態及測試狀態，時脈訊號係用以產生至少二不重疊之時脈相位（clock phases）包含第一時脈相位及第二時脈相位。

再者，一種於類比測試中可接收數位測試激發訊號之可重新規劃（Reconfigurable）切換電容（Switched-Capacitor）輸入電路，其係應用於具有切換電容式輸入電路的數位可測試架構，可重新規劃切換電容輸入電路包括：一類比輸入訊號具有正相電壓訊號及負相電壓訊號；一數位資料訊號具有兩個邏輯狀態，包括加法狀態及減法狀態；數個直流電壓源包括：一第一直流電壓源、一第二直流電壓源、以及一第三直流電壓源；一運算放大器具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，運算放大器將第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於第一放大器輸出端與第二放大器輸出端之間；至少一切換

電容組由第一電容、第二電容及數個類比訊號開關器組合在一起，第一電容及第二電容具有一個接收端與一個輸出端，切換電容組具有一相對應之數位激發訊號，數位激發訊號係為一經過數位三角積分調變之數位激發位元流 (Sigma-Delta modulated digital stimulus bit-stream)；以及一數位開關訊號產生器至少接收一數位模式訊號，數位資料訊號，一時脈訊號，數位激發訊號，並產生數個開關訊號控制切換電容組之類比訊號開關器，且數位模式訊號具有兩個邏輯狀態，包括正常狀態及測試狀態，時脈訊號係用以產生至少二不重疊之時脈相位 (clock phases) 包含第一時脈相位及第二時脈相位。

底下藉由具體實施例配合所附的圖式詳加說明，當更容易瞭解本發明之目的、技術內容、特點及其所達成之功效。

### 【實施方式】

本發明係以切換電容電路與開關 (switch) 電路元件作為類比測試中可接收數位測試激發訊號之可重新規劃 (Reconfigurable) 切換電容輸入電路，可以數位訊號測試類比電路，大幅降低測試成本。

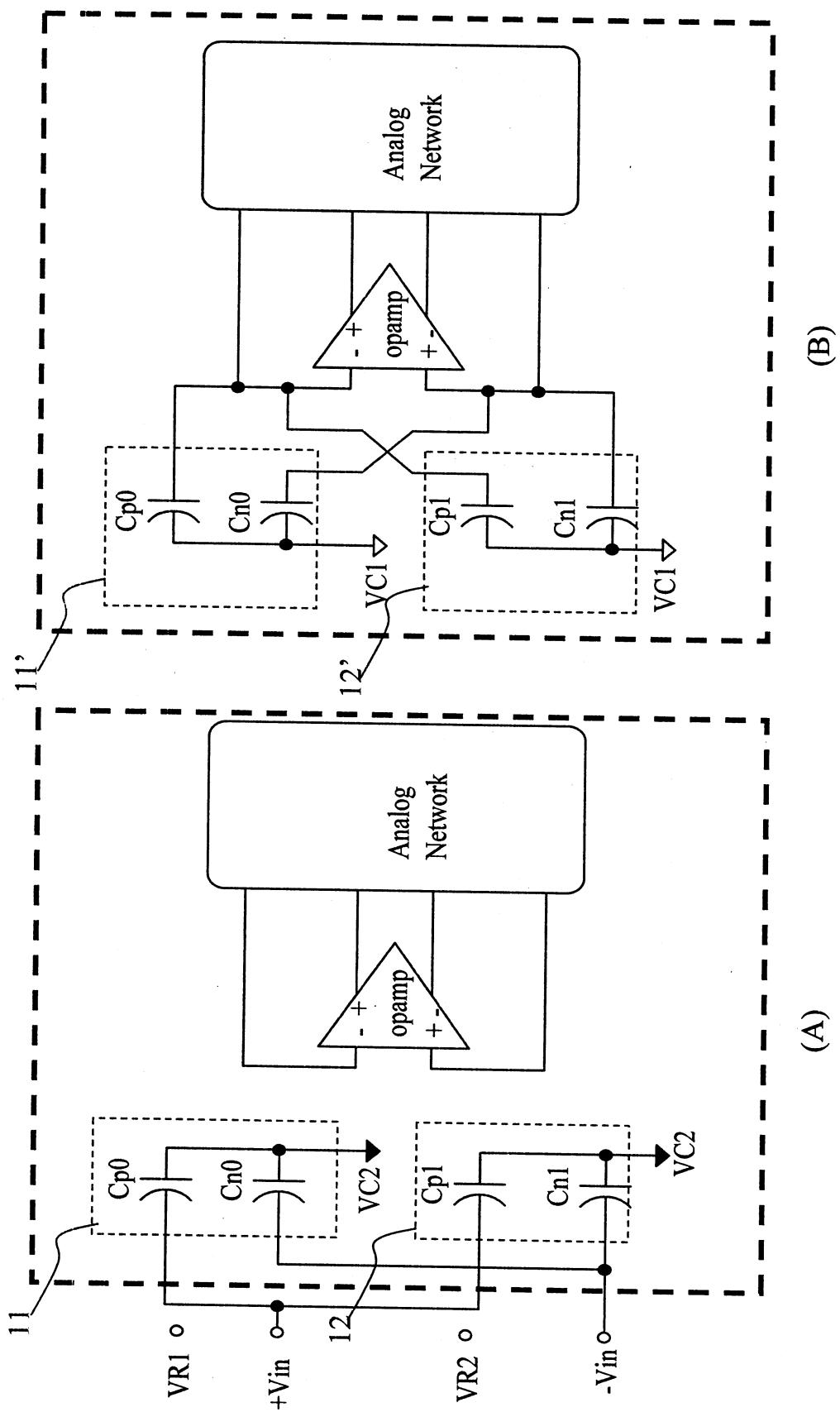

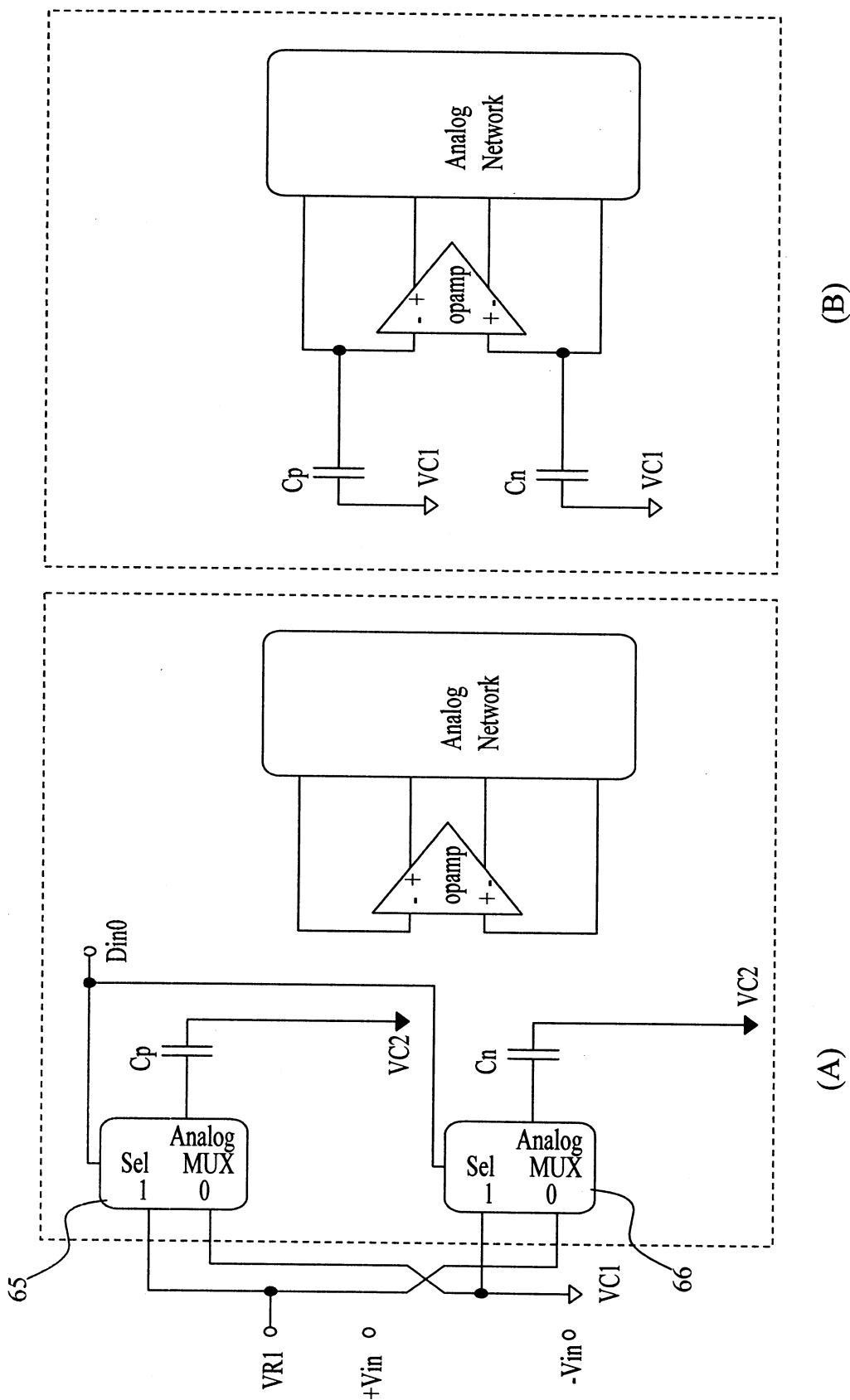

本發明為一適用於具有切換電容式輸入電路的嶄新數位可測試電路架構，本發明取代待測電路之原有切換電容式輸入電路，並藉由一個數位模式訊號控制本發明之切換電容式電路之工作模式為正常操作模式或測試模式，在正常工作模式下，待測電路維持原有的操作方法，參閱第一圖為本發明第一種實施例之正常操作模式輸入級之操作方法，至少分為兩個不重疊之時脈相位 (clock phases) (A) 及 (B)，在第一圖 (A) 中為第一時脈

相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電容組 11、12 之電容 Cp0、Cp1 接收端連接至類比輸入正相電壓訊號+Vin，同時將切換電容 11、12 組之電容 Cn0、Cn1 接收端連接至類比輸入負相電壓訊號-Vin，切換電容組 11、12 之電容 Cp0、Cn0、Cp1、Cn1 輸出端連接至直流電壓源 VC2；以及在第二時脈相位內切換電容組之連接狀態由第一圖(B)表示，切換電容組 11、12 之電容 Cp0、Cn0、Cp1、Cn1 接收端連接至直流電壓源 VC1，切換電容組 11、12 之電容 Cp0、Cp1 之輸出端連接至運算放大器(opamp)之負輸入端，切換電容組 11、12 之電容 Cn0、Cn1 之輸出端連接至運算放大器(opamp)之正輸入端。

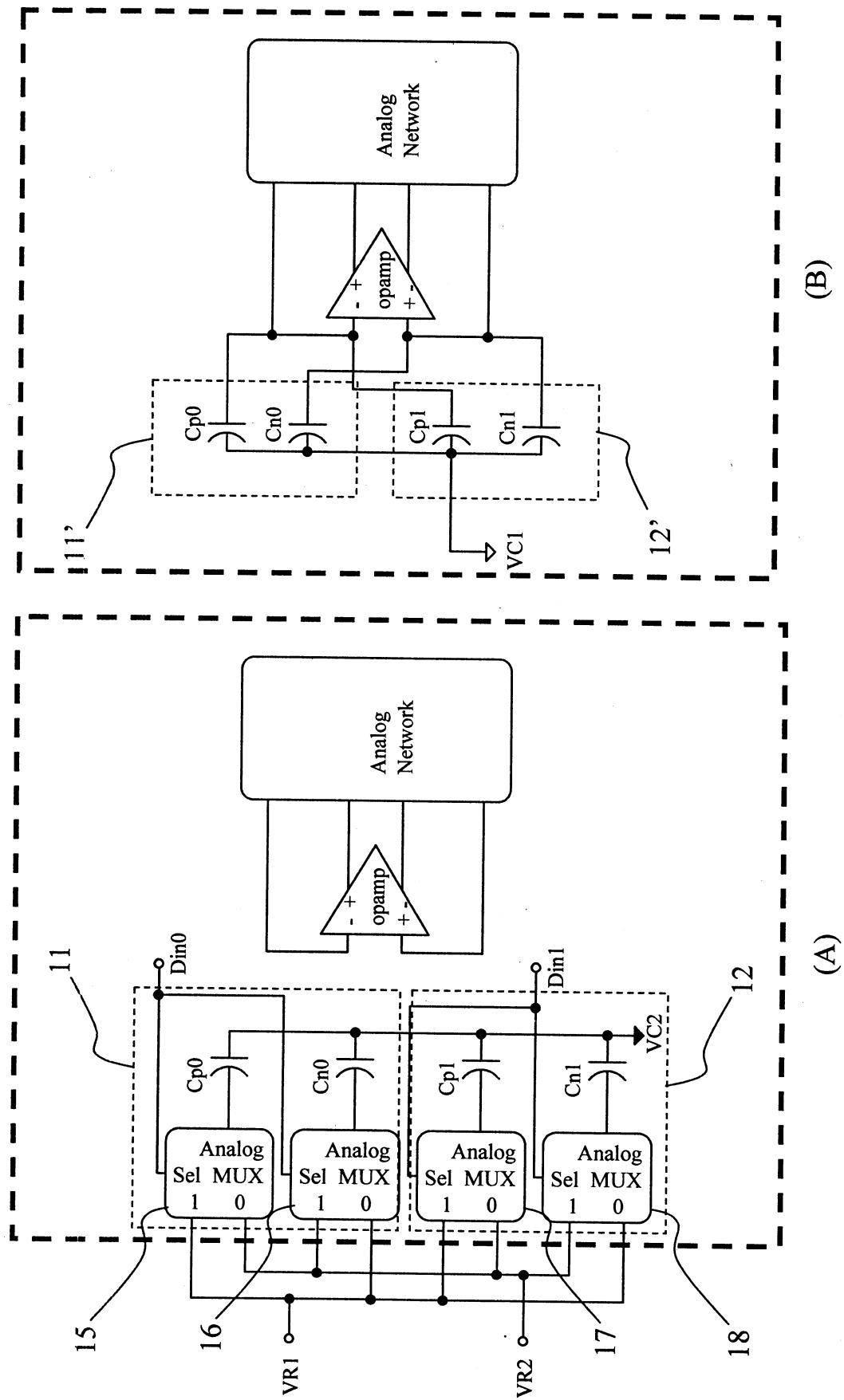

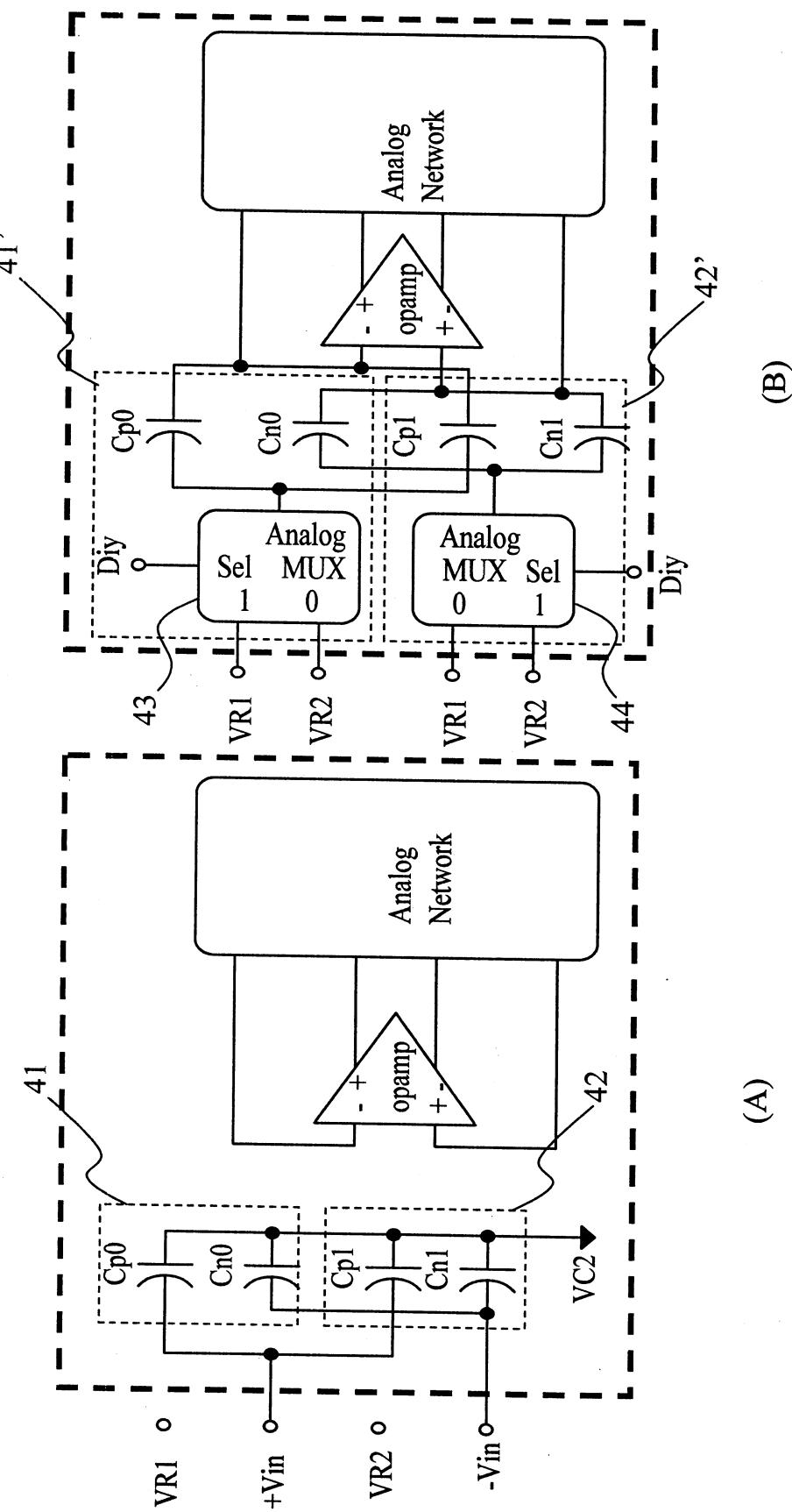

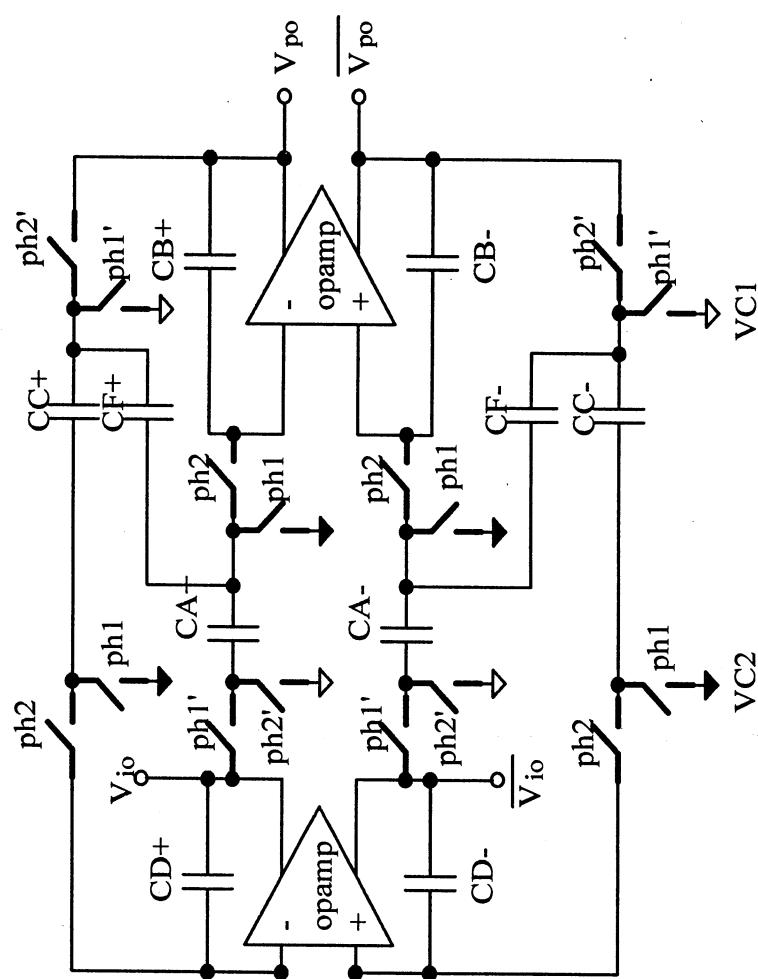

另外，再參閱第二圖為本發明第一種實施例之測試模式輸入級之操作方法，亦至少分為兩個不重疊之時脈相位(A)及(B)，在第二圖(A)中為測試模式下第一時脈相位內切換電容組之連接狀態，類比多工選擇器 15、16 對應於切換電容組 11 之電容，類比多工選擇器 17、18 則對應於切換電容組 12 之電容，切換電容組 11、12 之電容 Cp0、Cn0、Cp1、Cn1 輸出端接至一直流電壓源 VC2，並且數位開關訊號產生器接收數位激發訊號 Din0 並據以產生訊號控制類比多工選擇器 15、16，同時數位開關訊號產生器接收數位激發訊號 Din1 並據以產生訊號控制類比多工選擇器 17、18，以切換相對應之切換電容組 11、12 內之電容接收端之連接為增加狀態或減少狀態，該增加狀態為切換電容組 11、12 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR1，切換電容組 11、12 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR2，該減少狀態為切換電容組 11、12 之電容 Cp0、Cp1 接收端連接至直流

電壓源 VR2，切換電容組 11、12 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR1；其中，數位激發訊號 Din1、Din0 為一經過數位三角積分調變之數位激發位元流（Digital stimulus bit-stream），且數位激發訊號 Din1 與數位激發訊號 Din0 相同，但比數位激發訊號 Din0 延遲數個週期。在第二圖（B）中為測試模式下第二時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電容組 11'、12' 所有電容之輸入端接至一直流電壓源 VC1，切換電容組 11'、12' 之電容 Cp0、Cp1 之輸出端連接至運算放大器（opamp）之負輸入端，切換電容組電容組 11'、12' 之電容 Cn0、Cn1 之輸出端連接至運算放大器（opamp）之正輸入端。

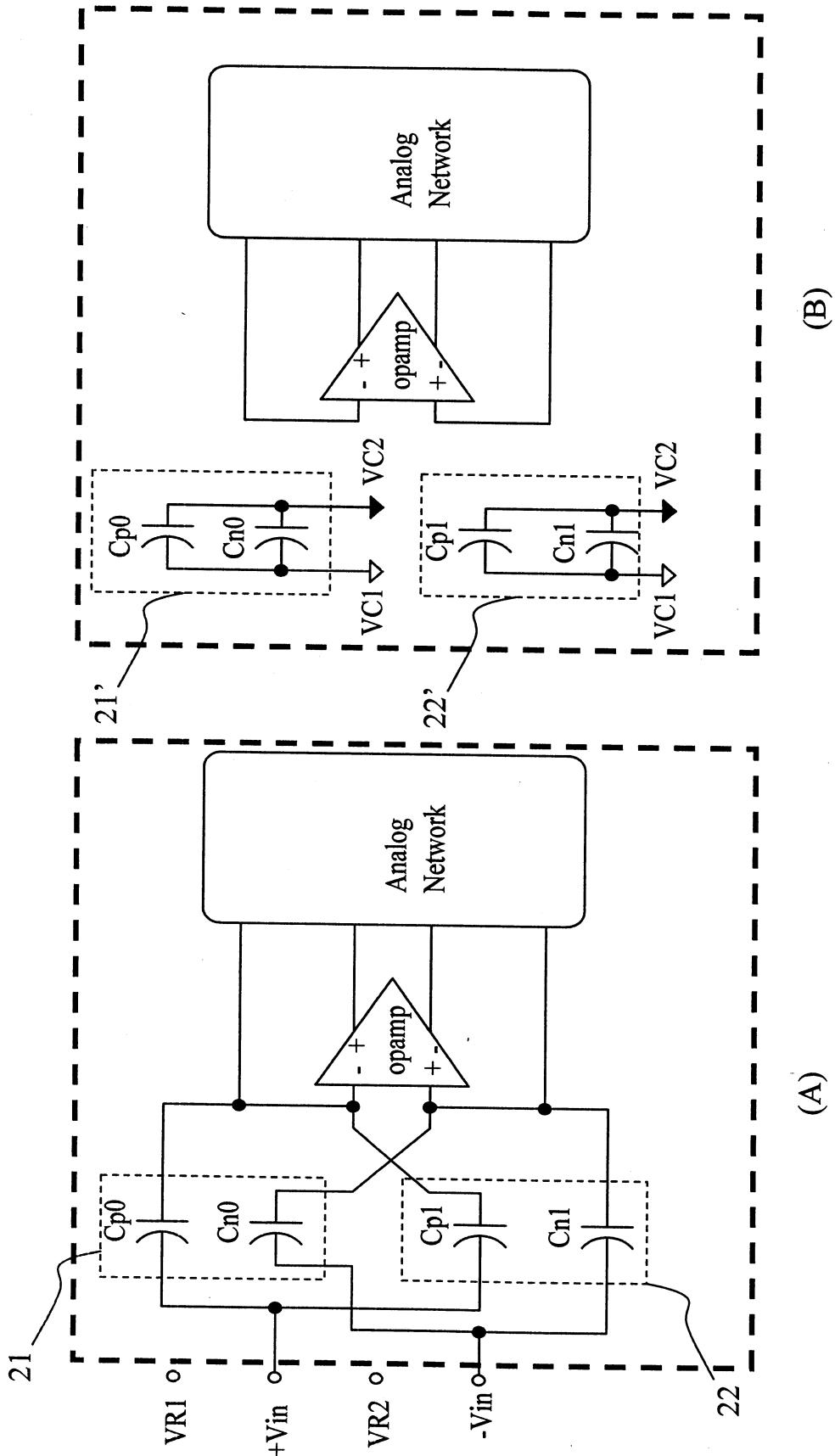

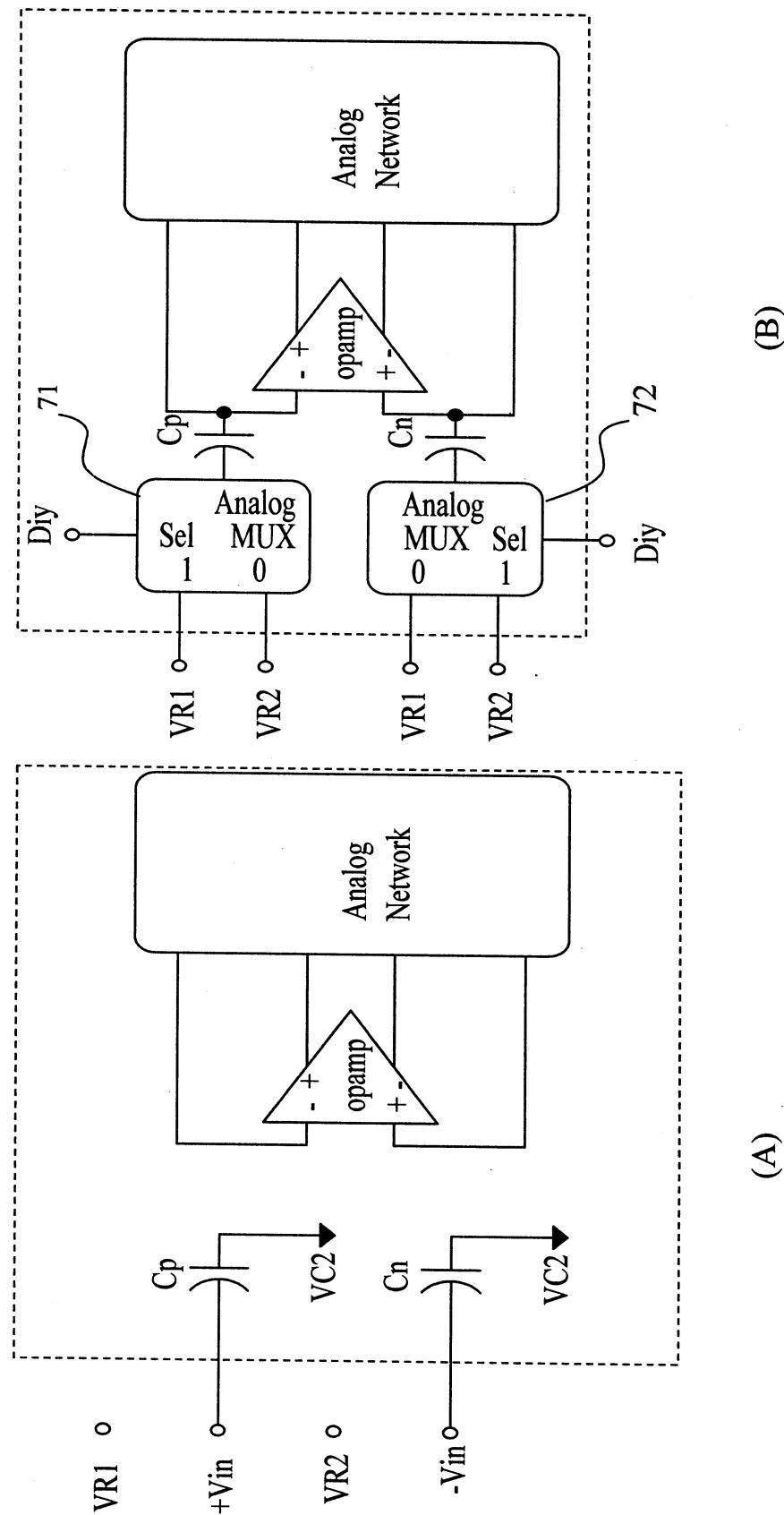

待測電路之正常操作模式並不限於第一圖，請參閱第三圖為本發明第二種實施例之正常操作模式輸入級之操作方法，至少分為兩個不重疊之時脈相位（A）及（B），在第三圖（A）中為第一時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將類比輸入正相電壓訊號+Vin 連接至切換電容組 21、22 之電容 Cp0、Cp1 的輸入端，同時將類比輸入負相電壓訊號-Vin 連接至切換電容組 21、22 之電容 Cn0、Cn1 的輸入端，切換電容組 21、22 之電容 Cp0、Cp1 之輸出端連接至運算放大器（opamp）之負輸入端，切換電容組 21、22 之電容 Cn0、Cn1 之輸出端連接至運算放大器（opamp）之正輸入端；在第三圖之（B）為第二時脈相位，數位開關訊號產生器產生開關訊號將切換電容組 21'、22' 輸入端接至一直流電壓源 VC1，同時將電容組 21'、22' 輸出端接至另一直流電壓源 VC2。

另外，第二種實施例之測試模式輸入級之操作方法，則如第二圖所示

亦有兩個時脈相位。

再者，第三種實施例之正常操作模式輸入級之操作方法，則如第一圖所示有兩個時脈相位。

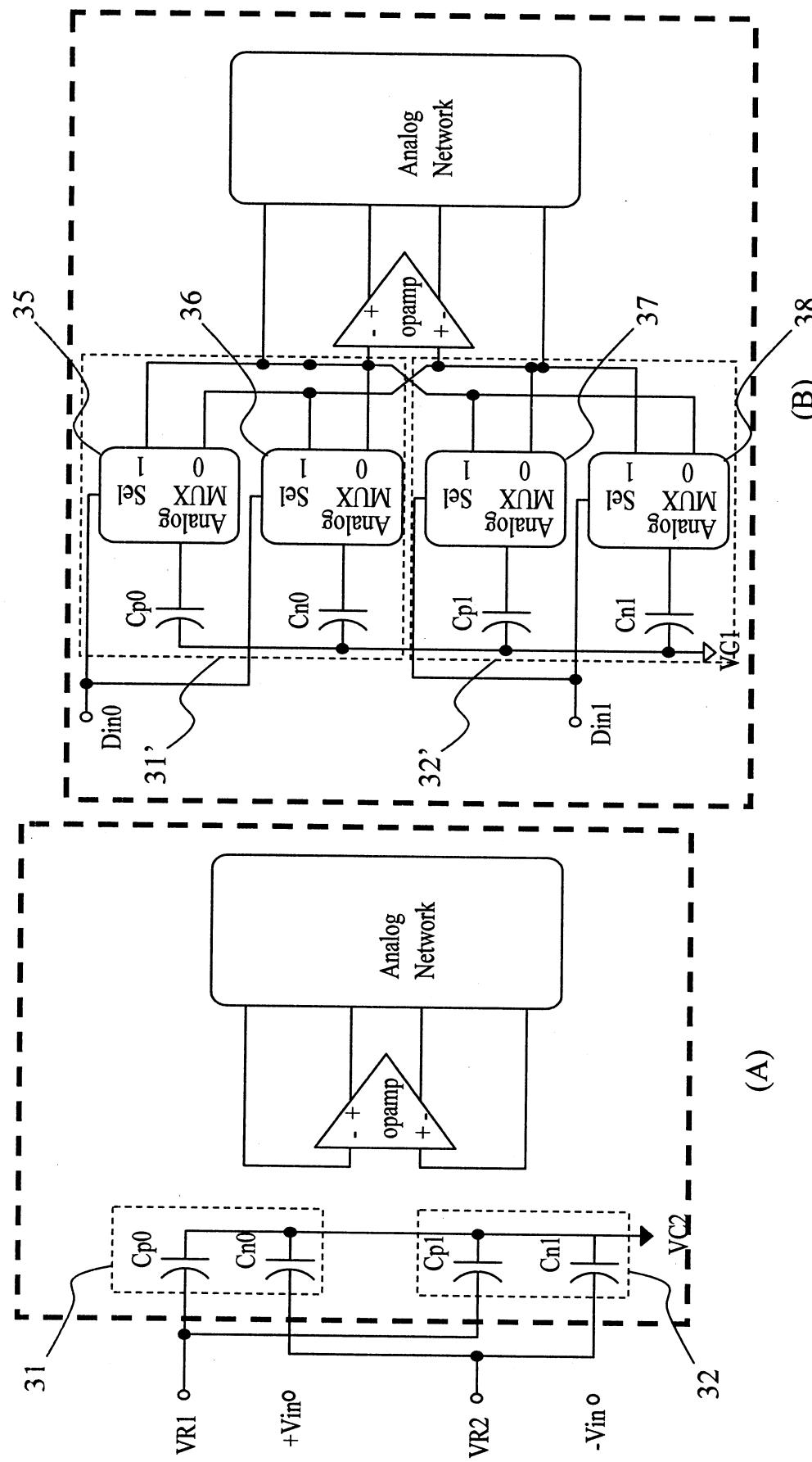

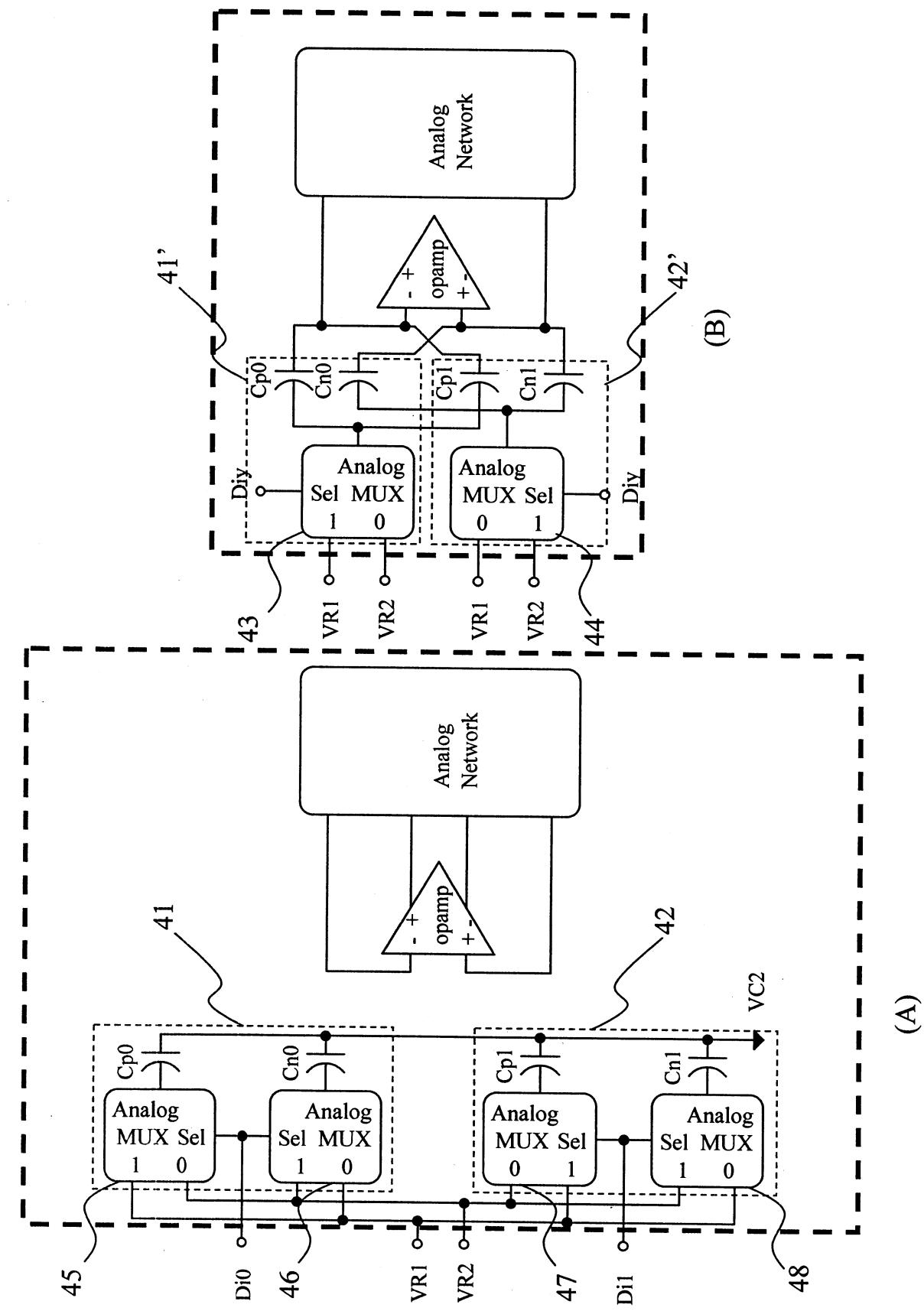

請參閱第四圖為本發明第三種實施例之測試模式輸入級之操作方法，亦至少分為兩個不重疊之時脈相位（A）及（B），在第四圖（A）中為測試模式下第一時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電容組 31、32 之電容 Cp0、Cn0、Cp1、Cn1 輸出端連接至直流電壓源 VC2，同時將切換電容組 31、32 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR1，切換電容組 31、32 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR2；在第四圖（B）中為第二時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電容組 31'、32' 內之所有電容輸入端接至直流電壓源 VC1，並同時將切換電容組 31'、32' 中各電容輸出端接至相對應的類比多工選擇器 35、36、37、38，並且數位開關訊號產生器接收數位激發訊號 Din0 並據以產生訊號控制切換電容組 31'，及數位激發訊號 Din1 並據以產生訊號控制切換電容組 32'，以切換相對應之切換電容組 31'、32' 內之電容接收端之連接為增加狀態或減少狀態，且該增加狀態為切換電容組 31'、32' 之電容 Cp0、Cp1 接收端連接至運算放大器（opamp）之負輸入端，切換電容組 31'、32' 之電容 Cn0、Cn1 接收端連接至運算放大器（opamp）之正輸入端，該減少狀態為切換電容組 31'、32' 之電容 Cp0、Cp1 輸出端連接至放大器之正輸入端，切換電容組 11、12 之電容 Cn0、Cn1 輸出端連接至放大器之負輸入端；其中，數位激發

訊號 Din1、Din0 為一經過數位三角積分調變之數位激發位元流 (Digital stimulus bit-stream)，數位激發訊號 Din1 與數位激發訊號 Din0 相同，但比數位激發訊號 Din0 延遲數個週期。

另外，第四種實施例之正常操作模式輸入級之操作方法，如第三圖所示有兩個時脈相位，其測試模式輸入級之操作方法則如第四圖所示亦有兩個時脈相位。

上述之第一種、第二種、第三種以及第四種之實施例中，正常操作模式與測試操作模式之二不重疊時脈的關係除了一一對應之外，正常操作模式之第一時脈相位也可以相對應測試操作模式之第二時脈相位，且正常操作模式之第二時脈相位同時相對應測試操作模式之第一時脈相位；另外，切換電容組可以共用數個類比訊號開關器，VC1 亦可以為 VR1 或 VR2，VC2 亦可以為 VC1、VR1 或 VR2；數位激發訊號 Din0 之增加狀態可以相對應數位激發訊號 Din1 之減少狀態，並且數位激發訊號 Din0 之減少狀態相對應數位激發訊號 Din1 之增加狀態。

請參閱第五圖為本發明第五種實施例之正常模式輸入級之操作方法，至少分為兩個不重疊之時脈相位 (A) 及 (B)，在第五圖 (A) 中為第一時脈相位內切換電容組之連接狀態，數位模式訊號為正常狀態時控制開關訊號，使可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據時脈相位切換每一切換電容組內之電容接收端或輸出端之連接，在第一時脈相位內，數位開關訊號產生器產生開關訊號控制切換電容組之類比訊號開關器將切換電容組 41、42 之電容 Cp0、Cp1 接收端連接至類比輸入正相

電壓訊號+Vin，同時切換電容組 41、42 之電容 Cn0、Cn1 接收端連接至類比輸入負相電壓訊號-Vin，切換電容組 41、42 之電容 Cp0、Cn0、Cp1、Cn1 輸出端連接至直流電壓源 VC2；以及在第二時脈相位內切換電容組之連接狀態如第五圖（B）所示，切換電容組 41'、42' 之電容 Cp0、Cp1 輸出端連接至運算放大器（opamp）之負輸入端，切換電容組 41'、42' 之電容 Cn0、Cn1 輸出端連接至運算放大器（opamp）之正輸入端，並且數位開關訊號產生器接收數位資料訊號Diy並據以產生訊號控制控制切換電容組 41'、42' 使切換電容組 41'、42' 內之電容接收端之連接為減法狀態或加法狀態；其中，該減法狀態為切換電容組 41'、42' 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR1，切換電容組 41'、42' 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR2，該加法狀態為切換電容組 41'、42' 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR2，切換電容組之電容 Cn0、Cn1 接收端連接至直流電壓源 VR1。

再請參閱第六圖為本發明第五種實施例之測試模式輸入級之操作方法，亦至少分為兩個不重疊之時脈相位（A）及（B），在第六圖（A）中為第一時脈相位切換電容組之連接狀態，在數位模式訊號為測試狀態時控制開關訊號，使可重新規劃切換電容輸入電路在一測試操作模式下運作，其係依據時脈相位切換每一切換電容組內之電容接收端或輸出端之連接，在第一時脈相位內，類比多工選擇器 45、46 對應於切換電容組 41 之電容，類比多工選擇器 47、48 則對應於切換電容組 42 之電容，並且數位開關訊號產生器產生訊號控制控制切換電容組 41 及切換電容組 42，以切換相對應

之切換電容組 41、42 內之電容接收端之連接為增加狀態或減少狀態，該增加狀態為切換電容組 41、42 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR1，切換電容組 41、42 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR2，該減少狀態為切換電容組 41、42 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR2，切換電容組 41、42 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR1；以及在第二時脈相位內如第六圖（B）所示，切換電容組 41'、42' 之電容 Cp0、Cp1 輸出端連接至運算放大器（opamp）之負輸入端，切換電容組 41'、42' 之電容 Cn0、Cn1 輸出端連接至運算放大器（opamp）之正輸入端，並且數位開關訊號產生器接收數位資料訊號 Diy 並據以產生訊號控制切換電容組 41' 及切換電容組 42'，使切換電容組 41' 及切換電容組 42' 內之電容接收端之連接為減法狀態或加法狀態，且該減法狀態為切換電容組 41'、42' 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR1，切換電容組 41'、42' 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR2，該加法狀態為切換電容組 41'、42' 之電容 Cp0、Cp1 接收端連接至直流電壓源 VR2，切換電容組 41'、42' 之電容 Cn0、Cn1 接收端連接至直流電壓源 VR1；其中，數位激發訊號 Din1、Din0 為一經過數位三角積分調變之數位激發位元流（Digital stimulus bit-stream），且數位激發訊號 Din1 與數位激發訊號 Din0 相同，但比數位激發訊號 Din0 延遲數個週期。

另外，在第五種實施例中，正常操作模式之減法狀態相對應測試操作模式之加法狀態，且正常操作模式之加法狀態相對應測試操作模式之減法狀態，切換電容組共用數個類比訊號開關器，VC2 為 VR1 或 VR2。

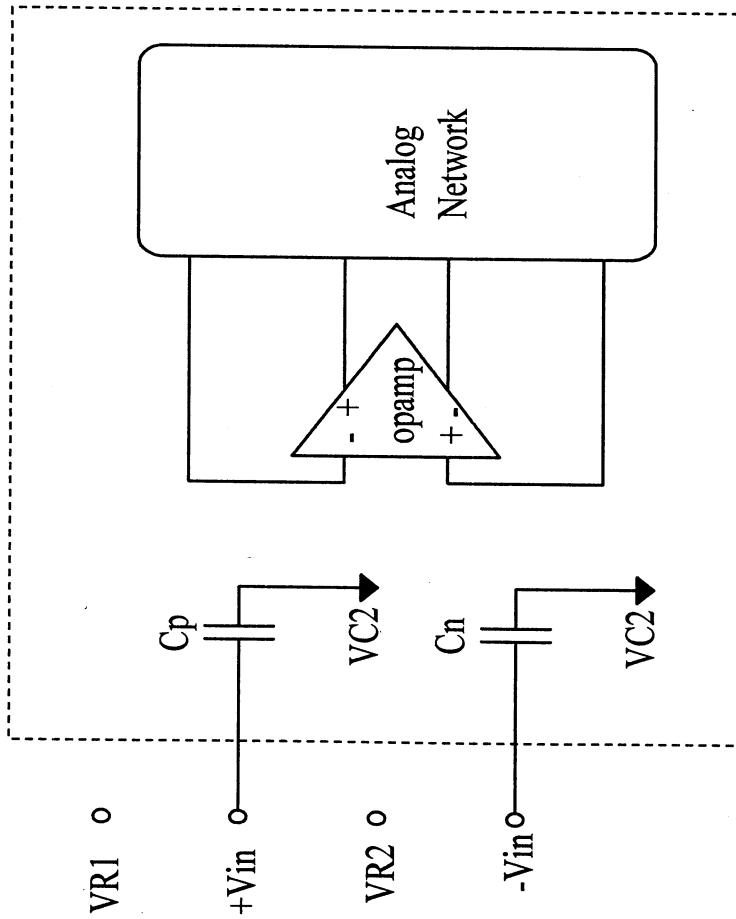

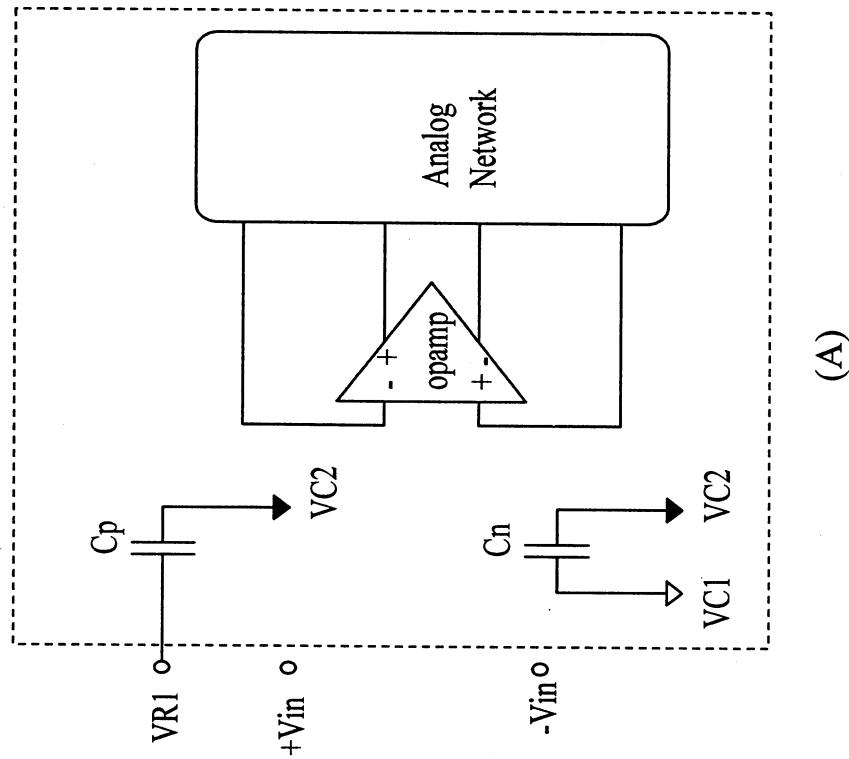

本發明亦可以應用至另一種數位可測試架構，請參閱第七圖為本發明第六種實施例之正常操作模式輸入級之操作方法，至少分為兩個不重疊之時脈相位（A）及（B），在第七圖（A）中為第一時脈相位切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電路切換一類比輸入正相電壓訊號+Vin 輸入電容 Cp，同時將切換電路切換一類比輸入負相電壓訊號-Vin 輸入電容 Cn，電容 Cp、Cn 輸出端接至一直流電壓源 VC2；在第七圖（B）中為第二時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將電容 Cp、Cn 輸入端接至一直流電壓源 VC1，電容 Cp 之輸出端連接至運算放大器（opamp）之負輸入端，電容 Cn 之輸出端連接至運算放大器（opamp）之正輸入端。

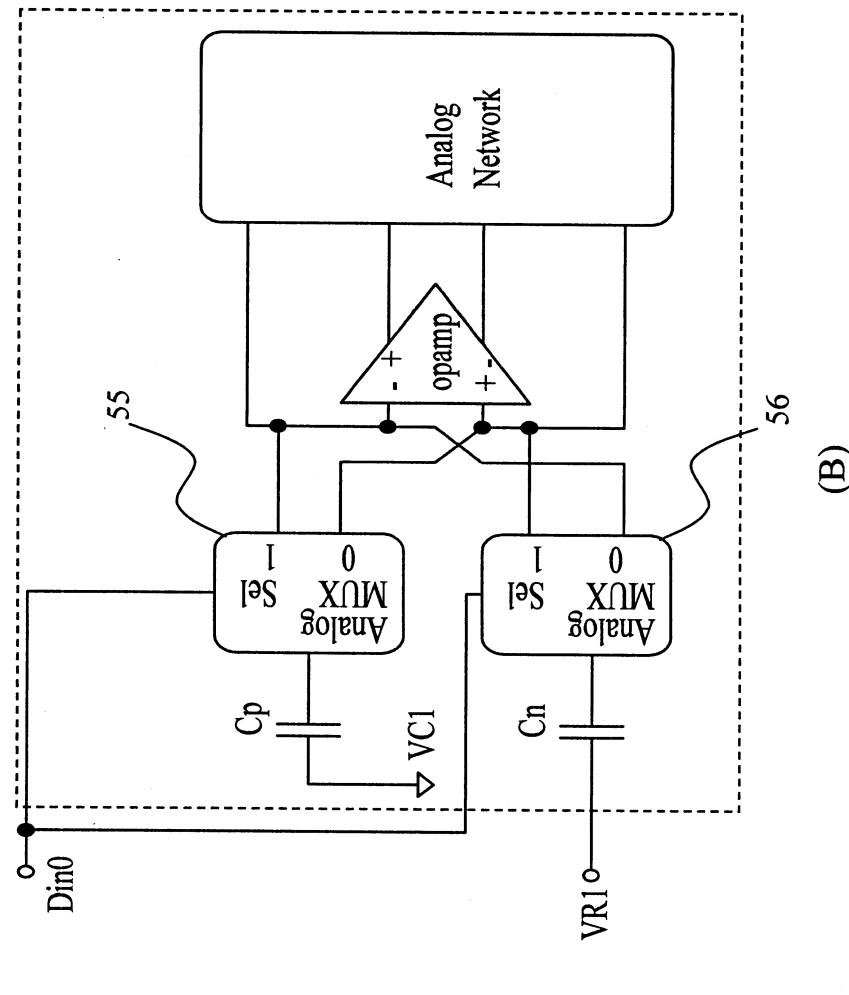

另外，參閱第八圖為本發明第六種實施例之測試模式輸入級之操作方法，至少分為兩個不重疊之時脈相位（A）及（B），在第八圖（A）中為第一時脈相位切換電容組之連接狀態，數位開關訊號產生器產生開關訊號控制切換電容組之類比訊號開關器將切換電容組之電容 Cp 之輸入端連接至直流電壓訊號 VR1，並將切換電容組之電容 Cn 輸入端接至直流電壓源 VC1，同時將電容 Cp、Cn 之輸出端接至直流電壓源 VC2：在第八圖（B）中為第二時脈相位內切換電容組之連接狀態，數位開關訊號產生器產生開關訊號控制切換電容組之類比訊號開關器將電容 Cp 輸入端接至直流電壓源 VC1，電容 Cp 輸出端接至類比多工選擇器 55，電容 Cn 輸入端接至直流電壓訊號 VR1，電容 Cn 輸出端接至類比多工選擇器 56，類比多工選擇器 55、56 最後輸出訊號至運算放大器（opamp），並且數位激發訊號 Din0 控制相對應之切

換電容，以切換電容輸出端之連接為增加狀態或減少狀態，該增加狀態為電容  $C_p$  輸出端連接至運算放大器 (opamp) 之負輸入端，電容  $C_n$  輸出端連接至運算放大器 (opamp) 之正輸入端，該減少狀態為電容  $C_p$  輸出端連接至運算放大器 (opamp) 之正輸入端，電容  $C_n$  輸出端連接至運算放大器 (opamp) 之負輸入端。

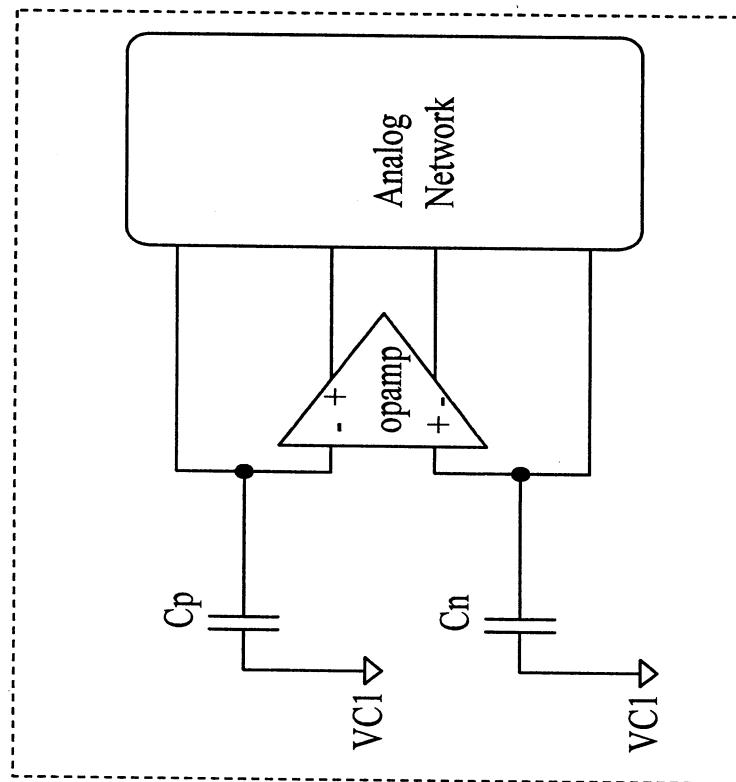

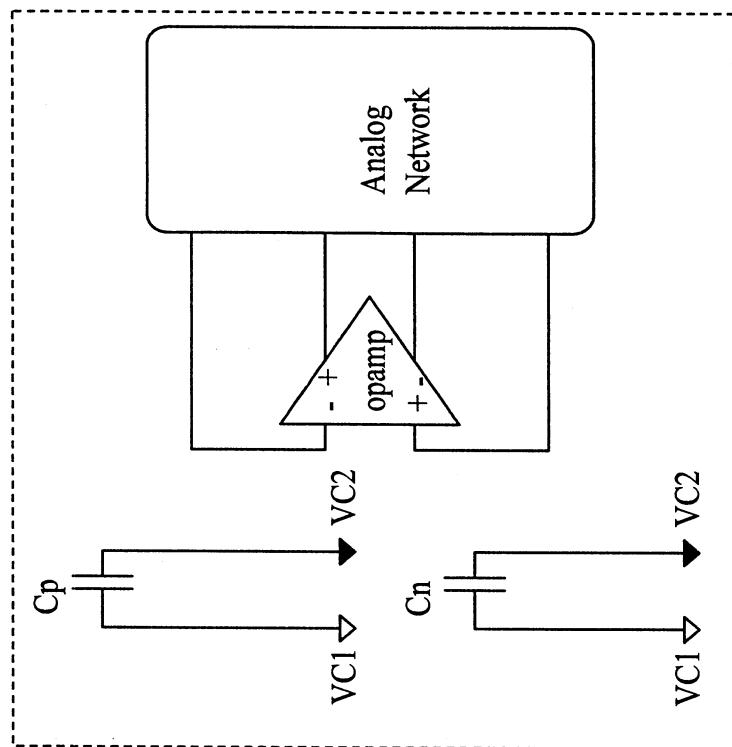

請參閱第九圖為本發明第七種實施例之正常操作模式輸入級之操作方法，至少分為兩個不重疊之時脈相位 (A) 及 (B)，在第九圖 (A) 中為第一時脈相位切換電容組之連接狀態，數位開關訊號產生器產生開關訊號控制切換電容組之類比訊號開關器將切換電容組之電容  $C_p$  之輸入端連接至一類比輸入正相電壓訊號  $+V_{in}$ ，電容  $C_n$  之輸入端連接至一類比輸入負相電壓訊號  $-V_{in}$ ，同時將電容  $C_p$  之輸出端連接至運算放大器 (opamp) 之負輸入端，電容  $C_n$  之輸出端連接至運算放大器 (opamp) 之正輸入端；在第九圖 (B) 中為第二時脈相位切換電容組之連接狀態，數位開關訊號產生器產生開關訊號將切換電路分別將電容  $C_p$ 、 $C_n$  之輸入端接至直流電壓源  $V_{C1}$ ，輸出端接至另一直流電壓源  $V_{C2}$ 。

再者，第七種實施例之測試模式輸入級之操作方法，則如第八圖所示有兩個時脈相位。

第八種實施例之正常操作模式輸入級之操作方法，則如第七圖所示有兩個時脈相位。

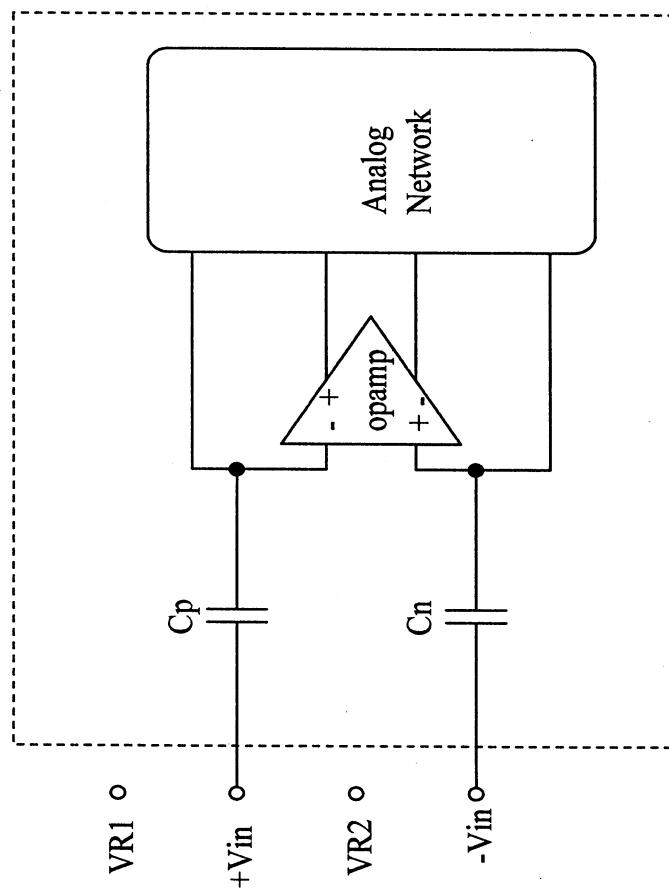

另外，請參閱第十圖為本發明第八種實施例之測試模式輸入級之操作方法，至少分為兩個不重疊之時脈相位 (A) 及 (B)，在第七圖 (A) 中為

第一時脈相位切換電容組之連接狀態，類比多工選擇器 65、66 接收直流電壓訊號 VR1 及直流電壓源 VC1 輸入，並由一數位激發訊號 Din0 控制，最後輸出訊號至電容 Cp、Cn，切換電路將電容 Cp、Cn 之輸出端接至一直流電壓源 VC2，並且數位開關訊號產生器接收數位激發訊號 Din0 並據以產生訊號控制類比多工選擇器 65、66，以切換電容接收端之連接為增加狀態或減少狀態，且該增加狀態為電容 Cp 接收端連接至直流電壓源 VR1，電容 Cn 接收端連接至直流電壓源 VR2，該減少狀態為電容 Cp 接收端連接至直流電壓源 VR2，電容 Cn 接收端連接至直流電壓源 VR1：在第十圖（B）中為第二時脈相位，二切換電路將分別將電容 Cp、Cn 之輸入端接至直流電壓源 VC1，電容 Cp 輸出端連接至該運算放大器（opamp）之負輸入端及電容 Cn 輸出端連接至該運算放大器（opamp）之正輸入端。

第九種實施例之正常操作模式輸入級之操作方法，則如第九圖所示有兩個時脈相位，且第九種實施例之測試模式輸入級之操作方法，則如第十圖所示有兩個時脈相位。

上述之第六種、第七種、第八種以及第九種之實施例中正常操作模式與測試操作模式之二不重疊時脈的關係除了一一對應之外，正常操作模式之第一時脈相位亦可以相對應測試操作模式之第二時脈相位，同時正常操作模式之第二時脈相位相對應測試操作模式之第一時脈相位；另外，切換電容組可以共用數個類比訊號開關器，VC1 亦可以為 VR1 或 VR2。

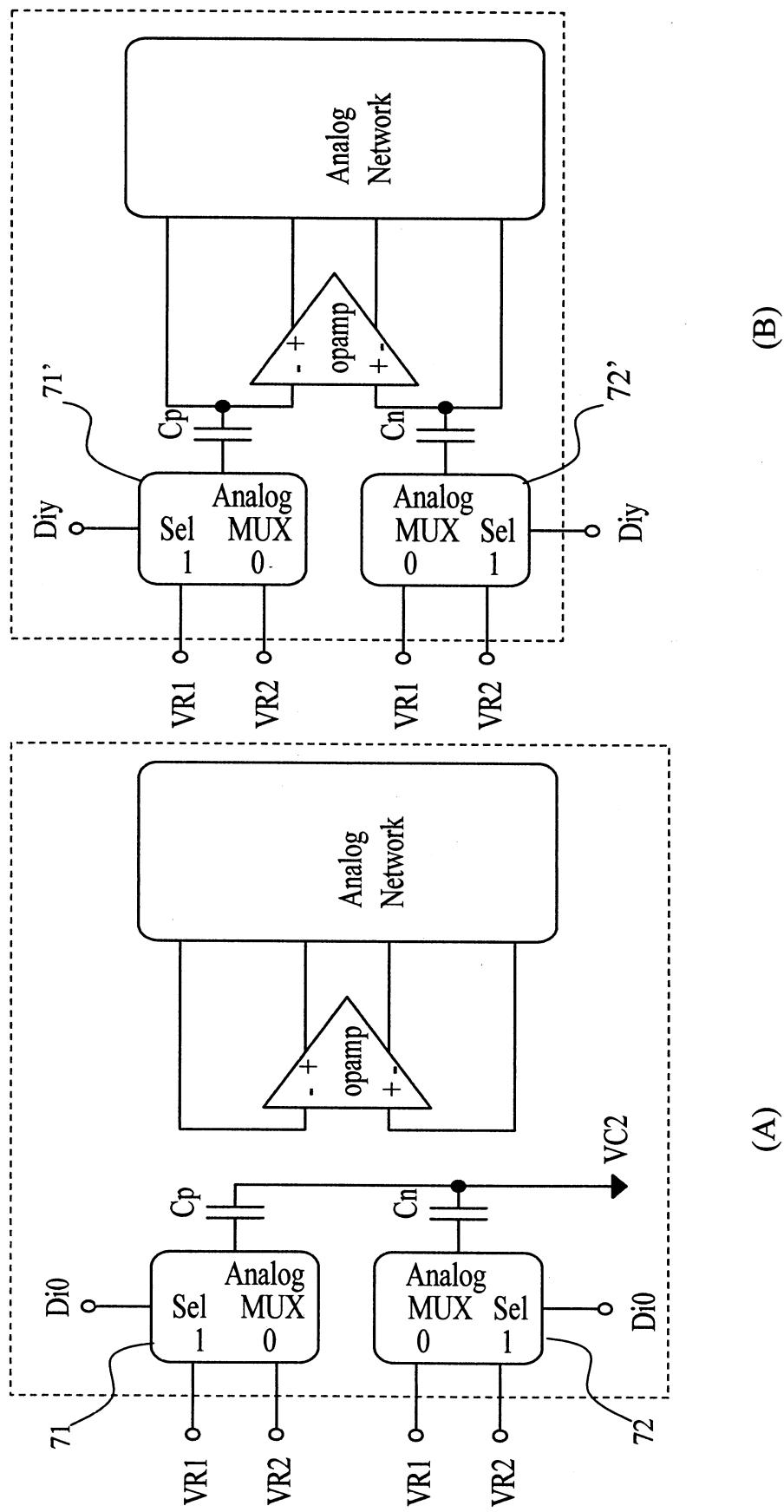

請參閱第十一圖為本發明之第十種實施例之正常操作模式輸入級之操作方法，至少分為兩個不重疊之時脈相位（A）及（B），在第十一圖（A）

中為第一時脈相位切換電容組之連接狀態，數位模式訊號為正常狀態時控制開關訊號，使可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據時脈相位切換切換電容組內之電容接收端及輸出端之連接，在第一時脈相位內，數位開關訊號產生器產生開關訊號將電容  $C_p$  接收端連接至類比輸入正相電壓訊號  $+V_{in}$ ，同時將電容  $C_n$  接收端連接至類比輸入負相電壓訊號  $-V_{in}$ ，電容  $C_p$ 、 $C_n$  輸出端連接至直流電壓源  $V_{C2}$ ；以及在第二時脈相位內如第十一圖 (B) 所示，電容  $C_p$  之輸出端連接至運算放大器 (opamp) 之負輸入端，電容  $C_n$  之輸出端連接至運算放大器 (opamp) 之正輸入端，並且數位開關訊號產生器接收數位資料訊號  $D_{iy}$  並據以產生訊號控制類比多工選擇器 71、72，以切換電容  $C_p$ 、 $C_n$  接收端之連接為減法狀態或加法狀態，且該減法狀態為電容  $C_p$  接收端連接至直流電壓源  $V_{R1}$ ，電容  $C_n$  接收端連接至直流電壓源  $V_{R2}$ ，該加法狀態為電容  $C_p$  接收端連接至直流電壓源  $V_{R2}$ ，電容  $C_n$  接收端連接至直流電壓源  $V_{R1}$ 。

請參閱第十二圖為本發明第十種實施例之測試模式輸入級之操作方法，分為兩個時脈相位 (A) 及 (B)，在第七圖 (A) 中為第一時脈相位切換電容組之連接狀態，在數位模式訊號為測試狀態時，控制電容接收端及輸出端之連接，使可重新規劃切換電容輸入電路在一測試操作模式下運作，測試操作模式係依據時脈相位切換電容接收端及輸出端之連接，在第一時脈相位內，數位開關訊號產生器接收數位激發訊號  $D_{in0}$  並據以產生訊號控制類比多工選擇器 71、72 控制電容  $C_p$ 、 $C_n$  輸出端連接至直流電壓源  $V_{C2}$ ，並同時控制電容  $C_p$  及電容  $C_n$  接收端之連接為增加狀態或減少狀態，

且該增加狀態為電容  $C_p$  接收端連接至直流電壓源  $VR_1$ ，電容  $C_n$  接收端連接至直流電壓源  $VR_2$ ，該減少狀態為電容  $C_p$  接收端連接至直流電壓源  $VR_2$ ，電容  $C_n$  接收端連接至直流電壓源  $VR_1$ ；以及在第二時脈相位內，如第七圖(B)中所示為其切換電容組之連接狀態，電容  $C_p$  之輸出端連接至運算放大器 (opamp) 之負輸入端，電容  $C_n$  之輸出端連接至運算放大器 (opamp) 之正輸入端，並且數位開關訊號產生器接收數位資料訊號  $D_{iy}$  並據以產生訊號控制類比多工選擇器  $71'$ 、 $72'$  使電容  $C_p$ 、 $C_n$  接收端之連接為減法狀態或加法狀態，且該減法狀態為電容  $C_p$  接收端連接至直流電壓源  $VR_1$ ，電容  $C_n$  接收端連接至直流電壓源  $VR_2$ ，該加法狀態為電容  $C_p$  接收端連接至直流電壓源  $VR_2$ ，電容  $C_n$  接收端連接至直流電壓源  $VR_1$ 。

其中，第十種實施例之正常操作模式之減法狀態可以相對應測試操作模式之加法狀態，同時正常操作模式之加法狀態相對應測試操作模式之減法狀態，且切換電容組可以共用數個類比訊號開關器， $VC_2$  亦可以為  $VR_1$  或  $VR_2$ 。

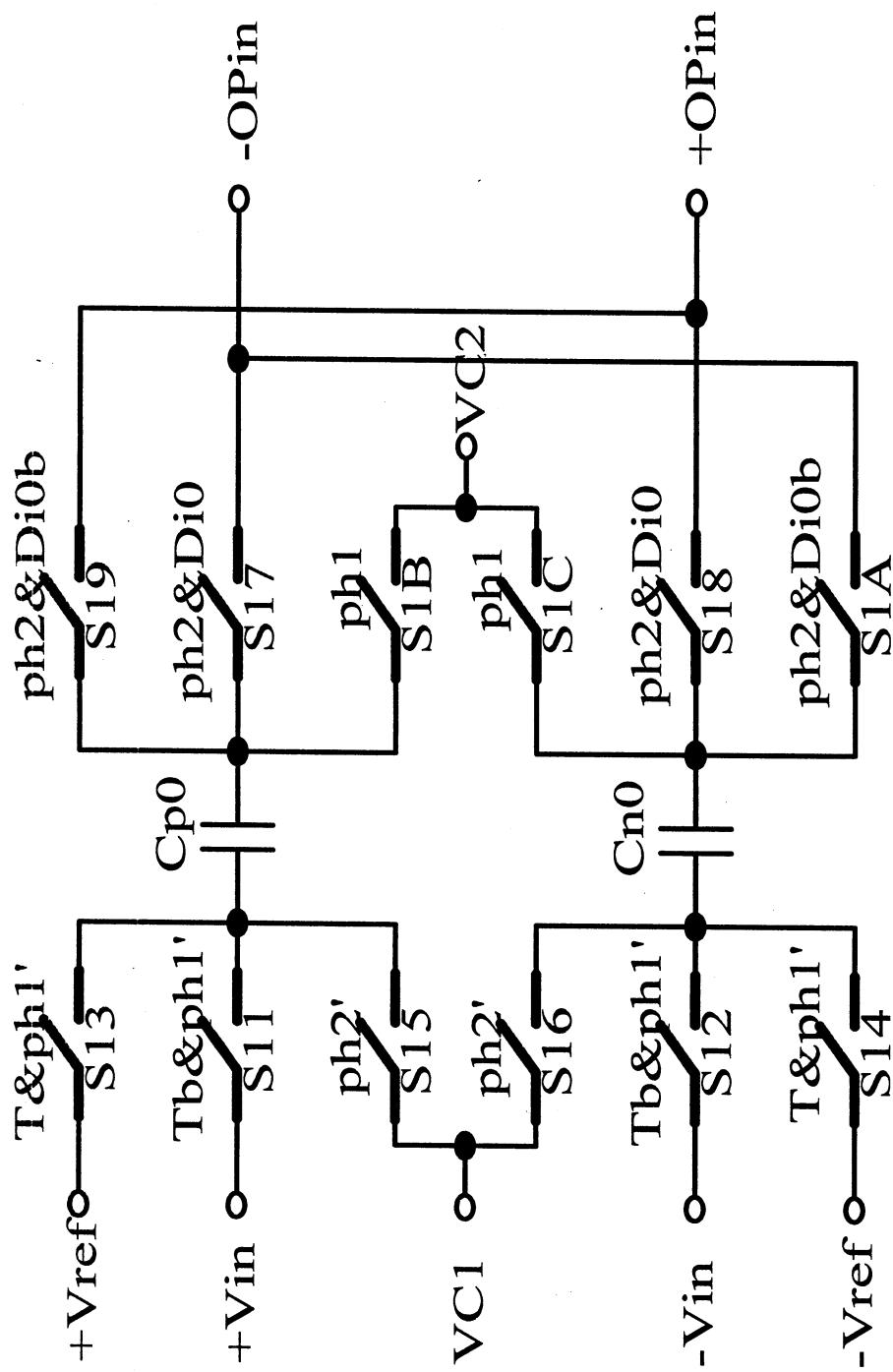

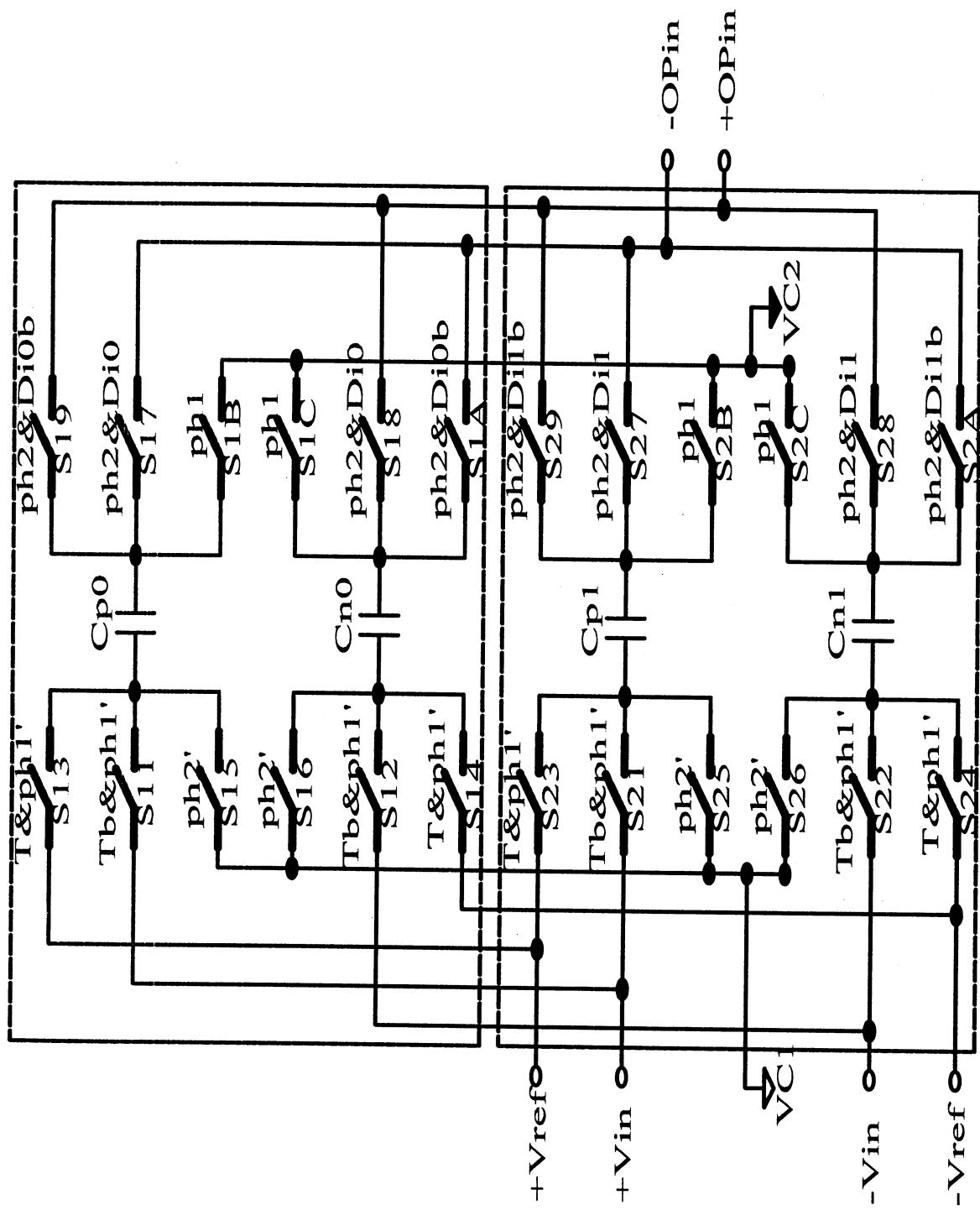

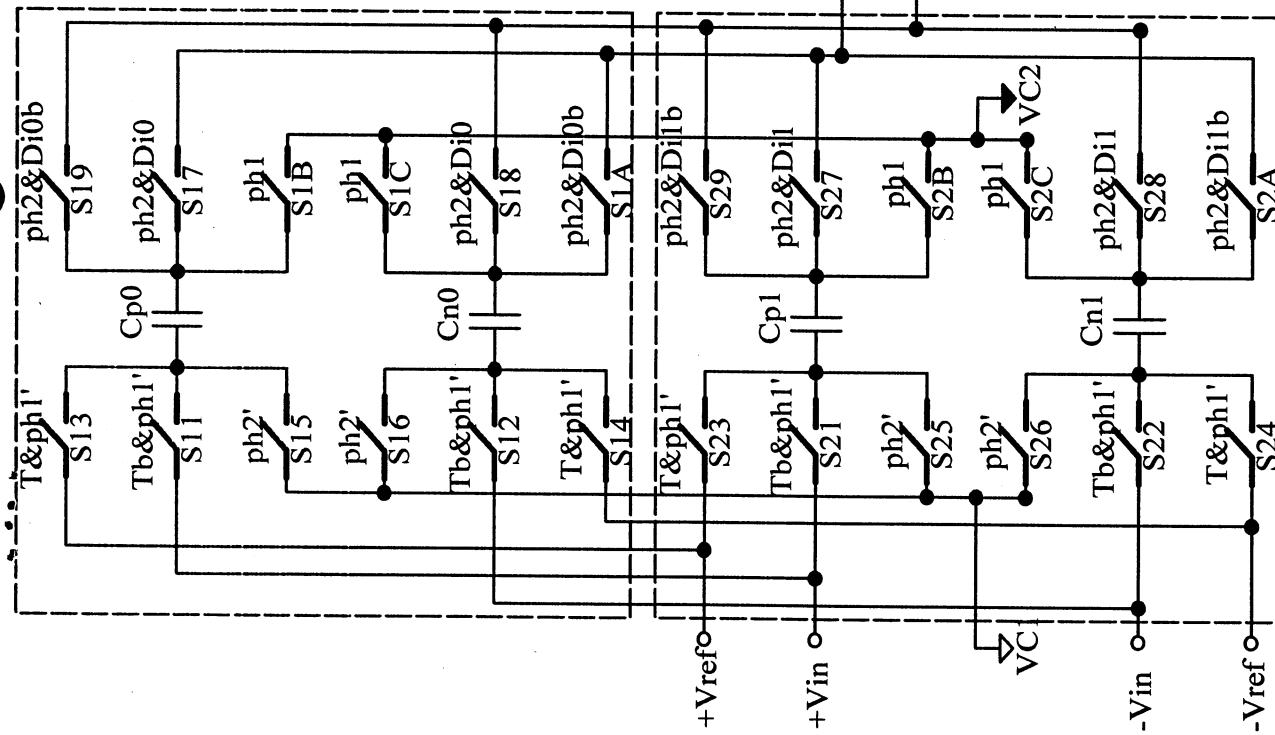

請參閱第十三圖為本發明使用於第三種實施例中一個切換電容組之電路圖。

請參閱第十四圖為本發明第三種實施例使用兩個切換電容組之電路圖。

請參閱第十五圖為本發明第三種實施例使用兩個切換電容組並且該等切換電容組共享數個類比開關器之電路圖。

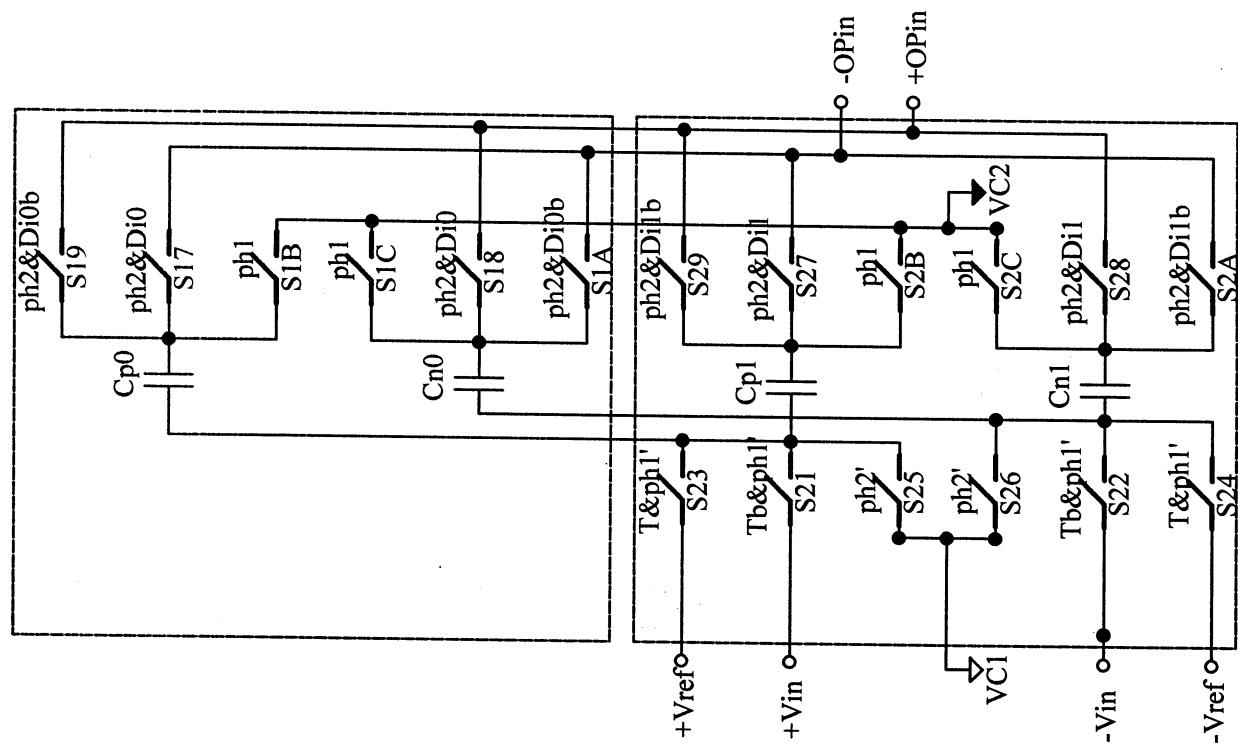

請參閱第十六圖為本發明使用在二階三角積分調變器之一種電路圖，

具有兩個電容組 57、58，此實施例之電路共分兩種工作模式：正常工作模式與測試模式。當  $T=0$ 、 $Tb=1$   $Di0=1$ 、 $Di0b=0$ 、 $Di1=1$  且  $Di1b=0$  時為正常工作模式，本電路接受類比訊號  $\pm Vin$  輸入，為一正常工作之二階三角積分調變器（Modulator）。當  $T=1$  且  $Tb=0$  時則進入測試模式，本電路接受二個單位元（Single-bit）數位激發訊號輸入  $Di0$  和  $Di1$ ，其來源為一經過單位元數位三角積分調變之數位激發波（Digital Stimulus），其中  $Di0b$  和  $Di1b$  係為相對應  $Di0$  和  $Di1$  之反向邏輯訊號，此時  $S1 \sim S8$ 、 $SA \sim SH$ 、 $C0$ 、 $C1$ 、 $C2$  及  $C3$  與運算放大器（opamp）形成兩個一位元（one-bit）的數位類比轉換器（DAC），以作為二階三角積分調變器的測試激發源；其中， $Di0$  和  $Di1$  為相同之單位元數位流（bit-stream），並在兩者之間做適當的延遲（delay），如此相當於使得原有之一位元的數位類比轉換器測試激發信號經過一個有限響應（FIR）低通濾波器，借此來獲得與傳統類比激發源類似的激發源，以提高測試精準度。

另外，由於本發明在兩種操作模式共用所有的電容與運算放大器與大部分的類比開關器，故可得到高測量準確度（High measurement accuracy），且因為所有元件都可被測試因此可以提高錯誤覆蓋率（High fault coverage），並且由於在測試模式下運算放大器（opamp）的電容負載與正常模式下相同，所以可以進行全速度測試（At Speed testing）的功能。

本發明可以應用在各式不同架構、不同階數之三角積分調變器上，不論其為單迴路（Single Loop）或串接式（Cascaded）架構，實施方式只需

要將原本接收類比訊號的輸入級之切換電容電路，以本發明置換即可。在實際運用上，任何切換電容架構的電路，皆可將其輸入端之切換電容電路，以本發明取代，達成以純數位測試訊號取代昂貴之類比激發源測試平台，降低測試成本的目標。

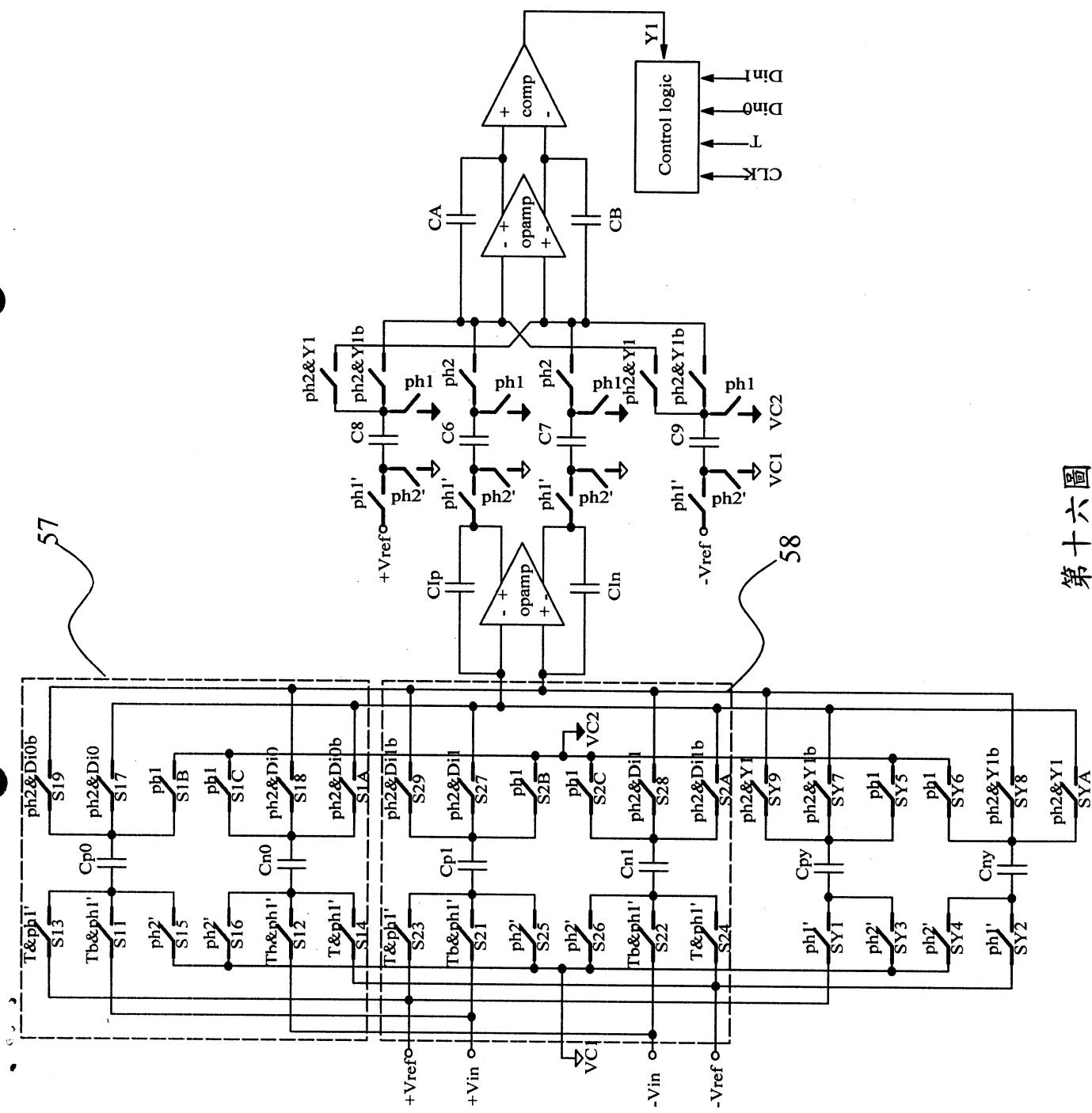

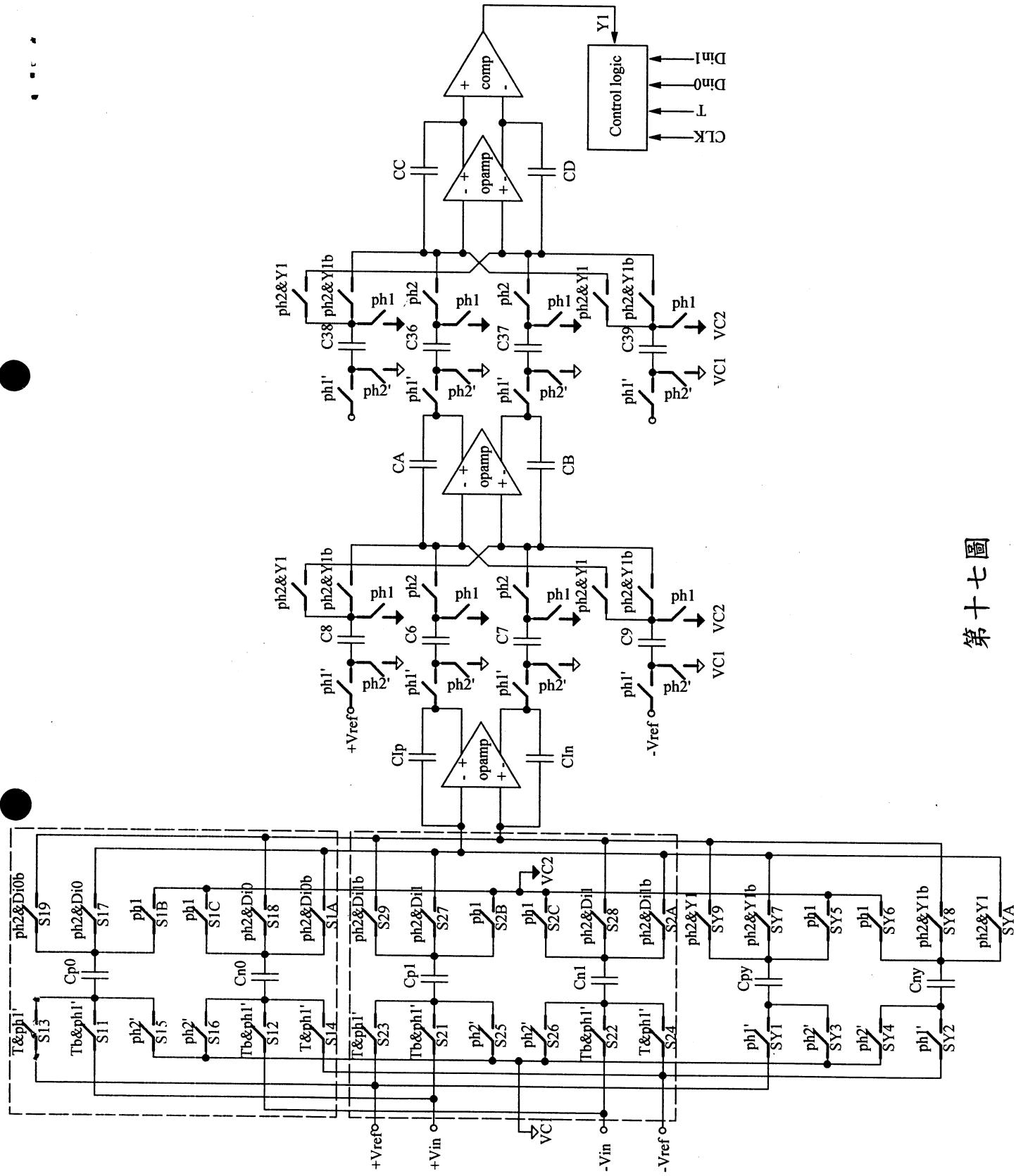

請參閱第十七圖為本發明使用在三階三角積分調變器之電路圖，如同前述二階三角積分調變器（2nd-order Modulator），此三階三角積分調變器（3rd-order Modulator）電路亦只須將第一級的輸入電路做些改變即可，工作模式亦和前述二階三角積分調變器相同。。

請參閱第十八圖為本發明使用在切換電容式低通濾波器之電路圖，此二階低通濾波器（biquad）電路只須將第一級的輸入電路以本發明取代即可達成以純數位測試訊號取代昂貴之類比激發源測試平台，降低測試成本的目標，工作模式亦和前述二階三角積分調變器（2nd-order Modulator）相同。

因此，本發明以三角積分調變為基礎，適用於任一具有切換電容式輸入電路的數位可測試架構，由一個測試模式控制訊號 T 控制待測切換電容式電路之工作模式為正常操作模式或測試模式。在正常操作模式下，本電路接受一類比訊號輸入，在測試模式下，輸入級的切換電容電路被重新規劃成一個或兩個以上並聯之接收數位測試訊號的數位電荷轉換器，以取代傳統上使用昂貴之類比激發源的測試法。

以上所述係藉由實施例說明本發明之特點，其目的在使熟習該技術者能瞭解本發明之內容並據以實施，而非限定本發明之專利範圍，故，凡其

他未脫離本發明所揭示之精神所完成之等效修飾或修改，仍應包含在以下所述之申請專利範圍中。

### 【圖式簡單說明】

第一圖為本發明第一種與第三種實施例之正常操作模式輸入級之操作方法。

第二圖為本發明第一種與第二種實施例之測試模式輸入級之操作方法。

第三圖為本發明第二種與第四種實施例之正常操作模式輸入級之操作方法。

第四圖為本發明第三種與第四種實施例之測試模式輸入級之操作方法。

第五圖為本發明第五種實施例之正常操作模式輸入級之操作方法。

第六圖為本發明第五種實施例之測試模式輸入級之操作方法。

第七圖為本發明第六種與第八種實施例之正常操作模式輸入級之操作方法。

第八圖為本發明第六種與第七種實施例之測試模式輸入級之操作方法。

第九圖為本發明第七種與第九種實施例之正常操作模式輸入級之操作方法。

第十圖為本發明第八種與第九種實施例之測試模式輸入級之操作方法。

第十一圖為本發明之第十種實施例之正常操作模式輸入級之操作方法。

第十二圖為本發明第十種實施例之測試模式輸入級之操作方法。

第十三圖為本發明使用於第三種實施例中一個切換電容組之一種電路實施例。

第十四圖為本發明第三種實施例使用兩個切換電容組之一種電路實施例。

第十五圖為本發明第三種實施例使用兩個切換電容組並且該等切換電容組共享數個類比開關器之電路實施例。

第十六圖為本發明使用在二階三角積分調變器之一種電路實施例。

第十七圖為一種本發明使用在三階三角積分調變器之電路實施例。

第十八圖為本發明使用在切換電容式低通濾波器之電路實施例。

### 【主要元件符號說明】

11、11' 切換電容組                  12、12' 切換電容組

15、16、17、18 類比多工選擇器

21、21' 切換電容組                  22、22' 切換電容組

31、31' 切換電容組                  32、32' 切換電容組

35、36、37、38 類比多工選擇器

41、42 切換電容組                  41' 、42' 切換電容組

55、56 類比多工選擇器                  65、66 類比多工選擇器

57、58 電容組

## 十、申請專利範圍：

1. 一種於類比測試中可接收數位測試激發訊號之可重新規劃 (Reconfigurable) 切換電容 (Switched-Capacitor) 輸入電路，其係應用於具有切換電容式輸入電路的數位可測試架構，該可重新規劃切換電容輸入電路包括：

一類比輸入訊號，其係具有正相電壓訊號及負相電壓訊號；

數個直流電壓源，其係包括：一第一直流電壓源、一第二直流電壓源、一第三直流電壓源、以及一第四直流電壓源；

一運算放大器，其係具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，該運算放大器將該第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於該第一放大器輸出端與該第二放大器輸出端之間；

至少二切換電容組，每一該等切換電容組係由第一電容、第二電容及數個類比訊號開關器組合在一起，每一該等電容具有一個接收端與一個輸出端，且每一該切換電容組具有一相對應之數位激發訊號，每一該數位激發訊號係為一經過數位三角積分調變之數位激發位元流 (Sigma-Delta modulated digital stimulus bit-stream)；以及

一數位開關訊號產生器，其係至少接收一數位模式訊號，一時脈訊號，該等數位激發訊號，並產生數個開關訊號控制該等切換電容組之類比訊號開關器，且該數位模式訊號，具有兩個邏輯狀態，包括正常狀態及測試狀態，該時脈訊號係用以產生至少二不重疊之時脈相位 (clock phases) 包括第一時脈相位及第二時脈相位。

2. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，在該數位模式訊號為測試狀態時，該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，其係依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之電容輸出端連接至該第四直流電壓源，並且該第一數位激發訊號控制該第一切換電容組，及該第二數位激發訊號控制該第二切換電容組，以切換相對應之該等切換電容組內之電容接收端之連接為增加狀態或減少狀態，且該增加狀態為該等切換電容組之第一電容接收端連接至該第一直流電壓源，該等切換電容組之第二電容接收端連接至該第二直流電壓源，該減少狀態為該等切換電容組之第一電容接收端連接至該第二直流電壓源，該等切換電容組之第二電容接收端連接至該第一直流電壓源；以及在該第二時脈相位內，該等切換電容組之該等電容接收端接至該第三直流電壓源，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

3. 如申請專利範圍第 2 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第一數位激發訊號之增加狀態相對應該第二數位激發訊號之減少狀態，並且該第一數位激發訊號之減少狀態相對應該第二數位激發訊號之增加狀態。

4. 如申請專利範圍第 2 項所述之於類比測試中可接收數位測試激發訊號之

可重新規劃切換電容輸入電路，該等切換電容組之電容及該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，該等切換電容組之電容輸出端連接至該第四直流電壓源；以及在該第二時脈相位內，該等切換電容組之電容接收端連接至該第三直流電壓源，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

5. 如申請專利範圍第 4 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之該第一時脈相位相對應該測試操作模式之該第二時脈相位且該正常操作模式之該第二時脈相位相對應該測試操作模式之該第一時脈相位。

6. 如申請專利範圍第 4 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電

容組之第二電容之輸出端連接至該運算放大器之第二輸入端，以及在該第二時脈相位內，該等切換電容組之電容接收端接至第三直流電壓源，並且該等切換電容組之電容輸出端接至第四直流電壓源。

7. 如申請專利範圍第 6 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之該第一時脈相位相對應該測試操作模式之該第二時脈相位且該正常操作模式之該第二時脈相位相對應該測試操作模式之該第一時脈相位。

8. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該等切換電容組共用數個類比訊號開關器。

9. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第三直流電壓源為該第一直流電壓源或該第二直流電壓源。

10. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第四直流電壓源為該第一直流電壓源、該第二直流電壓源或該第三直流電壓源。

11. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第二數位激發訊號與該第一數位激發訊號相同，但比該第一數位激發訊號延遲數個週期。

12. 如申請專利範圍第 4 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該等時脈相位切換該

等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位及該第二時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，且該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

13. 如申請專利範圍第4項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該運算放大器位於一待測電路中，且該待測電路至少包含第一回授電容與第二回授電容，該第一回授電容之輸出端連接至該運算放大器之第一放大器輸出端，該第一回授電容之輸入端連接至該運算放大器之第一輸入端；以及該第二回授電容之輸出端連接至該運算放大器之第二放大器輸出端，該第二回授電容之輸入端連接至該運算放大器之第二輸入端。

14. 如申請專利範圍第1項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，在該數位模式訊號為測試狀態時，該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，其係依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之電容輸出端連接至第四直流電壓源，該等切換電容組之第一電容接收端連接至該第一直流電壓源，該等切換電容組之第二電容接收端連接至該第二直流電壓源；以及在該第二

時脈相位內，該等切換電容組之該等電容接收端接至該第三直流電壓源，並且該第一數位激發訊號控制該第一切換電容組，及該第二數位激發訊號控制該第二切換電容組，以切換相對應之該等切換電容組內之電容輸出端之連接為增加狀態或減少狀態，且該增加狀態為該等切換電容組之第一電容輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容輸出端連接至該運算放大器之第二輸入端，該減少狀態為該等切換電容組之第一電容輸出端連接至該運算放大器之第二輸入端，該等切換電容組之第二電容輸出端連接至該運算放大器之第一輸入端。

15. 如申請專利範圍第 14 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第一數位激發訊號之增加狀態相對應該第二數位激發訊號之減少狀態，並且該第一數位激發訊號之減少狀態相對應該第二數位激發訊號之增加狀態。

16. 如申請專利範圍第 14 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該等切換電容組之電容及該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，該等切換電容組之電容輸出端連接至該第四直流電壓源；以及在該第二時

脈相位內，該等切換電容組之電容接收端連接至該第三直流電壓源，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

17. 如申請專利範圍第 16 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之該第一時脈相位相對應該測試操作模式之該第二時脈相位且該正常操作模式之該第二時脈相位相對應該測試操作模式之該第一時脈相位。

18. 如申請專利範圍第 16 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端，以及在該第二時脈相位內，該等切換電容組之電容接收端接至第三直流電壓源，並且該等切換電容組之電容輸出端接至第四直流電壓源。

19. 如申請專利範圍第 18 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之該第一時脈相位相對應該測試操作模式之該第二時脈相位且該正常操作模式之該第二時脈相位相對應該測試操作模式之該第一時脈相位。

20. 如申請專利範圍第 16 項所述之於類比測試中可接收數位測試激發訊號

之可重新規劃切換電容輸入電路，該正常操作模式依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位及該第二時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，且該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

21. 如申請專利範圍第 16 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該運算放大器位於一待測電路中，且該待測電路至少包含第一回授電容與第二回授電容，該第一回授電容之輸出端連接至該運算放大器之第一放大器輸出端，該第一回授電容之輸入端連接至該運算放大器之第一輸入端；以及該第二回授電容之輸出端連接至該運算放大器之第二放大器輸出端，該第二回授電容之輸入端連接至該運算放大器之第二輸入端。

22. 如申請專利範圍第 1 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第三直流電壓源為該第四直流電壓源，且該數位開關訊號產生器係接收該數位模式訊號，該時脈訊號，該等數位激發訊號，以及一數位資料訊號並產生數個開關訊號控制該等切換電容組之類比訊號開關器；在該數位模式訊號為測試狀態時該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，其係依據該等時

脈相位切換每一該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之電容輸出端連接至第四直流電壓源，並且該第一數位激發訊號控制該第一切換電容組，及該第二數位激發訊號控制該第二切換電容組，以切換相對應之該等切換電容組內之電容接收端之連接為增加狀態或減少狀態，且該增加狀態為該等切換電容組之第一電容接收端連接至該第一直流電壓源，該等切換電容組之第二電容接收端連接至該第二直流電壓源，該減少狀態為該等切換電容組之第一電容接收端連接至該第二直流電壓源，該等切換電容組之第二電容接收端連接至該第一直流電壓源；以及在該第二時脈相位內，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端，並且該數位資料訊號控制該第一切換電容組及該第二切換電容組，以切換該等切換電容組內之電容接收端之連接為減法狀態或加法狀態，且該減法狀態為該等切換電容組之第一電容接收端連接至該第一直流電壓源，該等切換電容組之第二電容接收端連接至該第二直流電壓源，該加法狀態為該等切換電容組之第一電容接收端連接至該第二直流電壓源，該等切換電容組之第二電容接收端連接至該第一直流電壓源。

23. 如申請專利範圍第 22 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第一數位激發訊號之增加狀態相對應該第二數位激發訊號之減少狀態，並且該第一數位激發訊號之減少狀態相對應該第二數位激發訊號之增加狀態。

24. 如申請專利範圍第 22 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該等切換電容組之電容及該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換每一該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，該等切換電容組之電容輸出端連接至該第四直流電壓源；以及在該第二時脈相位內，該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端，並且該數位資料訊號控制該第一切換電容組及該第二切換電容組，以切換該等切換電容組內之電容接收端之連接為減法狀態或加法狀態，且該減法狀態為該等切換電容組之第一電容接收端連接至該第一直流電壓源，該等切換電容組之第二電容接收端連接至該第二直流電壓源，該加法狀態為該等切換電容組之第一電容接收端連接至該第二直流電壓源，該等切換電容組之第二電容接收端連接至該第一直流電壓源。

25. 如申請專利範圍第 24 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之減法狀態相對應該測試操作模式之加法狀態，且該正常操作模式之加法狀態相對應該測試操作模式之減法狀態。

26. 如申請專利範圍第 24 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該等時脈相位切換該等切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位及該第二時脈相位內，該等切換電容組之第一電容接收端連接至該類比輸入正相電壓訊號，該等切換電容組之第二電容接收端連接至該類比輸入負相電壓訊號，且該等切換電容組之第一電容之輸出端連接至該運算放大器之第一輸入端，該等切換電容組之第二電容之輸出端連接至該運算放大器之第二輸入端。

27. 如申請專利範圍第 24 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該運算放大器位於一待測電路中，且該待測電路至少包含第一回授電容與第二回授電容，該第一回授電容之輸出端連接至該運算放大器之第一放大器輸出端，該第一回授電容之輸入端連接至該運算放大器之第一輸入端；以及該第二回授電容之輸出端連接至該運算放大器之第二放大器輸出端，該第二回授電容之輸入端連接至該運算放大器之第二輸入端。

28. 一種於類比測試中可接收數位測試激發訊號之可重新規劃 (Reconfigurable) 切換電容 (Switched-Capacitor) 輸入電路，其係應用於具有切換電容式輸入電路的數位可測試架構，該可重新規劃切換電容輸入電路包括：

一類比輸入訊號，其係具有正相電壓訊號及負相電壓訊號；

數個直流電壓源，其係包括：一第一直流電壓源、一第二直流電壓源、以

及一第三直流電壓源；

一運算放大器，其係具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，該運算放大器將該第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於該第一放大器輸出端與該第二放大器輸出端之間；

至少一切換電容組，其係由第一電容、第二電容及數個類比訊號開關器組合在一起，該第一電容及該第二電容具有一個接收端與一個輸出端，該切換電容組具有一相對應之數位激發訊號，該數位激發訊號係為一經過數位三角積分調變之數位激發位元流（Sigma-Delta modulated digital stimulus bit-stream）；以及

一數位開關訊號產生器，其係至少接收一數位模式訊號，一時脈訊號，該數位激發訊號，並產生數個開關訊號控制該切換電容組之類比訊號開關器，且該數位模式訊號具有兩個邏輯狀態，包括正常狀態及測試狀態，該時脈訊號係用以產生至少二不重疊之時脈相位（clock phases）包含第一時脈相位及第二時脈相位。

29. 如申請專利範圍第 28 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，在該數位模式訊號為測試狀態時，該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，該測試操作模式係依據該等時脈相位切換該切換電容組內之電容接收端及輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該第一直流

電壓源，該第二電容接收端連接至該第二直流電壓源，該電容組之電容輸出端連接至該第三直流電壓源；以及在該第二時脈相位內，該第一電容接收端連接至該第二直流電壓源，該第二電容接收端連接至該第一直流電壓源，並且該數位激發訊號控制相對應之該切換電容組，以切換該切換電容組內之電容輸出端之連接為增加狀態或減少狀態，且該增加狀態為該第一電容輸出端連接至該運算放大器之第一輸入端，該第二電容輸出端連接至該運算放大器之第二輸入端，該減少狀態為該第一電容輸出端連接至該運算放大器之第二輸入端，該第二電容輸出端連接至該運算放大器之第一輸入端。

30. 如申請專利範圍第 29 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該等切換電容組之電容與該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換該切換電容組內之電容接收端及輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該類比輸入正相電壓訊號，該第二電容接收端連接至該類比輸入負相電壓訊號，該切換電容組之電容輸出端連接至該第三直流電壓源；以及在該第二時脈相位內，該切換電容組之電容接收端連接至該第二直流電壓源，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端。

31. 如申請專利範圍第 30 項所述之於類比測試中可接收數位測試激發訊號

之可重新規劃切換電容輸入電路，其中，該正常操作模式之第一時脈相位對應該測試操作模式之第二時脈相位且該正常操作模式之第二時脈相位對應該測試操作模式之第一時脈相位。

32. 如申請專利範圍第 29 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該時脈訊號產生之二不重疊時脈相位切換該切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該類比輸入正相電壓訊號，該第二電容接收端連接至該類比輸入負相電壓訊號，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端；以及在該第二時脈相位內，該切換電容組之電容接收端連接至該第二直流電壓源，該切換電容組之電容輸出端連接至該第三直流電壓源。

33. 如申請專利範圍第 32 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之第一時脈相位對應該測試操作模式之第二時脈相位且該正常操作模式之第二時脈相位對應該測試操作模式之第一時脈相位。

34. 如申請專利範圍第 28 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中包含至少二切換電容組以及與該等切換電容組相對應之至少二數位激發訊號，該第二數位激發訊號與該第一數位激發訊號相同，但比該第一數位激發訊號延遲數個週期。

35. 如申請專利範圍第 34 項所述之於類比測試中可接收數位測試激發訊號

之可重新規劃切換電容輸入電路，其中，該等切換電容組共用數個類比訊號開關器。

36. 如申請專利範圍第 35 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第三直流電壓源為該第一直流電壓源或該第二直流電壓源。

37. 如申請專利範圍第 36 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第一數位激發訊號之增加狀態相對應該第二數位激發訊號之減少狀態，並且該第一數位激發訊號之減少狀態相對應該第二數位激發訊號之增加狀態。

38. 如申請專利範圍第 29 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該運算放大器位於一待測電路中，且該待測電路至少包含第一回授電容與第二回授電容，該第一回授電容之輸出端連接至該運算放大器之第一放大器輸出端，該第一回授電容之輸入端連接至該運算放大器之第一輸入端；以及該第二回授電容之輸出端連接至該運算放大器之第二放大器輸出端，該第二回授電容之輸入端連接至該運算放大器之第二輸入端。

39. 如申請專利範圍第 28 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，在該數位模式訊號為測試狀態時，該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，該測試操作模式係依據該等時脈相位切換該切換電容組內之電容接收端及輸

出端之連接，在該第一時脈相位內，該第一電容輸出端連接至該第三直流電壓源，該第二電容輸出端連接至該第三直流電壓源，並且該數位激發訊號控制相對應之該切換電容組，以切換該切換電容組內之電容接收端之連接為增加狀態或減少狀態，且該增加狀態為該第一電容接收端連接至該第一直流電壓源，該第二電容接收端連接至該第二直流電壓源，該減少狀態為該第一電容接收端連接至該第二直流電壓源，該第二電容接收端連接至該第一直流電壓源，以及在該第二時脈相位內，該第一電容接收端連接至該第二直流電壓源及輸出端連接至該運算放大器之第一輸入端，該第二電容接收端連接至該第二直流電壓源及輸出端連接至該運算放大器之第二輸入端。

40. 如申請專利範圍第 39 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該等切換電容組之電容與該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換該切換電容組內之電容接收端及輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該類比輸入正相電壓訊號，該第二電容接收端連接至該類比輸入負相電壓訊號，該切換電容組之電容輸出端連接至該第三直流電壓源；以及在該第二時脈相位內，該切換電容組之電容接收端連接至該第二直流電壓源，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端。

41. 如申請專利範圍第 40 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之第一時脈相位對應該測試操作模式之第二時脈相位且該正常操作模式之第二時脈相位對應該測試操作模式之第一時脈相位。

42. 如申請專利範圍第 39 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該正常操作模式依據該時脈訊號產生之二不重疊時脈相位切換該切換電容組內之電容接收端或輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該類比輸入正相電壓訊號，該第二電容接收端連接至該類比輸入負相電壓訊號，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端；以及在該第二時脈相位內，該切換電容組之電容接收端連接至該第二直流電壓源，該切換電容組之電容輸出端連接至該第三直流電壓源。

43. 如申請專利範圍第 42 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之第一時脈相位對應該測試操作模式之第二時脈相位且該正常操作模式之第二時脈相位對應該測試操作模式之第一時脈相位。

44. 如申請專利範圍第 39 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該運算放大器位於一待測電路中，且該待測電路至少包含第一回授電容與第二回授電容，該第一回授電容之輸出端連接至該運算放大器之第一放大器輸出端，該第一回授電容之輸入

端連接至該運算放大器之第一輸入端；以及該第二回授電容之輸出端連接至該運算放大器之第二放大器輸出端，該第二回授電容之輸入端連接至該運算放大器之第二輸入端。

45. 一種於類比測試中可接收數位測試激發訊號之可重新規劃（Reconfigurable）切換電容（Switched-Capacitor）輸入電路，其係應用於具有切換電容式輸入電路的數位可測試架構，該可重新規劃切換電容輸入電路包括：

一類比輸入訊號，其係具有正相電壓訊號及負相電壓訊號；

一數位資料訊號，具有兩個邏輯狀態，包括加法狀態及減法狀態；

數個直流電壓源，其係包括：一第一直流電壓源、一第二直流電壓源、以及一第三直流電壓源；

一運算放大器，其係具有第一輸入端、第二輸入端、第一放大器輸出端及第二放大器輸出端，該運算放大器將該第二輸入端及第一輸入端之電壓差予以放大產生一輸出電壓於該第一放大器輸出端與該第二放大器輸出端之間；

至少一切換電容組，其係由第一電容、第二電容及數個類比訊號開關器組合在一起，該第一電容及該第二電容具有一個接收端與一個輸出端，該切換電容組具有一相對應之數位激發訊號，該數位激發訊號係為一經過數位三角積分調變之數位激發位元流（Sigma-Delta modulated digital stimulus bit-stream）；以及

一數位開關訊號產生器，其係至少接收一數位模式訊號，該數位資料訊號，

一時脈訊號，該數位激發訊號，並產生數個開關訊號控制該切換電容組之類比訊號開關器，且該數位模式訊號具有兩個邏輯狀態，包括正常狀態及測試狀態，該時脈訊號係用以產生至少二不重疊之時脈相位(clock phases)包含第一時脈相位及第二時脈相位。

46. 如申請專利範圍第 45 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，在該數位模式訊號為測試狀態時，該數位開關訊號產生器產生數個開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一測試操作模式下運作，該測試操作模式係依據該時脈相位切換該切換電容組內之電容接收端及輸出端之連接，在該第一時脈相位內，該切換電容組之電容輸出端連接至第三直流電壓源，並且該數位激發訊號控制該第一電容及該第二電容接收端之連接為增加狀態或減少狀態，且該增加狀態為該第一電容接收端連接至該第一直流電壓源，該第二電容接收端連接至該第二直流電壓源，該減少狀態為該第一電容接收端連接至該第二直流電壓源，該第二電容接收端連接至該第一直流電壓源；以及在該第二時脈相位內，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端，並且該數位資料訊號控制該切換電容組，以切換該切換電容組內之電容接收端之連接為減法狀態或加法狀態，且該減法狀態為該第一電容接收端連接至該第一直流電壓源，該第二電容接收端連接至該第二直流電壓源，該加法狀態為該第一電容接收端連接至該第二直流電壓源，該第二電容接收端連接至該第一直流電壓源。

47. 如申請專利範圍第 46 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，該等切換電容組之電容與該運算放大器係位於一待測電路之中，該數位模式訊號為正常狀態時，該數位開關訊號產生器產生該等開關訊號控制該等切換電容組之類比訊號開關器，使該可重新規劃切換電容輸入電路在一正常操作模式下運作，其係依據該等時脈相位切換該切換電容組內之電容接收端及輸出端之連接，在該第一時脈相位內，該第一電容接收端連接至該類比輸入正相電壓訊號，該第二電容接收端連接至該類比輸入負相電壓訊號，該切換電容組之電容輸出端連接至該第三直流電壓源；以及在該第二時脈相位內，該第一電容之輸出端連接至該運算放大器之第一輸入端，該第二電容之輸出端連接至該運算放大器之第二輸入端，並且該數位資料訊號控制該切換電容組，以切換該切換電容組內之電容接收端之連接為減法狀態或加法狀態，且該減法狀態為該第一電容接收端連接至該第一直流電壓源，該第二電容接收端連接至該第二直流電壓源，該加法狀態為該第一電容接收端連接至該第二直流電壓源，該第二電容接收端連接至該第一直流電壓源。

48. 如申請專利範圍第 47 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該正常操作模式之減法狀態相對應該測試操作模式之加法狀態，且該正常操作模式之加法狀態相對應該測試操作模式之減法狀態。

49. 如申請專利範圍第 45 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，更包含至少二切換電容組以及與

該等切換電容組相對應之至少二數位激發訊號，該第二數位激發訊號與該第一數位激發訊號相同，但比該第一數位激發訊號延遲數個週期。

50. 如申請專利範圍第 49 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該等切換電容組共用數個類比訊號開關器。

51. 如申請專利範圍第 50 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第一數位激發訊號之增加狀態相對應該第二數位激發訊號之減少狀態，並且該第一數位激發訊號之減少狀態相對應該第二數位激發訊號之增加狀態。

52. 如申請專利範圍第 51 項所述之於類比測試中可接收數位測試激發訊號之可重新規劃切換電容輸入電路，其中，該第三直流電壓源為該第一直流電壓源或該第二直流電壓源。

200713836

第一圖

200713836

第二圖

200713836

第三圖

200713836

第四圖

200713836

第五圖

200713836

第六圖

200713836

第七圖

200713836

第八圖

200713836

第九圖

(B)

(A)

200713836

第十圖

200713836

第十一圖

200713836

200713836

第十三圖

200713836

第十四圖

200713836

第十五圖

200713836

第十六圖

200713836

圖十七第

200713836

第十八圖