### (19) United States

# (12) Patent Application Publication

(10) Pub. No.: US 2014/0084971 A1 Mar. 27, 2014 (43) **Pub. Date:**

#### (54) FREQUENCY MULTIPLIER APPARATUS AND OPERATING METHOD THEREOF

- (71) Applicant: National Chiao Tung University, Hsinchu City (TW)

- Inventors: Chien-Nan Kuo, Hsinchu (TW); Tzu-Chao Yan, Tainan (TW)

- (73) Assignee: National Chiao Tung University, Hsinschu City (TW)

- Appl. No.: 13/896,950

- (22) Filed: May 17, 2013

(21)

Foreign Application Priority Data (30)

Sep. 21, 2012 (TW) ...... 101134839

#### **Publication Classification**

(51) Int. Cl. H03B 19/00 (2006.01)

U.S. Cl.

ABSTRACT (57)

The present invention provides a frequency multiplier apparatus. The frequency multiplier apparatus includes an injection-locked frequency multiplier and a frequency-to-control signal converter. The injection-locked frequency multiplier outputs an output signal having a first frequency in response to an input signal having a first basic frequency. The frequency-to-control signal converter provides a first control signal to the injection-locked frequency multiplier in response to the input signal. The injection-locked frequency multiplier adjusts the first frequency to a second frequency in response to a change of the first control signal when the first basic frequency is changed to a second basic frequency.

Fig. 1 (Prior Art)

Fig. 2 (Prior Art)

Fig. 3(a)

Fig. 3(b)

Fig. 3(c)

Fig. 5(a)

Fig. 5(b)

Fig. 6

Fig. 7(a)

Fig. 7(b)

Fig. 8(a)

Fig. 8(b)

### FREQUENCY MULTIPLIER APPARATUS AND OPERATING METHOD THEREOF

### CROSS REFERENCE TO RELATED APPLICATION AND CLAIM OF PRIORITY

[0001] The present invention claims the benefits of priority from the Taiwanese Patent Application No. 101134839, filed on Sep. 21, 2012, the contents of the specification of which are hereby incorporated herein by reference.

#### FIELD OF THE INVENTION

[0002] The present invention relates to a frequency multiplier apparatus and the operating methods thereof, particularly an auto-adjustable frequency multiplier apparatus and the operating methods thereof.

#### BACKGROUND OF THE INVENTION

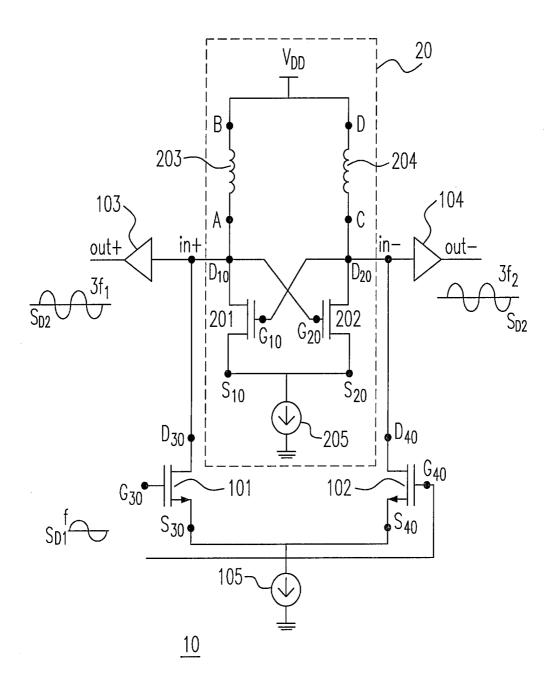

[0003] Due to the restriction of the injection-locking mechanism, the lockable bandwidth of output signals of ordinary injection-locked frequency multiplier is small, and therefore the range of operable frequencies of the output signals thereof is limited. Please refer to FIG. 1, which illustrates an injection-locked frequency multiplier 10 according to the prior art. The injection-locked frequency multiplier 10 includes an oscillator 20 with transistors 201, 201, inductors 203, 204, and a current source 205. The injection-locked frequency multiplier 10 further includes transistors 101, 102, buffers 103, 104 and a current source 105. The buffers 103, 104 have input terminals in+, in- and output terminals out+, out-, respectively.

[0004] The oscillation frequency of the oscillator 20 is fixed, relevant to the amount of the parasitic capacitance (not shown) due to the capacitors 201, 202 and the inductors 203, 204, and to be locked at M times of basic frequency f of a differential signal  $S_{D1}$  by using harmonic signals  $S_{D2}$ ,  $S_{D3}$ , which are generated by inputted the differential signal  $S_{D1}$ into gates G<sub>30</sub>, G<sub>40</sub> of the transistors 101, 102, respectively. M is the ratio of injection-locked frequency multiplier. Accordingly, the range of the lockable frequency is relatively small. When there is a need to adjust the output frequency of the injection-locked frequency multiplier, not only the basic frequency f of the differential signal  $S_{D1}$  but also the resonated frequency of oscillator 20 which is determined by capacitances of capacitors 201, 202 and the inductances of inductors 203, 204 should be changed. Therefore, another type of injection-locked frequency multiplier is provided for improving the abovementioned deficiency.

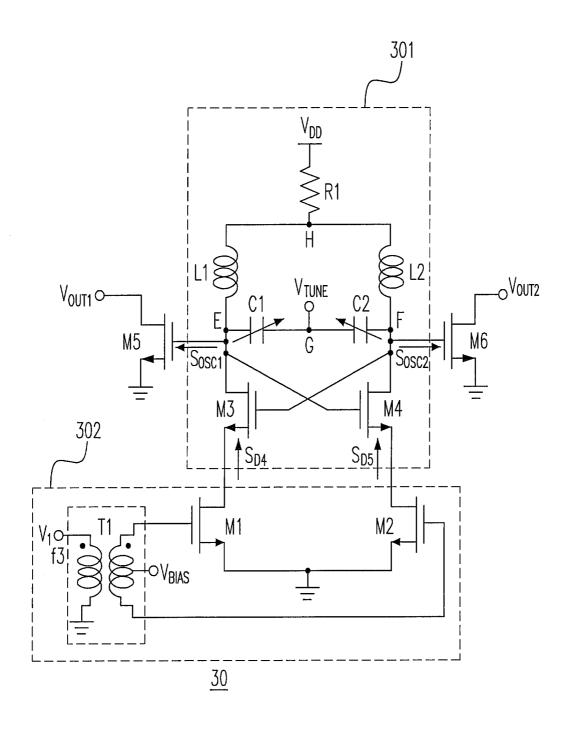

[0005] Please refer to FIG. 2, which illustrates another injection-locked frequency multiplier by 3 times 30 according to the prior art. The injection-locked frequency multiplier 30 includes a varactor tuned and voltage controlled oscillator 301 and a harmonic generator 302. The oscillator 301 includes inductors L1, L2, capacitors C1, C2, transistors M3, M4 and a resister R1. The harmonic generator 302 includes transistors M1, M2 and a power transformer T1, which is an element disposed outer to the chip and having a primary side and a secondary side.

[0006] Referring to FIG. 2, a voltage V1 with a basic frequency f3 is applied to the primary side of the power transformer T1. When adjusting a gate bias  $V_{BLAS}$  of the transistor M1, M2, the harmonic generator 302 can generate harmonic signals  $S_{H1}$ ,  $S_{H2}$  with largest gain and a frequency  $3f_3$  being triple of the basic frequency f3. A tuning voltage  $V_{TUNE}$  is

applied to the location G to adjust the capacitances of the capacitors C1, C2, so as to increase the injection-locked range of the resonance frequency. The resistor R1 is for improving the harmonic rejection ratios. Eventually, resonance frequency signals  $S_{OSC1}$ ,  $S_{OSC2}$  are outputted at the drains of the transistors M3, M4, and the frequencies  $f_{OSC1}$ ,  $f_{OSC2}$  of the outputted signals are equal to the triple frequency  $3f_3$ .

[0007] According to the above-mentioned, it is necessary to adjust the basic frequency f3 and manually adjust the voltage VTUNE when one would like to obtain required resonance frequencies  $f_{OSC1}$ ,  $f_{OSC2}$ , which is inconvenient. Besides, it is not easy to adjust the frequencies  $f_{OSC1}$ ,  $f_{OSC2}$  using the capacitors C1, C2, since the parasitic capacitance of the transistors M3, M4 are usually larger than the capacitance of the capacitors C1, C2. According, the injection-locked range of the resonance frequencies  $f_{OSC1}$ ,  $f_{OSC2}$  is limited. Therefore, there is a need to develop an adjustable frequency multiplier apparatus and the operating methods thereof.

#### SUMMARY OF THE INVENTION

[0008] To achieve the abovementioned advantages, the present invention provides a frequency multiplier apparatus. The frequency multiplier apparatus includes an injection-locked frequency multiplier and a frequency-to-control signal converter. The injection-locked frequency multiplier outputs an output signal having a first frequency in response to an input signal having a first basic frequency. The frequency-to-control signal converter provides a first control signal to the injection-locked frequency multiplier in response to the input signal. The injection-locked frequency multiplier adjusts the first frequency to a second frequency in response to a change of the first control signal when the first basic frequency is changed to a second basic frequency.

[0009] In accordance with another aspect of the present invention, a method for operating a frequency multiplier apparatus is provided. The method includes steps of: (a) outputting an output signal having a first frequency in response to an input signal having a first basic frequency; (b) outputting a control signal in response to the input signal; and (c) adjusting the first frequency to a second frequency in response to a change of the control signal, when the first basic frequency is changed to a second basic frequency.

[0010] In accordance with a further aspect of the present invention, a method for operating a frequency multiplier apparatus is provided. The method includes steps of: (a) generating a predetermined operating frequency; (b) generating a control signal in response to the predetermined operating frequency; and (c) outputting a required frequency in response to the control signal.

**[0011]** The frequency multiplier apparatus and operating method thereof can obtain and lock resonance frequencies at a larger bandwidth scope by automatically adjusting the frequency multiplier apparatus, and therefore the convenience as well as flexibility for use is improved.

[0012] The above objects and advantages of the present invention will be more readily apparent to those ordinarily skilled in the art after reading the details set forth in the descriptions and drawings that follow, in which:

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0013] FIG. 1 is a schematic diagram showing one injection-locked frequency multiplier according to the prior art;

[0014] FIG. 2 is a schematic diagram showing another injection-locked frequency multiplier according to the prior art:

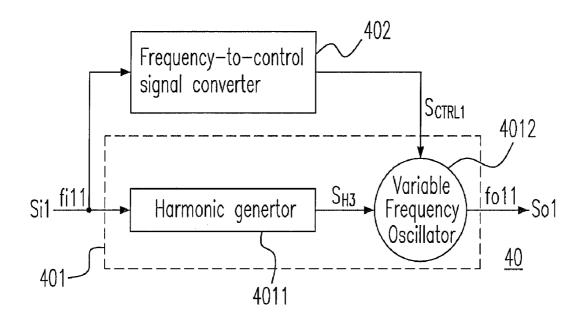

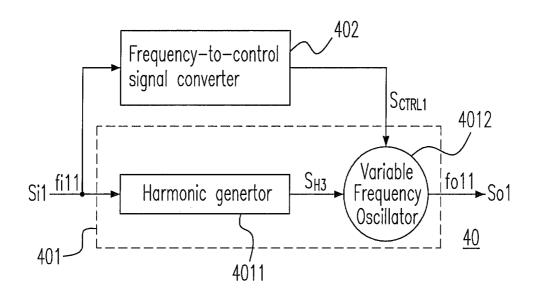

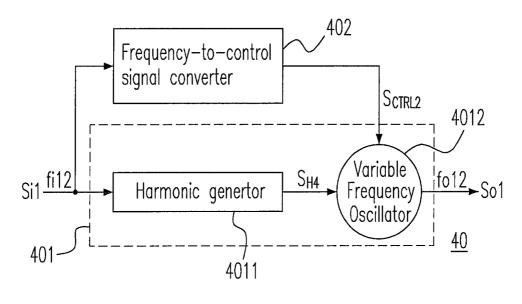

[0015] FIGS. 3(a) and 3(b) are schematic diagrams showing a frequency multiplier apparatus in accordance with one embodiment of the present invention, wherein 4011 denotes a harmonic generator;

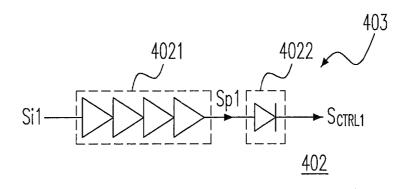

[0016] FIG. 3 (c) is a schematic diagram showing a frequency-to-control signal converter in accordance with one embodiment of the present invention;

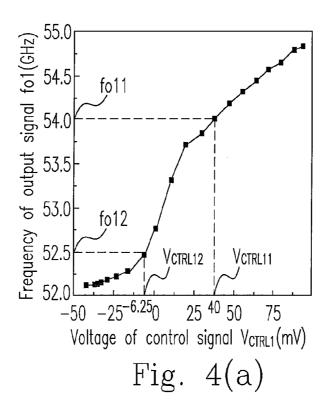

[0017] FIG. 4(a) is a schematic diagram showing the relation between the frequency of output signal and the voltage of the control signal in accordance with one embodiment of the present invention;

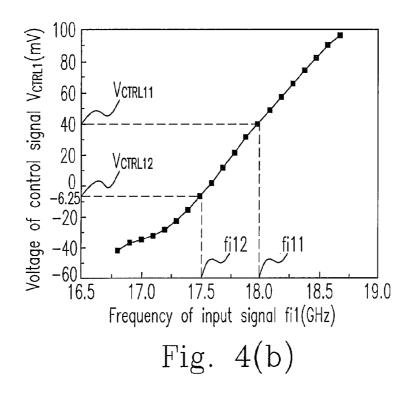

[0018] FIG. 4(b) is a schematic diagram showing the relation between the frequency of input signal and the voltage of the control signal in accordance with one embodiment of the present invention;

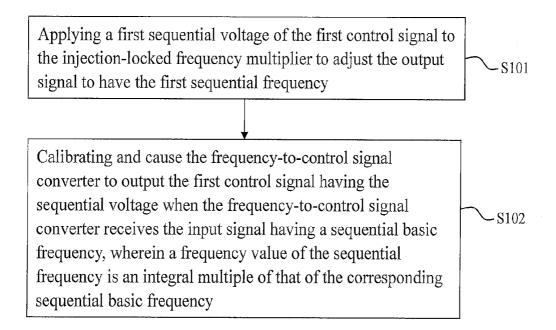

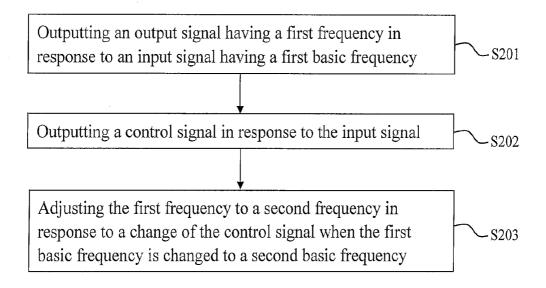

[0019] FIGS. 5(a) and 5(b) are flow diagrams showing the operation method of the frequency multiplier apparatus in accordance with one embodiment of the present invention;

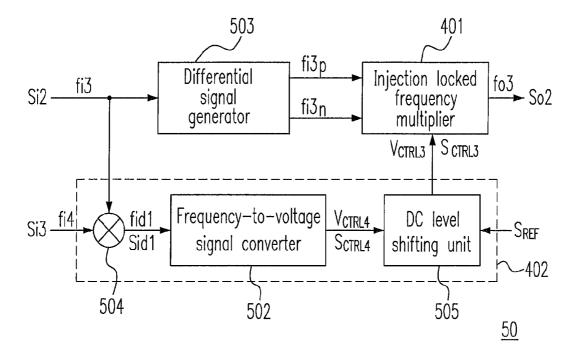

[0020] FIG. 6 is a schematic diagram showing a frequency multiplier apparatus in accordance with another embodiment of the present invention;

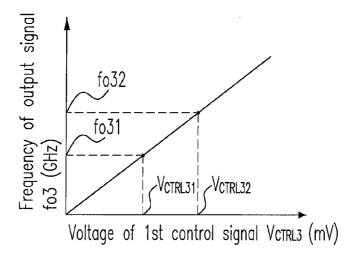

[0021] FIG. 7(a) is a schematic diagram showing the relation between the frequency of the output signal and the voltage of the first control signal according to the abovementioned embodiment of the present invention;

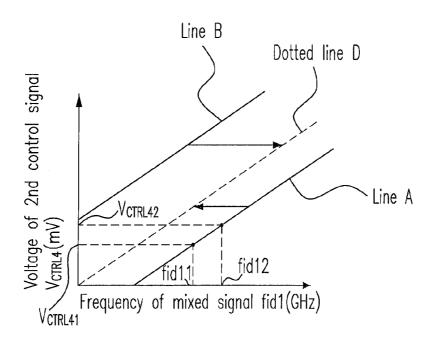

[0022] FIG. 7(b) is a schematic diagram showing the relation between the frequency of the mixed signal and the voltage of the second control signal in accordance with one embodiment of the present invention;

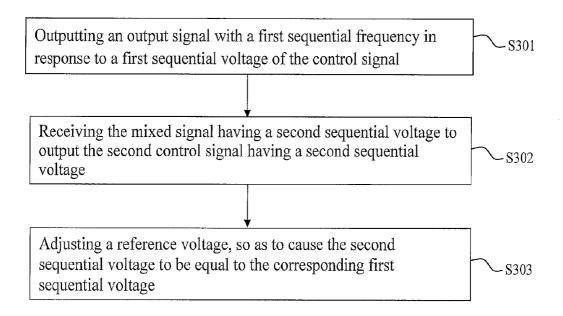

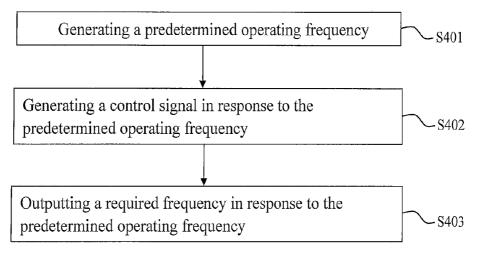

[0023] FIGS. 8(a) and 8(b) are flow diagrams showing the operation method of the frequency multiplier apparatus in accordance with another embodiment of the present invention:

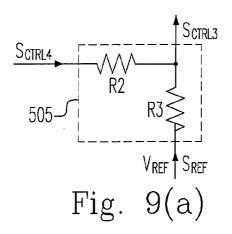

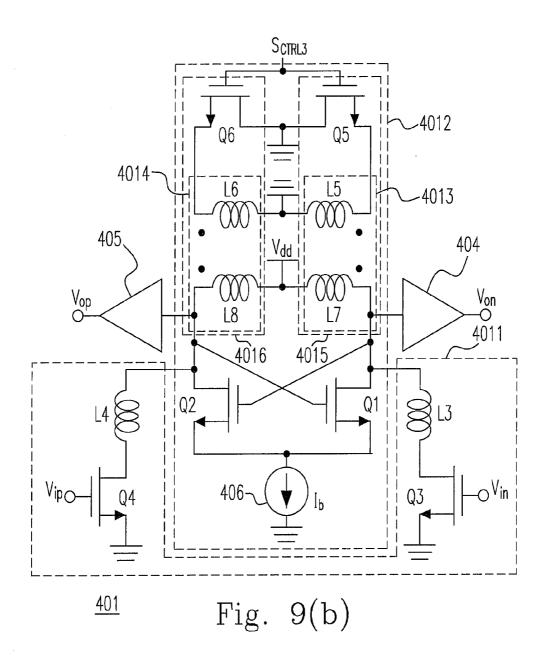

[0024] FIG. 9(a) is a schematic diagram showing the DC level shifting unit according to one embodiment of the present invention; and

[0025] FIG. 9(b) is a schematic diagram showing the injection locked frequency multiplier according to one embodiment of the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

[0026] The present invention will now be described more specifically with reference to the following embodiments. It is to be noted that the following descriptions of preferred embodiments of this invention are presented herein for the purposes of illustration and description only; it is not intended to be exhaustive or to be limited to the precise form disclosed. [0027] Please refer to FIGS. 3(a) and 3(b), which illustrate a frequency multiplier apparatus 40 in accordance with one embodiment of the present invention. The frequency multiplier apparatus 40 includes an injection-locked frequency multiplier 401 and a frequency-to-control signal converter 402. The injection-locked frequency multiplier 401 outputs an output signal So1 with a first frequency fo11 in response to an input signal Si1 with a first basic frequency fi11. The frequency-to-control signal converter 402 provides a first control signal  $S_{CTRL1}$  to the injection-locked frequency multiplier 401 in response to the input signal Si1. According to FIGS. 3(a) and 3(b), the injection-locked frequency multiplier 401 adjusts the first frequency foll to a second frequency fo12 in response to a change of the first control signal  $S_{\mathit{CTRL1}}$  when the first basic frequency fi11 of the output signal So1 is changed to a second basic frequency fi12, and the  $S_{\mathit{CTRL1}}$  is changed to a second control signal  $S_{\mathit{CTRL2}}$ . Notably, the first control signal  $S_{\mathit{CTRL1}}$  includes a first control voltage  $V_{\mathit{CTRL1}}$  or a first control current or a first control digital code, and the second control signal  $S_{\mathit{CTRL1}}$  includes a second control voltage  $V_{\mathit{CTRL2}}$  or a second control current or second control digital code.

[0028] In the illustration of FIG. 3(a), the injection-locked frequency multiplier 401 includes a harmonic generator 4011 and a variable-frequency oscillator 4012. In response to the input signal Si1, the harmonic generator 4011 generates a harmonic signal  $S_{H3}$  with a frequency value M\*fi11, which is M-times of the first basic frequency fi11. In response to the first control signal  $S_{CTRL1}$  and the harmonic signal  $S_{H3}$ , the variable-frequency oscillator 4012 generates the output signal So1 with the first frequency fo11, which is the M-times of the first basic frequency fi11.

**[0029]** Referring to the illustration of FIG. 3(b), when the frequency of the input signal Si1 changes from the first basic frequency fi11 to the second basic frequency fi12, the harmonic generator **4011** generates a harmonic signal  $S_{H4}$ , with a frequency value 3fi12, which is triple of the second basic frequency fi12. In response to the second control signal  $S_{CTRL2}$  and the harmonic signal  $S_{H4}$ , the variable-frequency oscillator **4012** generates the output signal So1 with the second frequency fo12, which is triple of the second basic frequency fi12.

[0030] According to the embodiment set forth above, the frequency of the output signal is M-times of that of the inputted signal. It is appreciated that the frequency value of the output signal can be other multiple of that of the inputted signal when applicable.

[0031] In FIGS. 3(a) and 3(b), the variable-frequency oscillator 4012 may be a voltage-controlled oscillator, a currentcontrolled oscillator or a digital-controlled oscillator, the frequency-to-control signal converter 402 may be a frequencyto-voltage signal converter, a frequency-to-current signal converter or a frequency-to-digital signal converter, and the first control signal  $\mathbf{S}_{CTRL1}$  may be a voltage signal, a current signal or a digital signal. The type of the variable-frequency oscillator 4012 shall match that of the frequency-to-control signal converter 402. For example, if the variable-frequency oscillator 4012 is a voltage-controlled oscillator and the first control signal  $\mathbf{S}_{\mathit{CTRL}1}$  a voltage signal, the frequency-to-control signal converter 402 is a frequency-to-voltage signal converter. Likewise, if the variable-frequency oscillator 4012 is a current-controlled oscillator and the first control signal  $S_{CTRL1}$  a current signal, the frequency-to-control signal converter 402 is a frequency-to-current signal converter.

[0032] Please refer to FIG. 3(c), which is a schematic diagram of an embodiment of the frequency-to-control signal converter 402 according to the present invention. When the frequency-to-control signal converter 402 is a frequency-to-voltage signal converter 403, the frequency-to-voltage signal converter 403 includes a limiting amplifier 4021 and a power detector 4022. The limiting amplifier 4021 amplifies the input signal Si1 to generate a power signal  $S_{P1}$ . The power detector 4022 detects the power signal  $S_{P1}$ , and transforms the power signal SP1 into the first control signal  $S_{CTRL1}$ .

[0033] The frequency-to-control signal converter 402 can automatically adjust the first control signal  $S_{TRL1}$  as appropriate in response to a change of the basic frequency of the

input signal Si1, so as to cause the frequency-to-control signal converter 402 adjust the output signal So1 to a predetermined frequency. Such an efficacy of the present invention is advantageous over the technical schemes of the prior art.

[0034] Please refer to FIG. 4(a), which illustrates the relation between the frequency fol of output signal and the voltage  $V_{\textit{CTRL}1}$  of the control signal according to a preferred embodiment of the present invention. It is appreciated that the frequency-to-control signal converter 402 is the frequencyto-voltage signal converter 403 and the variable-frequency oscillator 4012 a voltage-controlled oscillator in this embodiment. The frequency multiplier apparatus 40 cannot automatically adjust the first control signal  $S_{CTRL1}$  to a required frequency when the frequency-to-control signal converter 402 has not been calibrated in response to the frequency change of the input signal Si1. Before calibrating the frequency-to-control signal converter 402, there is a need to apply a sequence of the first control voltage  $V_{\textit{CTRL}1}$  , where  $V_{CTRL1} = \{V_{CTRL11}, V_{CTRL12}, \dots, V_{CTRL1n}\}$ , to the voltage-controlled oscillator. At this moment, the harmonic signals SH3, SH4 have not been injected into the voltage-controlled oscillator. Thus, the voltage-controlled oscillator can generates a signal So1 with a free vibration frequency in response to the first control voltage  $V_{\textit{CTRL}1}$ , and the free vibration frequency may change following a change of the first control voltage V<sub>CTRL1</sub>. Typically, there is a linear relationship between the frequency fo1 of output signal and the voltage  $V_{\mathit{CTRL}\,1}$  of the control signal, and the frequency fol of output signal is not locked yet.

[0035] Please refer to FIG. 4(b), which illustrates the relation between the frequency fil of input signal and the voltage  $V_{CTRL1}$  of the control signal according to a preferred embodiment of the present invention. After determining the relation between the frequency fol of the output signal So1 and the first control voltage  $V_{CTRL1}$ , the frequency-to-voltage signal converter 403 is then calibrated. The input signal Si1 received by the frequency-to-voltage signal converter 403 has a sequential frequency fil, where fil={fil1, fil2, ..., filn}. Having received the input signal Si1, the frequency-to-voltage signal converter 403 outputs a first control signal  $S_{CTRL1}$  with a sequence of first control voltage  $V_{CTRL1}$ , where  $V_{CTRL1}$ ={ $V_{CTRL11}$ ,  $V_{CTRL12}$ ,...,  $V_{CTRL1n}$ }, in response to the input signal Si1.

[0036] Again, referring to FIGS. 4(a) and 4(b), which illustrates an example in accordance with the embodiment that the frequency fol of the output signal So1 is triple of the frequency fi1 of the input signal Si1. In other words, fo1=3\*fi1. If the required value of the frequency fo1 is 54 GHz, the value of the frequency fi1 is 18 GHz. In FIG. 4(a), the first control voltage  $V_{\mathit{CTRL}1}$  at  $V_{\mathit{CTRL}11}$ , which is 40 millivolt, corresponds to the frequency foll, which is 54 GHz, of the output signal So1. Therefore, the frequency-to-voltage signal converter 403 is calibrated and outputs the first control signal  $S_{CTRL1}$ with the first control voltage  $V_{\textit{CTRL}1}$  at  $V_{\textit{CTRL}1}$ , which is 40 millivolt, when the frequency-to-voltage signal converter 403 receives the input signal Si1 with the frequency fi1, which is 18 GHz. Likewise, if the required value of the frequency fo1 is 52.5 GHz, the value of the frequency fil is 17.5 GHz. In FIG. 4(a), the first control voltage  $V_{CTRL1}$  at  $V_{CTRL12}$ , which is -6.25 millivolt, corresponds to the frequency fo12, which is 54 GHz, of the output signal So1. Therefore, the frequencyto-voltage signal converter 403 is calibrated and outputs the first control signal  $S_{CTRL1}$  with the first control voltage  $V_{CTRL1}$  at  $V_{CTRL12}$ , which is -6.25 millivolt, when the frequency-to-voltage signal converter 403 receives the input signal Si1 with the frequency fi1, which is 17.5 GHz.

[0037] Accordingly, the method set forth in the proceeding paragraph can be adopted to obtain the illustrations of FIGS. 4(a) and 4(b). Having completing the calibration for the frequency-to-voltage signal converter 403, the frequency multiplier apparatus 40 can automatically adjust the frequency fol of the output signal So1 in response to the change of the frequency fil of the input signal Si1, and the output signal So1 is locked, since the input signal Si1 is injected into the injection-locked frequency multiplier 401 while the harmonic signals  $S_{H3}$ ,  $S_{H4}$  are injected into the voltage-controlled oscillator

[0038] Please refer to FIG. 5(a), which illustrates the operation method of the frequency multiplier apparatus 40 according to the abovementioned embodiment of the present invention, and in particular the method for calibrating the frequency-to-control signal converter 402. The operation method includes the following steps: Step S101, applying a sequence of first control voltage  $V_{CTRL1}$ , where  $V_{CRTRL1} = \{V_{CTRL11}, V_{CTRL12}, \dots, V_{CTRL1n}\}$ , of the first control signal  $S_{CTRL1}$  to the injection-locked frequency multiplier 401 to adjust the output signal So1 to have the first sequential frequency fo1= $\{$ fo11, fo12, ..., fo1n $\}$ ; and Step S102, calibrating and cause the frequency-to-control signal converter 402 to output the first control signal  $S_{CTRL1}$  having the sequential voltage  $V_{CTRL1} = \{V_{CTRL11}, V_{CTRL12}, \dots, V_{CTRL1n}\}$  when the frequency-to-control signal converter receives the input signal Si1 having a sequential basic frequency  $fi1=\{fi11, fi12, \dots, fi1n\}$ , wherein a frequency value of the sequential frequency fol is an integral multiple of that of the corresponding sequential basic frequency fil.

[0039] Please refer to FIG. 5(b), which illustrates the operation method of the frequency multiplier apparatus 40 according to the abovementioned embodiment of the present invention, and in particular the auto-adjustment method after calibrating the frequency-to-control signal converter 402. The operation method includes the following steps: Step S201, outputting an output signal So1 having a first frequency fo11 in response to an input signal Si1 having a first basic frequency fi11; Step 202, outputting a control signal  $S_{CTRL1}$  in response to the input signal Si1; and Step 203, adjusting the first frequency fo11 to a second frequency fo12 in response to a change of the control signal  $S_{CTRL1}$  when the first basic frequency fi11 is changed to a second basic frequency fi12.

[0040] Please refer to FIG. 6, which illustrates a frequency multiplier apparatus 50 in accordance with another embodiment of the present invention. The frequency multiplier apparatus 50 includes an injection-locked frequency multiplier 401 and a frequency-to-control signal converter 402. The frequency multiplier apparatus 50 further includes a differential signal generator 503, which is employed for generating a phase-complimentary differential signal as the input signal. In FIG. 6, for example, the differential signal 503 receives an input signal Si2 with a third basic frequency fi3={fi31, fi32, ..., fi3n}, and generates differential signals fi3p, fi3n, wherein the phase difference therebetween is 180 degrees. In one another embodiment of the present invention, the frequency-to-control signal converter 402 includes a frequency to volt

another embodiment of the present invention, the frequency-to-control signal converter **402** includes a frequency-to-voltage signal converter **502**, a signal-mixing unit **504** and a DC level shifting unit **505**, while the differential signal generator **503** is not used.

[0041] The signal-mixing unit 504 is employed to process the input signal Si2 with the third basic frequency fi3 and the

signal Si3 with a frequency fi4 to generate a mixed signal Sid1 with a frequency fid1 as the input signal to the frequency-to-voltage signal converter 502. For instance, if the frequencies fi3 and fi4 are 20 GHz and 15 GHz respectively, the signal-mixing unit 504 obtain a frequency fid1=5 GHz by subtracting the frequency value of the frequency fi4 from that of the third basic frequency fi3. Such a method for frequency reduction is an alternative when the frequency of the input signal is too high that the frequency-to-voltage signal converter 502 cannot receive the input signal, and is advantageous for the consequent processing of the frequency-to-voltage signal converter 502 directly receives the input signal Si2 for processing while the signal-mixing unit 504 is not used.

[0042] According to one embodiment of the present invention, the frequency-to-voltage signal converter 502 can be the same as the frequency-to-voltage signal converter 403 as illustrated in FIG. 3(c). However, the calibrating method for the embodiment shown in FIG. 6 is different from that for the embodiment in FIGS. 3(a) and 3(b). Particularly, the DC level shifting unit 505 may be employed for compensating the voltage difference between the DC voltage  $V_{CTRL3}$  of the first control signal  $S_{CTRL3}$  and the DC voltage  $V_{CTRL4}$  of the output signal  $S_{CTRL4}$  from the frequency-to-voltage signal converter 502

[0043] Please refer to FIG. 7(a), which illustrates the frequency fo3 of the output signal versus the voltage  $V_{CTRL3}$  of the first control signal according to the abovementioned embodiment of the present invention, taking the voltagecontrolled oscillator as the variable frequency oscillator 4012 of the Injection locked frequency multiplier 401 for example. Before calibrating the frequency-to-control signal converter 502, there is a need to apply a sequence of the first control voltage  $V_{CTRL3}$ , where  $V_{CTRL3} = \{V_{CTRL31}, V_{CTRL32}, \dots, \}$  $V_{CTRL3n}$ , to the voltage-controlled oscillator. At this moment, the input signal Si2 has not been injected into the voltage-controlled oscillator. Thus, the voltage-controlled oscillator can generates a signal So2 with a free vibration frequency in response to the first control voltage  $V_{\textit{CTRL3}}$ , and the free vibration frequency may change following a change of the first control voltage  $V_{CTRL3}$ . Typically, there is a linear relationship between the frequency fo3 of output signal and the voltage  $V_{\textit{CTRL}3}$  of the control signal, and the frequency fo3 of output signal So2 is not locked yet.

[0044] Please refer to FIG. 7(b), which illustrates the relation between the frequency fid1 of mixed signal and the voltage  $\mathbf{V}_{\mathit{CTRL4}}$  of the second control signal according to another preferred embodiment of the present invention. After determining the relation between the frequency fo3 of the output signal So2 and the first control voltage V<sub>CTRL3</sub>, the frequency-to-voltage signal converter 502 is then calibrated. The mixed signal Sid1 received by the frequency-to-voltage signal converter 502 has a sequential frequency fid1, where  $fid1 = \{fid11, fid12, \dots, fid1n\}$ . Having received the mixed signal Sid1, the frequency-to-voltage signal converter 502 outputs a second control signal  $S_{\textit{CTRL4}}$  with a sequence of second control voltage  $V_{CTRL4}$ , where  $V_{CTRL4} = \{V_{CTRL41}, V_{CTRL42}, \dots, V_{CTRL4n}\}$ , in response to the mixed signal Sid1. In one embodiment, the frequency fo3, where fo3={fo31, fo32, ..., fo3n}, of the output signal So2 is triple of the frequency fi3, where fi3= $\{$ fi31, fi32, ..., fi3n $\}$ , of the input signal Si2 for example. In other words, fo3=3\*fi3.

[0045] According to FIG. 7(b), in one embodiment, the relation between the second control voltage  $V_{CTRL4}$  and the

sequential frequency fid1 can be illustrated as either the line A or the line B, which are linear without passing the origin. Thus, one may adjust a signal  $S_{REF}$  of the DC level shifting unit **505** to cause the voltage value of the first control voltage  $V_{CTRL3}$  equals to that of the second control voltage  $V_{CTRL4}$ , i.e., to move line A or line B toward the dotted line which passes through the origin. The signal  $S_{REF}$  can be a reference voltage or a reference current, and alternatives for the frequency-to-voltage signal converter **502** may be a frequency-to-current signal converter or a frequency-to-digital signal converter, according to the requirements.

[0046] Having completing the calibration for the frequency-to-voltage signal converter 502, the frequency multiplier apparatus 50 can automatically adjust the frequency fo3 of the output signal So2 in response to the change of the frequency fi3 of the input signal Si2, and the frequency fo3 the output signal So3 is locked, since the input signal Si2 is injected into the injection-locked frequency multiplier 401. The frequency-to-control signal converter 402 causes a change of the first control signal VCTRL3 in response to the signal Si2 with the frequency fi3, so as to automatically adjust the frequency fo3 of the output signal So2.

[0047] Please refer to FIG. 8(a), which illustrates the operation method of the frequency multiplier apparatus 50 according to the abovementioned embodiment of the present invention, and in particular the method for calibrating the frequency-to-control signal converter 502. The operation method includes the following steps: Step S301, outputting an output signal So2 with a first sequential frequency fo3, where fo3={fo31, fo32, . . . , fo3n}, in response to a first sequential voltage  $V_{CTRL3}$ , where  $V_{CTRL3}$ ={ $V_{CTRL31}$ ,  $V_{CTRL32}$ , . . . ,  $V_{CTRL3n}$ }, of the first control signal  $S_{CTRL3}$ ; Step S302, the frequency-to-control signal converter 502 receiving the mixed signal Sid1 having a second sequential voltage fid1, where fid1={fid11, fid12, . . . , fid1n}, and outputting a second control signal  $S_{CTRL4}$  with a second sequential voltage  $V_{CTRL4n}$ , where  $V_{CTRL4}$ ={ $V_{CTRL41}$ ,  $V_{CTRL42}$ , . . . ,  $V_{CTRL4n}$ }, in response to the mixed signal Sid1; and Step 303, adjusting a reference voltage, so as to cause the second sequential voltage  $V_{CTRL4}$  to be equal to the corresponding first sequential voltage  $V_{CTRL3}$ .

[0048] Please refer to FIG. 8(b), which illustrates the operation method of the frequency multiplier apparatus 50 according to the abovementioned embodiment of the present invention, and in particular the auto-adjustment and outputting the frequency fo3 after calibrating the frequency-to-control signal converter 502. The method shown in FIG. 8(b) may also be applicable to the frequency multiplier apparatus 40. Please also refer to FIGS. 3(a) and 6, the operation method for the frequency multiplier apparatus 40 or 50 includes the following steps: Step S401, generating a predetermined operating frequency fid1, fi1; Step S402, generating a control signal  $S_{CTRL3}$ ,  $S_{CTRL4}$  in response to the predetermined operating frequency fio3, fo1 in response to the predetermined operating frequency fio3, fo1 in response to the predetermined operating frequency fid1, fi1.

**[0049]** Please refer to FIG. **9**(*a*), in one embodiment, the DC level shifting unit **505** includes resistors R2, R3. The second control voltage  $V_{CTR4}$  of the second control signal  $S_{CTRL4}$  is applied to the resistor R2 while the reference voltage  $V_{REF}$  of the reference signal  $S_{REF}$  is applied to the resistor R3, so as to adjust the second control voltage  $V_{CTR4}$  to be equal to the first control voltage  $V_{CTR3}$ .

[0050] FIG. 9(b) shows one embodiment of the injection locked frequency multiplier 401 according to the present invention. The harmonic generator 4011 includes a pair of transistors Q3, Q4, coupled to the drains of transistors Q1, Q2 via inductors L3, L4, respectively. Voltages Vin, Vip are applied to the gates of the transistors Q3, Q4 respectively, so as to produce a bias at a non-linear area and generate third harmonics which is injected into the variable frequency oscillator 4012. The variable frequency oscillator 4012 includes a pair of transistors Q5, Q6, a pair of voltage transformers 4013, 4014 and a pair of transistors Q1, Q2. The injection locked frequency multiplier 401 further includes a pair of buffers 404, 405 respectively outputting output voltages Von, Vop at each of the output terminals thereof. A current source 406 is coupled to the sources of the transistors Q1, Q2 to provide a bias current Ib. The gates of the transistors Q1, Q2 are coupled to the input terminals of the buffers 404, 405 respectively. Inductors L7, L8 are coupled to the buffers 404, 405 respectively. A voltage Vdd is applied to the location where the inductors L7, L8 are connected to each other. The transistors Q5, Q6 are respectively coupled to two inductors L7, L8 in parallel.

[0051] Gates of the transistors Q5, Q6 are coupled to each other, and controlled by the first control voltage  $V_{CTRL3}$  of the first control signal  $S_{CTRL3}$ . Thus, each of the transistors Q5, Q6 can be used as a variable resistor whose equivalent resistance can be adjusted by the first control voltage  $V_{CTRL3}$ . The transistor Q5 is coupled to the voltage transformer 4013, and therefore the combination thereof constitutes a variable inductor 4015 whose inductance can be adjusted by controlling the first control voltage  $V_{CTRL3}$ , which is different from the prior art that adjusts resonance frequencies using capacitors C1, C2 in FIG. 2. The advantage of adjusting resonance frequencies by using variable inductors 4015, 4016 according to present invention is that a wider range of resonance frequencies is achievable.

#### **Embodiments**

[0052] 1. A frequency multiplier apparatus, comprising: [0053] an injection-locked frequency multiplier outputting an output signal having a first frequency in response to an input signal having a first basic frequency; and

- [0054] a frequency-to-control signal converter providing a first control signal to the injection-locked frequency multiplier in response to the input signal, wherein the injection-locked frequency multiplier adjusts the first frequency to a second frequency in response to a change of the first control signal when the first basic frequency is changed to a second basic frequency.

- 2. The frequency multiplier apparatus of embodiment 1, wherein a frequency value of the second frequency is an integral multiple of that of the second basic frequency.

- 3. The frequency multiplier apparatus of embodiment 1, wherein the injection-locked frequency multiplier includes: [0055] a harmonic generator generating a harmonic signal in response to the input signal; and

- [0056] a variable-frequency oscillator including one selected from a group consisting of a voltage-controlled oscillator, a current-controlled oscillator and a digital-controlled oscillator, and adjusting the first basic frequency to the second basic frequency in response to a change of the first control signal and a change of the harmonic signal.

- 4. The frequency multiplier apparatus of embodiment 1, wherein the frequency-to-control signal converter includes

- one selected from a group consisting of a frequency-to-voltage signal converter, a frequency-to-current signal converter and a frequency-to-digital signal converter.

- 5. The frequency multiplier apparatus of embodiment 1, wherein the first control signal includes one selected from a group consisting of a voltage signal, a current signal and a digital signal.

- 6. The frequency multiplier apparatus of embodiment 1, wherein the frequency-to-control signal converter includes:

- [0057] a signal-mixing unit down-converting the first basic frequency to a third basic frequency, and outputting a mixed signal having the third basic frequency;

- [0058] a frequency-to-voltage signal converter receiving the mixed signal, outputting a second control signal, and including:

- [0059] a limiting amplifier amplifying the mixed signal to generate a power signal; and

- [0060] a power detector detecting the power signal, and transforming the power signal into the second control signal; and

- [0061] a DC level shifting unit outputting the first control signal in response to the second control signal.

- 7. The frequency multiplier apparatus of embodiment 6, wherein the frequency-to-voltage signal converter changes a voltage of the second control signal in response to the mixed signal, and the DC level shifting unit adjusts the first control signal in response to the second control signal, when the first basic frequency is changed to the second basic frequency.

- 8. The frequency multiplier apparatus of embodiment 1, further comprising:

- [0062] a differential-signal generator generating a phase-complimentary differential signal as the input signal.

- 9. The frequency multiplier apparatus of embodiment 6, configured to apply a first voltage of the first control signal to the injection-locked frequency multiplier to adjust the output signal to have a first sequential frequency.

- 10. The frequency multiplier apparatus of embodiment 9, wherein the frequency-to-voltage signal converter receives the mixed signal having a second frequency to adjust the second control signal to have a second voltage.

- 11. The frequency multiplier apparatus of embodiment 10, wherein:

- [0063] the first control signal is a sequential first control signals and the first voltage is a sequential first voltages;

- [0064] the output signal is a sequential output signals and the first frequency is a sequential first frequencies;

- [0065] the second control signal is a sequential second control signals and the second voltage is a sequential second voltages; and

- [0066] the mixed signal is sequential mixed signals and the second frequency is a sequential second frequencies.

- 12. The frequency multiplier apparatus of embodiment 11, configured to adjust a reference voltage applied to the DC level shifting unit, so as to cause the second sequential voltages to be correspondingly equal to the first sequential voltages

- 13. The frequency multiplier apparatus of embodiment 1, configured to apply a voltage of the first control signal to the injection-locked frequency multiplier, so as to adjust the output signal to have a frequency.

- 14. The frequency multiplier apparatus of embodiment 13, configured to calibrate and cause the frequency-to-control signal converter to output the first control signal having the voltage when the frequency-to-control signal converter

receives the input signal having a basic frequency, wherein a frequency value of the frequency is an integral multiple of that of the basic frequency.

15. A method for operating a frequency multiplier apparatus, comprising steps of:

[0067] outputting an output signal having a first frequency in response to an input signal having a first basic frequency;

[0068] outputting a control signal in response to the input signal; and

[0069] adjusting the first frequency to a second frequency in response to a change of the control signal, when the first basic frequency is changed to a second basic frequency.

16. The method of embodiment 15, wherein the frequency multiplier apparatus comprises a frequency-to-control signal converter, and the method further comprises a step of:

[0070] adjusting the output signal to have a frequency in response to a voltage of the control signal.

17. The method of embodiment 16, further comprising a step of:

[0071] calibrating and causing the frequency-to-control signal converter to output the control signal having the voltage when receiving the input signal having a basic frequency.

18. The method of embodiment 17, wherein a frequency value of the frequency is an integral multiple of that of the basic frequency.

19. The method of embodiment 18, wherein:

[0072] the output signal is a sequential output signals, and the frequency is a sequential frequencies;

[0073] the control signal is a sequential control signals, and the voltage is a sequential voltages;

[0074] the input signal is a sequential input signals, and the basic frequency is a sequential basic frequencies; and

[0075] a plurality of values of the sequential frequencies are a plurality of integral multiples of the those of the sequential basic frequencies correspondingly.

20. A method for operating a frequency multiplier apparatus, comprising steps of:

[0076] generating a predetermined operating frequency;

[0077] generating a control signal in response to the predetermined operating frequency; and

[0078] outputting a required frequency in response to the control signal.

[0079] While the invention has been described in terms of what is presently considered to be the most practical and preferred embodiments, it is to be understood that the invention needs not be limited to the disclosed embodiments. On the contrary, it is intended to cover various modifications and similar arrangements included within the spirit and scope of the appended claims that are to be accorded with the broadest interpretation so as to encompass all such modifications and similar structures.

What is claimed is:

- 1. A frequency multiplier apparatus, comprising:

- an injection-locked frequency multiplier outputting an output signal having a first frequency in response to an input signal having a first basic frequency; and

- a frequency-to-control signal converter providing a first control signal to the injection-locked frequency multiplier in response to the input signal, wherein the injection-locked frequency multiplier adjusts the first frequency to a second frequency in response to a change of the first control signal when the first basic frequency is changed to a second basic frequency.

- 2. A frequency multiplier apparatus as claimed in claim 1, wherein a frequency value of the second frequency is an integral multiple of that of the second basic frequency.

- 3. A frequency multiplier apparatus as claimed in claim 1, wherein the injection-locked frequency multiplier includes:

- a harmonic generator generating a harmonic signal in response to the input signal; and

- a variable-frequency oscillator including one selected from a group consisting of a voltage-controlled oscillator, a current-controlled oscillator and a digital-controlled oscillator, and adjusting the first basic frequency to the second basic frequency in response to a change of the first control signal and a change of the harmonic signal.

- 4. A frequency multiplier apparatus as claimed in claim 1, wherein the frequency-to-control signal converter includes one selected from a group consisting of a frequency-to-voltage signal converter, a frequency-to-current signal converter and a frequency-to-digital signal converter.

- 5. A frequency multiplier apparatus as claimed in claim 1, wherein the first control signal includes one selected from a group consisting of a voltage signal, a current signal and a digital signal.

- **6.** A frequency multiplier apparatus as claimed in claim **1**, wherein the frequency-to-control signal converter includes:

- a signal-mixing unit down-converting the first basic frequency to a third basic frequency, and outputting a mixed signal having the third basic frequency;

- a frequency-to-voltage signal converter receiving the mixed signal, outputting a second control signal, and including:

- a limiting amplifier amplifying the mixed signal to generate a power signal; and

- a power detector detecting the power signal, and transforming the power signal into the second control signal; and

- a DC level shifting unit outputting the first control signal in response to the second control signal.

- 7. A frequency multiplier apparatus as claimed in claim 6, wherein the frequency-to-voltage signal converter changes a voltage of the second control signal in response to the mixed signal, and the DC level shifting unit adjusts the first control signal in response to the second control signal, when the first basic frequency is changed to the second basic frequency.

- **8**. A frequency multiplier apparatus as claimed in claim **1**, further comprising:

- a differential-signal generator generating a phase-complimentary differential signal as the input signal.

- **9.** A frequency multiplier apparatus as claimed in claim **6**, configured to apply a first voltage of the first control signal to the injection-locked frequency multiplier to adjust the output signal to have a first sequential frequency.

- 10. A frequency multiplier apparatus as claimed in claim 9, wherein the frequency-to-voltage signal converter receives the mixed signal having a second frequency to adjust the second control signal to have a second voltage.

- 11. A frequency multiplier apparatus as claimed in claim 10, wherein:

the first control signal is a sequential first control signals and the first voltage is a sequential first voltages;

the output signal is a sequential output signals and the first frequency is a sequential first frequencies;

the second control signal is a sequential second control signals and the second voltage is a sequential second voltages; and

the mixed signal is sequential mixed signals and the second frequency is a sequential second frequencies.

- 12. A frequency multiplier apparatus as claimed in claim 11, configured to adjust a reference voltage applied to the DC level shifting unit, so as to cause the second sequential voltages to be correspondingly equal to the first sequential voltages.

- 13. A frequency multiplier apparatus as claimed in claim 1, configured to apply a voltage of the first control signal to the injection-locked frequency multiplier, so as to adjust the output signal to have a frequency.

- 14. A frequency multiplier apparatus as claimed in claim 13, configured to calibrate and cause the frequency-to-control signal converter to output the first control signal having the voltage when the frequency-to-control signal converter receives the input signal having a basic frequency, wherein a frequency value of the frequency is an integral multiple of that of the basic frequency.

- **15**. A method for operating a frequency multiplier apparatus, comprising steps of:

- outputting an output signal having a first frequency in response to an input signal having a first basic frequency;

- outputting a control signal in response to the input signal; and

- adjusting the first frequency to a second frequency in response to a change of the control signal, when the first basic frequency is changed to a second basic frequency.

- **16**. A method as claimed in claim **15**, wherein the frequency multiplier apparatus comprises a frequency-to-control signal converter, and the method further comprises a step of:

- adjusting the output signal to have a frequency in response to a voltage of the control signal.

- 17. A method as claimed in claim 16, further comprising a step of:

- calibrating and causing the frequency-to-control signal converter to output the control signal having the voltage when receiving the input signal having a basic frequency.

- **18**. A method as claimed in claim **17**, wherein a frequency value of the frequency is an integral multiple of that of the basic frequency.

- 19. A method as claimed in claim 18, wherein:

- the output signal is a sequential output signals, and the frequency is a sequential frequencies;

- the control signal is a sequential control signals, and the voltage is a sequential voltages;

- the input signal is a sequential input signals, and the basic frequency is a sequential basic frequencies; and

- a plurality of values of the sequential frequencies are a plurality of integral multiples of the those of the sequential basic frequencies correspondingly.

- **20**. A method for operating a frequency multiplier apparatus, comprising steps of:

- generating a predetermined operating frequency;

- generating a control signal in response to the predetermined operating frequency; and

- outputting a required frequency in response to the control signal.

\* \* \* \* \*