### (19) United States

# (12) Patent Application Publication

(10) Pub. No.: US 2011/0276936 A1 Nov. 10, 2011 (43) **Pub. Date:**

### (54) METHOD FOR ANALOG PLACEMENT AND GLOBAL ROUTING CONSIDERING WIRING **SYMMETRY**

Iris Hui-Ru JIANG, Yonghe City (75) Inventors:

(TW); Yu-Ming YANG, Xindian City (TW)

**National Chiao Tung University** (73) Assignee:

Appl. No.: 12/824,942

(22) Filed: Jun. 28, 2010

(30)Foreign Application Priority Data

(TW) ...... 099114823

### **Publication Classification**

(51) Int. Cl. G06F 17/50 (2006.01) **U.S. Cl.** ...... **716/126**; 716/122; 716/129

#### ABSTRACT (57)

A method for analog placement and global routing considering wiring symmetry performs a layout for a circuit which is described by a netlist having a set of devices and wires. First, the method inputs the netlist, and each device thereof has a design constraint and a corresponding priority. Based on the priorities, it performs a sorting on the devices to establish a constraint library. Then, based on the design constraint and corresponding priority of each device, the method establishes a hierarchical constraint tree. According to the hierarchical constraint tree, the method performs placement of each device, wherein possible shape of each device is represented by a shape curve. For each placement of the device, the method calculates a corresponding cost function. Then, it selects an optimum placement of the device according to the cost functions. The method establishes an RSMT for each wire and then performs an analog routing.

FIG. 2

\*\*\*\*\*\*\*\*ob amp\*\*\*\*\*\*\*

| *symmetry1 proximity1 | *symmetry1 proximity1 | *symmetry2 proximity2 | *symmetry2 proximity2 | *symmetry3 proximity2 | *symmetry3 proximity2 | *symmetry4 proximity2 | *symmetry4 proximity2 | *symmetry5 proximity2 | *symmetry5 proximity2 | *proximity1 |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------|

| m=12                  | m=12                  | m=16                  | m=16                  | m=20                  | m=20                  | m=13                  | m=13                  | m=12                  | m=12                  | m=14        |

| W=10u                 | W=10u                 | W=20u                 | W=20u                 | W=20u                 | W=20u                 | W=9.75u               | W=9.75u               |                       | W=9.45u               | W=10u       |

| L=1u                  | L=1u        |

| nch                   | nch                   | pch                   | pch                   | pch                   | pch                   | nch                   | nch                   | nch                   | nch                   | nch         |

|                       |                       |                       |                       | vdd                   |                       |                       |                       |                       |                       |             |

| vi+ net2              | net2                  | net1                  | net3                  | ppx                   | ppy                   | net4                  | net5                  | gnd                   | gnd                   | gnd         |

| ; <u>+</u>            | <u>.</u>              | vb3                   | vb3                   | vb4                   | vb4                   | vb2                   | vb2                   | vb1                   | vb1                   | vb0         |

| net1                  | net3                  | -0/                   | <b>10</b>             | net1                  | net3                  | 9                     | <b>10</b>             | net4                  | net5                  | net2        |

| Σ                     | M2                    | M3                    | <b>M</b>              | M5                    | 9W                    | M7                    | ₩                     | <b>6</b> ₩            | M10                   | M11         |

| _ |          |           |              |           |          |

|---|----------|-----------|--------------|-----------|----------|

|   |          | 0         | -            | 2         | Priority |

|   |          | others    | power        | proximity | Type     |

|   | 8        | 4         | 5            | 9         | Priority |

|   | matching | mirroring | differential | input     | Type     |

Total\_Wiring\_Difference = 10 =0

# METHOD FOR ANALOG PLACEMENT AND GLOBAL ROUTING CONSIDERING WIRING SYMMETRY

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to the technical field of analog layout and, more particularly, to a method for analog placement and global routing considering wiring symmetry.

[0003] 2. Description of Related Art

[0004] Analog designs are quite different from digital designs from a layout perspective. Unlike a large-scale digital design, an analog design usually has a relatively small scale, i.e., an analog circuit typically has a relatively small die size. However, its physical behavior is very sensitive to the layout geometry, e.g., parasitic coupling effect, small signal transmission, wiring crossovers, etc. Hence, area minimization is usually not a concern for an analog design. A digital designer can leverage mature commercial EDA tools to automate layout generate an analog layout is far from automatic. The manual, time-consuming, error-prone task highly depends on the layout designer's experience and wit. However, analog design automation has become desirable.

[0005] To facilitate the automatic analog layout generation, the designer's expertise can be translated to topological constraints. Three symmetry constraints, i.e., device matching, device mirroring, and device proximity constraints, for analog device placement are proposed in the prior art.

[0006] The device matching constraint is created for the devices that can share common gate or should be placed closely. The device mirroring constraint is used on two devices that have to be placed symmetrically to avoid parasitic mismatches. For the devices with the same functionality, the device proximity constraint restricts them to be placed together.

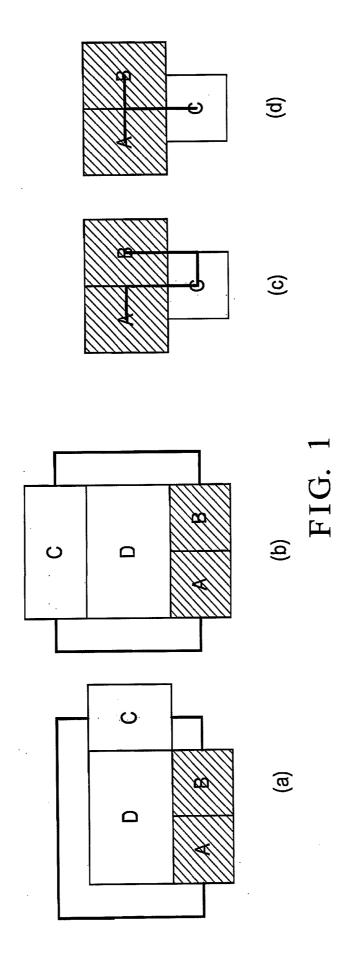

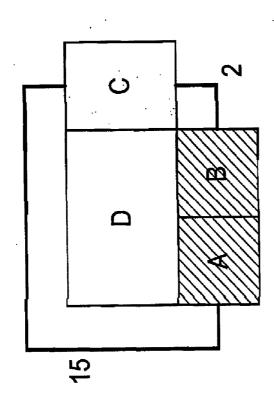

[0007] The parasitic mismatch between two devices can be minimized by the device matching constraint, the device mirroring constraint, and the device proximity constraint cited above. Nevertheless, if the signal paths going out of and coming into the symmetry constrained modules are not symmetric, the signal still mismatches and may cause the circuit failure. Therefore, for the analog design automation, the prior works only consider the device symmetry and neglect wiring symmetry. FIG. 1 is a schematic view of two typical analog layouts, which demonstrates the importance of the wiring symmetry. As shown in FIG. 1, devices A and B have the device mirroring constraint, and they are placed symmetrically. They both connect to device C. FIG. 1(a) shows a placement topology with wire asymmetry, while FIG. 1(b)shows a placement topology with wire symmetry. It can be seen in FIG.  $\mathbf{1}(a)$  and FIG.  $\mathbf{1}(b)$  that the symmetry depends not only on symmetric devices but also on the devices that they connect, because the asymmetric placement induces asymmetric wiring, leading to different physical behaviors for symmetric devices. As shown in FIG.  $\mathbf{1}(c)$  and FIG.  $\mathbf{1}(d)$ , although mirroring devices A and B are placed symmetrically with their common connected device C, careless routing may distort the symmetry. Obviously, compared with FIG. 1(c), the topology in FIG. 1(d) is symmetric on both placement and routing. The previous works have emphasized only on device (placement) symmetry, but the wiring (routing) in an analog circuit can cause the physical effect to impact on the circuit performance. Therefore, only device symmetry consideration

is not enough. If the wiring symmetry is neglected at layout, it causes unbalanced physical behavior to these symmetric devices and cannot achieve the symmetric layout.

[0008] Therefore, it is desirable to provide an improved method for analog placement and global routing considering wiring symmetry to mitigate and/or obviate the aforementioned problems.

### SUMMARY OF THE INVENTION

[0009] The object of the present invention is to provide a method for analog placement and global routing considering wiring symmetry, which allows the analog placement and global routing design to maintain both device symmetry and wiring symmetry to further increase the analog signal quality and decrease the mismatch between two devices in process.

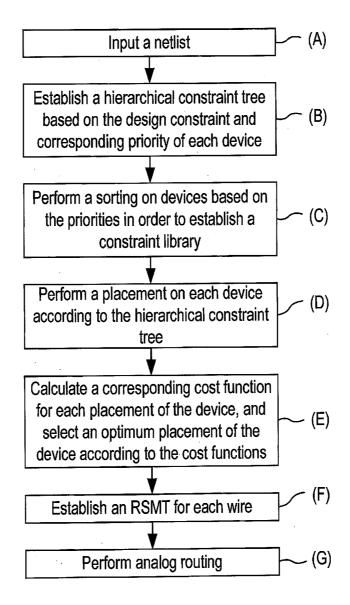

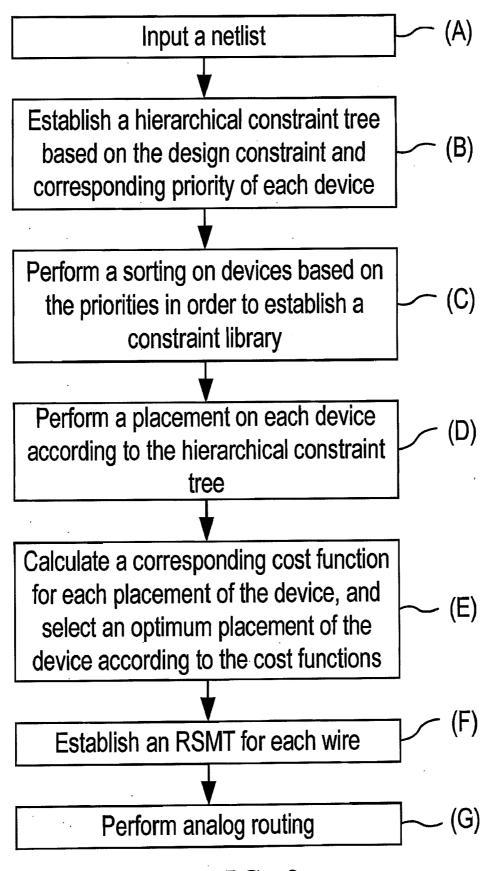

[0010] According to a feature of the invention, a method for analog placement and global routing considering wiring symmetry is provided, which is executed in a computer to perform a layout for an analog circuit described by a netlist having a set of devices and wires connected thereon. The method includes the steps of: (A) inputting the netlist, each device of the netlist having a design constraint, each design constraint corresponding to a priority; (B) establishing a hierarchical constraint tree based on the design constraint and corresponding priority of each device; (C) performing a sorting on the devices based on the priorities; (D) performing a placement on each device according to the hierarchical constraint tree, wherein a possible shape of each device is represented by a shape curve; (E) calculating a corresponding cost function for each placement of the device, and selecting an optimum placement of the device according to the cost functions; (F) establishing a rectilinear Steiner minimal tree (RSMT) for each wire; and (G) performing an analog routing.

[0011] Other objects, advantages, and novel features of the invention will become more apparent from the following detailed description when taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0012] FIG. 1 is a schematic view of two typical analog layouts;

[0013] FIG. 2 is a flowchart of a method for analog placement and global routing considering wiring symmetry in accordance with an embodiment of the invention;

[0014] FIG. 3 is a graph of a netlist in accordance with an embodiment of the invention;

[0015] FIG. 4 shows the design constraints in accordance with an embodiment of the invention;

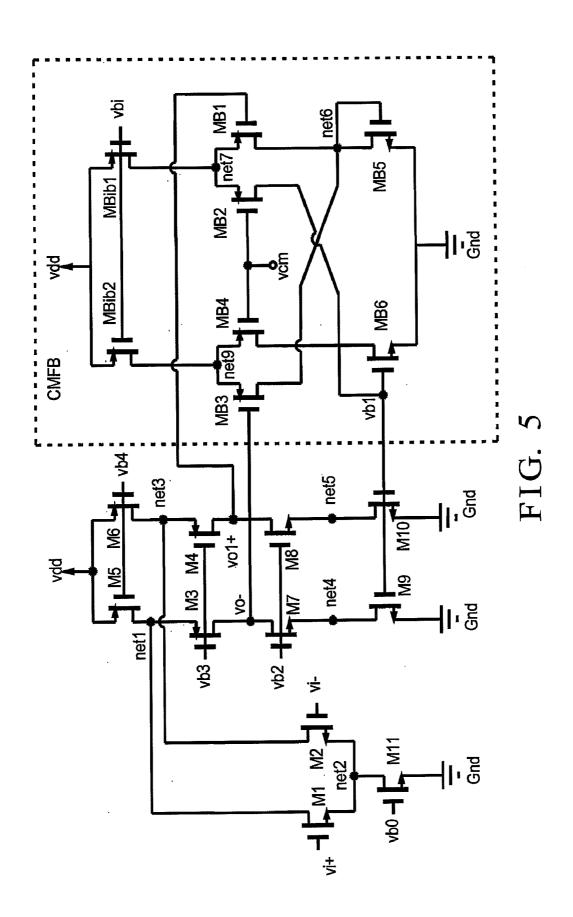

[0016] FIG. 5 is a circuit diagram of an operational amplifier in accordance with an embodiment of the invention;

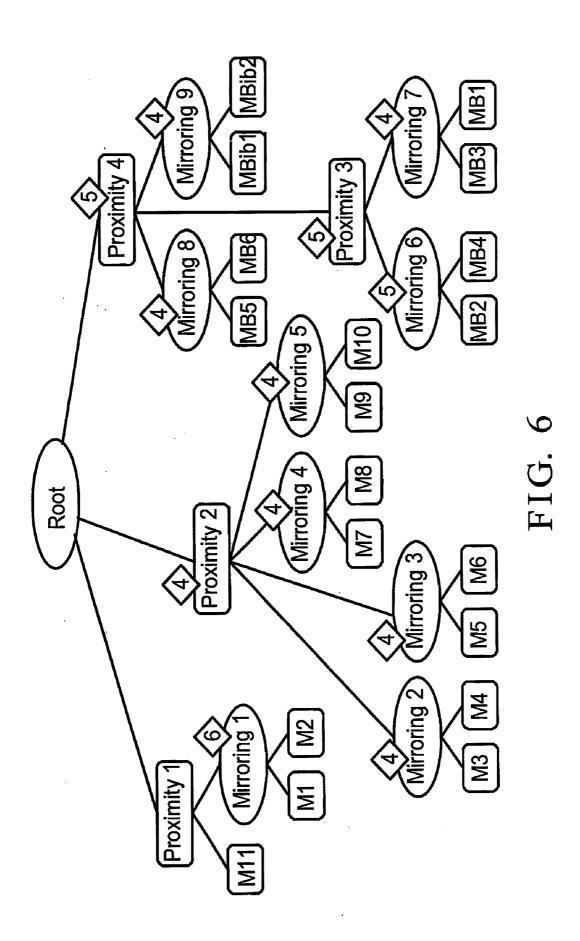

[0017] FIG. 6 is a schematic diagram of a hierarchical constraint tree of the operational amplifier of FIG. 5 in accordance with an embodiment of the invention;

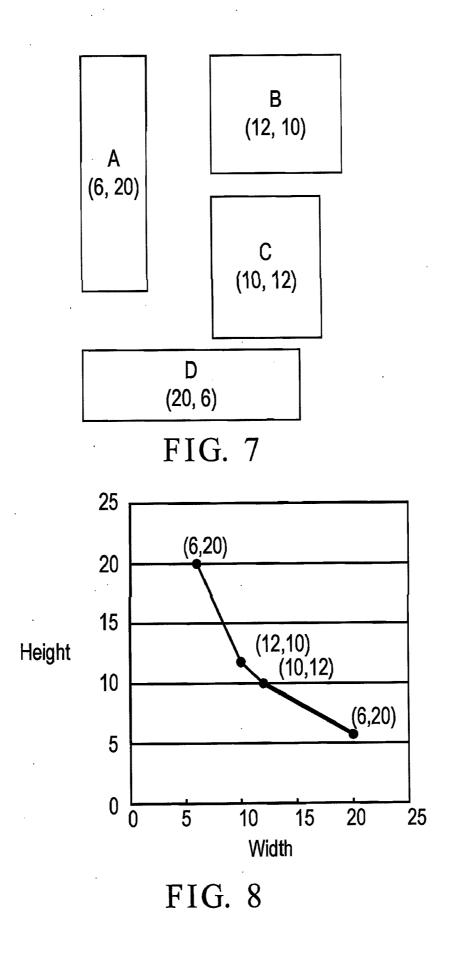

[0018] FIG. 7 is a schematic diagram of a device folding in accordance with an embodiment of the invention;

[0019] FIG. 8 is a graph of a shape curve generated by performing the device folding of FIG. 7 in accordance with an embodiment of the invention;

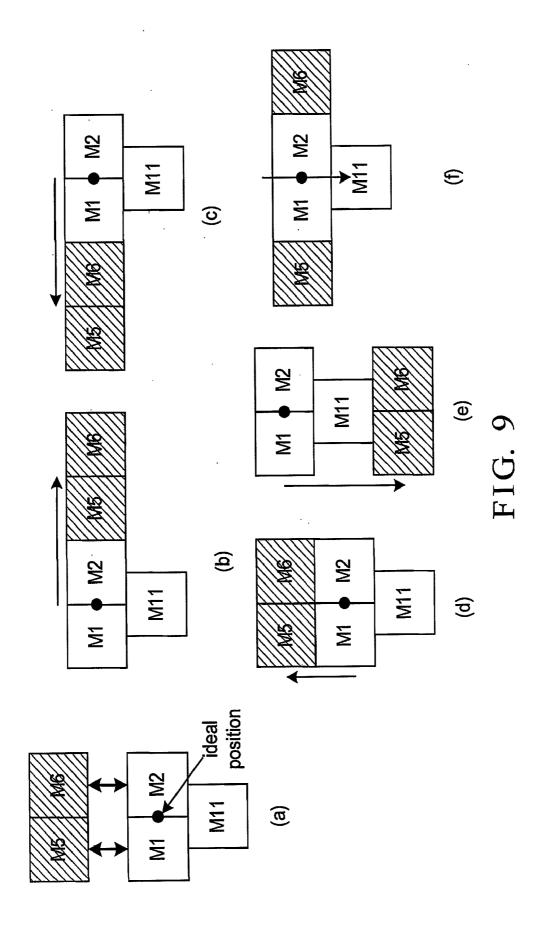

[0020] FIG. 9 is a schematic diagram of force-directed placement in accordance with an embodiment of the invention;

[0021] FIG. 10 is a schematic diagram of Total\_Wiring\_ Difference in accordance with an embodiment of the invention:

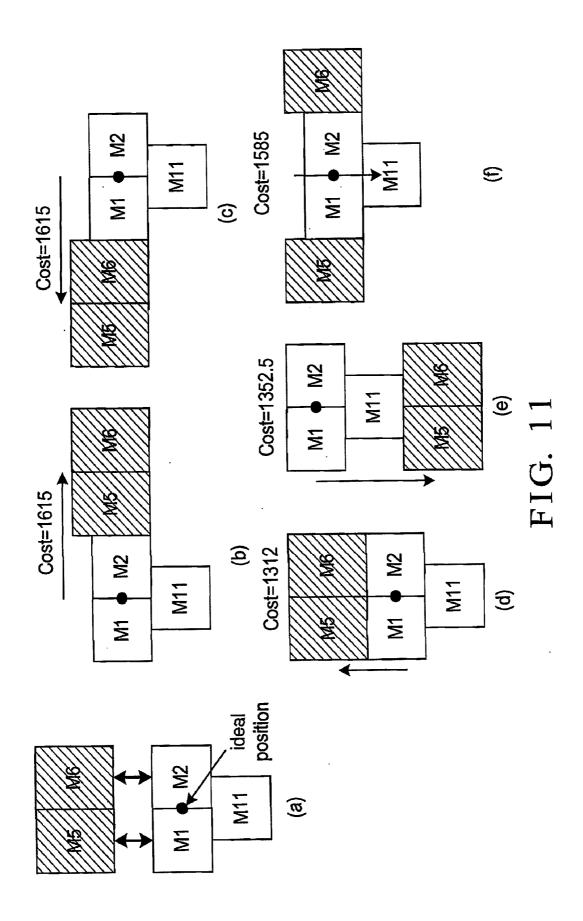

[0022] FIG. 11 is a schematic diagram of a cost function for the placement of FIGS. 9(b)-(f) in accordance with an embodiment of the invention;

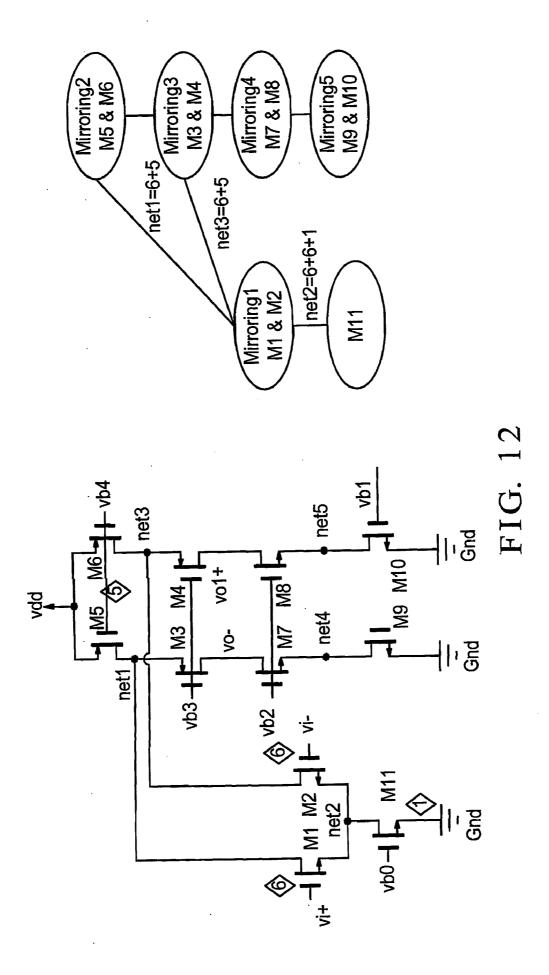

[0023] FIG. 12 is a schematic diagram of a wiring symmetry analysis in accordance with an embodiment of the invention; and

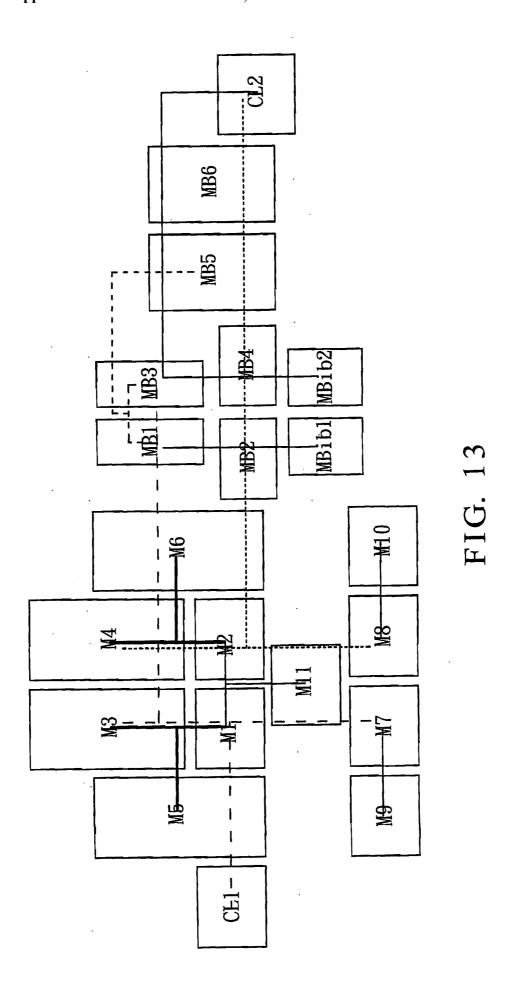

[0024] FIG. 13 is a schematic diagram of a result of a layout of FIG. 5 in accordance with an embodiment of the invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

[0025] FIG. 2 is a flowchart of a method for analog placement and global routing considering wiring symmetry in accordance with an embodiment of the invention. The method is executed in a computer to perform a layout for an analog circuit which is described by a netlist having a set of devices and wires connected thereon. In the method, step (A) is first executed for inputting the netlist, each device of the netlist having a design constraint, each design constraint corresponding to a priority.

[0026] FIG. 3 is a graph of a netlist in accordance with an embodiment of the invention. In this embodiment, the netlist is described in Simulation Program with Integrated Circuit (SPICE) format, and the design constraints are annotated into the netlist. The annotations are started with the symbol "\*". As shown in FIG. 3, transistor M1 has the design constraints Symmetry1 and Proximity1. The constraints can be done by designers or by automatic pattern recognition.

[0027] In other embodiments, the design constraints can be stored in another file other than the SPICE file for the analog circuit.

[0028] In other embodiments, step (A) can input the circuit diagram drawn by a schematic circuit layout tool. The circuit diagram has multiple devices and wires connected thereon, and the design constraints of each device can be arranged in an attribute field.

[0029] FIG. 4 shows the design constraints in accordance with an embodiment of the invention. As shown in FIG. 4, the types of design constraint include input, differential, mirroring, matching, proximity, power, and others. The design constraints of input, differential, mirroring, matching, proximity, power, and others have priorities of 6, 5, 4, 3, 2, 1 and 0, respectively, wherein the priorities are in descending order, i.e., number 6 is the highest priority and number 0 is the lowest priority.

[0030] Step (B) establishes a hierarchical constraint tree based on the design constraint and corresponding priority of each device.

[0031] In constraint-driven placement, the circuit analysis is the most important step. In this embodiment, this step builds up the hierarchical constraint tree of an analog circuit and represents each symmetry constrained module as a tree node. The hierarchical constrain tree structure is generated based on the functionalities of the devices.

[0032] Accordingly, step (C) performs a sorting on the devices based on the priorities in order to establish a constraint library. When design constraints have identical priority, the alphabetic order is used. For example, when both Proximity2 and Proximity3 are simultaneously existed in the same device, Proximity2 is processed before Proximity3.

[0033] FIG. 5 is a circuit diagram of an operational amplifier in accordance with an embodiment of the invention. The operational amplifier can be a folded cascade operational amplifier. FIG. 6 is a schematic diagram of a corresponding hierarchical constraint tree to the operational amplifier of FIG. 5 in accordance with an embodiment of the invention. As shown in FIG. 5, the differential signal passes into devices M1 and M2. Therefore, these two devices have to be constrained by the symmetry constraint and form the input stage.

[0034] As shown in FIG. 6, a proximity constraint covers a device mirroring constraint and a device matching constraint. It can be seen in FIG. 5 that using the proximity constraint can tie a symmetry constrained module and its connected devices together, thus considering the wiring symmetry constraint among them.

[0035] As shown in FIG. 6, each node in the hierarchical constraint tree is associated with a priority, which is labeled in a diamond-shaped frame attached to each node. A module or device with higher priority is placed earlier than the module or device with lower priority. The priority is propagated upwards to the root. The parent's priority inherits the maximum priority of his descendants.

[0036] Step (D) performs a placement on each device according to the hierarchical constraint tree, wherein the possible shapes of each device are represented by a shape curve.

[0037] Step (D) first processes the device with input signal, i.e., Mirroring1 in FIG. 6, and places the connected devices in a placement queue based on their connection relationship. The placement order in the queue is based on the priority of each device.

[0038] When the connected devices have the same proximity constraint, they are placed directly in the placement queue. For example, transistor M11 and the corresponding Mirroring1 have the same proximity constraint (Proximity 1), M11 and Mirroring1 are thus placed directly in the placement queue.

[0039] When the connected devices belong to different proximity constraints, all constrains with the same functionality are placed in the placement queue. For example, Proximity2 is placed in the queue as Mirroring2 connects to Mirroring1. When the priority of a newly placed proximity constraint is higher, the newly placed proximity constraint is placed at the forefront of the queue. Accordingly, the devices with higher priorities are processed first to achieve better device and wiring symmetry.

**[0040]** The dimensions of devices and placement results form a shape curve. Thus, a device folding technique is adopted to increase the flexibility of placement, and possible shapes of each device are represented by a shape curve. The device folding technique can fold up an analog device as a squarer shape.

[0041] Device folding can decompose a device of large aspect into small devices of uni-aspect ratio. In addition, the feasible folded dimension is subject to the aspect ratio constraint.

[0042] Each folded dimension is regarded as a candidate dimension and memorized as a point in the shape curve. Namely, the shape curve of each device is generated by the device folding technique. In other words, the number of points in a shape curve is decided by the number of feasible folded dimensions.

[0043] It is noted that even under the same area, an arbitrary dimension may be infeasible for an analog device, so the

number of feasible dimensions is finite and associated with the possible shapes, i.e., the shape curve is naturally discrete. [0044] FIG. 7 is a schematic diagram of a device folding in accordance with an embodiment of the invention. FIG. 8 is a graph of a shape curve generated by performing the device folding of FIG. 7. Using shape curves can reduce the solution space by pruning redundant solutions. Doing so can increase the flexibility of placement and enhance the symmetry in physical behavior.

[0045] In this embodiment, the priority of each device is used as the placement order, i.e., a device with higher priority is placed firstly. When the placement order and possible shape of each device are decided, a placement method is considered. In this embodiment, a force-directed method is used to place each device.

[0046] This embodiment applies the absolute coordinate because each device is placed to a certain position to minimize the wiring difference. The ideal position of a newly encountered device or a constrained module is decided by a force directed method considering its connections.

[0047] The ideal position is usually at the center of the current partial placement. The next step is legalization, pushing the newly placed device/module along one direction until no overlapping. Because the contours of placed devices are different in four directions, the legalization of the newly placed device/module considers four directions sequentially. The matching module is pre-placed before being added into the layout.

[0048] FIG. 9 is a schematic diagram of force-directed placement in accordance with an embodiment of the invention. As shown in FIG. 9, M5 and M6 are newly placed devices, and M1, M2, and M11 are placed devices. As shown in FIGS. 9(b)-(e), the ideal positions are calculated by the force-direction method considering the connections, and the devices M5 and M6 are pushed along the four directions until no overlapping.

[0049] Since each point in the shape curve represents the possible shape of a device, the above operation is applied to each point (i.e., the possible shapes) in the shape curve. Due to the placement symmetry, a flipping approach can be applied to save the required computation time.

[0050] As shown in FIG. 9(f), the fifth placement is selected for the mirror module. Due to the symmetry of the mirror module, the placement is more flexible.

[0051] Step (E) calculates a corresponding cost function for each placement of the device, and selects an optimum placement of the device according to the cost functions.

[0052] The cost function for each placement of the device is defined as follows:

$$\label{eq:cost} \begin{split} & \operatorname{Cost}(P) \!\!=\!\! \alpha \mathbf{x} (1 \! + \! \operatorname{Total\_Wiring\_Difference}) \mathbf{x} \\ & \operatorname{Wire-length} \! + \! \operatorname{Aspect\_RatioxLayout\_Area}, \end{split}$$

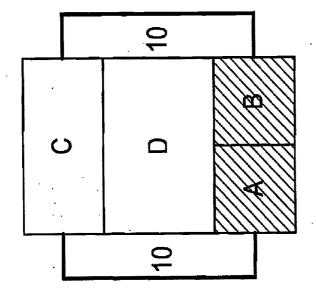

where  $\alpha$  is used to balance a weight between wire length and area, and Total\_Wiring\_Difference is used to estimate wiring symmetry. The cost is increased as Total\_Wiring\_Difference increasing, which indicates that the placement result does not guarantee the wiring symmetry. The Wirelength is an estimate of total wire length, and in this case Manhattan distance is used to estimate the wire length. Aspect\_Ratio is a ratio of length and width. Layout\_Area represents layout area. FIG.  $10\,$  is a schematic diagram of Total\_Wiring\_Difference in accordance with an embodiment of the invention. As shown in FIG.  $10\,$ , the wiring symmetry is better as Total\_Wiring\_Difference is smaller.

[0053] FIG. 11 is a schematic diagram of a cost function for the placement of FIGS. 9(b)-(f) in accordance with an embodiment of the invention. As shown in FIG. 11, the data shows that, due to the wiring difference, the cost is higher when both M5 and M6 are placed at left or right side. Cost=1585 when M5 and M6 are placed at both sides, which is not obviously advantageous because M5 and M6 have different sizes than M1 and M2 so that the wire length is longer than the wire length of M5 and M6 placed at the upper. The cost where both M5 and M6 are placed at the upper is relatively preferred among the placement topologies in FIG.

[0054] Step (F) establishes a rectilinear Steiner minimal tree (RSMT) for each wire. The RSMT is commonly used for routing. The RSMT for each routing point is established, and all routing points are connected by another routing method.

[0055] Step (G) performs an analog routing by a pattern routing and then a maze routing on the remaining wires which cannot be routed by the pattern routing.

[0056] Before routing, a wiring symmetry analysis is performed on each wire, which is based on a constraint library to sum the priorities of connected devices to each wire so as to generate a corresponding routing weight and thus perform the routing based on the routing weight.

[0057] FIG. 12 is a schematic diagram of a wiring symmetry analysis in accordance with an embodiment of the invention. As shown in FIG. 12, Net2 connects to M1, M2, and M11, with the priorities 6, 6 and 1, and in this case Net2 with a score of 13 higher than the other wires is routed first. Further, Net1, Net3 are a pair of symmetry wires to have the same score, and in this case Net1 and Net3 are routed tandem. Accordingly, the wiring symmetry feature can be maintained. [0058] FIG. 13 is a schematic diagram of a result of a layout of FIG. 5 in accordance with an embodiment of the invention. As shown in FIG. 13, to automate the analog layout generation, a deterministic placement and global routing algorithm in the invention is developed to maintain both the device and wiring symmetry. The prior analog design automation considers only the placement topology among devices and neglects the quality of signal paths impacting on the quality of the analog design automation. The symmetric devices are obviously affected by their signal paths. If the signal paths to the symmetry devices are not symmetric, it will result in signal mismatch and may cause the circuit failure. The invention merges the device folding into shape curve combination thus increasing the flexibility on symmetry.

[0059] In view of the foregoing, the contributions of the method for analog placement and global routing include:

[0060] 1. Considering wiring symmetry: Since the analog layout is quite sensitive to the layout geometry, especially to symmetric devices, not only the device symmetry but also the wiring symmetry should be considered. The wiring symmetry is maintained not only for the routing within symmetric devices but also for the routing among them and their connected devices, thus effectively raising the circuit performance.

[0061] 2. Placement priority: The device and wiring symmetry and the signal flow in an analog circuit are considered to decide the placement priorities of each device.

[0062] 3. Measuring wiring symmetry: The simple cost function is defined to reflect wiring symmetry.

[0063] 4. Utilizing device folding: Device folding allows an analog layout to maintain its physical behavior and the same area, with applying various aspect ratios. We use the device

folding to decompose a device of large aspect into small devices of uni-aspect ratio for selecting the optimum folded dimension in placement, thus increasing the flexibility and feasibility on the analog design automation.

[0064] Although the present invention has been explained in relation to its preferred embodiment, it is to be understood that many other possible modifications and variations can be made without departing from the spirit and scope of the invention as hereinafter claimed.

### What is claimed is:

- 1. A method for analog placement and global routing considering wiring symmetry, which is executed in a computer to perform a layout for an analog circuit described by a netlist having a set of devices and wires connected thereon, the method comprising the steps of:

- (A) inputting the netlist, each device of the netlist having a design constraint, each design constraint corresponding to a priority;

- (B) establishing a hierarchical constraint tree based on the design constraint and corresponding priority of each device:

- (C) performing a sorting on the devices based on the priorities:

- (D) performing a placement on each device according to the hierarchical constraint tree, wherein possible shapes of each device are represented by a shape curve;

- (E) calculating a corresponding cost function for each placement of the device, and selecting an optimum placement of the device according to the cost functions;

- (F) establishing a rectilinear Steiner minimal tree (RSMT) for each wire; and

- (G) performing an analog routing.

- 2. The method as claimed in claim 1, wherein the design constraint is selectively to be input, differential, mirroring, matching, proximity, power, and others.

- 3. The method as claimed in claim 2, wherein the design constraints of input, differential, mirroring, matching, proximity, power, and others have descending priorities of 6, 5, 4, 3, 2, 1 and 0, respectively.

- **4**. The method as claimed in claim **3**, wherein for the design constrains with identical priority, an alphabetic order is used to establish the constraint library.

- 5. The method as claimed in claim 4, wherein the netlist is described in a SPICE format, and the design constraints are annotated into the netlist.

- 6. The method as claimed in claim 5, wherein a structure of the hierarchical constrain tree is generated based on functionalities of the devices of the netlist.

- 7. The method as claimed in claim 6, wherein a proximity design constraint in the hierarchical constraint tree covers a mirroring design constraint and a matching design constraint.

- **8**. The method as claimed in claim **7**, wherein the shape curve of each device is generated by a device folding.

- 9. The method as claimed in claim 8, wherein a number of points in each shape curve correspond to a number of feasible folded dimensions.

- 10. The method as claimed in claim 9, wherein the shape curve is discrete.

- 11. The method as claimed in claim 10, wherein a force-directed method is used to place each device.

- 12. The method as claimed in claim 11, wherein step (G) comprises: (G1) performing a wiring symmetry analysis on each wire by using the constraint library to sum all priorities of connected devices to the wire to thereby generate a corresponding routing weight; and (G2) performing the analog routing based on the corresponding routing weight of each wire.

- 13. The method as claimed in claim 12, wherein step (G) performs the analog routing on the wires by a pattern routing and then by a maze routing on remaining wires which cannot be routed by the pattern routing.

\* \* \* \* \*