## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2005/0146375 A1 Ker et al.

- Jul. 7, 2005 (43) Pub. Date:

- (54) CHARGE PUMP CIRCUIT SUITABLE FOR LOW-VOLTAGE PROCESS

- (76) Inventors: Ming-Dou Ker, Hsinchu (TW); Chia-Sheng Tsai, Taichung City (TW)

Correspondence Address: ROSENBERG, KLEIN & LEE 3458 ELLICOTT CENTER DRIVE-SUITE 101 **ELLICOTT CITY, MD 21043 (US)**

(21) Appl. No.: 10/861,359

(22)Filed: Jun. 7, 2004

(30)Foreign Application Priority Data

(TW)...... 93100084 Jan. 2, 2004

### **Publication Classification**

#### (57)**ABSTRACT**

The present invention discloses a charge pump circuit suitable for a low-voltage process. The charge pump circuit is composed of stages of the voltage amplifying circuits connected each other, and the operation of two adjacent stages of voltage amplifying circuit is controlled by two opposite set of the timing signals. Each stage of the voltage amplifying circuit has a coupled pair of a first complementary MOS (CMOS) transistor and a second CMOS transistor switching in accordance with a timing signal and an inverse timing signal inputted into the first and second capacitors. Then, two diode devices guide charges to next stage, and a voltage higher than the integrated circuit voltage source is outputted. The present invention has advantage of high pumping gain, and the reliability issue of the gate oxide layer in the low-voltage process can be also solved.

(PRIOR ART)

(PRIOR ART)

Fig. 3(a)

Fig. 5

# CHARGE PUMP CIRCUIT SUITABLE FOR LOW-VOLTAGE PROCESS

### BACKGROUND OF INVENTION

[0001] 1. Field of the Invention

[0002] The invention relates to a charge pump circuit, and more particularly, to a charge pump circuit suitable for a low-voltage process and having a high pumping gain.

[0003] 2. Description of the Prior Art

[0004] When using the general volatile memory devices, such as dynamic random access memory (DRAM) or static random access memory (SRAM), the stored data will be removed after turning the power off. If we want to keep the data after turning the power off, we should use the non-volatile memory devices, such as read-only memory (ROM), programmable read-only memory (PROM), electrically erasable programmable read-only memory (EPROM) and flash memory (Flash).

[0005] The EEPROM or Flash needs a charge pump circuit to provide a voltage higher than the integrated circuit voltage source to perform the program or erase procedure. The charge pump circuit can not only provide the high voltage required for operation of the memory devices but also provide the high voltage for any other purposes.

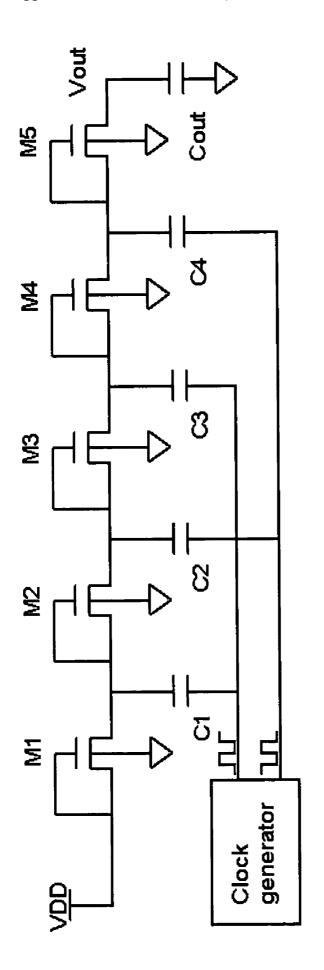

[0006] FIG. 1 shows a common charge pump circuit (called Dickson C.P), which is a 4-stage charge pump. The charge pump circuit provides memory devices the high voltage by controlling a series of connected NMOS transistors and capacitors to boost the voltage source ( $V_{\rm DD}$ ) stage by stage. But the threshold voltage (Vt) of the diodeconnected MOSFET is increased with the body effect while voltage of each pumping node is boosted, and that will cause the efficiency of charge pump worse. The aggravation of charge pump has great influence to the low-voltage source, and will cause the invalidity of the charge pump circuit in memory devices using low-voltage source.

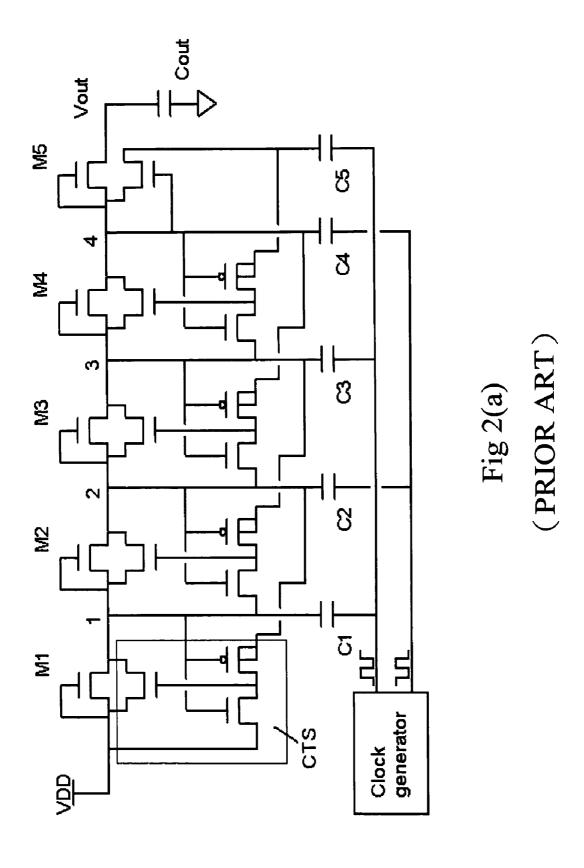

[0007] For improving the pumping gain, another charge pump circuit (called J.-T C.P) is developed. The charge pump circuit provides a method to transfer charges while the forward bias of the diode-connected MOSFET is lower than the threshold voltage. As shown in FIG. 2(a), a charge transfer circuits (CTS) is added into the charge pump circuit, and the MOSFET switch is timely opened or closed to be a charge transfer circuit to transfer charges. The pumping gain of the charge pump is improved to  $V_G = \Delta V \approx V_{DD}$  with those charge transfer circuits, and if the parasitic capacitance of each pumping node is ignored, the maximum voltage difference between each pumping stage will be  $V_{\rm d(max)} = V_{\rm DD} + V_{\rm G} = 2V_{\rm DD}$ . Please also refer to FIG. 2(b). The voltage difference between node 1 and node 2 is marked as V12, which has a maximum value  $2V_{DD}$  between time periods T1 and T3, and this situation is also happened on simultaneous V34 and V23 between time periods T2 and T4. If the voltage source is a typical voltage of manufacture process, such as 1.8V used in the 0.18- $\mu$ m process of the 40 Å thickness gate oxide layer, most MOSFET in the circuit will exceed the bearable voltage of the gate oxide layer (2\*1.8=3.6 V) and lead to the avalanche of the gate oxide layer and the invalidity of the device.

[0008] The conventional charge pump circuit has an exceeding high voltage on the gate oxide layer in the low-voltage manufacture process and the pumping gain of the conventional charge pump circuit is not high enough, so the present invention provides a charge pump circuit suitable for a low-voltage process and having a high pumping gain to overcome the disadvantages.

### SUMMARY OF INVENTION

[0009] It is therefore a primary objective of the claimed invention to provide a charge pump circuit suitable for a low-voltage process that has advantage of high pumping gain. The device is punily affected by the body effect, so the reliability issue of the gate oxide layer in the low-voltage process can be solved.

[0010] It is therefore another objective of the claimed invention to provide a charge pump circuit suitable for a low-voltage process that doesn't have problem of high voltage on the gate oxide layer, and this circuit is suitable for producing the high voltage applied to the low-voltage devices to overcome the overload problem on the gate oxide layer.

[0011] According to the claimed invention, a charge pump circuit is composed of stages of the voltage amplifying circuits connected each other, and the operation of two adjacent stages of voltage amplifying circuit is controlled by two opposite set of the timing signals. Each stage of the voltage amplifying circuit has a coupled pair of a first complementary MOS (CMOS) transistor and a second CMOS transistor, wherein the first CMOS transistor is connected to a corresponding first capacitor to perform switching operation in accordance with a timing signal inputted into the first capacitor and the second CMOS transistor is connected to a corresponding second capacitor to perform switching operation in accordance with an inverse timing signal inputted into the second capacitor. Then, two diode devices are individually connected to gate electrodes of the first and second CMOS transistors for guiding charges to next stage or to output. Finally, a voltage higher than the integrated circuit voltage source is outputted at the voltage-outputting terminal for the memory device.

[0012] These and other objectives of the present invention will no doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and drawings.

### BRIEF DESCRIPTION OF DRAWINGS

[0013] FIG. 1 is a schematic diagram of a charge pump circuit according to the prior art.

[0014] FIGS. 2(a) and 2(b) are a schematic diagram and a voltage signal diagram of another charge pump circuit according to the prior art.

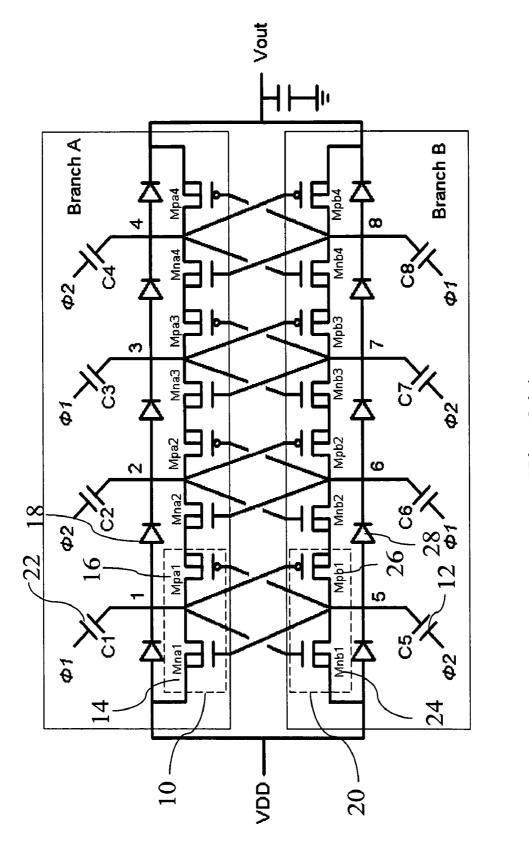

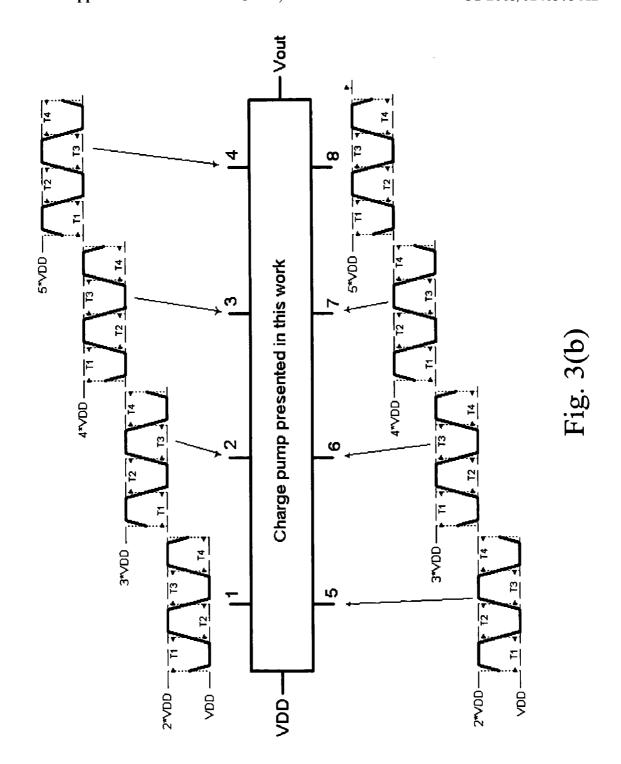

[0015] FIGS. 3(a) and 3(b) are a schematic diagram and a voltage signal diagram of a charge pump circuit according to the present invention.

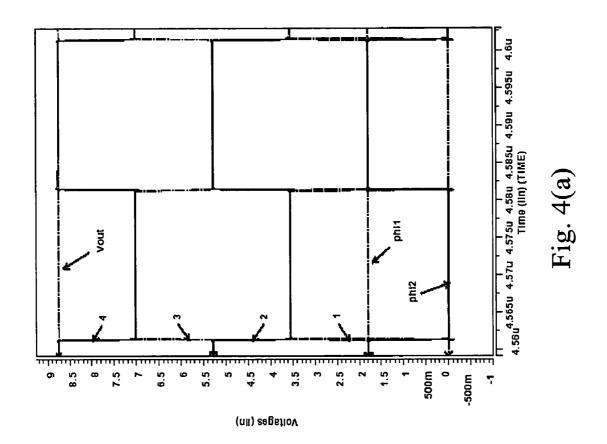

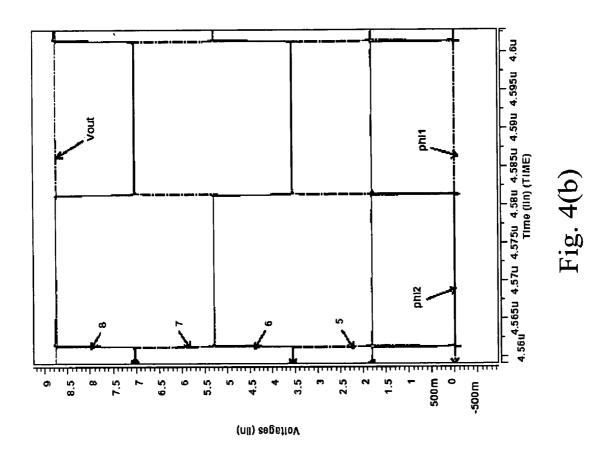

[0016] FIGS. 4(a) and 4(b) are diagrams of voltage wave at every nodes of the charge pump circuit according to the present invention.

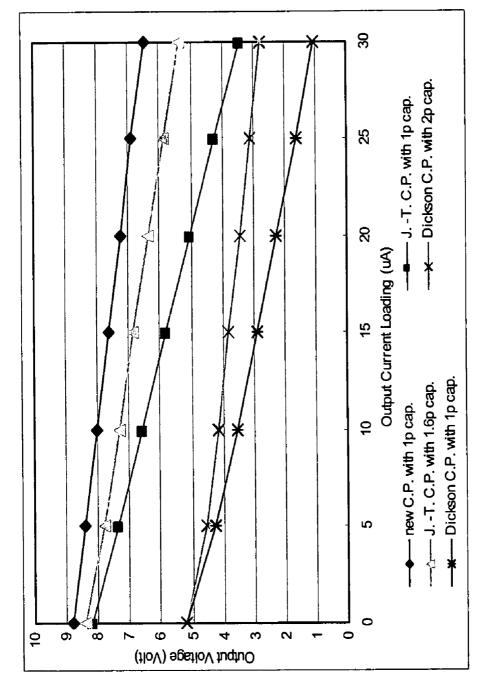

[0017] FIG. 5 is a comparison curve of the output voltage under different output currents of the present invention and the prior art.

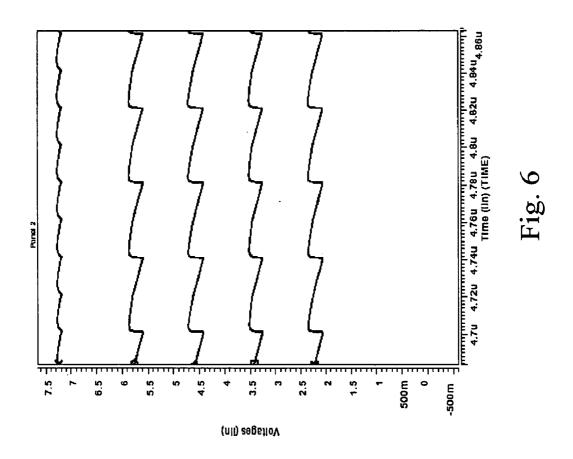

[0018] FIG. 6 is a comparison curve of the output voltage under different time of the present invention and the prior art.

[0019] 10 the first CMOS transistor

[0020] 12 the first capacitor

[0021] 14 NMOS transistor

[0022] 16 PMOS transistor

[0023] 18 diode device

[0024] 20 the second CMOS transistor

[0025] 22 the second capacitor

[0026] 24 NMOS transistor

[0027] 26 PMOS transistor

[0028] 28 diode device

### DETAILED DESCRIPTION

[0029] The charge pump circuit is popularly used in the integrated circuits, such as in the memory IC, the analog or digital IC and the LCD drive IC. With the progression of process, the voltage tolerance of devices is getting smaller, and the present invention discloses a charge pump circuit suitable for a low-voltage process that has high pumping gain and no exceeding voltage on the gate oxide layer.

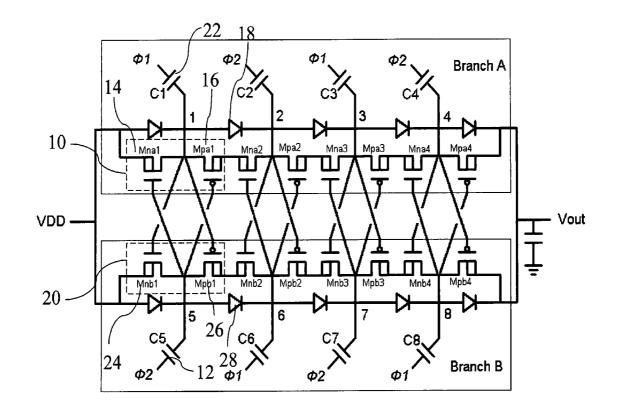

[0030] The claimed charge pump circuit is composed of a plurality of stages (1-stage to n-stage) of voltage amplifying circuits connected each other, and the operation of two adjacent stages of voltage amplifying circuits is controlled by two opposite timing signals. The embodiment in FIG. 3(a) uses a 4-stage voltage amplifying circuit to explain the present invention.

[0031] As shown in FIG. 3(a), each stage of the voltage amplifying circuit comprises a coupled pair of a first complementary MOS (CMOS) transistor 10 and a second CMOS transistor 20. The first CMOS transistor 10 is connected to a corresponding first capacitor (C5) 12 to perform switching operation in accordance with a timing signal ( $\phi$ 2) inputted into the first capacitor 12, and the first CMOS transistor 10 is composed of a NMOS transistor (Mna1~Mna4) 14 and a PMOS transistor (Mpa1~Mpa4) 16. The source electrode of the NMOS transistor 14 is connected to a voltage inputting terminal, and the source electrode of the PMOS transistor 16 is connected to the voltage inputting terminal of next stage. The drain electrodes of the NMOS transistor 14 and the PMOS transistor 16 are coupled to the first capacitor 12. In addition, the second CMOS transistor 20 is connected to a corresponding second capacitor (C1) 22 to perform switching operation in accordance with an inverse timing signal  $(\phi 1)$  inputted into the second capacitor 22, and the second CMOS transistor 20 is also composed of a NMOS transistor (Mnb1~Mnb4) 24 and a PMOS transistor (Mpb1~Mpb4) 26. The source electrode of the NMOS transistor 24 is connected to a voltage inputting terminal, and the source electrode of the PMOS transistor 26 is connected to the voltage inputting terminal of next stage. The drain electrodes of the NMOS transistor 24 and the PMOS transistor 26 are also coupled to the second capacitor 22.

[0032] Each stage of the voltage amplifying circuit further comprises two diode devices 18, 28 individually connected to gate electrodes of the first and second CMOS transistors 10, 20. The diode devices 18, 28 are used for limiting charges accumulating on gate electrode of the CMOS transistors 10, 20 to flow in one direction and guiding charges to next stage through the diode devices 18, 28. In addition, when the voltage difference between the diode devices 18, 28 is only 0.7V, the diode devices 18, 28 will be closed without guiding charges. At this moment, the CMOS transistors 10, 20 keep guiding charges to the next stage till voltages at both ends are equal. A voltage higher than the integrated circuit voltage source can be obtained at the voltage outputting terminal by continuously outputting and accumulating charges.

[0033] After referring FIG. 3(a), the timing signals  $\phi 1$  and  $\phi 2$  are opposite signals, and have the same amplitude with the voltage source (VDD). The charge pump circuit has two equivalent parts marked with Branch A and Branch B, and the both architectures are similar besides the timing signals. If the timing signal of the first and third stages of the voltage amplifying circuit in Branch A is  $\phi 1$ , the timing signal in Branch B will be  $\phi 2$ . Oppositely, if the timing signal of the first and third stages of the voltage amplifying circuit in Branch A is  $\phi 2$ , the timing signal in Branch B will be  $\phi 1$ . These two opposite timing signals  $\phi 1$  and  $\phi 2$  are produced by a timing signal generator.

[0034] Moreover, each stage of the claimed voltage amplifying circuit can be normally opened and closed, and each branch can be an independent charge pump circuit. Since the timing signals of Branch A and Branch B are inverse, the waveform at nodes 1-4 and nodes 5-8 are also inverse. The waveform at nodes 1-8 are shown in FIG. 3(b).

[0035] The operation status of each voltage amplifying circuit (also called the charge transfer circuit, CTS) is confirmed below. Firstly, to the first stage of the voltage amplifying circuit, as shown in **FIG. 3**(*b*), the timing signal  $\phi 1$  in time period T1 is low and  $\phi 2$  is high. The rated voltage of V15 is -VDD, so the switch Mna1 of the MOSFET is opened to drive charges flowing from the voltage source terminal to node 1 and the switch Mnb1 is closed to stop charges flowing from node 5 to the voltage source terminal. On the other hand, in time period T2, the ideal operating voltage of V15 is VDD. For stopping charges flowing from node 1 to the voltage source terminal, Mna1 is closed and Mnb1 is opened to drive charges flowing from the voltage source terminal to node 5. To other stages, illustrated with the second stage of the voltage amplifying circuit, the timing signal  $\phi 1$  in time period T1 is low and  $\phi 2$  is high. The rated voltages of V15 and V26 are -VDD and VDD, so the switches Mpa1 and Mna2 of the MOSFET is opened to drive charges flowing from node 1 to node 2 and the switches Mpb1 and Mnb2 are closed to stop charges flowing from node 6 to node 5. On the other hand, in time period T2, the ideal operating voltages of V15 and V26 are VDD and -VDD. For stopping charges flowing from node 2 to node 1, Mpa1 and Mna2 are closed and Mpb1 and Mnb2 are opened to drive charges flowing from node 5 to node 6. To the outputting stage, the timing signal  $\phi 1$  in time period T1 is

low and  $\phi 2$  is high. The rated voltage of V48 is VDD, so the switch Mpa4 of the MOSFET is opened to drive charges flowing from node 4 to the outputting node and the switch Mpb4 is closed to stop charges flowing from the outputting node to node 8. On the other hand, in time period T2, the ideal operating voltages of V48 is -VDD. For stopping charges flowing from the outputting node to node 4, Mpa4 is closed and Mpb4 is opened to drive charges flowing from node 8 to the outputting node. Hence, according to the above description, Branch A and Branch B will output a high voltage alternately.

[0036] The circuit is simulated with a SPICE model of a TSMC 0.18  $\mu$ m transistor and the result is shown in FIGS. 4(a) and 4(b). FIGS. 4(a) and 4(b) are diagrams of voltage wave at nodes 1-8 of the charge pump circuit with 1.8V voltage supply and 5  $\mu$ A outputting load current, and the result is similar to that anticipated. The trivial difference between the output voltage Vout 8.39V and the ideal value 5\*VDD=9V is produced by the parasitic capacitor and outputting load current.

[0037] The present invention and two prior arts are compared now. Firstly, to the reliability, the diode-connected MOSFET is used for driving charges to the next stage in the Dickson C.P charge pump circuit. When the diode-connected MOSFET is OFF to avoid charges flowing back, the voltage across the gate oxide layer of the diode-connected MOSFET is 2\*VDD-Vt. If VDD is the rated supplying voltage, the diode-connected MOSFET will be damaged in a short time. In the J.-T charge pump circuit, not only the diode-connected MOSFET but also the charge transfer circuit and its controlling circuit are operated in exceeding voltages at both ends of the gate oxide layer. The only method to safely operate in the low-voltage process is lowering the supplying voltage to about 0.5\*VDD, and that is not enough for the memory device. In the present invention, the charge pump circuit will overcome these problems and the reliability issue is also considered without lowering the supplying voltage.

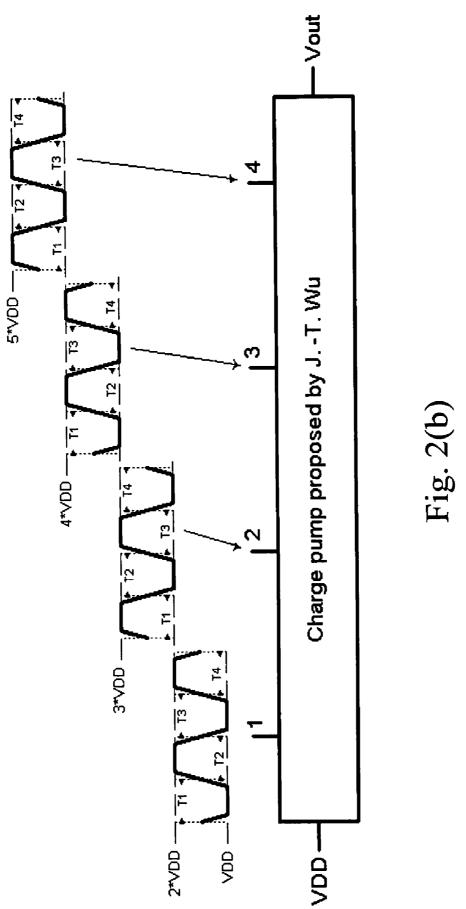

[0038] FIG. 5 is a comparison curve of the output voltage under different output currents of the present invention and the prior art. All the compared circuits have 2 p voltage-regulating capacitors. Obviously, in the situation of using same 1 p driving capacitor, the charge pump circuit of the present invention is better than that of the prior arts, especially in the situation of high current load. Since the charge pump circuit of the present invention has two branches to alternatively drive charges to the outputting nodes, and the voltage variance at each pumping node is

$$\Delta V = V_{CLK} \times \frac{C_{pump}}{C_{pump} + C_{par}} - \frac{I_O}{2f(C_{pump} + C_{par})} \approx V_{CLK} - \frac{I_O}{2fC_{pump}}$$

[0039] so the curve slope of the claimed charge pump circuit is about half of that of the prior arts.

[0040] Please refer to FIG. 6, which is a diagram of the outputting waveforms of the charge pump circuits under the fixed outputting current load 20µA. From high to low, the curves means the claimed charge pump circuit with 1 p driving capacitor, the J.-T charge pump with 1.6 p driving capacitor, the J.-T charge pump with 1 p driving capacitor,

the Dickson charge pump with 2 p driving capacitor, and the Dickson charge pump with 1 p driving capacitor. Thus it can be seen the curve of the charge pump circuit of the present invention is more stable than that of two prior charge pump circuits.

[0041] In the low-voltage process, the reliability issue of the gate oxide layer is very important. When a charge pump circuit is manufactured with a low-voltage process, the consideration of both reliability and performance will make the design complex and difficult. In contrast to the prior art, the present invention discloses a novel charge pump circuit to solve the disadvantages. The present invention can be safely operated in the low-voltage process without danger of avalanche, and can provide a higher and more stable outputting voltage. Hence, the present invention can not only be used in the low-voltage process but also have advantage of high pumping gain. This circuit doesn't have the problem of exceeding voltage of the gate oxide layer and is suitable for providing the high voltage in the low-voltage devices. In addition, this circuit can overcome the overload problem on the gate oxide layer and improve the reliability of the gate oxide layer.

[0042] Those skilled in the art will readily observe that numerous modifications and alterations of the device may be made while retaining the teachings of the invention. Accordingly, the above disclosure should be construed as limited only by the metes and bounds of the appended claims.

What is claimed is:

- 1. A charge pump circuit suitable for a low-voltage process, the charge pump circuit can produce a voltage higher than a integrated circuit voltage source and has n stage of a plurality of voltage amplifying circuits, each stage of the voltage amplifying circuit comprises:

- a coupled pair of a first complementary MOS (CMOS) transistor and a second CMOS transistor, the first CMOS transistor is connected to a corresponding first capacitor to perform switching operation in accordance with a timing signal inputted into the first capacitor, the second CMOS transistor is connected to a corresponding second capacitor to perform switching operation in accordance with an inverse timing signal inputted into the second capacitor; and

two diode devices individually connected to gate electrodes of the first and second CMOS transistors for guiding charges to next stage or to output.

- 2. The charge pump circuit of claim 1, wherein the first CMOS transistor is composed of a NMOS transistor and a PMOS transistor.

- 3. The charge pump circuit of claim 1, wherein the second CMOS transistor is composed of a NMOS transistor and a PMOS transistor.

- 4. The charge pump circuit of claim 2, wherein source electrode of the NMOS transistor of each CMOS transistor is connected to a voltage inputting terminal, source electrode of the PMOS transistor is connected to the voltage inputting terminal of next stage, and drain electrodes of the NMOS transistor and the PMOS transistor are connected to the coupled capacitors.

- 5. The charge pump circuit of claim 3, wherein source electrode of the NMOS transistor of each CMOS transistor is connected to a voltage inputting terminal, source electrode of the PMOS transistor is connected to the voltage inputting

terminal of next stage, and drain electrodes of the NMOS transistor and the PMOS transistor are connected to the coupled capacitors.

- 6. The charge pump circuit of claim 1, wherein the diode device is used for limiting charges accumulating on gate electrode of the CMOS transistor to flow in one direction.

- 7. The charge pump circuit of claim 1, wherein the timing signal and the inverse timing signal are produced by a timing signal generator.

- 8. A charge pump circuit suitable for a low-voltage process, the charge pump circuit can produce a voltage higher than a integrated circuit voltage source, the charge pump circuit at least comprises:

- a plurality of stages of voltage amplifying circuits connected each other, each voltage amplifying circuit has a coupled pair of a first CMOS transistor and a second CMOS transistor, the first CMOS transistor is connected to a corresponding first capacitor to perform switching operation in accordance with a timing signal inputted into the first capacitor, the second CMOS transistor is connected to a corresponding second capacitor to perform switching operation in accordance with an inverse timing signal inputted into the second capacitor; and

- a plurality of diode devices individually connected to gate electrodes of the first and second CMOS transistors of the voltage amplifying circuit for guiding charges to next stage or to output.

- The charge pump circuit of claim 8, wherein each first CMOS transistor is composed of a NMOS transistor and a PMOS transistor.

- **10**. The charge pump circuit of claim 8, wherein each second CMOS transistor is composed of a NMOS transistor and a PMOS transistor.

- 11. The charge pump circuit of claim 9, wherein source electrode of the NMOS transistor of each CMOS transistor is connected to a voltage inputting terminal, source electrode of the PMOS transistor is connected to the voltage inputting terminal of next stage, and drain electrodes of the NMOS transistor and the PMOS transistor are connected to the coupled capacitors.

- 12. The charge pump circuit of claim 10, wherein source electrode of the NMOS transistor of each CMOS transistor is connected to a voltage inputting terminal, source electrode of the PMOS transistor is connected to the voltage inputting terminal of next stage, and drain electrodes of the NMOS transistor and the PMOS transistor are connected to the coupled capacitors.

- 13. The charge pump circuit of claim 8, wherein the diode device is used for limiting charges accumulating on gate electrode of the CMOS transistor to flow in one direction.

- 14. The charge pump circuit of claim 8, wherein the timing signal and the inverse timing signal are produced by a timing signal generator.

- 15. The charge pump circuit of claim 8, wherein operation of two adjacent stages of voltage amplifying circuit is controlled by two opposite set of the timing signals.

\* \* \* \* \*