## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2004/0241921 A1 Yeh et al.

(43) **Pub. Date:**

Dec. 2, 2004

#### (54) METHOD FOR FABRICATION OF POLYCRYSTALLIN SILICON THIN FILM **TRANSISTORS**

(75) Inventors: Ching-Fa Yeh, Hsinchu (TW); Tien-Fu Chen, Hsinchu (TW); Jen-Chung Lou, Hsinchu (TW)

> Correspondence Address: TROXELL LAW OFFICE PLLC **SUITE 1404 5205 LEESBURG PIKE** FALLS CHURCH, VA 22041 (US)

(73) Assignee: National Chiao Tung University

10/601,701 Appl. No.:

(22)Filed: Jun. 24, 2003

(30)Foreign Application Priority Data

#### **Publication Classification**

- (51) **Int. Cl.**<sup>7</sup> ...... **H01L** 21/00; H01L 21/84

#### **ABSTRACT** (57)

The present invention provides a method for fabrication of polycrystalline silicon thin film transistors, which comprises polysilicon spacer capping onto the sidewall of the active layer in thin film transistors by an isotropic dry etching for silicon film. This method can suppress the shrinkage of the active layer during recrystallization by laser. Large grains can be formed in the channel after recrystallization of high-energy continuous wavelength laser or recrystallization of excimer laser annealing on active layer. This process does not require any additional mask. Uniform arrangement of grain boundaries and large grain sizes can promote device performance uniformity. This technique will play an important role in the fields of low temperature polycrystalline silicon thin film transistors (LTPS-TFTs).

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

#### METHOD FOR FABRICATION OF POLYCRYSTALLIN SILICON THIN FILM TRANSISTORS

#### REFERENCE CITED

[0001] 1. U.S. Pat. No. 6,495,405.

[0002] 2. U.S. Pat. No. 5,395,481.

[0003] 3. U.S. Pat. No. 5,021,119.

[**0004**] 4. U.S. Pat. No. 4,330,363.

[0005] 5. U.S. Pat. No. 4,592,799.

[0006] 6. Ching-Wei Lin et. al., "High-performance low-temperature Poly-si TFTs crystallized by excimer laser irradiation with Recessed-Channel Structure", IEEE Electron Devices Lett., vol.22, pp.269-271, 2001.

[0007] 7. G. K. Giust et. al., "Performance improvement obtained for thin-film transistors fabricated in prepatterned laser-recrystallized polysilicon", IEEE Electron Devices Lett., vol.18, pp.296-298, 1997.

[0008] 8. G. K. Giust et. al., "Comparison of excimer laser recrystallized prepatterned and unpatterned silicon films on SiO<sub>2</sub>", J. Appl. Phys. 81, pp.1204-1211, 1997.

[0009] 9. Yasuyuki Sano et. al., "High-performance single-crystalline-silicon TFTs on a non-alkali glass substrate", in Tech. Dig. IEDM, 2002.

#### FIELD OF THE INVENTION

[0010] The present invention relates to polycrystalline silicon thin film transistors for method of laser-recrystallized active layer. More particularly, the present invention form large silicon grain structure of the active layer without any additional mask.

#### BACKGROUND OF THE INVENTION

[0011] In growing thin film transistor display from low temperature polycrystalline silicon thin film transistor (LTPS-TFT) extending over amorphous silicon thin film transistor (a-si TFT), it has been proposed to use various conventional display devices, such as, personal digital assistant, digital camera, cell phone so as to substantially enhance resolution, brightness, size and electromagnetic disturbance by LTPS-TFT display.

[0012] However, such conventional laser annealing LTP-STFTs process has proven to be unsatisfactory. When forming the active layer of transistor after the laser recrystallization are used to fabricate LTPS-TFTs, the resulting silicon grain structure typically lacks uniform structure. Such non-uniformity is due to the small and irregular silicon grain which causes the difference of electric characteristic between elements. But, then the laser recrystallization after forming the active layer of transistor are used to fabricate LTPS-TFTs, the resulting surface tension induced shrinkages, which is caused by melting the silicon film. Therefore, the conventional method can not use to process of LTPS-TFTs.

[0013] The structure of TFT and silicon-on-insulator metal oxide semiconductor field effect transistor (SOI-MOSFET) is an insulated layer with poor thermo conductivity under

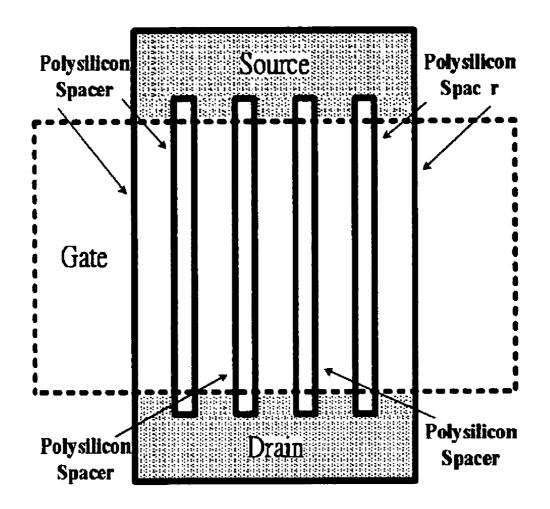

active layer. When working current of device is large to suddenly cause high temperature of active layer, mobility rate of carrier of active layer is to diminish, so the relative study reports the division of channel W into parallel connection of many small channels  $W_i$  to overcome self-heating effect as shown in FIG. 7. It shows a conventional view of settlement of self-heating effect. More particularly, such conventional division of channel W into parallel connection of many small channels  $W_i$  cannot be sufficiently overcome dispersing heat during the large working current so that the new invention is desirable.

#### SUMMARY OF THE INVENTION

[0014] Accordingly, the present invention discloses a method for fabrication of polycrystalline silicon thin film transistors, which comprises polysilicon spacer capping onto the sidewall of the active layer in thin film transistors by an isotropic dry etching for silicon film.

[0015] Therefore, the present invention provides uniform arrangement of grain boundaries and large grain sizes of active layer.

[0016] The main object of the present invention is to provide high mobility of field effect carrier of low temperature polycrystalline silicon thin film transistor (LTPS-TFT) and diminish difference between the devices. Therefore, the resolution of display substantially promote by present invention on pixel of the driving transistor to form small channel width have large silicon grain structure. Moreover, the laser-recrystallized process window is substantially broad to promote device performance and uniformity.

[0017] The other object of this invention is to trigger the no additional mask of recrystallization of melting lateral silicon after excimer laser annealing and improve the self-heating effect caused by dispersing the heat of high working current. The fabrication of polycrystalline silicon thin film transistors employ high energy continuous wavelength laser on dog-bone shape active layer by source-drain directional scanning to improve the channel of transistor of a silicon grain and then to hav high performance and good uniformity.

[0018] A method for fabrication of polycrystalline silicon thin film transistors comprising the steps of:

[0019] a) a substrate;

[0020] b) a buffer oxide formed on the substrate;

[0021] c) depositing a amorphous silicon film on the buffer oxide;

[0022] d) depositing a low-temperature oxide on the amorphous silicon film, wherein the low temperature oxide is employed to form a stop layer of silicon film dry etching after step d) process, a thermal insulating layer of laser annealing or a hard mask of the removal of polysilicon spacer after recrystallization;

[0023] e) forming amorphous silicon film by photoresist of hard mask on the low temperature polycrystalline silicon thin film transistor (LTPS-TFT) as a active layer, and then using a solution of silicon dioxide of wet isotropic etching to slightly go toward inner etching of the buffer oxide before or after the removal of the hard mask;

[0024] f) depositing another amorphous silicon film by connecting the active layer, and then forming the polysilicon spacer by dry etching behind either side of the active layer of the low temperature polycrystalline silicon thin film transistor (LTPS-TFT), and then forming large silicon grain structures of the active layer by recrystallization of high-energy continuous wavelength laser or recrystallization of excimer laser annealing on dog-bone shape active layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0025] The present invention will be better understood from the following detailed description of preferred embodiments of the invention, taken in conjunction with the accompanying drawings, in which

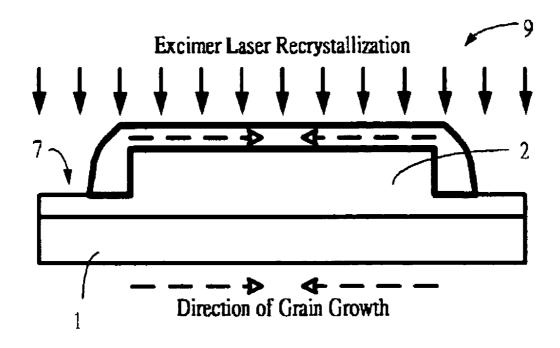

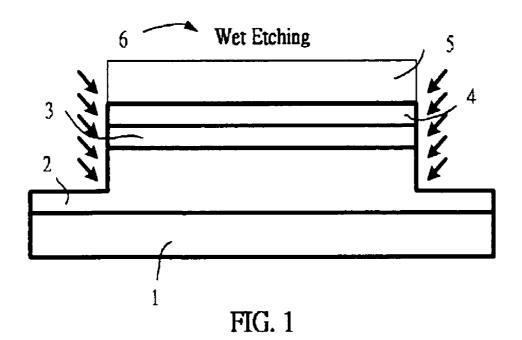

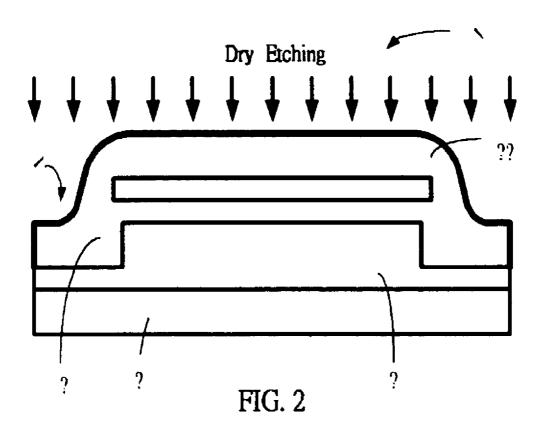

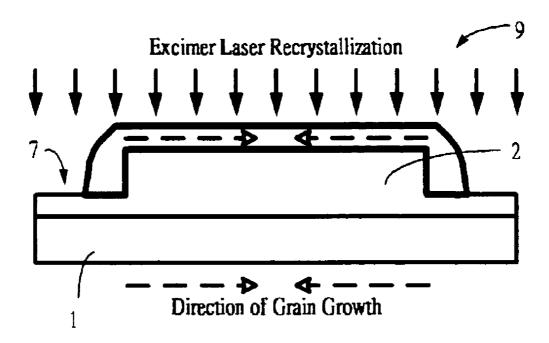

[0026] FIG. 1~FIG. 3 are schematic cross sections of the essential portion illustrating a process for polycrystalline silicon thin film transistors according to the present invention:

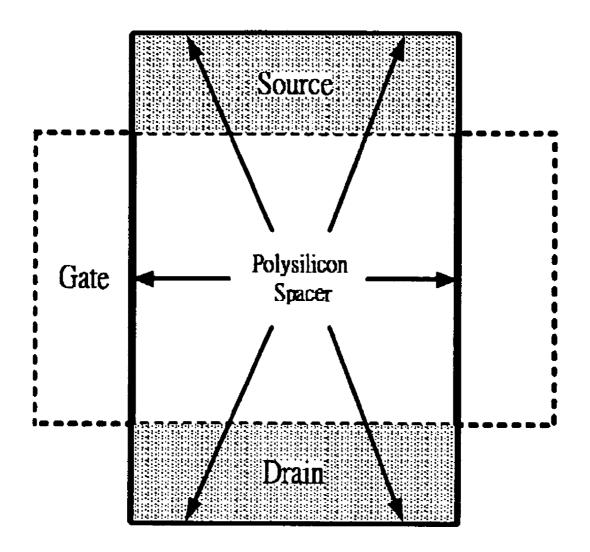

[0027] FIG. 4 is a schematic top plan view of relative position showing the laser-recrystallized active layer for polycrystalline silicon thin film transistors according to the present invention:

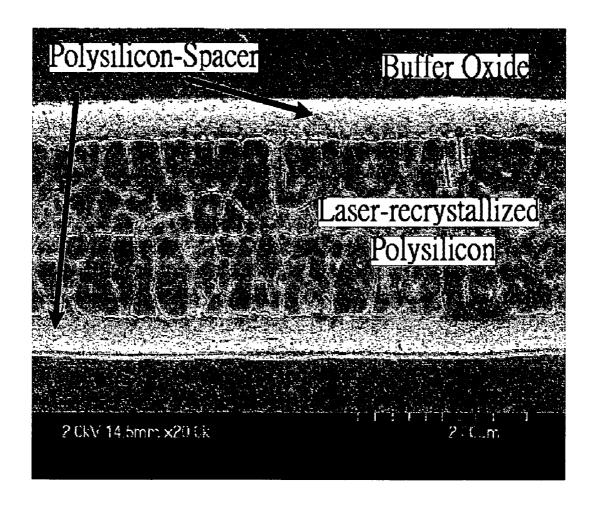

[0028] FIG. 5 is a scanning electron microscope (SEM) of silicon grain structures after excimer laser annealing (ELA) with silicon film thickness at 500 angstrom and line width at 2 microns according to the present invention;

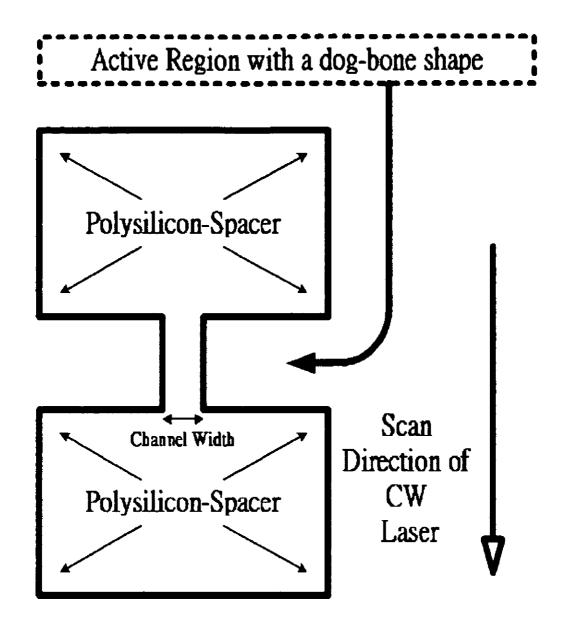

[0029] FIG. 6 is a schematic view showing active layer position and scanning direction of continuous-wavelength laser for recrystallization continuous-wavelength laser according to the present invention; and

[0030] FIG. 7 is a conventional view of settlement of self-heating effect.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0031] The following descriptions of the preferred embodiments are provided to understand the features and the structures of the present invention.

[0032] Please referring to the FIG. 1~FIG. 3, that are schematic cross sections of the essential portion illustrating a process for polycrystalline silicon thin film transistors comprising the steps of:

[0033] a) a substrate 1;

[0034] b) a buffer oxide 2 formed on said substrate 1;

[0035] c) depositing a amorphous silicon film 3 on the buffer oxide 2;

[0036] d) depositing a low temperature oxide 4 on the amorphous silicon film 3, wherein the low temperature oxide 4 is employed to form a stop layer of silicon film dry etching after step d) process, a thermal insulating layer of laser annealing or a hard mask of the removal of polysilicon spacer after recrystallization;

[0037] e) forming amorphous silicon film 3 by photoresist 5 of hard mask on the low temperature polycrystalline silicon thin film transistor (LTPS-TFT) as a active layer, and then using a solution of silicon dioxide

6 of wet isotropic etching to slightly go toward inner etching of the buffer oxide 2 before or after the removal of the hard mask;

[0038] f) depositing another amorphous silicon film 3aby connecting the amorphous silicon film 3, and then forming the polysilicon spacer 7 by dry etching 8 on either side of the another amorphous silicon film 3a and the amorphous silicon film 3. The polysilicon spacer 7 is selected from the group consisting of polycrystalline silicon film and amorphous silicon film. The polysilicon spacer 7 can replace dielectric material with oxide, nitride, and metal oxide, etc. and metal material with aluminum (Al), wolfram (W), molybdenum (Mo) and chromium (Cr), etc . . . And then can choice to cancel the polysilicon spacer 7 or not for the next process. The polysilicon spacer 7 form behind either side of the active layer (amorphous silicon film 3) of the low temperature polycrystalline silicon thin film transistor (LTPS-TFT), and then form large silicon grain structures of the active layer by recrystallization of highenergy continuous wavelength laser or recrystallization of excimer laser annealing 9 on dog-bone shape active layer as shown in FIG. 3. Therefore, the active layer generates temperature gradient.

[0039] The polysilicon spacer 7 form on either sid of the active lay r of selecting from the group consisting of thin film transistor (TFT) and silicon-on-insulator metal oxide semiconductor field effect transistor (SOI-MOSFET) in the low temperature or high temperature process. The polysilicon spacer 7 further comprises under either side of the active layer.

[0040] The main object of the polysilicon spacer 7 on laser-recrystallized either side of the active layer of thin film transistor (TFT) is to generate temperature gradient for recrystallization of active layer. Moreover, the order of forming polysilicon spacer 7 and recrystallization of active layer can change, forms recrystallization of active layer by selecting from the group consisting of excimer laser annealing (ELA), solid phase crystallization (SPC) or metalinduced lateral crystallization (MILC), and then forming the polysilicon spacer 7 on either side of said active layer of the thin film transistor (TFT) or silicon-on-insulator metal oxide semiconductor field effect transistor (SOI-MOSFET).

[0041] Please seeing the FIG. 4, it shows the relative position of gate 10, source 11, and drain 12 to be surrounded the side of active layer (amorphous silicon film 3) by the polysilicon spacer 7. Next, FIG. 5 is a scanning electron microscope (SEM) of silicon grain structures with silicon film thickness at 500 angstrom and line width at 2 microns after excimer laser annealing (ELA). It is clear that the elongated silicon grains measure over 1 micron with direction to side of active layer. Because the laser can't melt the thick boundary of active layer and can easily melt thin channel, and then the silicon grain trigger inner recrystallization by the spacer seed of the polysilicon spacer 7. Moreover, it also efficiently overcomes shrinkage effect of active layer caused by surface tension after melting of silicon film. Thus, the present invention is to efficiently improve the self-heating effect by forming thick polysilicon spacer 7 of no extra mask on side of small wide channel. FIG. 6 is a schematic view showing active layer position and scanning direction of continuous-wavelength laser for

recrystallization of continuous-wavelength laser according to embodiment of the present invention.

[0042] The present invention may be embodied in other specific forms without departing from the spirit of the essential attributes thereof; therefore, the illustrated embodiment should be considered in all respects as illustrative and not restrictive, reference being made to the appended claims rather than to the foregoing description to indicate the scope of the invention.

### What is claimed is:

- 1. A method for fabrication of polycrystalline silicon thin film transistors comprising the steps of:

- a) a substrate;

- b) a buffer oxide formed on said substrate;

- c) depositing a amorphous silicon film on said buffer oxide:

- d) depositing a low-temperature oxide on said amorphous silicon film, wherein said low temperature oxide is employed to form a stop layer of silicon film dry etching after step d) process, a thermal insulating layer of laser annealing or a hard mask of the removal of polysilicon spacer after recrystallization;

- e) forming amorphous silicon film by photoresist of hard mask on the low temperature polycrystalline silicon thin film transistor (LTPS-TFT) as a active layer, and then using a solution of silicon dioxide of wet isotropic etching to slightly go toward inner etching of said buffer oxide before or after the removal of said hard mask;

- f) depositing another amorphous silicon film by connecting said active layer, and then forming said polysilicon spacer by dry etching behind either side of said active

- layer of the low temperature polycrystalline silicon thin film transistor (LTPS-TFT), and then forming large silicon grain structures of said active layer by recrystallization of high-energy continuous wavelength laser or recrystallization of excimer laser annealing on dogbone shap active layer.

- 2. A method of claim 1, wherein said polysilicon spacer is selected from the group consisting of polycrystalline silicon film and amorphous silicon film.

- 3. A method of claim 1, wherein said polysilicon spacer of step 1) form on either side of said active layer of selecting from the group consisting of thin film transistor (TFT) and silicon-on-insulator metal oxide semiconductor field effect transistor (SOI-MOSFET) in the low temperature or high temperature process.

- **4**. A method of claim 1 further comprising under either side of said active layer.

- **5**. A method of claim 1, wherein said polysilicon spacer of step f) by recrystallization of high-energy continuous wavelength laser or recrystallization of excimer laser annealing on dog-bone shape active layer is to generate temperature gradient.

- 6. A method of claim 1, where said polysilicon spacer replace dielectric material with oxide, nitride, and metal oxide, etc. and metal material with aluminum (Al), wolfram (W), molybdenum (Mo) and chromium (Cr), etc.

- 7. A method of claim 1, wherein said the step f) forming recrystallization active layer by sel cting from the group consisting of excimer laser annealing (ELA), solid phase crystallization (SPC) or metal-induced lateral crystallization (MILC), and then forming said polysilicon spacer on either side of said active layer of the thin film transistor (TFT) or silicon-on-insulator metal oxide semiconductor field effect transistor (SOI-MOSFET).

\* \* \* \* \*