US 20030189226A1

## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2003/0189226 A1 Tsui et al.

Oct. 9, 2003 (43) Pub. Date:

#### (54) STRUCTURE OF METAL OXIDE SEMICONDUCTOR FIELD EFFECT **TRANSISTOR**

(75) Inventors: Bing-Yue Tsui, (US); Chih-Feng Huang, (US)

> Correspondence Address: Troxell Law Office PLLC 5205 Leesburg Pike **Suite 1404** Falls Church, VA 22041 (US)

Assignee: National Chiao Tung University, Hsinchu (TW)

10/114,933 (21)Appl. No.:

(22)Filed: Apr. 4, 2002

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> | <br>H01L 21/336 |  |

|------|-----------------------|-----------------|--|

| (52) | U.S. Cl.              | <br>257/347     |  |

#### **ABSTRACT** (57)

The present invention provides a structure of Metal Oxide Semiconductor Field Effect Transistor (MOSFET), which comprises a SOI (Silicon-On-Insulator) device, a MOS (Metal Oxide Semiconductor) formed on said SOI device, and a metal-silicide layer. Said SOI device includes a substrate, an insulation layer formed on said substrate, and a silicon layer formed on said insulation layer, and the MOS is formed on said SOI device. The metal-silicide layer is formed in accordance with a metal aligned process by a metal layer being deposited on said SOI device and on said MOS for reacting with said silicon layer, and an implantto-silicide process is employed to form a high-density source region and a high-density drain region for modifying Schottky Barrier and diminishing Carrier Injection Resistance.

Fig 2

Fig 3

Fig 4

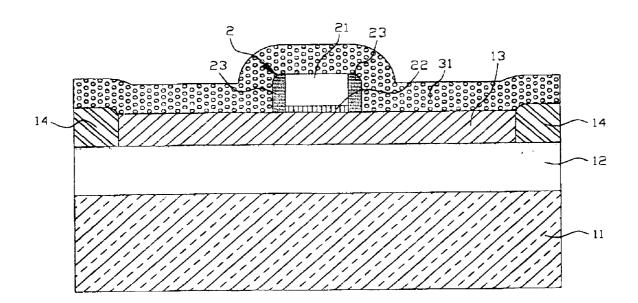

Fig 5

Fig 6

Fig 7

## STRUCTURE OF METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

#### REFERENCE CITED

[0001] C. Wang, et. al., "Sub-50-nm PtSi Schottky source/drain p-MOSFETs", in Proc. of Device Research Conf., p.72, 1998.

[0002] C. Wang, et. al., "Sub-40 nm PtSi Schottky source/drain metal-oxide-semiconductor field-effect transistors", Appl. Phys. Lett., vol.74, No.8, p.1174, 1999.

[0003] W. Saitoh, et. al., "35 nm metal gate SOI-p-MOS-FETs with PtSi Schottky source/drain", in Proc. of Device Research Conf., p.30, 1999.

[0004] A. Itoh, et. al., Very short channel metal-gate Schottky source/drain SOI-PMOSFETs and their short channel effect", in Proc. of Device Research Conf., p.77, 2000.

[0005] H. C. Lin, et. al., "A novel implantless MOS Thin-Film Transistor with simple processing, excellent performance, and ambipolar operation capability", in Dig. of IEDM, p.857, 2000.

[0006] K. Uchida, et. al., "Enhancement of hot-electron generation rate in Schottky source metal-oxide-semiconductor field-effect transistors", Appl. Phys. Lett., vol.76, No.26, p.3992, 2000.

#### FIELD OF THE INVENTION

[0007] The present invention relates to MOSFET (Metal Oxide Semiconductor Field Effect Transistor) for modifying Schottky Barrier and diminishing Carrier Injection Resistance. More particularly, the present invention employs SOI (Silicon-On-Insulator) device to be a substrate thereof for modifying Schottky Barrier and diminishing Carrier Injection Resistance, and a fabrication process therefor.

#### BACKGROUND OF THE INVENTION

[0008] The MOSFET industry has been working on down-scaling for microelectronic devices, particularly for the MOSFET, to increase its features and the density of component. It is very successful in some examples from the early micron till today's deep-submicron for MOSFET, however, it still has some problems for downscaling to nanomicron. Especially, the short channel effect is a very important problem, which is caused by crosswise dopant diffusion; after ion implanting in source and drain electrodes, annealing process may cause the crosswise dopant diffusion.

[0009] Lately, the structure of Schottky Barrier has been put in use on nanomicron SOI device. Metal silicide may replace the P-N junction without causing dopant diffusion; therefore, it may solve the problem of short channel effect. The structure of Schottky Barrier has been provided in 10 years ago for improving the latch-up problem, but it also caused high carriers injection resistance in source electrode and high current leakage in drain electrode of Schottky Barrier. Though an asymmetric structure has been provided for solving the problem of current leakage, it could not be accepted by CMOS process due to the different mask process for masking the source region, and the resistance problem still not be solved.

[0010] The structure of Schottky Barrier being employed on SOI device may improve the current leakage in drain electrode. Because after forming metal silicide the silicon layer is reacted completely, the area of Schottky Junction is squeezed in the channel for carriers passing through, and the current leakage problem may be improved dramatically. However, the problem of carrier injection resistance is still not solved. Besides, due to the different density channel of N-MOSFET and P-MOSFET respectively, it is necessary to have different metal-silicide for modifying Schottky Barrier, for example, PtSi adapted for P-MOSFET and ErSi<sub>2</sub> for N-MOSFET. Therefore, it may not be available for integrating into the standard MOS process with different materials.

[0011] Furthermore, "Sub-gate" has been provided to form "inversion layer" for generating a channel for carriers passing through; however, this kind of process is not accepted for the standard CMOS process, and also, the problem of employing different material is not solved. In addition, it needs high voltage to control the sub-gate, and it also may cause another problem in voltage control.

#### SUMMARY OF THE INVENTION

[0012] Accordingly, the present invention discloses a structure of MOSFET for modifying the Schottky Barrier and diminishing carrier Injection Resistance and method for fabricating the same, which comprises a SOI (Silicon-On-Insulator) device, a MOS (Metal Oxide Semiconductor) formed on said SOI device, and a metal-silicide layer. Said SOI device includes a substrate, an insulation layer formed on said substrate, and a silicon layer formed on said insulation layer. Said MOS is formed on said SOI device. The metal-silicide layer is formed in accordance with a metal self aligned process by a metal layer being deposited on said SOI device and on said MOS for reacting with said silicon layer, and an implant-to-silicide process is employed to form a high-density source region and a high-density drain region for modifying Schottky Barrier and diminishing Carrier Injection Resistance.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0013] The present invention will be better understood from the following detailed description of preferred embodiments of the invention, taken in conjunction with the accompanying drawings, in which

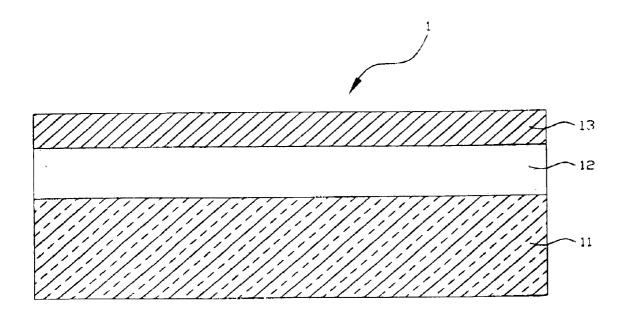

[0014] FIG. 1 is a schematic cross section of a SOI device;

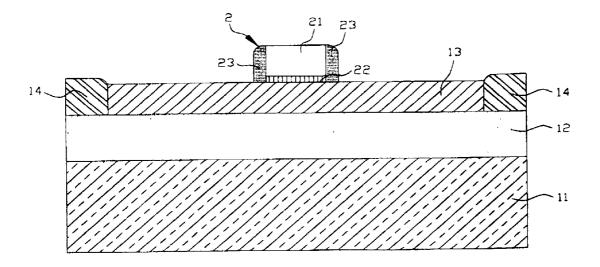

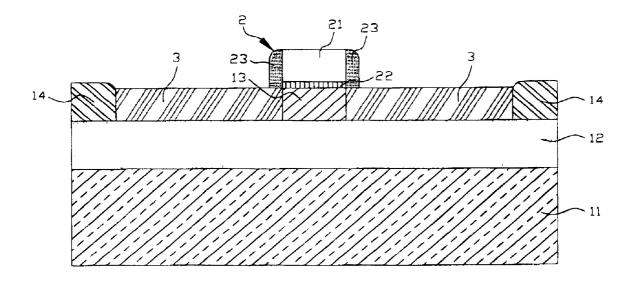

[0015] FIG. 2 is a schematic cross section of a MOS formed on the SOI device; and

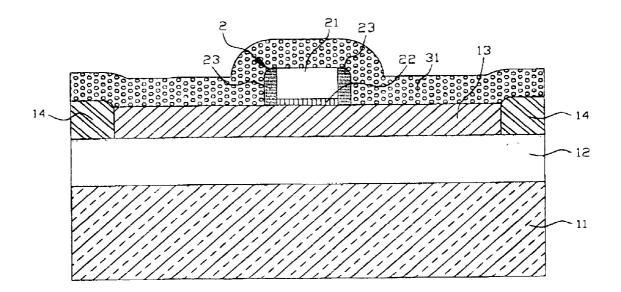

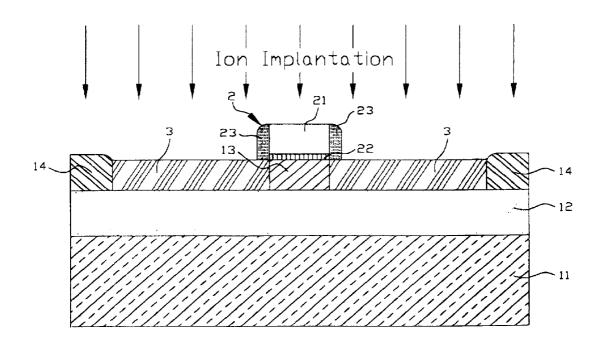

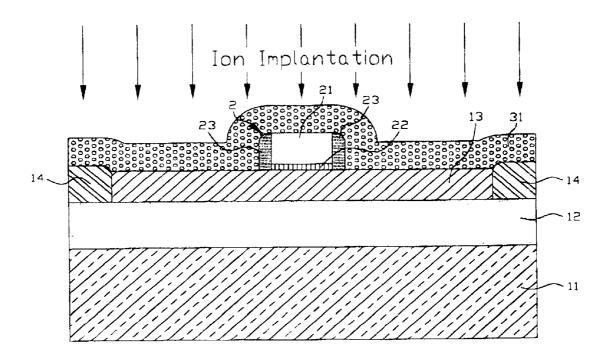

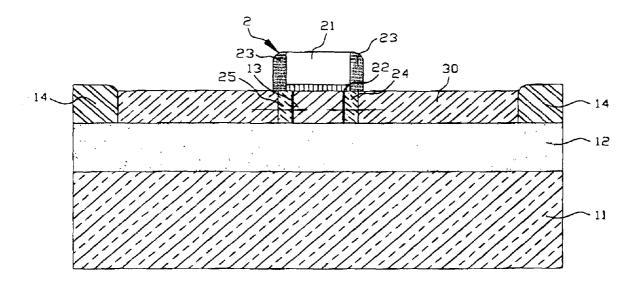

[0016] FIG. 3-FIG. 7 are schematic cross sections of the essential portion illustrating a process for manufacturing the MOSFET according to the present invention.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0017] The following descriptions of the preferred embodiments are provided to understand the features and the structures of the present invention.

[0018] Please referring to the FIG. 1 of a schematic cross section of a SOI device, it shows a SOI device 1 formed by a SOI process to be the substrate of the present invention. The SOI device 1 includes a substrate 11, an insulation layer

12 formed on said substrate 11, and a silicon layer 13 formed on said insulation layer 12; wherein said substrate 11 may be a silicon substrate or a glass substrate, and said insulation layer 12 may be an oxide layer. Next, please seeing the FIG. 2, the isolation area 14 is formed by a general isolation process. Then the process of dielectric oxidization or deposition, gate deposition, photolithography, and etching forms the gate isolation layer 22 and gate electrode 21. After that, depositing a dielectric isolation layer and adapting an anisotropic etching process, the spacers 23 will be formed. Thus, a MOS 2 is formed on said SOI device 1; wherein said MOS is selected from one of a P-MOS or an N-MOS.

Next, after depositing a metal layer 31, referring to the FIG. 3-FIG. 5, the silicon layer 13 may be reacted by the metal self-aligned silicide process to form a metal-silicide layer 3, and thereby, adapting an implant-to-silicide and annealing process, after forming said metal-silicide layer 3 further comprises the step of annealing process, which is processed after the implant-to-silicide for implanting carriers into said silicide layer processing, a high-density source region and a high-density drain region 24 and 25, as shown in the FIG. 7, are formed for modifying Schottky Barrier and diminishing Carriers Injection Resistance; wherein said MOS 2 further comprises a channel between source electrode and drain electrode for carriers passing through. Because the high-density source and drain regions 24 and 25 forms the modified Schottky Junction, which can solve dramatically the problem of leakage current. Furthermore, the source and the drain regions are completely reacted in metal silicide, therefore, the sheet resistance may be limited. In addition, the present invention adapts the ion-implantation to get the feature of metal silicide, and therefore, the process temperature won't be high, only about 600° C. It is another object of the present invention to provide a low temperature process.

[0020] Or, before the self-aligned silicide process in accordance with this invention, the ion implantation will be processed (implant-to-metal) with proper dopant, and then, a high-density source region and a high-density drain region will be formed. That is, referring to the FIG. 1-FIG. 3, a SOI device 1 formed by a SOI process to be the substrate of the present invention. The SOI device 1 includes a substrate 11, an insulation layer 12 formed on said substrate 11, and a silicon layer 13 formed on said insulation layer 12; wherein said substrate 11 may be a silicon substrate or a glass substrate, and said insulation layer 12 may be an oxide layer. Next, please seeing the FIG. 2, the isolation area 14 is formed by a general isolation process. Then the process of dielectric oxidization or deposition, gate deposition, photolithography, and etching forms the gate isolation layer 22 and gate electrode 21. After that, depositing a dielectric isolation layer and adapting an anisotropic etching process, the spacers 23 will be formed. Thus, a MOS 2 is formed on said SOI device 1; wherein said MOS is selected from one of a P-MOS or an N-MOS. After depositing the metal layer 31, then referring to the FIG. 6 and FIG. 7, the ion implantation is processed (implant-to-metal) with proper dopant to form a metal-silicide layer 30 by said metal layer 31 reacting with said silicon layer 3 in accordance with the metal self-aligned process. Therefore, a high-density source region 24 and a high-density drain region 25 are formed for modifying the Schottky Barrier and diminishing Carrier Injection Resistance, as shown in the FIG. 7; wherein said MOS 2 further comprises a channel between source electrode and drain electrode for carriers passing through. Because the high-density source and drain regions 24 and 25 forms the modified Schottky Junction, which can solve the problem of leakage current in drain electrode. Furthermore, the source and the drain are completely reacted in metal silicide, therefore, the sheet resistance may be limited. In addition, the present invention adapts the ion-implantation to get the feature of metal silicide, and therefore, the process temperature won't be high, only about 600° C. It is another object of the present invention to provide a low temperature process.

[0021] The present invention may be embodied in other specific forms without departing from the spirit of the essential attributes thereof; therefore, the illustrated embodiment should be considered in all respects as illustrative and not restrictive, reference being made to the appended claims rather than to the foregoing description to indicate the scope of the invention.

#### What is claimed is:

- 1 A structure of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) for modifying Schottky Barrier and diminishing Carrier Injection Resistance, which comprises:

- a SOI (Silicon-On-Insulator) device having a substrate, an insulation layer formed on said substrate, and a silicon layer formed on said insulation layer;

- a MOS (Metal Oxide Semiconductor) formed on said SOI device; and

- a metal-silicide layer, which is formed in accordance with a metal self aligned process by a metal layer being deposited on said SOI device and on said MOS for reacting with said silicon layer, and an implant-to-silicide process is employed to form a high-density source region and a high-density drain region for modifying Schottky Barrier and diminishing Carrier Injection Resistance.

- 2 The structure of claim 1, wherein said MOS is selected from one of P-MOS or N-MOS.

- 3 The structure of claim 1, wherein said MOS further comprises a channel between said source electrode and said drain electrode for carriers passing through.

- 4 The structure of claim 1, wherein said substrate is selected from one of a silicon substrate or a glass substrate.

- **5** The structure of claim 1, wherein said insulation layer is an oxide layer.

- **6** A structure of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) for modifying Schottky Barrier and diminishing Carrier Injection Resistance, which comprises:

- a SOI (Silicon-On-Insulator) device having a substrate, an insulation layer formed on said substrate, and a silicon layer formed on said insulation layer;

- a MOS (Metal Oxide Semiconductor) formed on said SOI device; and

- a metal-silicide layer, which employs an implant-to-metal process for forming thereof in accordance with a metal self-aligned process by a metal layer being deposited on said SOI device and on said MOS for reacting with said silicon layer, and a high-density source region and a high-density drain region are formed for modifying Schottky Barrier and diminishing Carrier Injection Resistance.

- 7 The structure of claim 6, wherein said MOS is selected from one of P-MOS or N-MOS.

- 8 The structure of claim 6, wherein said MOS further comprises a channel between said source electrode and said drain electrode for carriers passing through.

- **9** The structure of claim 6, wherein said substrate is selected from one of a silicon substrate or a glass substrate.

- 10 The structure of claim 6, wherein said insulation layer is an oxide layer.

- 11 A method for fabricating MOSFET for modifying Schottky Barrier and diminishing Carrier Injection Resistance, which comprises the steps of:

- a.) providing a SOI (Silicon-On-Insulator) device, which

has a substrate, an insulation layer formed on said

substrate, and a silicon layer formed on said insulation

layer;

- b.) forming a MOS (Metal Oxide Semiconductor) on said SOI device in accordance with a standard process of semiconductors;

- c.) depositing a metal layer on said SOI device and on said MOS; and

- d.) reacting with said silicon layer to form a metal-silicide layer by a metal self-aligned process, and to form a high-density source region and a high-density drain

- region by a implant-to-silicide process for modifying Schottky Barrier and diminishing Carrier Injection Resistance.

- 12 The method of claim 11, wherein the step of reacting with said silicon layer to form a metal-silicide layer by a metal self-aligned process may be changed with the step of implant-to-metal process, which forms a high-density source region and a high-density drain region first, and then reacts with said silicon layer to form said metal-silicide layer for modifying the Schottky Barrier for diminishing Carrier Injection Resistance.

- 13 The method of claim 11, after forming said metalsilicide layer further comprises the step of annealing process, wherein the implant-to-silicide for implanting carriers into said silicide layer processing, then processing the step of annealing.

- 14 The method of claim 11, wherein said MOS is selected from one of P-MOS or N-MOS.

- 15 The method of claim 11, wherein said MOS further comprises a channel between said source electrode and said drain electrode for carriers passing through.

- 16 The method of claim 11, wherein said substrate is selected from one of a silicon substrate or a glass substrate.

- 17 The method of claim 11, wherein said insulation layer is an oxide layer.

\* \* \* \* \*