## 公告本

發明專利說明書

(本說明書格式、順序及粗體字，請勿任意更動，※記號部分請勿填寫)

※申請案號： 97138825

※申請日期：97.10.09   ※IPC分類：

H03L 7/08(2006.01)

H03L 7/085(2006.01)

H03L 7/07(2006.01)

### 一、發明名稱：

用於全數位鎖相迴路設計之數位濾波器 / Digital Loop Filter for All-Digital Phase-Locked Loop Design

### 二、申請人：(共 1 人)

姓名或名稱：國立交通大學 / National Chiao Tung University

代表人：吳重雨 / WU, CHONG-YU

住居所或營業所地址：新竹市大學路 1001 號 / No. 1001 University Road, Hsinchu, Taiwan 300, R.O.C

國 稷：中華民國/Taiwan , Republic of China, R.O.C

### 三、發明人：(共 2 人)

姓 名：(中文/英文)

- 1, 李鎮宜/ Chen-Yi Lee

- 2, 鍾菁哲/ Ching-Che Chung

國 稷：

1、2, 中華民國 / Taiwan , Republic of China, R.O.C ;

#### 四、聲明事項：

主張專利法第二十二條第二項第一款或第二款規定之事實，其事實發生日期為： 年 月 日。

申請前已向下列國家（地區）申請專利：

【格式請依：受理國家（地區）、申請日、申請案號 順序註記】

有主張專利法第二十七條第一項國際優先權：

無主張專利法第二十七條第一項國際優先權：

主張專利法第二十九條第一項國內優先權：

【格式請依：申請日、申請案號 順序註記】

主張專利法第三十條生物材料：

須寄存生物材料者：

國內生物材料 【格式請依：寄存機構、日期、號碼 順序註記】

國外生物材料 【格式請依：寄存國家、機構、日期、號碼 順序註記】

不須寄存生物材料者：

所屬技術領域中具有通常知識者易於獲得時，不須寄存。

## 五、中文發明摘要：

本發明係揭示一種數位濾波器，其係裝設在一全數位鎖相迴路中，該數位濾波器係接收該全數位鎖相迴路中之一鎖相迴路控制器，所傳送之一震盪器控制碼，並計算出一平均值，使該鎖相迴路控制器可藉由該平均值而產生一另一震盪器控制碼，藉以控制並調整數位控制震盪器之一輸出端訊號保持在該平均值附近，進而持續的補償與該輸入端訊號間的相位差/頻率差，可進一步減少該輸入端訊號之抖動對該全數位鎖相迴路之影響，及有效的降低該輸出端訊號之抖動現象，且可保持對該輸入端訊號頻率及相位的追蹤及鎖定。

## 六、英文發明摘要：

The present invention discloses a digital loop filter installed in an all-digital phase-locked loop (PLL) for receiving a digitally controlled oscillator (DCO) control code transmitted from a PLL controller in the all-digital PLL, and calculating an average value, such that the PLL controller can produce another DCO control code by the average value for controlling and adjusting an output signal of a digitally controlled oscillator (DCO) in the neighborhood of the average value to maintain compensating a phase/frequency difference with an

input signal, so as to minimize the jitter effect of the input signal on the all-digital PLL, reduce the jitter effect of the output signal, and keep tracking and locking the frequency and the phase of the input signal.

七、指定代表圖：

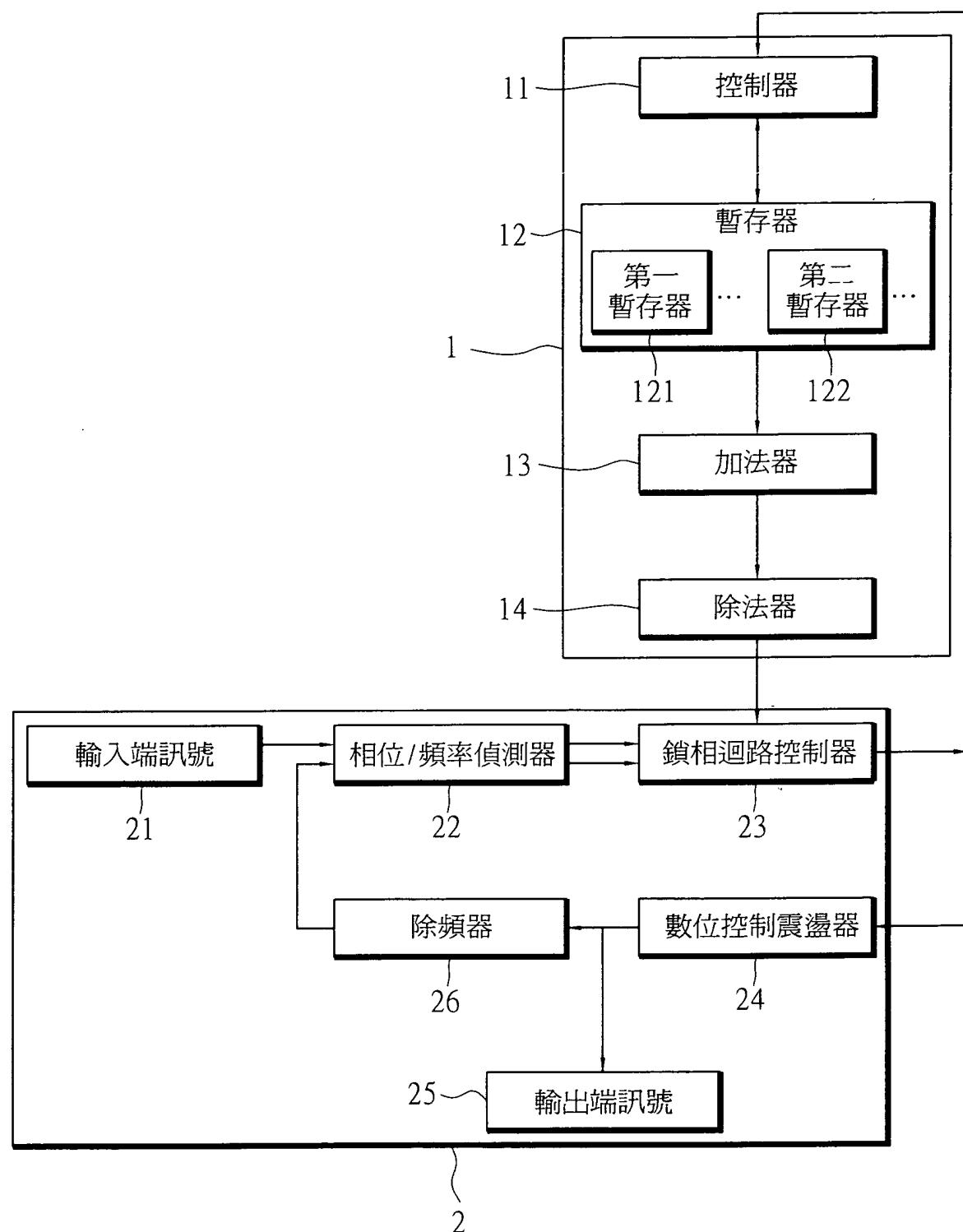

(一)本案指定代表圖為：第（一）圖。

(二)本代表圖之元件符號簡單說明：

1 、 數位濾波器

11 、 控制器

12 、 暫存器

121 、 第一暫存器

122 、 第二暫存器

13 、 加法器

14 、 除法器

2 、 全數位鎖相迴路

21 、 輸入端訊號

22 、 相位/頻率偵測器

23 、 鎖相迴路控制器

24 、 數位控制震盪器

25 、 輸出端訊號

26 、 除頻器

八、本案若有化學式時，請揭示最能顯示發明特徵的化學式：

## 九、發明說明：

### 【發明所屬之技術領域】

本發明為提供一種數位濾波器，其係裝設在一全數位鎖相迴路中，可減少一輸入端訊號之抖動對該全數位鎖相迴路之影響，並有效的降低一輸出端訊號之抖動現象，使該全數位鎖相迴路可保持對該輸入端訊號頻率及相位的追蹤及鎖定。

### 【先前技術】

現今因通訊產品的使用量與重要性日趨成長，且積體電路發展迅速，使得通訊積體電路的需求也相對增加，其中鎖相迴路(Phase-Locked Loop，簡稱：PLL)是最常被使用的電路之一，通常鎖相迴路可分別應用於通訊上做調變及解調、無線電系統上做頻率合成器及在數位電路上做時序訊虔回復系統等等。

而鎖相迴路的原理主要是將輸入端訊號及輸出端訊號的相位及頻率做追蹤及鎖定，使兩個訊號能夠時時刻刻保持一致，當兩個訊號的相位誤差等於零或非常小時，我們就可以稱為鎖定(locked)，因此快速鎖定在鎖相迴路的設計中變得越來越重要且成為必要的條件。

習用之數位濾波器設計方式，普遍利用積分器累積平均，進而消除輸入端訊號之抖動對鎖相迴路之影響，已有相當多專利發表，包括：Qualcomm 公司(US pat. 7,042,972)、Texas Instruments 公司(US pat. 7,145,399)及一參考文獻，其係刊登於 2005 年三月所出版之 IEEE Transactions on circuits and

systems II 之中，該參考文獻名稱為：Phase Domain All-Digital Phase-Locked Loop 之論文等等。

然而，上述之習知專利及論文，皆是利用積分之方式，來消除輸入端訊號之抖動對鎖相迴路之影響，但當輸入端訊號之週期抖動非常嚴重時，積分器亦會將這些嚴重抖動資訊一一記錄下來，使積分器的輸出無法維持穩定，導致無法降低鎖相迴路之輸出端訊號，而會有週期抖動之缺點，造成設計數位濾波器的困擾。

除此之外，相關專利，如：MOTOROLA 公司(US pat. 5,473,285)所提出之更新 ANCHOR REGISTER 方法，可產生鎖相迴路控制器所需之基準頻率，再藉由每四次連續的控制信號(UP/DOWN)來更新基準頻率，可以部分降低輸入端訊號之抖動對鎖相迴路之影響，惟當輸入端訊號之週期性抖動非常嚴重時，此專利所提出的更新 ANCHOR REGISTER 方法，則無法有效壓抑輸入端訊號之抖動對鎖相迴路之影響，導致無法有效降低鎖相迴路之輸出端訊號，而會有週期抖動之缺點。

### 【發明內容】

有鑑於上述之習知專利及論文，其均無法有效降低鎖相迴路之輸出端訊號會有週期抖動之缺點；因此，發明人開發設計出一種數位濾波器，其係用於低抖動全數位鎖相迴路設計之中。

本發明之一目的，在提供一種用於全數位鎖相迴路設計之數位濾波器，其係裝設在一全數位鎖相迴路中，以減少一輸入端訊號之抖動對該全數位鎖相迴路之影

響，並有效的降低一輸出端訊號之抖動現象，使該全數位鎖相迴路可保持對該輸入端訊號頻率及相位的追蹤及鎖定。

本發明之另一目的，在提供一種用於全數位鎖相迴路設計之數位濾波器，其係採用一全數位鎖相迴路相關設計技術，以改善一傳統類比鎖相迴路的漏電問題和難以操作在低壓工作的重要解決方案，可大幅改良成本架構與商品競爭條件。

### 【實施方式】

本發明係一種「用於全數位鎖相迴路設計之數位濾波器」，請參閱第一圖所示，係為本發明實施例之數位濾波器 1(Digital Loop Filter)裝設在一全數位鎖相迴路 2 中之架構圖，其中該數位濾波器 1 分別包含有一控制器 11，係用以接收該全數位鎖相迴路 2 中之一鎖相迴路控制器 23(Phase-Locked Loop Controller，簡稱 PLL Controller)，所傳來之一震盪器控制碼及另一震盪器控制碼，並將該震盪器控制碼及該另一震盪器控制碼更新至複數個暫存器 12 中。

該複數個暫存器 12 係用以儲存經由該控制器 11 所更新並傳來之該震盪器控制碼及該另一震盪器控制碼，其中該複數個暫存器 12 係包含有複數個第一暫存器 121(如： $M = T_0 \sim T_{(M-1)}$ )及複數個第二暫存器 122(如： $K = T_M \sim T_{(M+K-1)}$ )，該複數個第一暫存器 121 係用以儲存該控制器 11 傳來之該震盪器控制碼，而該複數個第二暫存器 122 係用以儲存該控制器 11 所傳來經由該鎖相迴

路控制器 23 所產生之另一震盪器控制碼。

一加法器 13，係用以接收並計算出該複數個第一暫存器 121 中之該震盪器控制碼之總和。

一除法器 14，係用以接收並計算出經由該加法器 13 所計算出該震盪器控制碼之總和之一平均值，並將該平均值傳送至該鎖相迴路控制器 23。

前述該全數位鎖相迴路 2 分別包含有一相位/頻率偵測器 22(Phase/Frequency Detector, 簡稱 PFD)，係用以分別量測一輸入端訊號 21 及經由一除頻器 26(Frequency Divider)除頻處理後所產生之訊號，當該二訊號間有相位差/頻率差時，該相位/頻率偵測器 22 即會送出一另一訊號(UP/DOWN)至該鎖相迴路控制器 23。

又，該鎖相迴路控制器 23，係用以分別接收該相位/頻率偵測器 22 及該數位濾波器 1，所傳來之該另一訊號及該平均值，以分別產生該震盪器控制碼及該另一震盪器控制碼。

一數位控制震盪器 24(Digital Controlled oscillator，簡稱 DCO)，係用以接收該鎖相迴路控制器 23 所傳來之該另一震盪器控制碼，以補償與該輸入端訊號 21 間之相位差及頻率差；而該除頻器 26 則係接收該數位控制震盪器 24 所傳來之一訊號，並做除頻處理，以降低該訊號之頻率後，再傳送至該相位/頻率偵測器 22。

在本發明實施例中，該等第一暫存器 121 為計算出

100年12月6日修正替換

該平均值之震盪器控制碼數量，且該等第一暫存器 121 數量之多寡將會影響到輸出之該平均值之穩定性，當增加該等第一暫存器 121 之數量時，亦可同時增加該數位濾波器 1 輸出之穩定性。

在本發明實施例中，該等第二暫存器 122 為每次輸入之該另一震盪器控制碼之數量，且該等第二暫存器 122 之數量至少為二，又，當該等第二暫存器 122 之數量等於二時，該複數個暫存器 12 內容更新動作將可簡化為去除最大值與最小值的動作，並將剩餘之該震盪器控制碼儲存至該第一暫存器 121 中，而可增加該數位濾波器 1 的處理速度，進而降低其硬體成本。

在本發明實施例中，前述 M 及 K 為常數，當所計算出的該平均值之震盪器控制碼數量為四個時，則 M 等於 4 (即是該等第一暫存器 121 為四個)，又，K 等於 2，即是該等第二暫存器為二個。

在本發明實施例中，當該等第二暫存器 122 之數量大於二時，該複數個暫存器 12 內容更新動作將會變為將該震盪器控制碼及該另一震盪器控制碼做一排序(該排序係選自由大數值排序至小數值及小數值排序至大數值其中之一)，並保留位於中間數值之該震盪器控制碼(該震盪器控制碼之數量即為該等第一暫存器 121 之數量)，再將該震盪器控制碼儲存至該第一暫存器 121 中。

藉此，本發明實施例之該數位濾波器 1 使用在低抖動之該全數位鎖相迴路 2 時，該輸入端訊號 21 及該數

102年12月6日修正替換

位控制震盪器 24 所產生，並經由該除頻器 26 除頻處理後產生之訊號間有相位差/頻率差時，該相位/頻率偵測器 22 即會測知該數位控制震盪器 24 之輸出為過快/過慢，而送出該另一訊號(UP/DOWN)至該鎖相迴路控制器 23，使該鎖相迴路控制器 23 可根據該相位/頻率偵測器 22 的偵測結果產生該震盪器控制碼，並將該震盪器控制碼傳送且經由該數位濾波器 1 上所設相關電子元件之處理，進而產生該平均值，再將該平均值傳送至該鎖相迴路控制器 23，使該鎖相迴路控制器 23 會藉由該平均值而產生該另一震盪器控制碼，藉以控制並調整該數位控制震盪器 24 之一輸出端訊號 25 保持在該平均值附近，進而持續的補償與該輸入端訊號 21 間的相位差/頻率差，可進一步減少該輸入端訊號 21 之抖動對該全數位鎖相迴路 2 之影響，及有效的降低該輸出端訊號 25 之抖動現象，使該全數位鎖相迴路 2 可保持對該輸入端訊號 21 頻率及相位的追蹤及鎖定。

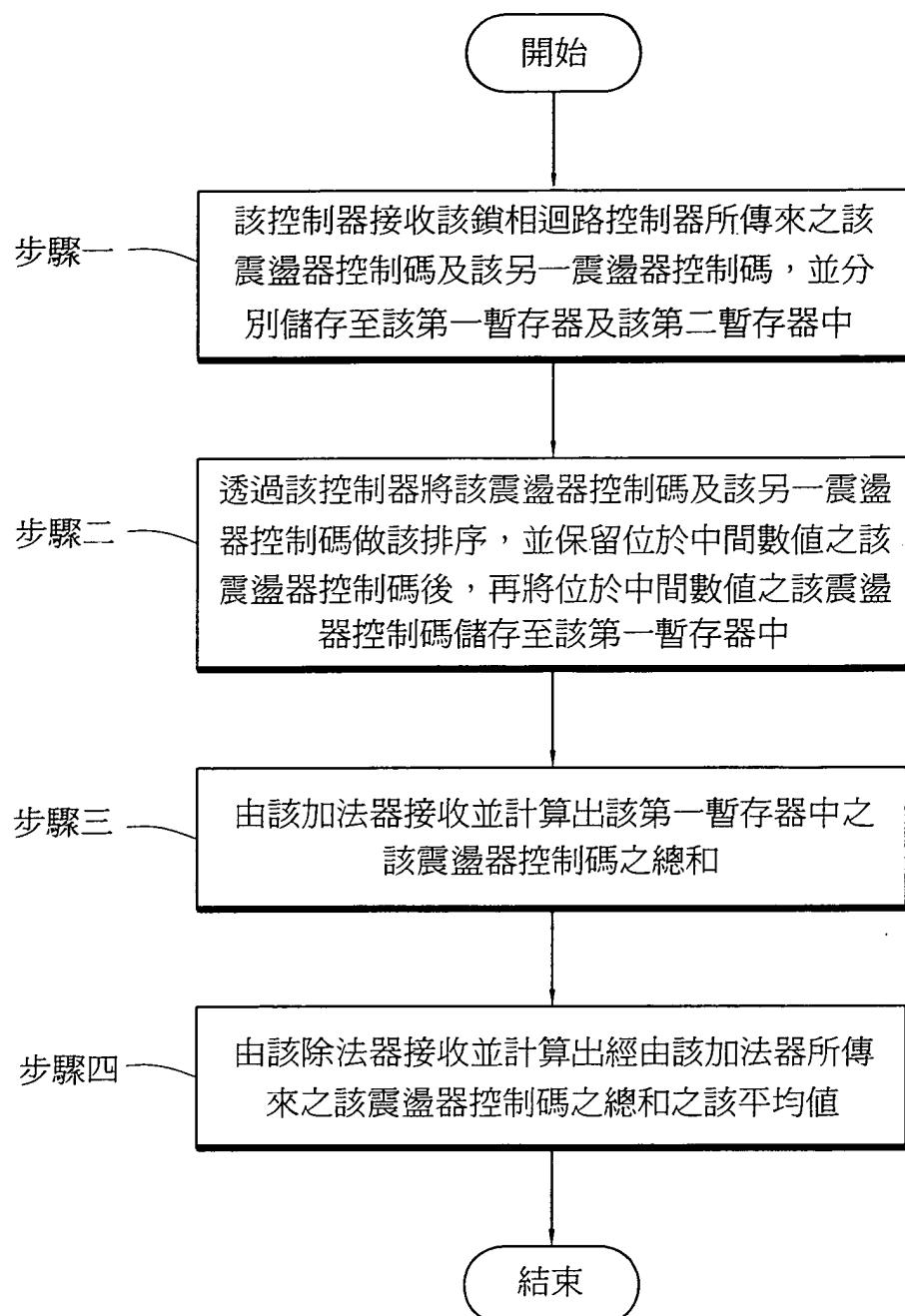

請參閱第二圖所示，其係為本發明實施例之該數位濾波器 1 使用在低抖動之該全數位鎖相迴路 2 時，接收該震盪器控制碼及該另一震盪器控制碼，以產生該平均值之流程步驟：

步驟一：首先，該控制器 11 接收該鎖相迴路控制器 23 所傳來之該震盪器控制碼及該另一震盪器控制碼，並分別將該震盪器控制碼及另一震盪器控制碼儲存至該第一暫存器 121 及該第二暫存器 122 中；

100年12月6日修正替換頁

步驟二：透過該控制器 11 將該震盪器控制碼及該另一震盪器控制碼做該排序，並保留位於中間數值之該震盪器控制碼後，再將位於中間數值之該震盪器控制碼儲存至該第一暫存器 121 中；

步驟三：再由該加法器 13 接收並計算出該第一暫存器 121 中之該震盪器控制碼之總和；

步驟四：再由該除法器 14 接收並計算出經由該加法器 13 所傳來之該震盪器控制碼之總和之該平均值，如此，即結束一次利用該數位濾波器 1 接收該震盪器控制碼及該另一震盪器控制碼，並更新至該複數個暫存器 12，進而產生該平均值之處理步驟。

又，本發明實施例之該數位濾波器 1 使用在該全數位鎖相迴路 2 時，接收該震盪器控制碼及該另一震盪器控制碼，以產生該平均值之方法，以下提出一實驗數據：

假設該數位濾波器 1 中之該第一暫存器 121（如： $M=T_0 \sim T_{(M-1)}$ ）之數量為四個( $T_0 \sim T_3$ )，即是  $M=4$ ，且該第一暫存器 121 內之該震盪器控制碼之初值假設為(9, 10, 10, 10)，而該數位濾波器 1 中之該第二暫存器 122（如： $K=T_M \sim T_{(M+K-1)}$ ）之數量為二個( $T_4 \sim T_5$ )，即是  $K=2$ ，且儲存至該第二暫存器 122 內之該另一震盪器控制碼 假 設 依 序 為  $(10, 11) \Rightarrow (12, 13) \Rightarrow (14, 13) \Rightarrow (12, 11) \Rightarrow (12, 13) \Rightarrow (12, 11) \Rightarrow (12, 13) \Rightarrow (1, 2, 11) \Rightarrow (12, 13) \Rightarrow (12, 11) \dots\dots$ 。

將上述之實驗數據代入第二圖所示之流程步驟即

10年2月6日修正替換頁

可算出該平均值，意即當該震盪器控制碼初值假設為(9, 10, 10, 10)，而該另一震盪器控制碼假設為(10, 11)時，該控制器 11 將去除該二震盪器控制碼中之最大值（即：11）及最小值（即：9），再將剩餘之震盪器控制碼儲存至該第一暫存器 121( $T_0 \sim T_3$ )中，故該第一暫存器 121( $T_0 \sim T_3$ )中之該震盪器控制碼會由原先(9, 10, 10, 10)變化成(10, 10, 10, 10)，而該平均值亦會由(9.75)變化成(10)。

藉由上述該另一震盪器控制碼之變化，該第一暫存器 121( $T_0 \sim T_3$ )中之該震盪器控制碼即依序變化為

$=>(12, 10, 10, 10)=>(12, 13, 10, 10)=>(12, 12, 11, 10)=>$

$(12, 12, 11, 12)=>(12, 12, 11, 12)=>(12, 12, 12, 12)=>(1$

$2, 12, 12, 12)=>(12, 12, 12, 12)=>(12, 12, 12, 12) \dots \dots$ ；

使得該平均值亦會從(10)，依序變化為 $=>(10.5)$

$=>(11.25)=>(11.25)=>(11.75)=>(11.75)=>(12)=>(12)$

$=>(12)=>(12) \dots \dots$ 。

綜上所述可知，本發明有別習用技術關鍵在於：當該全數位鎖相迴路 2 鎖定後，該鎖相迴路控制器 23 會不斷調整該另一震盪器控制碼，以追蹤該輸入端訊號 21 的頻率與相位變化，而本發明之數位濾波器 1 可以不斷的排除掉，所記錄下該震盪器控制碼及該另一震盪器控制碼的最大值與最小值，因此在很快的時間內，該數位濾波器 1 便可輸出穩定之該平均值，使得該全數位鎖相迴路 2 之輸出得以維持穩定，可有效地消除該輸入端訊號 21 抖動對該全數位鎖相迴路 2 的影響，且保持

10年12月6日修正替換頁

對該輸入端訊號 21 頻率與相位的追蹤能力。

按，上述詳細說明為針對本發明之一種較佳之可行實施例說明而已，惟該實施例並非用以限定本發明之申請專利範圍，舉凡其他未脫離本發明所揭示之技藝精神下所完成之均等變化與修飾變更，均應包含於本發明所涵蓋之專利範圍中。

#### 【圖式簡單說明】

第一圖係為本發明實施例之數位濾波器裝設在該全數位鎖相迴路中之架構圖。

第二圖係為本發明實施例產生該平均值之流程示意圖。

#### 【主要元件符號說明】

- |     |           |     |            |

|-----|-----------|-----|------------|

| 1   | 、 數位濾波器   |     |            |

| 11  | 、 控制器     |     |            |

| 12  | 、 暫存器     |     |            |

| 121 | 、 第一暫存器   | 122 | 、 第二暫存器    |

| 13  | 、 加法器     | 14  | 、 除法器      |

| 2   | 、 全數位鎖相迴路 |     |            |

| 21  | 、 輸入端訊號   | 22  | 、 相位/頻率偵測器 |

| 23  | 、 鎖相迴路控制器 | 24  | 、 數位控制震盪器  |

| 25  | 、 輸出端訊號   | 26  | 、 除頻器      |

## 十、申請專利範圍：

- 1、一種數位濾波器，其係裝設在一全數位鎖相迴路中，藉以控制該全數位鎖相迴路中一數位控制震盪器之一輸出端訊號，而該數位濾波器係包括：

- 一控制器，係用以接收該全數位鎖相迴路中之一鎖相迴路控制器，所傳來之一震盪器控制碼及一另一震盪器控制碼；

- 複數個暫存器，係用以儲存經由該控制器所更新並傳來之該震盪器控制碼及該另一震盪器控制碼；

- 一加法器，用以接收並計算出該等暫存器中之該震盪器控制碼之總和；

- 一除法器，係用以接收並計算出經由該加法器所計算出該震盪器控制碼之總和之一平均值，再將該平均值傳送至該鎖相迴路控制器，使得該鎖相迴路控制器可產生前述該另一震盪器控制碼，藉以控制並調整該數位控制震盪器之輸出端訊號保持在該平均值附近，進而持續的補償與該全數位鎖相迴路中之一輸入端訊號間之相位差及頻率差。

- 2、如申請專利範圍第 1 項所述之數位濾波器，其中該複數個暫存器包含有複數個第一暫存器，用以儲存該控制器傳來之該震盪器控制碼。

- 3、如申請專利範圍第 2 項所述之數位濾波器，其中該加法器係透過該複數個第一暫存器來接收並計算出該震盪器控制碼之總和。

- 4、如申請專利範圍第 2 項所述之數位濾波器，其中該

等第一暫存器為計算出該平均值之震盪器控制碼數量，且該等第一暫存器數量之多寡，會影響到輸出之該平均值之穩定性。

- 5、如申請專利範圍第 1 項所述之數位濾波器，其中該複數個暫存器包含有複數個第二暫存器，用以儲存該控制器所傳來經由該鎖相迴路控制器所產生之另一震盪器控制碼。

- 6、如申請專利範圍第 5 項所述之數位濾波器，其中該等第二暫存器為每次輸入之另一震盪器控制碼之數量，且該等第二暫存器之數量至少為二。

- 7、如申請專利範圍第 6 項所述之數位濾波器，其中當該等第二暫存器之數量等於二時，該複數個暫存器內容更新動作可簡化為去除最大值與最小值的動作，再將剩餘之該震盪器控制碼儲存至該第一暫存器中。

- 8、如申請專利範圍第 6 項所述之數位濾波器，其中當該等第二暫存器之數量大於二時，該複數個暫存器內容更新動作將會變為將該震盪器控制碼及該另一震盪器控制碼做一排序，並保留位於中間數值之該震盪器控制碼，再將位於中間數值之該震盪器控制碼儲存至該第一暫存器中。

- 9、如申請專利範圍第 8 項所述之數位濾波器，其中該排序係選自由大數值排序至小數值及小數值排序至大數值其中之一。

- 10、如申請專利範圍第 1 項所述之數位濾波器，其中該

全數位鎖相迴路係包含有：

一相位/頻率偵測器，係用以分別量測該輸入端訊號及經由一除頻器除頻處理後所產生之訊號，當該二訊號間有相位差/頻率差時，該相位/頻率偵測器即會送出一另一訊號至該鎖相迴路控制器；

該鎖相迴路控制器，係用以分別接收該相位/頻率偵測器及該數位濾波器，所傳來之該另一訊號及該平均值，以分別產生該震盪器控制碼及該另一震盪器控制碼；

該數位控制震盪器，係用以接收該鎖相迴路控制器所傳來之該另一震盪器控制碼，以補償與該輸入端訊號間之相位差及頻率差；

該除頻器，係用以接收該數位控制震盪器所傳來之一訊號，並做除頻處理，以降低該訊號之頻率後，再傳送至該相位/頻率偵測器。

## 十一、圖式：

第一圖

第二圖