# On the RF Extrinsic Resistance Extraction for Partially-Depleted SOI MOSFETs

Sheng-Chun Wang, Pin Su, *Member, IEEE*, Kun-Ming Chen, Chien-Ting Lin, Victor Liang, and Guo-Wei Huang, *Member, IEEE*

Abstract—We have investigated the radio frequency (RF) extrinsic resistance extraction for partially-depleted (PD) silicon-on-insulator (SOI) metal-oxide-semiconductor field effect transistors (MOSFETs). Although the thick buried oxide in SOI devices can block the substrate coupling, the SOI neutral-body coupling effect is significant for RF applications. An equivalent circuit considering this effect has been proposed. Based on this equivalent circuit, a new model capturing the frequency dependence of extrinsic resistances has been derived. After considering the impact of quasi-neutral body, we have developed a physically accurate RF extrinsic resistance extraction methodology for PD SOI MOSFETs.

*Index Terms*—Metal-oxide-semiconductor field effect transistors (MOSFETs), radio frequency (RF), resistance extraction, silicon-on-insulator (SOI) technology.

#### I. INTRODUCTION

Due to its highly integrated nature, CMOS technology has become an excellent choice for radio frequency (RF) applications. Silicon-on-insulator (SOI) CMOS is especially promising for RF system-on-chip integration because of the reduction in crosstalk between RF and digital circuits and easy integration of high quality passive elements [1], [2]. With the penetration of SOI CMOS into RF applications [3], [4], RF SOI modeling becomes a crucial design issue.

For RF CMOS modeling, the model accuracy hinges upon the extraction of extrinsic gate/source/drain resistance  $(R_g/R_s/R_d)$  for small-signal, noise, and large-signal applications. Several studies [5]–[7] have presented resistance extraction methods for SOI metal-oxide-semiconductor field effect transistors (MOSFETs) based on those developed for their bulk counterparts [8], [9]. Among these approaches, the zero method [5], [8] developed under the zero condition (i.e.,  $V_{\rm GS} = V_{\rm DS} = 0$ ) is attractive because it simplifies the corresponding equivalent circuit and avoids the error caused by the

Manuscript received August 21, 2006; revised January 3, 2007. This work was supported in part by the National Science Council of Taiwan, R.O.C., under Contract NSC94-2215-E-009-049.

S.-C. Wang is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. and also with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C. (e-mail: scwang@mail.ndl.org.tw).

P. Su is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

K.-M. Chen and G.-W. Huang are with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C.

C.-T. Lin and V. Liang are with the United Microelectronics Corporation, Hsinchu 300, Taiwan, R.O.C.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2007.895713

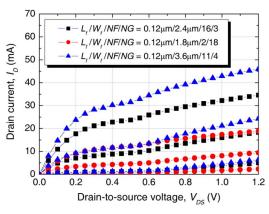

Fig. 1.  $I_D$  versus  $V_{\rm DS}$  characteristics for PD SOI MOSFETs used in this study.  $V_{\rm GS}$  is from 0.4 to 0.8 V with step 0.2 V.

non-quasi-static (NQS) effect [7]. Based on the equivalent circuit built for bulk MOSFETs under the zero condition without considering the substrate loss [8], the following frequency-independent resistance expressions have been derived to directly determine  $R_s, R_d$ , and  $R_g$ , respectively

$$Re(Z_{21}) = Re(Z_{12}) = R_s$$

(1)

$$Re(Z_{22} - Z_{12}) = R_d \tag{2}$$

$$Re(Z_{11} - Z_{12}) = R_g. (3)$$

For partially-depleted (PD) SOI MOSFETs, however, (1)–(3) may not be valid due to the existence of the floating body region. In this work, we investigate the RF extrinsic resistance extraction for PD SOI MOSFETs. We will show that, for RF SOI MOSFETs, the coupling path between the source and drain terminals through the quasi-neutral body region makes the resistance expressions behave frequency-dependently. After taking this effect into account, we develop a physical RF extrinsic resistance extraction methodology for PD SOI MOSFETs.

## II. DEVICES AND MEASUREMENTS

The PD SOI MOSFETs used in this study were fabricated using UMC 0.13- $\mu$ m SOI technology. The thicknesses for gate oxide, SOI layer, and buried oxide are 1.4, 40, and 200 nm, respectively. The presence of kinks in Fig. 1 shows that the devices under study are partially depleted. These RF devices were laid out in the multi-finger and multi-group structure with various finger number NF, group number NG, and finger length  $W_f$  for a given gate length  $L_f$  (0.12  $\mu$ m). On-wafer two-port S parameters up to 20 GHz were measured, de-embedded with an open dummy, and then transformed to Z parameters to obtain the resistance versus frequency characteristics.

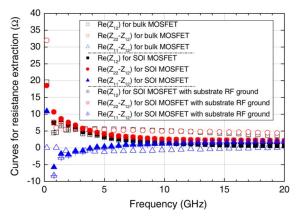

Fig. 2. Resistance curves for the bulk and PD SOI MOSFETs with  $L_f/W_f/{\rm NF/NG}=0.12~\mu\,{\rm m}/2.4~\mu\,{\rm m}/16/3.$

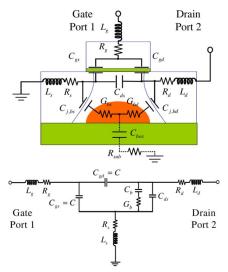

Fig. 3. (a) Cross-sectional view of the zero PD SOI MOSFET. (b) Equivalent circuit for zero PD SOI MOSFETs.

To further minimize possible substrate resistive loss through the buried oxide layer [10], a bias-network connected to the chuck of the probe station was used to provide the substrate dc ground (i.e., back-gate voltage  $V_{\rm ES}=0$ ) with RF floating. In fact, as shown in Fig. 2, whether the substrate RF ground is provided or not, the resistance curves are almost unchanged. This indicates that the substrate effect is negligible in this experiment.

# III. RESULTS AND DISCUSSIONS

Fig. 2 also compares the resistance versus frequency characteristics under the zero condition for PD SOI MOSFET and its bulk counterpart with identical layout structure and geometry. All of these curves more or less are frequency-dependent. The poor shapes for the bulk MOSFET can be attributed to the complicated and significant substrate resistive loss [11], [12]. For the SOI MOSFET, however, the substrate loss may not be responsible for this frequency-dependent behavior because the thick buried oxide layer in the SOI transistor has provided good isolation from the substrate.

Fig. 3(a) shows a cross-sectional view of the PD SOI MOSFET under the zero condition. The neutral-body coupling path is constituted by source- and drain-side junction capacitances ( $C_{j,\mathrm{bs}}$  and  $C_{j,\mathrm{bd}}$ ), and body conductances ( $G_{\mathrm{bs}}$  and

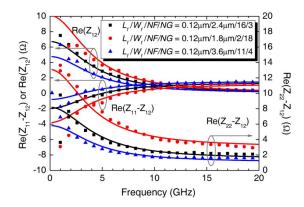

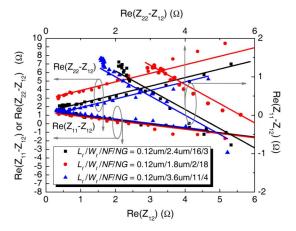

Fig. 4. Modeling results for extrinsic resistance extraction considering the neutral-body effect (points: measured data. lines: model).

Fig. 5. Correlation between  $Re(Z_{22}-Z_{12})$ ,  $Re(Z_{12})$  and  $Re(Z_{11}-Z_{12})$  (Points: measured data. lines: model).

$G_{\rm bd}$ ). Its corresponding equivalent circuit without substrate RF ground is depicted in Fig. 3(b). Here, the neutral-body coupling path is represented by a lumped junction capacitance  $C_b = (1/C_{j,\rm bs} + 1/C_{j,\rm bd})^{-1}$  and a lumped body conductance  $G_b = (1/G_{\rm bs} + 1/G_{\rm bd})^{-1}$ . Based on this equivalent circuit, the following resistance expressions regarding  $R_s$ ,  $R_d$ , and  $R_g$  can be derived:

$$Re(Z_{21}) = Re(Z_{12}) = R_s + A/(\omega^2 + B)$$

(4)

$$Re(Z_{22} - Z_{12}) = R_d + A/(\omega^2 + B)$$

(5)

$$Re(Z_{11} - Z_{12}) = R_q - 0.5 \times A/(\omega^2 + B)$$

(6)

where

$$A = 2C_b^2 G_b / D$$

$$B = G_b^2 \left( 4C_{ds}^2 + C^2 + 4C_b^2 + 4CC_{ds} + 8C_{ds}C_b + 4CC_b \right) / D$$

and

$$D = (C^2 C_b^2 + 4C_{ds}CC_b^2 + 4C_{ds}^2C_b^2).$$

Note that we have assumed  $C_{\rm gs} = C_{\rm gd} = C$  in the derivation. Equations (4)–(6) predict that the existence of neutral body may cause the resistance curves regarding  $R_s$ ,  $R_d$ , and  $R_g$  frequency-dependent and explain the anomalous SOI behavior in Fig. 2. It is worth noting that (4)–(6) will approach (1)–(3), respectively, as the frequency (or angular frequency,

В  $R_s$  $R_d$  $R_g$  $(\times 10^{21} F^{-1}.s^{-1})$  $(\times 10^{20} \text{s}^{-2})$ (µ m)  $(\Omega)$ (Ω)  $(\Omega)$ (Ω) (Ω) (Ω) 115.2 4.9 1.4 1.45 0.1 FET1 7.2 2.15 1.5 1.4 FET2 64.8 6.4 6.4 2.9 1.35 2.8 0.1 3 1.3 3.5 0.9 1.55

TABLE I MODEL PARAMETERS

The values of  $L_f/W_f/NF/NG$  for FET1, FET2 and FET3 are 0.12 $\mu$  m/2.4 $\mu$  m/16/3, 0.12 $\mu$  m/2.18 $\mu$  m/2/18, 0.12 $\mu$  m/3.6 $\mu$  m/11/4, respectively.

$\omega$ ) approaches infinity. In other words, the extrinsic resistances can be determined by the high frequency asymptotes of  $\mathrm{Re}(Z_{12}), \mathrm{Re}(Z_{22}-Z_{12})$ , and  $\mathrm{Re}(Z_{11}-Z_{12})$ . Note that the drain-source coupling capacitance,  $C_{\mathrm{ds}}$ , will short the neutral-body path and hence eliminate this neutral-body effect at very high frequency.

Using this new model, a physical RF extrinsic resistance extraction methodology for PD SOI MOSFETs can be developed. The model-data comparison for the extraction of  $R_s$ ,  $R_d$ , and  $R_g$  with various layout geometries are shown in Fig. 4. It can be seen that the frequency-dependent resistance characteristics are well fitted by our model. Moreover, according to (4)–(6),  $\operatorname{Re}(Z_{22}-Z_{12})$ ,  $\operatorname{Re}(Z_{12})$ , and  $\operatorname{Re}(Z_{11}-Z_{12})$  are mutually correlated [6] by

$$Re(Z_{22} - Z_{12}) = Re(Z_{12}) + R_{ds}$$

(7)

$$Re(Z_{11} - Z_{12}) = -0.5 \times Re(Z_{12}) + R_{gs}$$

(8)

$$\operatorname{Re}(Z_{11} - Z_{12}) = -0.5 \times \operatorname{Re}(Z_{22} - Z_{12}) + R_{\text{gd}}$$

(9)

where  $R_{\rm ds} = R_d - R_s$ ,  $R_{\rm gs} = R_g + 0.5 \times R_s$ ,  $R_{\rm gd} = R_g + 0.5 \times R_d$ . Equations (7)–(9) have been verified in Fig. 5.

The extracted extrinsic resistances and model parameters  $A,B,R_{\rm ds},R_{\rm gs}$ , and  $R_{\rm gd}$  for each SOI device are listed in Table I. One can find that  $R_s$  is nearly equal to zero whereas  $R_d$  is not. This is because the RF devices were laid out in the multi-finger and multi-group structure. The multi-source regions were out-connected at two ends of each finger, while the multi-drain regions were out-connected at only one side. In addition, the interconnection between each group may provide additional resistance for the drain terminal and result in discrepancy between  $R_d$  and  $R_s$ .

Since all the involved device conductance and capacitances in (4)–(6) are proportional to the total gate width  $W_{\rm total} (\approx W_f \times {\rm NF} \times {\rm NG})$ , the parameter A should increase as  $W_{\rm total}$  decreases. As indicated in Fig. 4, the resistance curves for the device with smaller  $W_{\rm total}$  indeed have a larger deviation from its high-frequency asymptote in the lower frequency regime. Therefore, one can minimize the extraction error resulted from the SOI neutral-body effect by using the wide device.

### IV. CONCLUSION

We have investigated the extrinsic resistance extraction for PD SOI MOSFETs. Although the thick buried oxide in SOI devices can block the complicated substrate network, the SOI neutral-body coupling effect may become significant for RF applications. An equivalent circuit considering this effect has been proposed. Based on the equivalent circuit, a new model

capturing the frequency dependence of extrinsic resistances has been derived. After considering the impact of quasi-neutral body, we have developed a physically accurate RF extrinsic resistance extraction methodology for PD SOI MOSFETs.

#### ACKNOWLEDGMENT

The authors would like to thank the staff at UMC for providing the SOI devices used in this study.

#### REFERENCES

- J.-P. Raskin, A. Viviani, D. Flandre, and J.-P. Colinge, "Substrate crosstalk reduction using SOI technology," *IEEE Trans. Electron Devices*, vol. 44, no. 12, pp. 2252–2261, Dec. 1997.

- [2] E. Zencir, N. S. Dogan, and E. Arvas, "Modeling and performance of spiral inductors in SOI CMOS technology," in *Proc. IEEE Can. Conf. Elect. Comput. Eng.*, May 2002, pp. 408–411.

- [3] J. Kim, J.-O. Plouchart, and N. Zamdmer, "Design and manufacturability aspect of SOI CMOS RFICs," in *Proc. Custom Integr. Circuit Conf.*, Oct. 2004, pp. 541–548.

- [4] T. Douseki, T. Tsukahara, Y. Yoshida, F. Utsunomiya, and N. Hama, "A batteryless wireless system with MTCMOS/SOI circuit technology," in *Proc. Custom Integr. Circuit Conf.*, Sep. 2003, pp. 163–168

- [5] J.-P. Raskin, R. Gillon, D. Vanhoenacker, and J.-P. Colinge, "Direct extraction method of SOI MOSFET transistors parameters," in *Proc. IEEE Int. Conf. Microelectron. Test Struct.*, Mar. 1996, vol. 9, pp. 101–104

- [6] J.-P. Raskin, G. Dambrine, and R. Gillon, "Direct extraction of the series equivalent circuit parameters for the small-signal model of SOI MOSFET's," *IEEE Microw. Guided Wave Lett.*, vol. 7, no. 12, pp. 408–410, Dec. 1997.

- [7] A. Bracale, V. Ferlet-Cavrois, N. Fel, D. Pasquet, J. L. Gautier, J. L. Pelloie, and J. du Port de Poncharra, "A new approach for SOI devices small-signal parameters extraction," in *Analog and Integrated Circuits and Signal Processing*. Norwell, MA: Kluwer, 2000, pp. 157–169.

- [8] D. Lovelace, J. Costa, and N. Camilleri, "Extracting small-signal model parameters of silicon MOSFET transistors," in *IEEE MTT-S Int. Dig.*, 1994, pp. 865–868.

- [9] S. Lee, H. K. Yu, C. S. Kim, J. G. Koo, and K. S. Nam, "A novel approach to extracting small-signal model parameters of silicon MOS-FETs," *IEEE Microw. Guided Wave Lett.*, vol. 7, no. 3, pp. 75–77, Mar. 1997.

- [10] C. L. Chen, R. H. Mathews, J. A. Burns, P. W. Wyatt, D. Yost, C. K. Chen, M. Fritze, J. M. Knecht, V. Suntharalingam, A. Soares, and C. L. Keast, "High-frequency characterization of sub-0.25-\(\mu\) m fully depleted silicon-on-insulator MOSFETS," *IEEE Electron Device Lett.*, vol. 21, no. 10, pp. 497–499, Oct. 2000.

- [11] W. Liu, R. Gharpurey, M. C. Chang, U. Erdogan, R. Aggarwal, and J. P. Mattia, "R.F. MOSFET modeling accounting for distributed substrate and channel resistances with emphasis on the BSIM3v3 SPICE model," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, 1997, pp. 309–312.

- [12] R. T. Chang, M. T. Yang, P. P. C. Ho, Y. J. Wang, Y. T. Chia, B. K. Liew, C. P. Yue, and S. S. Wong, "Modeling and optimization of substrate resistance for RF-CMOS," *IEEE Trans. Electron Devices*, vol. 51, no. 3, pp. 421–426, Mar. 2004.