# 10-GHz Highly Symmetrical Sub-Harmonic Gilbert Mixer Using GaInP/GaAs HBT Technology

Tzung-Han Wu, Student Member, IEEE, and Chinchun Meng, Member, IEEE

Abstract—A 10-GHz sub-harmonic Gilbert mixer is demonstrated using GaInP/GaAs hetero-junction bipolar transistor technology. The local oscillator (LO) signal time-delay path in the sub-harmonic LO stage is compensated using the fully symmetrical stacked-LO doubler; therefore, the balance of the sub-harmonic LO stage, the radio frequency to intermediate frequency isolation, and IIP $_2$  are improved. The demonstrated 10-GHz sub-harmonic mixer achieves 10 dB conversion gain, IP $_{1\rm dB}$  of -12 dBm, IIP $_3$  of 2 dBm and IIP $_2$  of 33 dBm.

Index Terms—Micromixer, 1/f noise, port-to-port isolation, sub-harmonic Gilbert mixer, time-delay-compensated doubler.

### I. INTRODUCTION

HE direct conversion architecture plays a dominate role in the radio frequency (RF) receiver design. The integration level of the direct conversion receiver is very high but suffers from the self-mixing problem; therefore, sub-harmonic mixer topologies [1]–[3] are proposed. The stacked-local oscillation (LO) sub-harmonic mixer [1] contains two stacked Gilbert cells and these Gilbert cells switch the RF currents in quadrature phase.

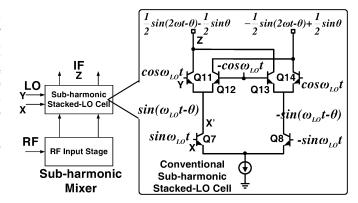

A Gilbert multiplier can be used as the frequency doubler [4] for the stacked-LO cell. A new highly symmetrical stacked-LO doubling cell [5], [6] is employed in this letter to improve the LO speed, IIP<sub>2</sub> and the radio frequency to intermediate frequency (RF-to-IF) isolation. In general, the HBT device generates output collector current with a time delay with respect to the input base-emitter voltage. This time delay limits the speed of the LO stage as well as the performances of IIP<sub>2</sub> and RF-to-IF isolation. When two quadrature LO signals are injected into a conventional stacked-LO doubler as shown in Fig. 1, the signal from node X to node Z suffers from a larger time delay when compared with the signal from node Y to node Z. This time delay generates a dc term  $(-1/2\sin\theta)$  in the conventional stacked-LO doubling cell [5], [6] as shown in Fig. 1.

The dc term in the LO stage influences the LO balance of the mixer, and the IIP<sub>2</sub> performance can be degraded. Moreover, the

Manuscript received November 7, 2006; revised February 11, 2007. This work was supported by the National Science Council of Taiwan, R.O.C., under Contracts NSC 96-2752-E-009-001-PAE and NSC 95-2221-E-009-043-MY3, by the Ministry of Economic Affairs of Taiwan under Contract 95-EC-17-A-05-S1-020, by the MoE ATU Program under Contract 95W803, and by the NDL and CIC.

The authors are with the Department of Communication Engineering, National Chiao-Tung University, Hsinchu, Taiwan, Republic of China (fax: 886-3-5736952, e-mail: ccmeng@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2007.895717

Fig. 1. Conventional stack-LO doubler with the time delay effect.

mixer suffers from poor IIP<sub>2</sub> performance if the LO stage can not respond fast enough [7]. Because the speed of the LO doubling cell has increased and the balance of the LO stage is further improved by the highly symmetrical stacked-LO doubling cell in our work, the IIP<sub>2</sub> performance is improved. Besides, the dc term or the LO balance influences the RF-to-IF isolation drastically [8]. The RF-to-IF isolation can be improved in our work because the dc term in the LO stage is eliminated by the highly symmetrical LO sub-harmonic stage.

The highly symmetrical stacked-LO sub-harmonic mixer was demonstrated at 10 GHz using SiGe HBT technology [9]. However, the IIP<sub>2</sub> and RF-to-IF isolation are inferior to these of the GaInP/GaAs HBT sub-harmonic mixer in this letter. A stacked-LO sub-harmonic mixer needs an resistor and capacitor–capacitor and resistor (RC–CR) quadrature generator. It is difficult to achieve high accuracy RC–CR in the silicon technology at high frequencies even with electronic tuning [2]. The accurate high frequency RC–CR quadrature generator can be realized in the GaAs technology because the thin film resistors and capacitors can be fabricated precisely on the semi-insulating substrate. Furthermore, the GaAs semi-insulating substrate eliminates the substrate parasitic and coupling effects when compared with the silicon substrate. Thus, the IIP<sub>2</sub> and RF-to-IF isolation are greatly improved in this work.

# II. CIRCUIT DESIGN

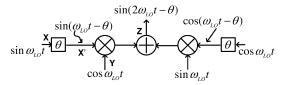

The crossed-coupled time-delay-compensated stacked-LO doubler as shown in Fig. 2 can remove the extra dc component caused by the time delay in the conventional stacked-LO doubler. If two doublers are connected as shown in Fig. 2, the output signal at port Z contains no dc term. Thus, the time-delay compensated LO doubler is employed in the LO stage of the

Fig. 2. Block diagram of the time-delay-compensated LO frequency doubler.

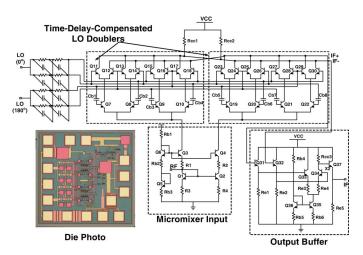

Fig. 3. Circuit schematic and the die photo of the 10-GHz double-balanced sub-harmonic mixer with the LO time-delay compensation.

sub-harmonic Gilbert mixer to improve the LO speed, the RF-to-IF isolation and IIP<sub>2</sub>.

The demonstrated sub-harmonic Gilbert mixer as shown in Fig. 3 consists of a micromixer input stage [10] (transistors  $Q_1$ – $Q_4$ ), LO delay-compensated doublers (transistors  $Q_7$ – $Q_{30}$ ) and an output buffer. The micromixer is suitable for high frequency mixer design. The common-base transistor  $Q_3$  and common-emitter transistor  $Q_2$  work together to generate differential RF signals. Because the diode-connected transistor  $Q_1$  lowers the input impedance of the common-emitter transistor  $Q_2$ , the micromixer input stage possesses better frequency response when compared with the conventional emitter-coupled input stage; therefore, the frequency response of the micromixer RF input stage could easily reach 10 GHz.

As shown in Fig. 3, two time-delay-compensated LO doublers are employed to form a double-balanced sub-harmonic Gilbert mixer. One consists of transistors  $Q_7$ – $Q_{18}$  and the other consists of transistors  $Q_{19}$ – $Q_{30}$ . The LO frequency is designed at 5-GHz and a two-section polyphase filter is employed to generate the quadrature LO signals that are needed by the sub-harmonic LO cell.

### III. RESULTS AND DISCUSSIONS

The GaInP/GaAs HBT device has the peak cut-off frequency of 40 GHz and  $BV_{\rm CEO}$  of 13 V. The dc supply voltage is 5 V and the current consumption of the mixer core is 4 mA. The die photo of the 10-GHz double-balanced down-conversion subharmonic mixer is shown in Fig. 3 and the die size is 1 mm  $\times$  1 mm.

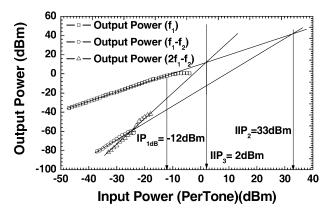

As shown in Fig. 4, the measured power performance of  $IP_{1dB}$ ,  $IIP_3$ , and  $IIP_2$  are -12 dBm, 2 dBm, and 33 dBm, respectively, when the IF frequency is 100 KHz. The

Fig. 4. Measured power performance of the 10-GHz sub-harmonic mixer with the LO time-delay compensation.

TABLE I Comparisions of the IIP $_2$  of Sub-Harmonic GILBERT Mixers

|                               | This Work              | Ref [1]        | Ref [2]        | Ref [3]         | Ref [9]         |

|-------------------------------|------------------------|----------------|----------------|-----------------|-----------------|

| Tech.                         | 2 μmGaInP/<br>GaAs HBT | 0.5 μm<br>SiGe | 0.5 μm<br>SiGe | 0.35 μm<br>SiGe | 0.35 μm<br>SiGe |

| RF (GHz)                      | 10                     | 1              | 5-6            | 2               | 10              |

| IIP <sub>2</sub> (dBm)        | 33                     | 35             | 29             | 27              | 10              |

| IP <sub>1dB</sub> (dBm)       | -12                    | N/A            | -5.4           | -16             | -20             |

| RF-to-IF<br>Isolation<br>(dB) | -50                    | N/A            | N/A            | N/A             | -45             |

| DSB<br>Noise<br>(dB)          | 14                     | 7              | N/A            | 8               | 16              |

time-delay-compensated LO cell provides higher order symmetry [6]. Even-order harmonics can be eliminated and the IIP<sub>2</sub> performance can be improved. Moreover, the GaAs technology also helps to maintain the balance of the sub-harmonic mixer as described in the introduction.

The IIP<sub>2</sub> of some excellent BJT-type sub-harmonic Gilbert mixers are compared in Table I. As described in the introduction, it is difficult to achieve good IIP<sub>2</sub> performance at high frequencies [7]. Our work has second to none IIP<sub>2</sub> performance for the RF frequency around 10 GHz when compared with other works because a high-speed and fully balanced LO stage is achieved using GaInP/GaAs HBT technology [7].

The demonstrated mixer has better than 15-dB input return loss and 11-dB output return loss from dc to 20 GHz. The measured RF-to-IF isolation is about -50 dB when the RF frequency is 10 GHz. The good RF-to-IF isolation demonstrated here indicates that the time-delay compensated LO doublers are effective. The LO-to-RF the LO-to-IF, 2LO-to-RF [1] and the 2LO-to-IF isolations are -65 dB, -48 dB, -75 dB, and -62 dB, respectively, when the LO frequency is 5 GHz.

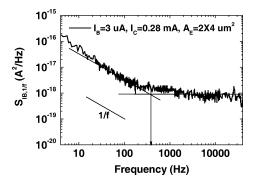

The Low-frequency noise figure is another important issue for a direct-conversion receiver and the 1/f noise dominates the low-frequency noise figure of the direct-conversion mixer [11]. Generally speaking, the CMOS direct-conversion mixer suffers from high 1/f noise corner. The current conduction mechanism of a ledge-passivated GaInP/GaAs HBT is the bulk conduction

Fig. 5. Measured low-frequency noise spectrum of the HBT (AE =  $2 \times 4 \mu \text{m}^2$ , IC = 2.8 mA, and IB =  $3 \mu \text{A}$ ).

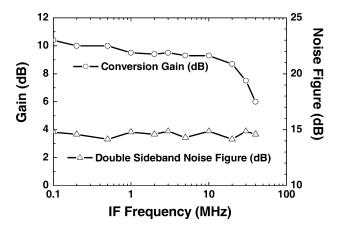

Fig. 6. Measured double sideband noise figure and conversion gain of the 10-GHz sub-harmonic micromixer as a function of IF frequency.

[12], thus the 1/f noise performance is better than that of the surface-conducting CMOS device. The measured low frequency noise of the GaInP/GaAs HBT device is shown in Fig. 5. The 1/f noise corner is about 400 Hz and the measured slope is 20 dB/decade.

Fig. 6 shows the measured double sideband noise figure and conversion gain as a function of IF frequency. The measured IF bandwidth is 30 MHz. Because of the characteristic of the HBT device, the measured low-frequency noise keeps constant from 100 KHz to 40 MHz without extra circuit design techniques [11]. As shown in Fig. 6, the double sideband noise figure is about 14 dB without the appearing of the 1/f noise corner. Compared with the former result [9], this work has 2-dB improvement of noise figure. It is because the base resistance of the heavily doped base in the GaInP/GaAs HBT device is much smaller and thus the thermal noise is less.

The series sub-harmonic doubler core presented in this work contains much more transistors when compared with the parallel sub-harmonic core [3]. The base resistance Rb dominates the thermal noise floor and thus the series sub-harmonic doubler cores suffer from more noise contributors. On the other hand, the thermal noise is smaller in the parallel structure because the resistors Rb are in parallel. The  $P_{\rm 1dB}$  of the presented structure is also limited in the series sub-harmonic mixer in this work. Because there are too many Gilbert cells stacked together, the signals waveform clippings of the demonstrated mixer are more serious than that of the parallel sub-harmonic core.

## IV. CONCLUSION

The sub-harmonic Gilbert mixer is designed with the time-delay-compensated LO doubler stage to improve the IIP<sub>2</sub>, and RF-to-IF isolation. The measured double sideband noise figure indicates that the GaInP/GaAs HBT device is suitable in a direct-conversion receiver because of the excellent low-frequency-noise characteristics. Thus, a 10-GHz GaInP/GaAs HBT sub-harmonic Gilbert mixer with peak  $f_T$  of 40 GHz can be demonstrated in this letter.

### REFERENCES

- [1] L. Sheng, J. C. Jensen, and L. E. Larson, "A wide-bandwidth Si/SiGe HBT direct conversion sub-harmonic mixer/downconverter," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1329–1337, Sep. 2000.

- [2] R. Svitek and S. Raman, "5–6 GHz SiGe active I/Q subharmonic mixers with power supply noise effect characterization," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 7, pp. 319–321, Jul. 2004.

- [3] M. Goldfarb, E. Balboni, and J. Cavey, "Even harmonic double-balanced active mixer for use in direct conversion receivers," *IEEE J. Solid-State Circuits*, vol. 38, no. 10, pp. 1762–1766, Oct. 2003.

- [4] V. Puyal, A. Konczykowska, P. Nouet, S. Bernard, S. Blayac, F. Jorge, M. Riet, and J. Godin, "A DC- 100 GHz frequency doubler in InP DHBT technology," in *IEEE MTT-S Int. Dig.*, Fort Worth, TX, 2004, pp. 167–170.

- [5] A. W. Buchwald, K. W. Martin, A. K. Oki, and K. W. Kobayashi, "A 6-GHz integrated phase-locked loop using AlGaAs/GaAs heterojunction bipolar transistors," *IEEE J. Solid-State Circuits*, vol. 27, no. 12, pp. 1752–1762, Dec. 1992.

- [6] R. Magoon, A. Molnar, J. Zachan, G. Hatcher, and W. Rhee, "A single-chip quad-band (850/900/1800/1900 MHz) direct conversion GSM/GPRS RF transceiver with integrated VCOs and franctional-N synthesizer," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1710–1720, Dec. 2002.

- [7] D. Manstretta, M. Brandolini, and F. Svelto, "Second-order intermodulation mechanisms in CMOS downconverters," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 394–406, Mar. 2003.

- [8] S. C. Tseng, C. C. Meng, Y. H. Li, and G. W. Huang, "The port-to-port isolation of the downconversion p-type micromixer using Different N-Well Topologies," *IEICE Trans. Electron.*, vol. E89-C, no. 4, pp. 482–487, Apr. 2006.

- [9] T. H. Wu and C. C. Meng, "10-GHz SiGe BiCMOS sub-harmonic gilbert mixer using the fully symmetrical and time-delay compensated LO cells," *IEICE TRANS. Fund. Electron., Commun. Comput. Sci.*, vol. E90-A, no. 2, pp. 326–332, Feb. 2007.

- [10] B. Gilbert, "The MICROMIXER: A highly linear variant of the Gilbert mixer using a bisymmetric Class-AB input stage," *IEEE J. Solid-State Circuits*, vol. 32, no. 9, pp. 1412–1423, Sep. 1997.

- Circuits, vol. 32, no. 9, pp. 1412–1423, Sep. 1997.

[11] H. Darabi and J. Chiu, "A noise cancellation technique in active RF-CMOS mixers," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2628–2632. Dec. 2005.

- [12] D. Costa and A. Khatibzadeh, "Use of surface passivation ledge and local feedback to reduce amplitude modulation noise in AlGaAs/GaAs heterojunction bipolar transistor," *IEEE Microw. Guided Wave Lett.*, vol. 4, no. 2, pp. 45–47, Feb. 1994.