# A 90-dB $\Omega$ 10-Gb/s Optical Receiver Analog Front-End in a 0.18- $\mu$ m CMOS Technology

Wei-Zen Chen, Member, IEEE, and Da-Shin Lin

Abstract—A 10-Gb/s 90-dBΩ optical receiver analog front-end (AFE), including a transimpedance amplifier (TIA), an automatic gain control circuit, and a postamplifier (PA), is fabricated using a 0.18-μm CMOS technology. In contrast with a conventional limiting amplifier architecture, the PA is consisted of a voltage amplifier followed by a slicer. By means of the TIA and the PA codesign, the receiver front-end provides a -3-dB bandwidth of 7.86 GHz and a gain bandwidth product (GBW) of 248.5 THz-Ω. The tiny photocurrent received by the AFE is amplified to a differential voltage swing of 900 mV $_{\rm PP}$  when driving 50-Ω output loads. The measured input sensitivity of the optical receiver is -13 dBm at a bit-error rate of  $10^{-12}$  with a  $2^{3\,1}-1$  pseudorandom test pattern. The optical receiver AFE dissipates a total power of 199 mW from a 1.8-V supply, among which 35 mW is consumed by the output buffer. The chip size is  $1300~\mu m \times 1796~\mu m$ .

*Index Terms*—Optical receiver, postamplifier (PA), transformer, transimpedance amplifier (TIA).

## I. INTRODUCTION

THIS PAPER describes an optical receiver analog front end (AFE) that incorporates a transimpedance amplifier, an automatic gain control circuit, and a post amplifier (PA) in a single chip. Conventionally, the PA is basically a limiting amplifier which consists of identical gain cells and with equal gain-bandwidth performance in each gain stage [2], [6], [7]. However, in such a multistage cascaded amplifier, the last few stages may be driven into large-signal operation mode, and the overall signal bandwidth is limited by the first few stages. It turns out that the gain and bandwidth assignment for each gain stage is not optimally designed.

Different from the prior art, in this design, the PA is composed of a voltage amplifier followed by a slicer, whose gain and bandwidth are assigned separately. Thus, their gain bandwidth product (GBW) requirement per stage can be further relaxed so as to save power dissipation. The proposed receiver also provides several advantages over conventional multiple chips solutions [1]–[3]. First, tiny photocurrent generated from the photodetector can be on-chip enlarged to a logic level. It increases noise immunity and off-chip interference can be

Manuscript received March 16, 2006; revised June 5, 2006. This work was supported in part by projects under Contract NSC-93-2220-E009-004 and Contract 93-EC-17-A-07-S1-001, by Mediatek Inc., and by the Industrial Technology Research Institute (ITRI)/SoC Technology Center (STC).

W.-Z. Chen is with the Department of Electronics Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan 300, R.O.C. (e-mail: wzchen@mail.nctu.edu.tw).

D.-S. Lin was with National Chiao-Tung University, Hsin-Chu, Taiwan 300, R.O.C. He is now with MediaTek Inc, Hsin-Chu, Taiwan 300, R.O.C.

Digital Object Identifier 10.1109/TVLSI.2007.893625

avoided. Second, no interstage matching networks are required at the transimpedance amplifier (TIA) output stage and the input stage of the PA. Broadband matching networks in general induce gain loss and are power hungry. By these means the receiver manifests a GBW as high as  $248.5~\text{THz-}\Omega$  and consumes much less power while fewer peaking inductors are required in comparison to the prior art.

This paper is organized as follows. Section II describes the architecture of the optical receiver. The TIA and the PA are codesigned, and the design issues of the receiver AFE are discussed in Section III. To achieve both wide-band and high gain design goals, inductive peaking techniques are adopted using 3-D symmetric transformers [4]. In this paper, distributed capacitance models [13] of the 3-D transformer are proposed, and its superiorities over the conventional architectures are investigated in detail. Their performance comparisons are discussed in Section IV. Section V describes the experimental results. Finally, our conclusions are presented in Section VI.

## II. OPTICAL RECEIVER ARCHITECTURE

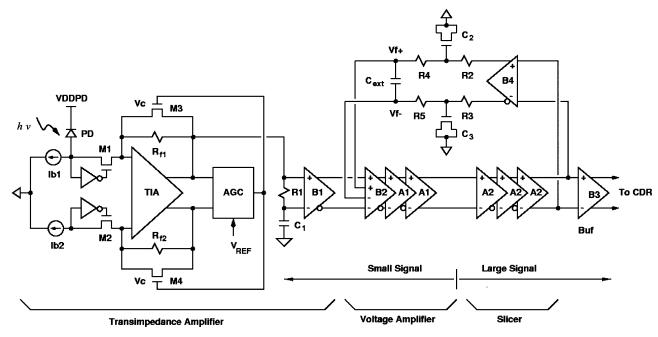

The receiver architecture is shown in Fig. 1, which integrates a transimpedance amplifier, an automatic gain control (AGC) circuit, and a PA in a single chip. To alleviate bandwidth degradation caused by the parasitic capacitance of the photodetector and IC package, a regulated cascode (RGC) input stage is adopted [5]. The TIA architecture is in pseudo differential configuration with shunt-feedback for better sensitivity and higher common mode noise immunity. Furthermore, an AGC loop is built in to avoid data jitter induced by signal overload. The AGC is composed of an amplitude detector, a comparator, and an integrator [15]. As the TIA's output swing exceeds a threshold voltage, the AGC will be activated to keep output amplitude constant by turning on the tunable feedback resistors M3 and M4. Otherwise, the AGC will be disabled, and M3 and M4 are switched off for high-gain and low-noise operation. The single ended TIA output is converted to a fully differential signal by the B1 amplifier in conjunction with the R1 and C1 low-pass filter. The conversion gain of the TIA is chosen to make its output swing overpass the sensitivity level of the PA, and its bandwidth is chosen to compromise between ISI and noise performance [7].

Different from our previous work in [7], the PA is consisted of a voltage amplification stage (for small-signal amplification) followed by a slicing stage (for large signal operation). In contrast to a conventional limiting amplifier that is composed of five or six identical gain cells [2], [6], [7], the voltage amplifier is designed to provide a sufficient gain to fully switch the slicer. In

Fig. 1. Optical receiver architecture.

this case, a three-stage cascaded amplifier is required for a minimum power dissipation. Thus the required GBW per gain stage is much relaxed compared to that of conventional architectures, and no peaking inductors are required in the voltage amplifier design. The slicer functions as a predriver for the output buffer. As a large-signal operation stage, it also provides 24-dB conversion gain before driving the last buffer stage, and the bandwidth degradation caused by the slicer is almost negligible [8].

## III. TIA AND PA CODESIGN

For an optical receiver, the input sensitivity is limited by the input referred noise current  $\overline{I_{n,\text{in}}^2}$ , which can be expressed

$$\overline{I_{n,\text{in}}^2} = \overline{I_{n,\text{TIA}}^2} \text{BW}_{\text{TIA}} + \frac{\overline{V_{n,\text{PA}}^2} \text{BW}_{\text{PA}}}{T_z^2}$$

(1)

where  $T_z$  is the conversion gain of the TIA,  $\overline{I_{n,{\rm TIA}}^2}$  and  $\overline{V_{n,{\rm PA}}^2}$  represent the input referred noise current of the TIA and the input referred noise voltage of the PA, BW<sub>TIA</sub> and BW<sub>PA</sub> denote their noise bandwidth, respectively. The lower bound of the  $T_z$  is chosen to avoid the PA degrading the input sensitivity level, and the input referred noise current of the TIA is essential to the overall receiver performance. As a rule of thumb, the -3-dB bandwidth of the TIA is chosen to be about 0.7 bit rate to compromise between ISI and noise performance, while the -3-dB bandwidth of the PA is chosen for about 1.2 bit rate to minimize ISI.

In this design, to achieve an input sensitivity level of -13 dBm with a photodetector whose responsivity is 1 A/W, the transimpedance amplifier is designed to provide a conversion gain of 50 dB $\Omega$  and a -3 dB bandwidth of about 8 GHz. The TIA output is then enlarged and limited to a voltage swing of 900 mVpp (differential) to drive external 50- $\Omega$  loads by the PA. The corresponding conversion gain in the post amplification stage is about 40 dB. Since the output stage delivers high

output current and introduces significant capacitance to the amplifier core, inverse scaling [16] is not applied in this design [2].

Conventional PA is comprised of identical cascaded gain cells [2], [6], [7]. Assuming each gain cell is identical and approximated by a two-pole amplifier, its conversion gain can be described by A(s), where

$$A(s) = \frac{A_s \cdot \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}.$$

(2)

Here,  $A_s$  denotes the small-signal dc gain,  $\zeta$  is the corresponding damping factor, and  $\omega_n$  is the nature frequency. Let the targeted -3 dB bandwidth of an N-stage cascaded amplifier be  $\omega_c$ , and the conversion gain be  $A_c$ . For a flat response, the required gain bandwidth product (GBW) per stage can be expressed as [2], [6]

GBW =

$$\omega_c \times \left(\frac{1}{2^{1/N} - 1}\right)^{1/4} \times A_c^{1/N}$$

. (3)

For a targeted bandwidth of 12 GHz and a conversion gain of 40 dB, according to (3), a five-stage limiting amplifier demands a GBW of 49 GHz per stage, and, thus, inductive peaking for bandwidth enhancement is required in a conventional design. In contrast to a conventional limiting amplifier that is comprised of identical gain cells, in this design, the PA is constructed of a voltage preamplifier (small-signal operating stage) followed by a slicer (large-signal operating stage). For the same input sensitivity level, the preamplifier only needs to provide 16-dB voltage gain to fully switch the slicer. Thus, a three-stage voltage amplifier is chosen for a minimum power dissipation by the analytical model proposed in [6]. It corresponds to a required GBW of 35 GHz per stage according to (3), which is much relaxed compared to that of a conventional stand-alone limiting amplifier with identical gain cells. A lower GBW per stage means no special peaking inductors are required in the gain cell design,

and the chip area can be further saved. The slicer stage, which is consisted of three identical buffers, further provides 24-dB conversion gain before driving the last output buffer. Since it is a large-signal operating stage, the bandwidth degradation caused by the slicer is negligible [8].

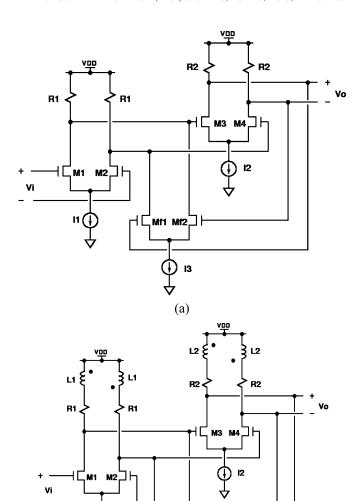

The core circuit of the voltage amplifier is shown in Fig. 2(a), which is based on Cherry-Hooper circuit architecture with active feedback [2], [17]. Compared to the prior art in [2], since the GBW requirement of the gain cell is much relaxed, thus no peaking inductor is required to save area. Also, different from our previous work in [7] using resistive feedback, unilaterally active feedback avoids tradeoffs between the feedback factor (close loop gain) and the open loop gain (close loop bandwidth) of the voltage amplifier.

Let C1 and C2, respectively, represent the parasitic capacitance at the drain node of M1 and M3,  $G_{m1}$  and  $G_{m2}$  denote the transconductance of the differential pair  $(M_1 - M_2)$  and  $(M_3 - M_4)$ , and  $G_{mf}$  be the transconductance of the active feedback stage  $(M_{f1}-M_{f2})$ , the conversion gain of the voltage amplifier can be derived as [2]

$$\frac{V_o}{V_i} = \frac{A_v \omega_n^2}{s^2 + 2\varsigma \omega_n s + \omega_n^2} \tag{4}$$

where

$$A_v = \frac{G_{m1}G_{m2}R_1R_2}{1 + G_{m2}G_{mf}R_1R_2} \tag{5}$$

$$A_{v} = \frac{G_{m1}G_{m2}R_{1}R_{2}}{1 + G_{m2}G_{mf}R_{1}R_{2}}$$

$$\zeta = \frac{1}{2} \frac{R_{1}C_{1} + R_{2}C_{2}}{\sqrt{R_{1}R_{2}C_{1}C_{2}(1 + G_{mf}G_{m2}R_{1}R_{2})}}$$

$$\sqrt{1 + G_{mf}G_{m2}R_{1}R_{2}}$$

$$(5)$$

$$\omega_n = \sqrt{\frac{1 + G_{mf} G_{m2} R_1 R_2}{R_1 R_2 C_1 C_2}}.$$

(7)

For a maximally flat Butterworth response, the -3-dB bandwidth of the voltage amplifier is about  $\omega_n$ . In addition, it has been shown in [2] that the active feedback can increase the GBW of the voltage amplifier beyond the technology  $f_T$ . The core cell of the slicer is shown in Fig. 2(b). Herein, a symmetric transformer is utilized to accelerate voltage switch and balance the rising and the falling time of the output waveform at a high voltage level.

# IV. DISTRIBUTED CAPACITANCE MODEL OF TRANSFORMERS

To realize broadband amplifiers under low supply voltage, inductive peaking techniques are applied in the TIA, slicer, and buffer stage design [9]. Conventional planar inductors and transformers are in general bulky and occupy significant chip areas [10], [11]. Although a miniaturized 3-D inductor structure has been proposed [12], it is asymmetric and two inductors are needed in a fully differential amplifier. To reduce inductor counts and save chip area, a 3-D inverting type transformer is utilized in this design [4]. Furthermore, as a peaking inductor in a broad band amplifier design, the self-resonant frequency  $(f_{SR})$  of the inductor is more demanding than its quality factor since the peaking inductor would become a capacitive load as the operating frequency exceeds  $f_{SR}$ . The resonant frequency can be viewed as the frequency at which the peak magnetic  $(E_M)$  and electric energy  $(E_E)$  are equal, and can

Fig. 2. (a) Gain cell of preamplifier. (b) Gain cell of slicer.

be determined by  $f_{SR} = (2\pi\sqrt{C_{eq}L_{eq}})^{-1}$ , where  $L_{eq}$  and  $C_{\rm eq}$ , respectively, represent the equivalent inductance and capacitance of the inductor [11], [12]. In the following, the  $C_{\rm eq}$  of both a planar inductor and our proposed 3-D symmetric transformer are analyzed utilizing a distributed capacitance model, and their  $f_{SR}$  comparisons are investigated in detail.

(b)

For a given peak voltage of  $V_0$  across the inductor and a stored electric energy of  $(E_E)$  in the structure, the equivalent capacitance  $C_{\rm eq}$  can be calculated by [11]

$$E_E = \frac{1}{2} C_{\rm eq} V_o^2. \tag{8}$$

To derive the electric energy stored in the parasitic capacitors of the inductor, the following assumptions are made to simplify the derivations [11]–[13].

1) Voltage distribution is proportional to the length of the metal track.

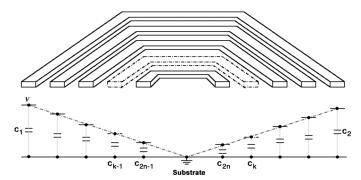

Fig. 3. Cross-sectional view and voltage profile of a planar inductor.

2) The voltage potential is equal in half turn of the metal wire in the transformer and is determined by averaging the voltages of the previous half turn and the next one.

Fig. 3 illustrates the cross-sectional view of an n turn planar inductor and its electrical potential distribution. Assume the lengths of each half turn are denoted as  $l_1, l_2, \ldots, l_{2n}$ , the metal width is W, metal thickness is T, and the total length of the metal wire is  $l_T = \sum_{k=1}^{2n} l_k$ .

metal wire is  $l_T = \sum_{k=1}^{2n} l_k$ .

Define  $d_k = (1/l_T) \cdot \sum_{i=1}^{k} l_i$ , the voltage profile of the inductor can be described as

$$V_k = V_0 \times (1 - d_k). \tag{9}$$

Based on these assumptions, the voltage of the kth half turn can be approximated as

$$V(k) = \frac{1}{2} \left[ V_0 \times (1 - d_{k-1}) + V_0 \times (1 - d_k) \right]. \tag{10}$$

Let  $C_{\mathrm{mts}}(k)$  denote the unit capacitance of metal k to substrate, the electrical energy stored in the capacitor between the metal layer and the substrate can be expressed as  $E_{E1,mts}$ , where

$$E_{E1,mts} = \frac{1}{2} \sum_{k=1}^{2n} C_{\text{mts}}(k) \cdot l_k \cdot W \cdot V(k)^2.$$

(11)

In addition, let  $C_{\rm msm}(k)$  denote the unit side-wall capacitance between metal k and k+2, the electric energy stored in the side-wall parasitic capacitors between the metal layers can be expressed as  $E_{E1,mtm}$ , where

$$E_{E1,mtm} = \frac{1}{2} \sum_{k=1}^{2n-2} C_{\text{msm}}(k) \cdot l_k \cdot T \cdot [V(k) - V(k+2)]^2.$$

(12)

Combining (11) and (12), the total electric energy  $(E_{E1,tot})$  stored in the structure can be derived as [13]

$$E_{E1,\text{tot}} = E_{E1,mts} + E_{E1,mtm} = \frac{1}{2}C_{\text{eq}1}V_0^2.$$

(13)

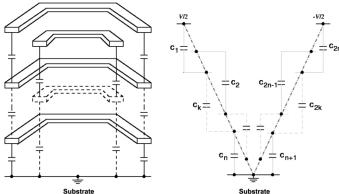

Fig. 4. Cross-sectional view and voltage profile of a 3-D transformer.

Thus, the effective parasitic capacitance of a planar inductor can be expressed as  $C_{\rm eq1}$ , which is shown here

$$C_{\text{eq1}} \approx \frac{1}{4} \sum_{k=1}^{2n} C_{\text{mts}}(k) \cdot l_k \cdot W \cdot (2 - d_{k-1} - d_k)^2 + \frac{1}{4}$$

$$\times \sum_{k=1}^{2n-2} C_{\text{msm}}(k) \cdot l_k \cdot T \cdot (d_{k+2} - d_k + d_{k+1} - d_{k-1})^2. \quad (14)$$

On the other hand, the cross-sectional view of an n-turn, single turn per layer, 3-D symmetric transformer and its electrical potential distribution is illustrated in Fig. 4. In case of a differential excitation, the center point of the transformer can be connected to a common mode voltage and ac grounded. The voltage profile of the transformer can be described as

$$V_k = V_0 \times (1/2 - d_k). \tag{15}$$

Also, it can be seen that the metal to substrate capacitors exist in the bottom two metal layers only. Based on the same assumptions previously mentioned, the electrical energy stored in the capacitor between the metal layer and the substrate can be expressed as  $E_{E2,mts}$ , where

$$E_{E2,mts} = \frac{1}{2} \sum_{k=n-1}^{n+2} C_{\text{mts}}(k) \cdot l_k \cdot W \cdot V(k)^2.$$

(16)

On the other hand, since there is only one turn on a metal layer, the side-wall capacitors do not exist. Let  $C_{\mathrm{mtm}}(k)$  denote the unit metal to metal overlapped capacitance between metal k and k+2, the electrical energy stored in the metal to metal parasitic capacitors can be represented as

$$E_{E2,mtm} = \frac{1}{2} \left[ \sum_{k=1}^{n-2} C_{\text{mtm}}(k) \cdot l_k \cdot W \cdot [V(k) - V(k+2)]^2 + \sum_{k=n+1}^{2n-2} C_{\text{mtm}}(k) \cdot l_k \cdot W \cdot [V(k) - V(k+2)]^2 \right]. \quad (17)$$

By taking both (16) and (17) into account, the total electric energy  $(E_{E2,\text{tot}})$  stored in the structure can be derived as [13]

$$E_{E2,\text{tot}} = \frac{1}{2}C_{eq2}V_0^2 = E_{E2,mts} + E_{E2,mtm}.$$

(18)

The effective parasitic capacitance of the 3-D transformer can be expressed as  $C_{eq2}$ , which is also shown here

$$C_{eq2} \approx \frac{1}{4} \sum_{k=n-1}^{n+2} C_{\text{mts}}(k) \cdot l_k \cdot W \cdot (1 - d_k - d_{k-1})^2$$

$$+ \frac{1}{4} \sum_{k=1}^{n-2} C_{\text{mtm}}(k) \cdot l_k \cdot W$$

$$\cdot (d_{k+2} - d_k + d_{k+1} - d_{k-1})^2$$

$$+ \frac{1}{4} \sum_{k=n+1}^{2n-2} C_{\text{mtm}}(k) \cdot l_k \cdot W$$

$$\cdot (d_{k+2} - d_k + d_{k+1} - d_{k-1})^2.$$

$$(19)$$

Based on the derived equations in (14) and (19), for an inductor pair with an inductance of 2.85 nH in each branch, five turns, metal width =  $10~\mu m$ , metal spacing =  $1.5~\mu m$ , and an inner diameter of  $110~\mu m$ , the effective parasitic capacitance of the 3-D transformer ( $C_{\rm eq2}$ ) is reduced by 45% compared to that of a planar inductor pair ( $C_{\rm eq1}$ ). The significant improvement is due to the following reasons.

- The metal to substrate capacitance is minimized and only exists in the bottom two metal layers.

- The side-wall capacitors are negligible in this architecture, which would become significant in a deep-submicrometer process [13].

- 3) The metal to metal parasitic capacitances are reduced by increasing the distance between metal plates and minimizing the electrical potential across the top and bottom plates [4].

By EM simulation, the 3-D transformer manifests a higher self resonant frequency (12 GHz versus 9 GHz) compared to its planar counterpart owing to a smaller  $C_{\rm eq}$ . Furthermore, the substrate loss of the 3-D transformer is improved by a differential stimulus, and a wider operating bandwidth is achieved in contrast to a single-ended driven counterpart [14]. Most important of all, the chip area of the 3-D transformer is 47% smaller than that of its planar counterparts, which is essential in the multistage broadband amplifier design.

## V. EXPERIMENTAL RESULTS

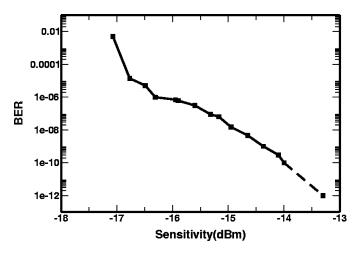

For performance measurement, the receiver IC and a photodetector are mounted on a printed circuit board. The eye diagrams and the bit error rate performance are characterized using Agilent N4901B. The pattern generator sends a  $2^{31} - 1$  PRBS test pattern to modulate a commercial 10-Gb/s laser module. With an Oepic-P5030A photodetector, whose responsivity is 1 A/W and parasitic capacitance is about 0.15 pF, the measured sensitivity of the optical receiver AFE at 10 Gb/s is about -13 dBm for a bit error rate of less than  $10^{-12}$ . The bit error rate performance is summarized in Fig. 5. The tolerated power level is up to 0 dBm by the built-in automatic gain control scheme. The

Fig. 5. Measured bit error rate performance of the optical receiver.

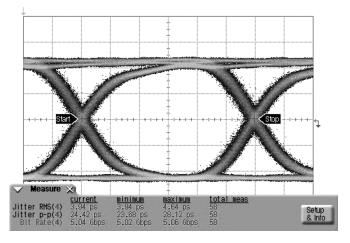

Fig. 6. Measured 5 Gb/s eye diagram with  $2^{31}-1$  PRBS input. (X-axis: 33.3 ps/div, Y-axis: 100 mV/div, Jitter(pp) = 24.42 ps).

input-referred noise current  ${\cal I}_N$  of the optical receiver is derived from its sensitivity performance. As

Sensitivity

$$\approx 10 \log \left[ \frac{14.1 I_N(r_e+1)}{2\rho(r_e-1)} 1000 \right] dBm$$

(20)

where  $\rho$  is the responsivity of the photodetector, and  $r_e$  is the extinction ratio. The corresponding  $I_N$  is about 6.68  $\mu$ A<sub>rms</sub>.

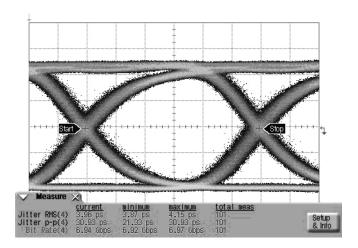

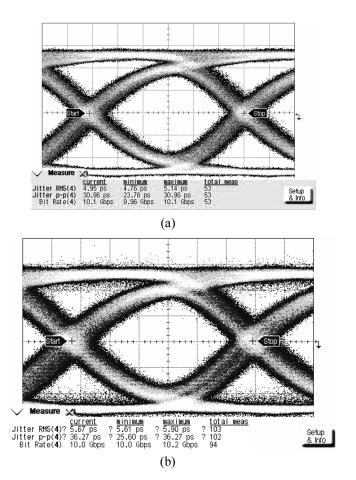

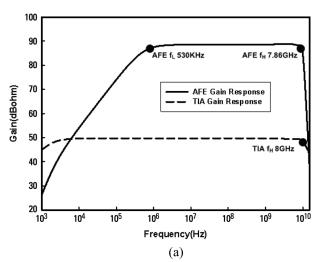

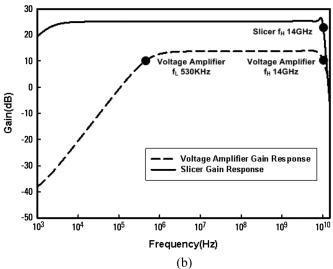

Fig. 6 and Fig. 7 illustrate the measured eye diagrams at 5 and 7 Gb/s, respectively, at sensitivity level. The data jitter is about 3.94  $ps_{rms}$  (24.4  $ps_{pp}$ ) and 3.96  $ps_{rms}$  (30.9  $ps_{pp}$ ). Fig. 8(a) illustrates the measured 10 Gb/s eye diagram at the input power of sensitivity level (-13 dBm), and Fig. 8(b) illustrates the measured 10 Gb/s eye diagram when the input power is overloaded. The measured jitters are about 4.95  $ps_{rms}$  (30.96  $ps_{pp}$ ) and 5.67  $ps_{rms}$  (36.27  $ps_{pp}$ ). Fig. 9(a) illustrates the simulated conversion gain of the receiver AFE and the TIA, and the frequency response of the PA, including the voltage amplifier and the slicer, is shown in Fig. 9(b).

In summary, the receiver front-end provides a conversion gain of 90 dB $\Omega$ , among which 50 dB $\Omega$  is provided by the TIA. It is capable of delivering 900 mV $_{\rm pp}$  differential voltage swings to 50  $\Omega$  output loads directly. The  $f_{H-3}$  dB is about 7.86 GHz,

Fig. 7. Measured 7 Gb/s eye diagram with  $2^{31}-1$  PRBS input. (X-axis: 24 ps/div, Y-axis: 97.3 mV/div, Jitter(pp) = 30.93 ps).

Fig. 8. Measured 10 Gb/s eye diagram with  $2^{31} - 1$  PRBS input. (a) Input power = -13 dBm. (b) Input power = 0 dBm (X-axis: 16 ps/div, Y-axis: 100 mV/div).

which is limited by the transimpedance amplifier. The PA exhibits a conversion gain of 40 dB. The voltage amplifier provides a 16-dB conversion gain to fully switch the slicer. As a tapered buffer, the slicing stage further provides 24-dB voltage gain. The tolerated power level is up to 0 dBm by the built in automatic gain control scheme. Operating under a 1.8-V supply,

Fig. 9. (a) Simulated frequency response of the optical receiver analog frontend. (b) Simulated frequency response of the post voltage amplifier.

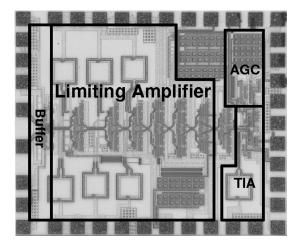

Fig. 10. Chip photograph.

the power dissipation is 199 mW, among which 35 mW is consumed by the output buffer. Fig. 10 illustrates the chip photo. Fabricated in a 0.18- $\mu$ m CMOS technology, the chip size is 1300  $\mu$ m  $\times$  1566  $\mu$ m.

|                    | This work              | [1]<br>02' RFIC                         | [2]<br>03' ISSCC | [3]<br>02' ESSCIRC | [7]<br>05' JSSC           | [16]<br>00' JSSC | [18]<br>04' ISSCC |

|--------------------|------------------------|-----------------------------------------|------------------|--------------------|---------------------------|------------------|-------------------|

| Function           | TIA+AGC+LA single chip | TIA and LA chip sets                    | LA               | TIA                | TIA+AGC+LA<br>Single chip | LA               | Amplifier         |

| Power              | 199 mW<br>(1.8V)       | TIA 108 mW<br>LA 360mW<br>(1.8V)        | 150 mW<br>(1.8V) | 137.5 mW<br>(2.5V) | 210 mW<br>(1.8V)          | 53mW<br>(2.5V)   | 190mW<br>(2.2V)   |

| CMOS<br>Process    | 0.18 μm                | 0.18 μm                                 | 0.18 μm          | 0.18 μm            | 0.18 μm                   | 0.25 μm          | 0.18 μm           |

| Inductor<br>Counts | 7                      | N.A.                                    | 24               | 2                  | 9                         | 0                | 20                |

| GBW                | 248.5 THz-Ω            | (TIA)<br>11.7 THz-Ω<br>(LA)<br>1.19 THz | 2.97 THz         | 4.6 THz-Ω          | 135 THz-Ω                 | 0.119 THz        | 0.123 THz         |

TABLE I PERFORMANCE BENCHMARK

#### VI. CONCLUSION

This paper describes the design of a 10-Gb/s optical receiver analog front-end in a generic 0.18- $\mu$ m CMOS technology. The optical AFE provides a conversion gain of 90 dB $\Omega$  and a -3 dB bandwidth of about 7.86 GHz, which is limited by the transimpedance amplifier. A regulated cascode input stage is utilized to decouple the loading effect at the input node, and wide bandwidth is achieved by means of shunt feedback and inductive peaking. The PA is composed of a preamplification stage followed by a slicing stage. In contrast to a conventional limiting amplifier which consists of identical gain cells, the GBW requirements in the proposed topology are much relaxed, thus, both peaking inductors and power consumption can be saved. Moreover, an AGC is built in to alleviate overload induced data jitter. Instead of using bulky planar inductors or two asymmetric 3-D inductors, a novel fully symmetric 3-D transformer for inductive peaking is utilized in this design to save chip area. A distributed capacitance model of the 3-D transformer is also proposed. The superiority of the proposed transformer over conventional planar counterpart is demonstrated.

The performance benchmark of this paper, our previous work in [7], and the prior art of TIA and limiting amplifiers [1]–[3], [7], [16], [18] is summarized in Table I. By a single chip integration, gain-bandwidth requirement for the individual building blocks can be rearranged and further optimized. The proposed prototype is power efficient, manifests a GBW as high as 248.5 THz- $\Omega$ , while fewer peaking inductors are required.

### ACKNOWLEDGMENT

The authors would like to thank the Chip Implementation Center for chip fabrication.

## REFERENCES

[1] A. K. Petersen et al., "Front-end CMOS chipset for 10 Gb/s communication," in *IEEE RFIC Symp. Dig. Tech. Papers*, 2002, pp. 93–96.

- [2] S. Galal and B. Razavi, "10 Gb/s limiting amplifier and laser/modulator driver in 0.18 μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2003.

- [3] B. Analui and A. Hajimiri, "Multi-pole bandwidth enhancement technique for transimpedance amplifiers," in *Proc. Eur. Solid-State Circuits Conf.*, 2002, pp. 303–306.

- [4] W.-Z. Chen and W.-H. Chen, "Symmetric 3D passive components for RF ICs application," in *IEEE RFIC Symp. Dig. Tech. Papers*, 2003, pp. 599–602

- [5] S. M. Park and H.-J. Yoo, "1.25 Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications," *IEEE J. Solid-State Circuits*, pp. 112–121, Jan. 2004.

- [6] W.-Z. Chen and C.-H. Lu, "Design and analysis of A 2.5 Gbps optical receiver analog front-end in a 0.35 μm digital CMOS technology," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 5, pp. 977–983, May 2006.

- [7] W.-Z. Chen, Y.-L. Cheng, and D.-S. Lin, "A 1.8 V, 10 Gbps fully integrated CMOS optical receiver analog front end," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1388–1396, Jun. 2005.

- [8] B. Razavi, Design of Integrated Circuits for Optical Communications. New York: McGraw-Hill, 2003.

- [9] S. S. Mohan, M. Hershenson, S. P. Boyd, and T. H. Lee, "Bandwidth extension in CMOS with optimized on-chip inductors," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 346–355, Mar. 2000.

- [10] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol., no., pp. 1368–1382, Sep. 2000.

- [11] A. Zolfaghari, A. Chan, and B. Razavi, "Stacked inductors and transformers in CMOS technology," *IEEE J. Solid-State Circuits*, vol., no. 4, pp. 620–628, Apr. 2001.

- [12] C.-C. Tang, C.-H. Wu, and S.-I. Liu, "Miniature 3-D inductors in standard CMOS process," *IEEE J. Solid-State Circuits*, vol., no. 4, pp. 471–480, Apr. 2002.

- [13] C.-H. Wu, C.-C. Tang, and S.-I. Liu, "Analysis of on-chip spiral inductors using the distributed capacitance model," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1040–1044, Jun. 2003.

- [14] M. Danesh, J. R. Long, R. A. Hadaway, and D. L. Harame, "A Q-factor enhancement technique for MMIC inductors," in *Dig. IEEE Radio Freq. Integr. Circuits Symp.*, 1998, pp. 217–220.

- [15] M. A. T. Sanduleanu and P. Manteman, "A low noise, wide dynamic range, tranimpedance amplifier with automatic gain control for SDH/ SONET (STM16/OC48) in a 30 GHz fT BiCMOS process," in *Proc. Eur. Solid-State Circuits Conf.*, 2001, pp. 208–211.

- [16] E. Sackinger and W. C. Fischer, "A 3-GHz 32 dB CMOS limiting amplifier for SONET OC-48 receivers," *IEEE J. Solid-State Circuits*, pp. 1884–1888, 2000.

- [17] E. M. Cherry and D. E. Hooper, "The design of wide-band transistor feedback amplifier," *Inst. Elec. Eng. Proc.*, vol. 110, no. 2, pp. 375–389, Feb. 1963.

- [18] S. Galal and B. Razavi, "40 Gb/s amplifier and ESD protection circuit in 0.18 μm CMOS technology," in *IEEE ISSCC Dig. Tech. Papers*, 2004, pp. 480–481.

**Wei-Zen Chen** (M'99) received the B.S., M.S., and Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsin-Chu, Taiwan, R.O.C., in 1992, 1994, and 1999, respectively.

After graduation, he was with the Industrial Technology Research Institute (ITRI), Hsin-Chu, Taiwan, working on RF integrated circuit design. Since 2002, he has been with the Department of Electronics Engineering, National Chiao-Tung University, where he is currently an Associate Professor. From 1999 to 2002, he was with the Department of Electrical

Engineering, National Central University, Chung-Li, Taiwan. His research interests include integrated circuits and systems for high speed networks and wireless communications.

Dr. Chen is a member of Phi-Tau-Phi.

**Da-Shin Lin** was born in Changhua, Taiwan, R.O.C., in 1976. He received the B.S. degree in mechanical engineering from National Central University, Chung-Li, Taiwan, in 2001, and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Hsin-Chu, Taiwan, in 2004.

Currently, he is an Engineer with the R&D Division, MediaTek, Inc., Hsin-Chu, Taiwan. His research interests include CMOS optical receiver design.