# High-Temperature Stable $Ir_x$ Si Gates With High Work Function on HfSiON p-MOSFETs

B. F. Hung, C. H. Wu, Albert Chin, *Senior Member, IEEE*, S. J. Wang, F. Y. Yen, Y. T. Hou, *Member, IEEE*, Y. Jin, H. J. Tao, Shih C. Chen, *Member, IEEE*, and Mong-Song Liang, *Fellow, IEEE*

Abstract—A novel 1000 °C-stable Ir<sub>x</sub>Si gate on HfSiON is shown for the first time with full process compatibility to current very-large-scale-integration fabrication lines and proper effective work function of 4.95 eV at 1.6-nm equivalent-oxide thickness. In addition, small threshold voltages and good hole mobilities are measured in Ir<sub>x</sub>Si/HfSiON transistors. The 1000 °C thermal stability above pure metal (900 °C only) is due to the inserted 5-nm amorphous Si, which also gives less Fermi-level pinning by the accumulated metallic full silicidation at the interface.

Index Terms—Full silicidation (FUSI), HfSiON, Ir<sub>x</sub>Si.

#### I. INTRODUCTION

O CONTINUE down-scaling very-large-scale-integration (VLSI) technology and increase the integration density, high- $\kappa$  gate dielectrics are needed for MOSFETs to reduce the large dc power consumption from gate leakage current [1]–[10]. In addition, metal gates are required to eliminate poly gate depletion. However, metal-gate/high- $\kappa$  CMOSFETs show undesired high threshold voltages  $(V_t)$ , which is opposite to the VLSI scaling trend. This phenomenon is known as "Fermilevel pinning" [1], although the background physics may be attributed to interface dipole and/or charged defects [1], [8]. To compensate this Fermi-level pinning effect, high-work-function metal electrodes larger than the 5.2 eV of  $p^+$  poly-Si are needed. However, only Ir (5.27 eV) and Pt (5.65 eV) in the Periodic Table [11] can meet this requirement, which make the metal-gate/high- $\kappa$  p-MOSFETs especially challenging [1], [2]. Ir is more preferable than Pt due to a simpler etching process by reactive ion etching [12], [13]. Unfortunately, large metal diffusion through high- $\kappa$  dielectrics was found in pure Ir gates after 1000 °C rapid thermal annealing (RTA), which caused p-MOS device failures [7], [8]. Previous attempts by using Ir-N to improve the thermal stability also failed due to weak Ir-N bonding strengths, where Ir-N decomposition and penetrating

Manuscript received March 28, 2006; revised October 23, 2006. This work was supported in part by NSC(94-2215-E-009-062) of Taiwan. The review of this paper was arranged by Editor T. Skotnicki.

B. F. Hung and A. Chin are with the Nano Science and Technology Center, Department of Electronics Engineering, National Chiao-Tung University, University System of Taiwan, Hsinchu 300, Taiwan, R.O.C. (e-mail: achin@ cc.nctu.edu.tw).

C. H. Wu and S. J. Wang are with the Institute of Microelectronics, Department of Electrical Engineering, National Cheng Kung University, Tainan 701, Taiwan, R.O.C.

F. Y. Yen, Y. T. Hou, Y. Jin, H. J. Tao, S. C. Chen, and M.-S. Liang are with the Taiwan Semiconductor Manufacturing Corporation, Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2006.888626

high- $\kappa$  dielectrics were found after high-temperature RTA [8]. Another possibility is using low-temperature full silicidation (FUSI) gates [3]–[9]. However, the p-MOS devices incorporating high work function Pt<sub>x</sub>Si or Ir<sub>x</sub>Si still failed to integrate into the CMOS SALICIDE process due to the lack of required selective wet etching of Pt or Ir during SALICIDE.

To overcome this problem, we have proposed and demonstrated a new high-temperature stable Ir<sub>x</sub>Si FUSI gate on high- $\kappa$  HfSiON. This is different from the low-temperature FUSI process [3]-[6] since it is formed first before ion implantation and undergoes 1000 °C RTA thermal cycle for implant activation. To achieve this high-temperature stability goal, additional Si was inserted between Ir and high- $\kappa$  HfSiON, where less Fermi-level pinning was obtained by forming Ir-rich Ir<sub>x</sub>Si gates. High- $\kappa$  HfSiON also has good metaldiffusion barrier property [14], [15], which is similar to our previous HfAlON [7], [8], but it has the important advantage of better compatibility with currently used SiON gate dielectric with added Hf for higher  $\kappa$  value. After 1000 °C RTA, Ir<sub>x</sub>Si/HfSiON p-MOSFETs show good device integrity of a high effective work function  $(\phi_{m-eff})$  of 4.95 eV, a small  $V_t$  of -0.15 V, and a peak hole mobility of 84 cm<sup>2</sup>/V · s. These results are compatible with and even better than the best reported metal-gate/high- $\kappa$  p-MOSFETs [5]–[9].

## II. EXPERIMENTAL PROCEDURE

The gate-first Ir<sub>x</sub>Si/HfSiON p-MOSFETs were fabricated on 12-in N-type Si wafers with resistivity of 1–10  $\Omega \cdot cm$ . After RCA cleaning, 4-nm HfSiO dielectric (Hf/(Hf + Si) = 50%) was deposited by atomic-layer deposition. HfSiON gate dielectric was formed by applying NH<sub>3</sub> plasma surface nitridation on HfSiO [16]. After postdeposition annealing, 5-30-nm amorphous Si and 20-30-nm Ir were deposited by physical vapor deposition (PVD) [7]. For Ir/Si/HfSiON capacitors, a 1000 °C RTA was applied for 10 s to form  $Ir_xSi$  gates. For MOSFETs, additional 400-nm Si was deposited on top of Ir/Si to avoid ion implantation penetrating through the thin Ir/Si. After gate definition, Boron was implanted at 25-KeV energy and  $5 \times 10^{15}$  cm<sup>-2</sup> dose, and activated at 1000 °C RTA for 10 s. Meanwhile, Ir<sub>x</sub>Si was also formed during RTA, where the x = 3 was determined by X-ray diffraction measurements. Note that this process is different from the low-temperature FUSI process [3]–[6], and such a simple self-aligned process is fully compatible to current VLSI lines. Secondary ion-mass spectroscopy (SIMS) was measured to study the Ir distribution profile. The fabricated p-MOSFETs were further characterized

Ir\_Si(20/5nm) gate @ 1000°C 10s RTA 20 **Capacitance (fF/μm²**) 2 01 51 05 2 21 05 r gate @ 900°C 10s RTA Al gate reference 20/5nm) gate pMOSFF1 5 0 -0.5 2.0 -1.0 0.0 0.5 1.0 1.5 Voltage (V)

Ir<sub>x</sub>Si(30/30nm) gate @ 1000°C 10s RTA Ir Si(20/10nm) gate @ 1000°C 10s RTA

Fig. 1.  $C{-}V$  characteristics of HfSiON/n-Si with Ir\_xSi-, Ir-, and Al-gate capacitors. The device areas are 100  $\times$  100  $\mu m.$

by capacitance–voltage (C-V) and current–voltage (I-V) measurements. For comparison, Al and Ir-gated MOS capacitors on HfSiON were also fabricated. To prevent the different oxide charge from causing error in  $\phi_{\text{m-eff}}$  extraction, HfSiON was subjected to the same thermal cycle (1000 °C RTA for 10 s) before Al gate deposition.

# **III. RESULTS AND DISCUSSION**

Fig. 1 shows the measured C-V characteristics of  $Ir_xSi$ , Ir, and Al gates on HfSiON MOS devices. Low-temperature Al-gated HfSiON capacitors were used as a reference because pure metal deposited at low temperature has little interface reaction with high- $\kappa$  dielectrics to cause Fermi-level pinning [10]. In addition, the flatband voltage ( $V_{\rm fb}$ ) is expressed as

$$V_{\rm fb} = \phi_{\rm ms} - Q_f / C_{\rm ox}$$

=  $(\phi_m - \phi_s) - (Q_f / \varepsilon_o k_{\rm ox}) t_{\rm ox}$

=  $(\phi_m - \phi_s) - (Q_f / \varepsilon_o k_{\rm SiO2}) \text{EOT}$  (1)

where  $\phi_m$  and  $\phi_s$  are the work functions for metal gates and Si, respectively.  $Q_f$ ,  $C_{ox}$ ,  $t_{ox}$ , and equivalent-oxide thickness (EOT) are the oxide charge, capacitance, physical thickness, and EOT for high- $\kappa$  dielectrics, respectively. Since HfSiON has the same thermal cycle (1000 °C RTA for 10 s) before Al gate formation, the  $Q_f$  effect should be similar to FUSI gates. Therefore, the principal effect of  $V_{\rm fb}$  shift might be due to the difference of effective  $\phi_m$ . In comparing with the conventional  $\phi_{\rm m-eff}$  extraction from  $V_{\rm fb}$ - $t_{\rm ox}$  or  $V_{\rm fb}$ -EOT plot, this method uses a simple process without fabricating MOS devices with various  $t_{\rm ox}$  and measuring the thickness carefully by transmission electron microscopy (TEM). Since the capacitance value or EOT of  $\sim$ 1.6 nm is the same for various gated HfSiON capacitors, the shifts of C-V curves with different gate electrodes are attributed to the different work functions. Ir/HfSiON after 900 °C RTA has a large  $V_{\rm fb}$  shift of 1.15 V to control lowtemperature Al gates (4.1 eV  $\phi_{m-eff}$ ), which gives the required high  $\phi_{m-eff}$  of 5.25 eV. This work-function value is also close to the reported 5.27 eV for Ir [11], indicating no pinning effect in pure metal Ir gates. This is due to weak bonding strengths of Ir-O or Ir-N that reduce the Fermi-level-pinning-related interface reaction [8]. However, Ir/HfSiON capacitors failed after 1000 °C RTA. To improve thermal stability, additional

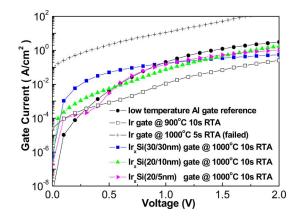

Fig. 2.  $J\!-\!V$  characteristics of HfSiON/n-Si with  $\mathrm{Ir}_x\mathrm{Si}$ -, Ir-, and Al-gate capacitors.

amorphous Si of 5-30 nm was inserted between Ir and HfSiON. Good C-V characteristics were measured for Ir<sub>x</sub>Si/HfSiON devices after the required 1000 °C RTA for implant activation, although thermal stability was traded off at the Fermi-level pinning caused by the Si/HfSiON interface reaction. However, the continuously increasing  $V_{\rm fb}$  toward the value of pure Ir gates was observed by decreasing the inserted amorphous Si layer, and a high  $\phi_{\text{m-eff}}$  of 4.95 eV was obtained for Ir<sub>x</sub>Si/HfSiON devices with the inserted 5-nm amorphous Si. This 4.95 eV  $\phi_{\text{m-eff}}$  is significantly larger than Ni<sub>3</sub>Si/HfSiON [6]. This result is also slightly better than previous  $Ir_xSi/HfAION$  [7] due to thinner amorphous Si on high- $\kappa$  dielectrics. Slow depletion for  $Ir_x$ Si/HfSiON devices with 30-nm amorphous Si may be due to nonuniform silicidation as examined by TEM, where locally unreacted Si was found to cause voltage drop in gate electrodes. The formation of FUSI gates is evident from the same inversion and accumulation capacitances measured in MOSFETs.

Fig. 2 shows the J-V characteristics of  $Ir_xSi$ , Ir, and Al gates on high- $\kappa$  HfSiON devices. After 1000 °C RTA, Ir/HfSiON devices failed due to large leakage current. In sharp contrast,  $Ir_xSi$  gates on HfSiON showed successfully improved thermal stability to 1000 °C RTA, which is evident from low leakage current comparable with p<sup>+</sup> poly-Si gates [17]. Here, hightemperature thermal cycle is required for dopant activation after ion implantation.

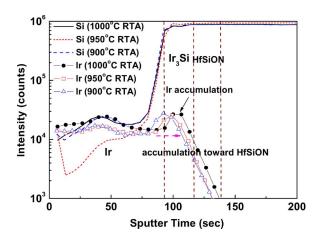

The measured large  $V_{\rm fb}$  shift of Ir<sub>x</sub>Si is supported by SIMS profile, as shown in Fig. 3. Here, Ir segregation toward amorphous Si was measured to form  $Ir_xSi$  on HfSiON surface. Such FUSI formation directly on high- $\kappa$  dielectrics is known to reduce Fermi-level pinning [6]–[8]. Therefore, good thermal stability of 1000 °C RTA, a reasonable high  $\phi_{\text{m-eff}}$  of 4.95 eV, and a low gate dielectric leakage current can be simultaneously achieved in Ir<sub>x</sub>Si/HfSiON MOS capacitors. To the best of our knowledge, this is the highest reported  $\phi_{m-eff}$  in high- $\kappa$  Hfbased oxide [5]-[8]. These are the few methods to achieve a high  $\phi_{m-eff}$  in Hf-based oxide p-MOS devices. Although the  $V_{\rm fb}$  tuning can be reached by impurity segregation in FUSI/SiON, this method becomes less useful in high- $\kappa$  metal oxide due to the stronger interface reaction. In the following, we will study Ir<sub>x</sub>Si/HfSiON devices with the thinnest 5-nm amorphous Si. This is because the  $V_{\rm fb}$  of thicker Si layer is too low for p-MOSFET application.

25

Fig. 3. SIMS profile of  $Ir_3Si$  gates on HfSiON at different RTA temperatures. The  $Ir_3Si$  that accumulated toward HfSiON interface is found to unpin the Fermi level.

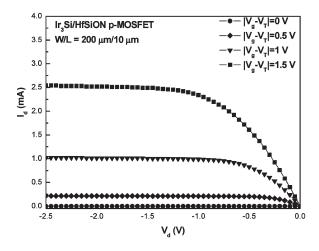

Fig. 4.  $I_d$ - $V_d$  characteristics of Ir<sub>3</sub>Si/HfSiON p-MOSFETs.

Fig. 4 shows the transistor  $I_d-V_d$  characteristics as a function of  $V_g-V_t$  for 1000 °C RTA Ir<sub>x</sub>Si/HfSiON p-MOSFETs. The well-behaved  $I_d-V_d$  curves of Ir<sub>x</sub>Si/HfSiON transistors show little device performance degradation.

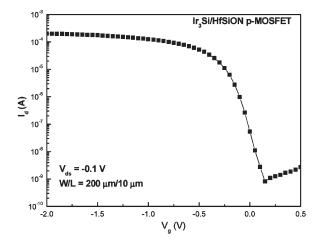

Fig. 5 shows the  $I_d-V_g$  characteristics of  $Ir_x$ Si-gated p-MOSFETs with HfSiON as the gate dielectric. A small  $V_t$  as low as -0.15 V is obtained from the linear  $I_d-V_g$  plot, which is consistent with the large  $\phi_{\text{m-eff}}$  of 4.95 eV from C-V curves and the Ir accumulation on HfSiON from SIMS.

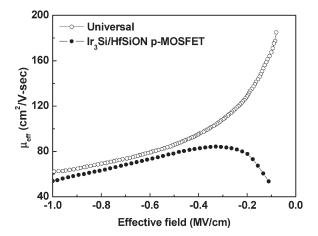

Fig. 6 shows the extracted hole mobilities versus gate electric fields from the measured  $I_d-V_g$  data of  $Ir_xSi/HfSiON$  p-MOSFETs. High hole mobilities of 84 and 53 cm<sup>2</sup>/V · s are obtained at peak value and 1 MV/cm effective field for  $Ir_xSi/HfSiON$  p-MOSFETs, respectively, which is compatible with the published data in the literature [5]–[8]. Good hole mobilities also indicate low Ir diffusion through HfSiON to inversion channel, even though excess Ir is necessary to prevent unreacted amorphous Si from causing gate depletion or increased Fermi-level pinning. Therefore, a high  $\phi_{m-eff}$ , a small  $V_t$ , and good hole mobilities are simultaneously achieved in  $Ir_xSi/HfSiON$  p-MOSFETs with additional merit of process compatible to current VLSI lines.

Fig. 5.  $I_d-V_g$  characteristics of Ir<sub>3</sub>Si/HfSiON p-MOSFETs.

Fig. 6. Extracted hole mobilities from  $I_d$ - $V_g$  characteristics of Ir<sub>3</sub>Si/HfSiON p-MOSFETs.

## **IV. CONCLUSION**

Good device performance of Ir<sub>x</sub>Si/HfSiON p-MOSFETs is shown by a high  $\phi_{m-eff}$  of 4.95 eV, a small  $V_t$  of -0.15 V, a peak hole mobility of 84 cm<sup>2</sup>/V · s, and 1000 °C RTA thermal stability with the advantage of full process compatible to current VLSI lines.

# ACKNOWLEDGMENT

The authors at National Chiao-Tung University would like to thank Prof. R. N. Kwo, M. H. Hong, and H. L. Hwang at National Tsing Hua University for their help.

#### REFERENCES

- J. K. Schaeffer, C. Capasso, L. R. C. Fonseca, S. Samavedam, D. C. Gilmer, Y. Liang, S. Kalpat, B. Adetutu, H.-H. Tseng, Y. Shiho, A. Demkov, R. Hegde, W. J. Taylor, R. Gregory, J. Jiang, E. Luckowski, M. V. Raymond, K. Moore, D. Triyoso, D. Roan, B. E. White, Jr., and P. J. Tobin, "Challenges for the integration of metal gate electrodes," in *IEDM Tech. Dig.*, 2004, pp. 287–290.

- [2] H.-H. Tseng, C. C. Capasso, J. K. Schaeffer, E. A. Hebert, P. J. Tobin, D. C. Gilmer, D. Triyoso, M. E. Ramón, S. Kalpat, E. Luckowski, W. J. Taylor, Y. Jeon, O. Adetutu, R. I. Hegde, R. Noble, M. Jahanbani, C. El Chemali, and B. E. White, "Improved short channel device

characteristics with stress relieved pre-oxide (SRPO) and a novel tantalum carbon alloy metal gate/HfO<sub>2</sub> stack," in *IEDM Tech. Dig.*, 2004, pp. 821–824.

- [3] B. Tavel, T. Skotnicki, G. Pares, N. Carrière, M. Rivoire, F. Leverd, C. Julien, J. Torres, and R. Pantel, "Totally silicided (CoSi<sub>2</sub>) polysilicon: A novel approach to very low-resistive gate (~2Ω/□) without metal CMP nor etching," in *IEDM Tech. Dig.*, 2001, pp. 815–828.

- [4] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goollgweon, and M. R. Lin, "Transistors with dual work function metal gate by single full silicidation (FUSI) of polysilicon gates," in *IEDM Tech. Dig.*, 2002, pp. 367–370.

- [5] T. Nabatame, M. Kadoshima, K. Iwamoto, N. Mise, S. Migita, M. Ohno, H. Ota, N. Yasuda, A. Ogawa, K. Tominaga, H. Satake, and A. Toriumi, "Partial silicides technology for tunable work function electrodes on high-κ gate dielectrics- fermi level pinning controlled PtSi<sub>x</sub> for HfO<sub>x</sub>(N) pMOSFET," in *IEDM Tech. Dig.*, 2004, pp. 83–86.

- [6] K. Takahashi, K. Manabe, T. Ikarashi, N. Ikarashi, T. Hase, T. Yoshihara, H. Watanabe, T. Tatsumi, and Y. Mochizuki, "Dual workfunction Ni-silicide/HfSiON gate stacks by phase-controlled full-silicidation (PC-FUSI) technique for 45 nm-node LSTP and LOP devices," in *IEDM Tech. Dig.*, 2004, pp. 91–94.

- [7] C. H. Wu, D. S. Yu, A. Chin, S. J. Wang, M.-F. Li, C. Zhu, B. F. Hung, and S. P. McAlister, "High work function Ir<sub>x</sub>Si gates on HfAlON p-MOSFETs," *IEEE Electron Device Lett.*, vol. 27, no. 2, pp. 90–92, Feb. 2006.

- [8] D. S. Yu, A. Chin, C. H. Wu, M.-F. Li, C. Zhu, S. J. Wang, W. J. Yoo, B. F. Hung, and S. P. McAlister, "Lanthanide and Ir-based dual metalgate/HfAION CMOS with large work-function difference," in *IEDM Tech. Dig.*, 2005, pp. 649–652.

- [9] C. H. Huang, D. S. Yu, A. Chin, W. J. Chen, C. X. Zhu, M.-F. Li, B. J. Cho, and D. L. Kwong, "Fully silicided NiSi and germanided NiGe dual gates on SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Ge-on-insulator MOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 319–322.

- [10] M. Koyama, Y. Kamimuta, T. Ino, A. Kaneko, S. Inumiya, K. Eguchi, M. Takayanagi, and A. Nishiyama, "Careful examination on the asymmetric Vfb shift problem for Poly-Si/HfSiON gate stack and its solution by the Hf concentration control in the dielectric near the Poly-Si interface with small EOT expense," in *IEDM Tech. Dig.*, 2004, pp. 499–502.

- [11] H. B. Michaelson, "The work function of the elements and its periodicity," J. Appl. Phys., vol. 48, no. 11, pp. 4729–4733, Nov. 1977.

- [12] C. H. Lai, A. Chin, K. C. Chiang, W. J. Yoo, C. F. Cheng, S. P. McAlister, C. C. Chi, and P. Wu, "Novel SiO<sub>2</sub>/AlN/HfAlO/IrO<sub>2</sub> memory with fast erase, large ΔV<sub>th</sub> and good retention," in VLSI Symp. Tech. Dig., 2005, pp. 210–211.

- [13] K. C. Chiang, A. Chin, C. H. Lai, W. J. Chen, C. F. Cheng, B. F. Hung, and C. C. Liao, "Very high-k and high density TiTaO MIM capacitors for analog and RF applications," in VLSI Symp. Tech. Dig., 2005, pp. 62–63.

- [14] C. C. Liao, C. F. Cheng, D. S. Yu, and A. Chin, "The copper contamination effect on Al<sub>2</sub>O<sub>3</sub> gate dielectric on Si," *J. Electrochem. Soc.*, vol. 151, no. 10, pp. G693–G696, Oct. 2004.

- [15] Y. H. Lin, F. M. Pan, Y. C. Liao, Y. C. Chen, I. J. Hsieh, and A. Chin, "The Cu contamination effect in oxynitride gate dielectrics," *J. Electrochem. Soc.*, vol. 148, no. 11, pp. G627–G629, Nov. 2001.

- [16] Y. T. Hou, F. Y. Yen, P. F. Hsu, V. S. Chang, P. S. Lim, C. L. Hung, L. G. Yao, J. C. Jiang, H. J. Lin, Y. Jin, S. M. Jang, H. J. Tao, S. C. Chen, and M. S. Liang, "High performance tantalum carbide metal gate stacks for nMOSFET application," in *IEDM Tech. Dig.*, 2005, pp. 35–39.

- [17] A. L. P. Rotondaro, M. R. Visokay, J. J. Chambers, A. Shanware, R. Khamankar, H. Bu, R. T. Laaksonen, L. Tsung, M. Douglas, R. Kuan, M. J. Bevan, T. Grider, J. Mcpherson, and L. Colombo, "Advanced CMOS transistors with a novel HfSiON gate dielectric," in *VLSI Symp. Tech. Dig.*, 2002, pp. 148–149.

His current research interests include the high- $\kappa$ / metal gate materials for CMOS Device applications. He is currently with the Institute of Microelectronics, Department of Electrical Engineering, National Cheng Kung University.

**Albert Chin** (SM'94) received the Ph.D. degree from the Department of Electrical Engineering, University of Michigan, Ann Arbor, in 1989.

He was with the AT&T-Bell Labs from 1989 to 1990, General Electric–Electronic Lab from 1990 to 1992, and visited Texas Instruments' Semiconductor Process and Device Center (SPDC) from 1996 to 1997. He is currently a Professor with the Nano Science and Technology Center, Department of Electronics Engineering, National Chiao-Tung University, University System of Taiwan, Hsinchu, Taiwan,

R.O.C., and a Visiting Professor at Silicon Nano Device Lab, National University of Singapore. He has published more than 300 technical papers and presentations. His research interests include Si VLSI, RF, and III-V devices. He is a pioneer in high- $\kappa$  gate dielectric and metal-gate research (Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, LaAlO<sub>3</sub>, and HfLaON with NiGe, YbSi<sub>2</sub>, and Ir<sub>3</sub>Si metal gates) for low dc power consumption CMOS, which result in largely improved dc leakage current in CMOS technology. He invented the Ge-On-Insulator (GOI) CMOS to enhance the mobility, three-dimensional IC to solve the ac power consumption, and able to extend the VLSI scaling, resonant cavity photo-detector for high gain-bandwidth product, and high-mobility strain-compensated HEMT. He is also the pioneer in high- $\kappa$  trapping layer research (Al(Ga)N and HfON) for MONOS nonvolatile memory, where  $100-\mu s$  fast program/erase speed, large memory window, and good retention are simultaneously achieved at record low  $< \pm 5$  V write for SoC. The high- $\kappa$  TiTaO and STO MIM he developed with  $k = 45 \sim 170$  can meet ITRS requirement of analog capacitor to year 2018. He also developed the high-performance RF passive devices on VLSIstandard Si substrate using ion implantation to convert into semi-insulating; much-improved RF device performance close to GaAs has been realized up to 100 GHz. The developed metal-gate/high- $\kappa$ /[Si or GOI] MOSFETs, MONOS memory, high-density MIM capacitor, and RF devices on process converted semi-insulating Si are followed by research labs universities worldwide and in pilot runs at IC fabs. He is currently working on metal-gate/high- $\kappa$  nano-CMOS, quantum-trap nanomemory, very high-density MIM DRAM capacitor, and RF Si technologies.

Dr. Chin has given invited talks at the IEEE International Electron Devices Meeting (IEDM) and other conferences in the U.S., Europe, Japan, Korea (i.e., Samsung Electronics), etc. He also served as a committee member in IEDM.

**S. J. Wang** received the Ph.D. degree from the Department of Electrical Engineering, National Cheng Kung University, Tainan, Taiwan, R.O.C., in 1985.

He was a Visiting Researcher with the Department of Electrical Engineering, UCLA, USA, from 1990 to 1991, and with the Department of Electrical and Electronic Engineering, Kyoto University, Japan, from 1995 to 1996. He is currently a Professor with the Department of Electrical Engineering, National Cheng Kung University. His research interests include microelectronics, semiconductor device

physics and simulation, SiGe MBE growth, quantum device design and development SiC epitaxy, high-power device high power, and high luminance LED.

**B. F. Hung** received the B.S. degree in electrical engineering from National Tsing Hua University, Hsinchu, Taiwan, R.O.C., in 2001, and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, in 2003, where he is currently working toward the Ph.D. degree.

His current research interest is in the high- $\kappa$ /metal gate CMOS devices. He is currently with the Nano Science and Technology Center, Department of Electronics Engineering, National Chiao-Tung University, University System of Taiwan.

**Y. T. Hou** (S'02–M'04) received the B.S. and M.S. degrees in physics from Peking University, Beijing, China, in 1990 and 1993, respectively, and the Ph.D. degree in electrical engineering from Silicon Nano Device Lab, National University of Singapore, Singapore, in 2004.

Currently, he is with the Logic Technology Platform I, R&D of Taiwan Semiconductor Manufacturing Corporation (TSMC), Science-Based Industrial Park, Hsinchu, Taiwan, R.O.C., on module technology development of metal gate high- $\kappa$  gate stacks.

Y. Jin, photograph and biography not available at the time of publication.

H. J. Tao, photograph and biography not available at the time of publication.

Shih C. Chen (M'97), photograph and biography not available at the time of publication.

**Mong-Song Liang** (F'06), photograph and biography not available at the time of publication.