# Fabrication of 0.15- $\mu$ m $\Gamma$ -Shaped Gate $In_{0.52}Al_{0.48}As/In_{0.6}Ga_{0.4}As$ Metamorphic HEMTs Using DUV Lithography and Tilt Dry-Etching Technique

Yi-Chung Lien, Szu-Hung Chen, Edward Yi Chang, Senior Member, IEEE, Ching-Ting Lee, Senior Member, IEEE, Li-Hsin Chu, and Chia-Yuan Chang

Abstract—An  $In_{0.52}Al_{0.48}$ As/ $In_{0.6}Ga_{0.4}$ As metamorphic high-electron mobility transistor (MHEMT) with 0.15- $\mu$ m  $\Gamma$ -shaped gate using deep ultraviolet lithography and tilt dry-etching technique is demonstrated. The developed submicrometer gate technology is simple and of low cost as compared to the conventional E-beam lithography or other hybrid techniques. The gate length is controllable by adjusting the tilt angle during the dry-etching process. The fabricated 0.15- $\mu$ m  $In_{0.52}Al_{0.48}As/In_{0.6}Ga_{0.4}As$  MHEMT using this novel technique shows a saturated drain–source current of 680 mA/mm and a transconductance of 728 mS/mm. The  $f_T$  and  $f_{\rm max}$  of the MHEMT are 130 and 180 GHz, respectively. The developed technique is a promising low-cost alternative to the conventional submicrometer E-beam gate technology used for the fabrication for GaAs MHEMTs and monolithic microwave integrated circuits.

Index Terms—Deep ultraviolet (DUV) lithography, metamorphic high-electron mobility transistors (MHEMTs), tilt dryetching technique,  $\Gamma$ -shaped gate.

### I. INTRODUCTION

Arr OR HIGH-SPEED wireless communications, metamorphic high-electron mobility transistors (MHEMTs) have received much attention recently due to its capability of combining the advantages of a high-performance InP-based structure and a low-cost high-mechanical-strength GaAs substrate. MHEMTs with excellent high-frequency performance comparable to the InP-based HEMTs have also been demonstrated [1], [2]. MHEMTs have been considered as a cost-effective alternative to the conventional lattice-matched or pseudomorphic InAlAs/InGaAs/InP HEMTs (InP-HEMTs). The gain and noise characteristics of the MHEMTs at high frequencies are strongly dependent on gate length  $L_g$  and the gate resistance; therefore, T- or Γ-shaped gates with small footprint and wide

Manuscript received September 27, 2006; revised November 14, 2006. This work was supported by the National Science Council and the Ministry of Economic Affairs, Taiwan, R.O.C., under Contract NSC 95-2752-E-009-001-PAE and Contract 94-EC-17-A-05-S1-020. The review of this letter was arranged by Editor J. del Alamo.

Y.-C. Lien, S.-H. Chen, E. Y. Chang, L.-H. Chu, and C.-Y. Chang are with the Department of Materials Science and Engineering, National Chiao-Tung University, Hsinchu 30050, Taiwan, R.O.C. (e-mail: edc@mail.nctu.edu.tw).

C.-T. Lee is with Institute of Microelectronics, Department of Electrical Engineering, National Cheng-Kung University, Tainan 701, Taiwan, R.O.C.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2006.889049

tee-top are commonly used for HEMTs to maximize the device performance. A wide variety of lithography methods have been used for the fabrication of submicrometer gates with T,  $\Gamma$ , or Y shapes to improve device performance [3]–[5]. Fabrications of submicrometer gates using angle and angled-shadow evaporation processes have been reported [6], [7]. A multilayer deep ultraviolet (DUV) photoresist process has been used to obtain 0.2- $\mu$ m T-shaped gates [8]. A hybrid method using E-beam lithography and reflowed-resist technology to shrink the gate length down to 0.1  $\mu$ m was also demonstrated [9]. I-line lithography combined with a chemical shrinking process has shown the capability of fabricating 0.1- $\mu$ m-gate InP HEMTs [10]. However, tightly controlled process conditions, complicated process steps, or expensive E-beam lithography tools are required for these processes.

For cost-effective production of submicrometer MHEMTs, a 0.15- $\mu$ m  $\Gamma$ -shaped-gate MHEMT technology using DUV lithography and a tilt dry-etching technique was developed and demonstrated for the first time. The final gate length of the  $\Gamma$  gate was mainly controlled by the top photoresist opening, the total resist thickness, and the tilt angle for the anisotropic dry etching. Comparing with the previously reported gate fabrication techniques, the tilt dry-etching gate process is a relatively simple, inexpensive, and flexible process for the fabrication of submicrometer GaAs MHEMTs and monolithic microwave integrated circuits (MMICs) for high-frequency applications.

# II. EXPERIMENT

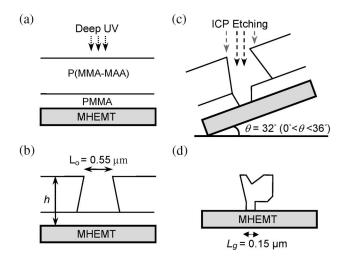

The MHEMT structure was grown on a (100) GaAs substrate by molecular beam epitaxy. The structure is given as follows: A 15-nm  $\rm In_{0.6}Ga_{0.4}As$  channel layer was grown on top of the InAlAs buffer layer. The top and bottom Si- $\delta$ -doping layers were separated from the channel layer by the upper and lower i-InAlAs spacers, respectively. The Schottky layer was a 15-nm-thick i-In\_{0.52}Al\_{0.48}As. The 15-nm-thick n-In\_{0.52}Ga\_{0.48}As cap  $(2\times 10^{18}~cm^{-3})$  layer was finally grown on the top. For the device fabrication, the mesa was done by wet etch, and the ohmic contacts were formed by evaporating Au/Ge/Ni/Au on the n-InGaAs cap layer and then alloyed at 300 °C to achieve a low contact resistance of 0.05  $\Omega$ mm. The process for fabricating the  $\Gamma$  gate is illustrated in Fig. 1. The bilayer resists consisting of the bottom 150-nm polymethyl

Fig. 1. DUV lithography and tilt dry-etching process steps for fabricating the submicrometer  $\Gamma$ -gate MHEMT. (a) DUV exposure. (b) Selective development of the top layer. (c) Tilt dry etching of the bottom layer. (d)  $\Gamma$ -gate profile after gate metal lift-off.

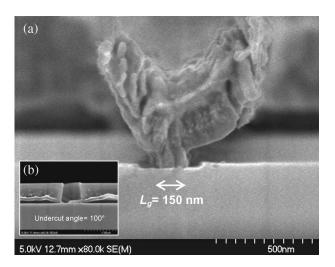

methacrylate (PMMA) and the top 600-nm PMMA-methacrylic acid [P(MMA-MAA)] were coated sequentially. In Fig. 1(a), the opening of 0.55  $\mu$ m on the top layer was defined by DUV( $\lambda = 254$  nm) exposure for 3 min using a contact aligner with a high-intensity light source. The exposure dose (1600 mJ/cm<sup>2</sup>) was carefully adjusted so that only the P(MMA-MAA) resist layer was opened. The selective development was realized easily due to the high sensitivity ratio of P(MMA-MAA) to PMMA ( $\sim$ 5:1). In Fig. 1(b), the undercut profile of the P(MMA-MAA) trench was due to the surface rate retardation during development. After the development, the wafer was tilted at an angle and was etched using inductive coupled plasma (ICP) ion etching with SF<sub>6</sub>/Ar etching gases. A low RF power of 50 W was applied to both the ICP source and the chuck to minimize the etch-induced damage for the underlying InGaAs layer. A set of tilt angles  $\theta$ , i.e.,  $0^{\circ}$ ,  $15^{\circ}$ , and  $32^{\circ}$ , was chosen to obtain the desired feature size in the bottom PMMA layer [Fig. 1(c)]. The optimum gas ratio  $SF_6$ : Ar = 1 : 1 was used to achieve highly anisotropic etching, and the etch rate of PMMA was 160 nm/min. After the tilt dry-etching process, gate recess was performed using a succinic acid/H<sub>2</sub>O<sub>2</sub>/NH<sub>4</sub>OH solution, and then, a Ti/Pt/Au gate metal was deposited. A lift-off process was performed after the gate metal deposition to form the 0.15- $\mu$ m  $\Gamma$  gate [Fig. 1(d)]. The cross-sectional scanning electron microscopy (SEM) images of the 0.15- $\mu$ m  $\Gamma$  gate and the resist profile just after the 32° tilt dry-etching process are shown in Fig. 2(a) and (b), respectively.

### III. RESULT AND DISCUSSION

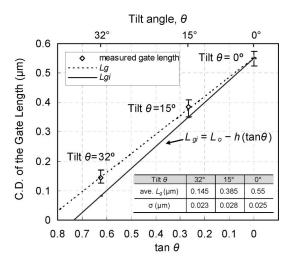

Fig. 3 shows the critical dimension (CD) of the measured gate length  $L_g$  as a function of the tangent of the tilt angle during the dry-etching process. The statistic data of the average gate length  $L_g$  and the standard deviation  $\sigma$  were estimated by using SEM observation. The data are shown in the inset table in Fig. 3. In this figure, the measured gate length  $L_g$  was decreased by increasing the dry-etching angle  $\theta$ . A line

Fig. 2. Cross-sectional SEM images of a (a) 0.15- $\mu$ m Ti/Pt/Au  $\Gamma$  gate and (b) resist profile after the tilt dry-etching process.

Fig. 3. CD of the measured gate length  $L_g$  and the ideal gate length  $L_{\rm gi}$  as a function of the tangent of tilt angle  $\theta$ .

of the predicted ideal gate length  $(L_{\rm gi} = L_o - h \times \tan \theta)$  was also plotted in the same figure for comparison.  $L_o$  (0.55  $\mu$ m) is the initial opening of the top P(MMA-MAA) layer, and the total resist thickness h is 0.75  $\mu$ m, as indicated in Fig. 1(b). There is a difference  $(\Delta L)$  between the  $L_{\rm gi}$  and the  $L_g$ .  $\Delta L$ increased with increasing tilt angle, which is due to the etching of the sidewall of the resist trench when the tilt angle is applied.  $\Delta L$  is about 0.06  $\mu m$  when  $\theta$  is 32°. The maximum allowed tilt angle is about  $\tan^{-1}(L_o/h) = 36^\circ$ . When  $\theta$  was increased to 32°, a gate length  $L_q$  of 0.15  $\mu$ m was achieved. This condition was applied for the MHEMT fabrication in this letter. In addition, the InGaAs cap layer exposed to the plasma was removed by the wet gate recess after the tilt dry etching. Therefore, the etch-induced damages had little influence on the device performance. This can be clearly seen from the electrical measurement data.

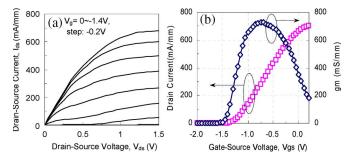

The drain-source current  $I_{\rm ds}$  versus drain-source voltage  $V_{\rm ds}$  curves and the transconductance  $g_m$  versus gate-source voltage  $V_{\rm gs}$  curves of the 0.15- $\mu$ m  $\Gamma$ -gate MHEMT are shown in Fig. 4(a) and (b), respectively. The  $2\times 50$ - $\mu$ m-wide device

Fig. 4. (a) Drain–source current versus drain–source voltage curves and (b) transconductance versus gate–source voltage of the 0.15- $\mu$ m  $\Gamma$ -gate MHEMT.

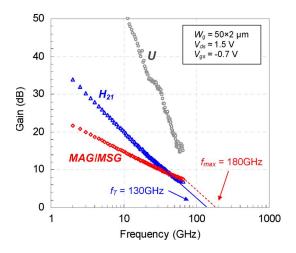

Fig. 5. Frequency dependence of the current gain  $H_{21}$ , the power gain MAG/MSG, and the unilateral gain U of the 0.15- $\mu$ m  $\Gamma$ -gate MHEMT. The frequency range was from 2 to 65 GHz, and the device was biased at  $V_{\rm ds}=1.5~{\rm V}$  and  $V_{\rm gs}=-0.7~{\rm V}$ .

exhibited good pinchoff characteristics, and the saturation  $I_{\rm ds}$  was 680 mA/mm. The maximum  $g_m$  of the device at a  $V_{\rm ds}$  of 1.5 V was 728 mS/mm, and the pinchoff voltage was -1.3 V. The gate–drain breakdown voltage  $V_{\rm BR}$  of the MHEMT was 7.5 V (defined at a gate–drain current of 1 mA/mm), which is the same as that of the device manufactured with a conventional E-beam T-gate. Based on the gate breakdown characteristics of the device, the etch-induced damages were minimized in this letter.

The S-parameters for the MHEMT were measured from 2 to 65 GHz using on-wafer 100- $\mu$ m-pitch ground-signal-ground probes. The gate resistance  $R_g$  of the device using the tilt dryetching process extracted from an S-parameter was 8.27  $\Omega$ . Fig. 5 shows the frequency dependence of the current gain  $H_{21}$ , the power gain "MAG/MSG," and the unilateral gain U of the MHEMT measured at  $V_{\rm ds}=1.5$  V and  $V_{\rm gs}=-0.7$  V. The current gain cut-off frequency  $f_T$  and the maximum oscillation frequency  $f_{\rm max}$  obtained for the  $2\times50~\mu{\rm m}$  MHEMT were 130 and 180 GHz, respectively. The  $f_T$  of the 0.15- $\mu{\rm m}$   $\Gamma$ -gate MHEMT in this letter is comparable to that of the devices reported by other groups with the same gate length [11], [12] and that of the device fabricated by E-beam lithography in

our previous work [9]. The excellent dc and RF performances of the devices demonstrate that the developed tilt dry-etching gate technology is a promising alternative to the conventional gate fabrication technology using E-beam direct writing or hybrid techniques.

### IV. CONCLUSION

A 0.15- $\mu$ m  $\Gamma$ -gate In $_{0.52}$ Al $_{0.48}$ As/In $_{0.6}$ Ga $_{0.4}$ As MHEMT fabricated on GaAs substrate using DUV lithography and a tilt dry-etching technique is demonstrated for the first time in this letter. The developed technology is simple, of low cost, and flexible for the submicrometer  $\Gamma$ -gate fabrication. The 100- $\mu$ m-wide MHEMT with 0.15- $\mu$ m  $\Gamma$  gate fabricated with a dry-etching tilt angle of 32° shows a saturation  $I_{\rm ds}$  of 680 mA/mm and a  $g_m$  of 728 S/mm. The MHEMT also exhibits an  $f_T$  of 130 GHz and an  $f_{\rm max}$  of up to 180 GHz. The excellent device performance shows that the developed 0.15- $\mu$ m  $\Gamma$ -gate technology can practically be used for high-performance MHEMT devices and MMIC manufacturing.

## REFERENCES

- [1] K. Elgaid, H. McLelland, M. Holland, D. A. J. Moran, C. R. Stanley, and I. G. Thayne, "50-nm T-gate metamorphic GaAs HEMTs with  $f_T$  of 440 GHz and noise figure of 0.7 dB at 26 GHz," *IEEE Electron Device Lett.*, vol. 26, no. 11, pp. 784–786, Nov. 2005.

- [2] S.-W. Kim, K.-M. Lee, J.-H. Lee, and K.-S. Seo, "High-performance 0.1-μm In<sub>0.4</sub>AlAs/In<sub>0.35</sub>GaAs MHEMTs with Ar plasma treatment," *IEEE Electron Device Lett.*, vol. 26, no. 11, pp. 787–789, Nov. 2005.

- [3] K. Tabatatabaie-Alavi, D. M. Shaw, and P. J. Duval, "Evolution of T-shaped gate lithography for compound semiconductors field effect transistors," *IEEE Trans. Semicond. Manuf.*, vol. 16, no. 3, pp. 365–369, Aug. 2003.

- [4] W.-S. Sul, S.-D. Kim, H.-M. Park, and J.-K. Rhee, "Electrical charateristics of the 0.1 μm gate length pseudomorphic high-electron-mobility transistors with low-dielectric-constant benzo-cyclo-butene passivations," *Jpn. J. Appl. Phys.*, vol. 42, no. 12, pp. 7189–7193, Dec. 2003.

- [5] N. Hara, K. Makiyama, T. Takahashi, K. Sawada, T. Arai, T. Ohki, M. Nihei, T. Suzuki, Y. Nakasha, and M. Nishi, "Highly uniform InAlAs–InGaAs HEMT technology for high-speed optical communication system ICs," *IEEE Trans. Semicond. Manuf.*, vol. 16, no. 3, pp. 370–375, Aug. 2003.

- [6] Y. Imai, M. Uchida, K. Yamamoto, and M. Hirayama, "A sub-half-micron gate-length GaAs MESFET with new gate structure," *IEEE Electron Device Lett.*, vol. EDL-4, no. 4, pp. 99–101, Apr. 1983.

- [7] P. C. Chao, W. H. Ku, P. M. Smith, and W. H. Perkins, "0.2 micron length T-shaped gate fabrication using angle evaporation," *IEEE Electron Device Lett.*, vol. EDL-4, no. 4, pp. 122–124, Apr. 1983.

- [8] E. Y. Chang, K. C. Lin, E. H. Liu, C. Y. Chang, T. H. Chen, and J. Chen, "Submicron T-shaped gate HEMT fabrication using deep UV lithography," *IEEE Electron Device Lett.*, vol. 15, no. 8, pp. 277–279, Aug. 1994.

- [9] Y. C. Lien, E. Y. Chang, H. C. Chang, L. H. Chu, G. W. Huang, H. M. Lee, C. S. Lee, S. H. Chen, P. T. Shen, and C. Y. Chang, "Lownoise metamorphic HEMTs with reflowed 0.1-\(\mu\)m T-gate," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 348–350, Jun. 2004.

- [10] K. Sawada, K. Makiyama, T. Takahashi, K. Nozaki, M. Igarashi, J. Kon, and N. Hara, "Fabrication of 0.1μm-gate InP HEMTs using i-line lithography," in *Proc. Int. Conf. Indium Phosphide and Relat. Mater.*, May 2003, pp. 65–68.

- [11] M. Kao, E. A. Beam, III, T. Yun, C. F. Campbell, M. S. Heins, P. Saunier, J. B. Delaney, and R. A. Eye, "Metamorphic HEMT technology for millimeter-wave and 40-Gb/s fiber-optics applications," in *Proc. Indium Phosphide and Relat. Mater.*, May 2003, pp. 361–364.

- [12] C. Karnfelt, R. Kozhuharov, H. Zirath, and I. Angelov, "High-purity 60-GHz-band single-chip × 8 multipliers in pHEMT and mHEMT technology," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 6, pp. 2887– 2898, Jun. 2006.