# Temperature-Oriented Experiment and Simulation as Corroborating Evidence of MOSFET Backscattering Theory

Ming-Jer Chen, Senior Member, IEEE, Shih-Guei Yan, Rong-Ting Chen, Chen-Yu Hsieh, Student Member, IEEE, Pin-Wei Huang, and Han-Ping Chen

Abstract—The MOSFET backscattering theory relies on a so-called " $k_BT$ " layer. In this letter, we adopt two different approaches to examine the temperature dependencies of the width spanned by this critical zone. First of all, a 55-nm channel length n-MOSFET is extensively characterized at three temperatures of 233 K, 263 K, and 298 K while undergoing a parameter decoupling/transformation process. A unique relationship is straightforwardly created and is comparable with that in the literature: The width of the " $k_BT$ " layer is proportional to the square root of temperature. The case of 77 K is also projected. Other corroborating evidence is a Monte Carlo particle simulation conducted on an 80-nm-long silicon conductor with the " $k_BT$ " layer's width proportional to the temperature in the high field region. Without adjusting any parameters, the backscattering theory is shown to work well for the demonstrated temperatures down to 77 K.

Index Terms—Backscattering, MOSFET, nanoscale, scattering.

## I. INTRODUCTION

ITHIN THE framework of the MOSFET backscattering theory constructed by Lundstrom [1], a key zone located near the thermal-equilibrium reservoir source can critically determine the device's performance. This specific region spans a certain range from the peak of the source-channel barrier in the direction toward the drain. The accompanying energy-band bending is approximately equal to  $k_BT$ , the magnitude of the thermal energy. On the basis of the multiple-backscattering events [2], [3] over this " $k_BT$ " layer, the backscattering coefficient denoted  $r_C$  can be written as [1]

$$r_C = \frac{l}{l+\lambda} \tag{1}$$

where l is the width of the " $k_BT$ " layer and  $\lambda$  is the quasiequilibrium mean-free-path. Equation (1) is valid only for drain voltage much larger than  $k_BT/q$ . Additionally, a temperaturedependent backscattering-coefficient model was developed [4]. So far, a series of potential applications have been demonstrated: Determining how close to the thermal or ballistic limit

Manuscript received October 11, 2006. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 93-2215-E-009-002. The review of this letter was arranged by Editor E. Sangiorgi.

The authors are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. (e-mail: chenmj@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2006.889504

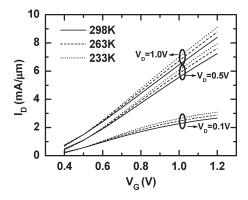

Fig. 1. Measured drain-current per-unit channel width versus gate voltage for three different drain voltages and three different temperatures.

the device can be operated [5]–[7], creating guidelines to follow in strain engineering [8], and addressing self-heating effects in advanced silicon-on-insulator/germanium-on-insulator devices [9]. In spite of these successful demonstrations, the " $k_BT$ " layer itself was not clarified fully. Thus, to testify to the backscattering theory, examination of the temperature dependencies of the width spanned by this critical layer is essential. Here, this goal is achieved through two temperature-oriented approaches: one of experiment and one of simulation.

# II. EXPERIMENT

The device under study was a 55-nm channel length n-MOSFET fabricated using a state-of-the-art manufacturing process. The channel width was 10  $\mu$ m. The following process parameters were assessed through the experimental capacitance-voltage fitting: gate oxide thickness = 1.65 nm,  $n^+$  poly silicon doing concentration =  $9 \times 10^{19}$  cm<sup>-3</sup>, and channel doping concentration =  $8 \times 10^{17}$  cm<sup>-3</sup>. Fig. 1 depicts measured drain-current versus gate voltage for three drain voltages and three temperatures. Other electrical measurements at corresponding temperatures of 298 K, 263 K, and 233 K separately led to quasi-equilibrium threshold voltage of 0.328, 0.345, and 0.360 V and the drain-induced barrier lowering (DIBL) magnitude of 130, 123, and 120 mV/V. Additionally, the long-channel counterparts were utilized to determine the source/drain series resistance ( $\sim 75~\Omega-\mu m$ , regardless of temperature range under study) and the quasi-equilibrium electron mobility. To determine the average thermal injection velocity, a self-consistent Schrödinger-Poisson equations

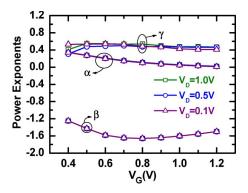

Fig. 2. Extracted power exponents versus gate voltage for three drain voltages.

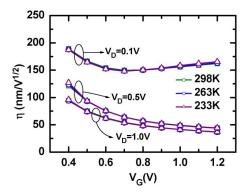

Fig. 3. Extracted values of the prefactor in the developed power-law relation corresponding to Fig. 1.

solver [10] was employed. Then, by incorporating a parameter decoupling/transformation process detailed elsewhere [11], the backscattering coefficient associated with the experimental current–voltage (I-V) was transformed, via the known quasi-equilibrium mean-free-path in (1), into the width of the underlying " $k_BT$ " layer.

Since there are three different " $k_BT$ " layer widths corresponding to three different temperatures, a unique power-law relation results:  $l \propto (k_B T)^{\gamma}$ . The power exponent  $\gamma$  as depicted in Fig. 2 appears to remain constant ( $\sim 0.5$  on the average), regardless of drain and gate voltages. Also plotted in Fig. 2 are other power-law relations involving the average thermal injection velocity  $\propto (k_B T)^{\alpha}$  and the near-equilibrium mobility  $\propto$  $(k_BT)^{\beta}$ . Surprisingly, the created relation,  $l=\eta(k_BT/q)^{0.5}$ , is comparable with that in the literature [12], the validity of which has been confirmed by nonequilibrium Green's function simulations [12]. The prefactor  $\eta$  is expected to be independent of temperature. To testify to this argument, experimental I-Vfitting was again carried out. The resulting  $\eta$  is plotted in Fig. 3. Indeed,  $\eta$  is shown to be a weak function of temperature. It is, therefore, inferred that the picture of the theory can be clarified with the temperature dependencies of the width of the " $k_BT$ " layer.

# III. SIMULATION

SDemon, a Monte Carlo particle-simulation program available in the open source [10], was performed on an 80-nm-long silicon conductor with a constant electric field. Therefore, for

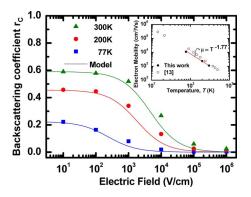

Fig. 4. Simulated (symbols) and calculated (lines) backscattering coefficient versus electric field for three temperatures. The device under study was a silicon conductor with the doping concentration of  $10^{12}~\rm cm^{-3}$ . The electric field is constant throughout the conductor, equal to the applied voltage divided by the length (= 80 nm) of the conductor. The inset shows extracted electron quasi-equilibrium mobility versus temperature. Also plotted in the inset are literature values from the comparable doping concentrations [13]. A fitting line of mobility  $\mu \propto T^{1.77}$  is drawn. The details about the physics framework and numerical implementation in the underlying SDemon simulator can be found through the source [10] or in a textbook [3] by Lundstrom.

applied voltage larger than  $k_BT/q$ ,  $l=k_BT/qE$ , where E is the electric field, indicating that the " $k_BT$ " layer's width is proportional to the temperature. The simulated value of  $r_C$ over a wide range of electric field is displayed in Fig. 4 for different temperatures. The underlying mean-free-path can be readily determined from the flat portion in the low field region (i.e., the applied voltage across the conductor with a length L is significantly less than  $k_BT/q$ , for which  $r_C = L/(L+\lambda)$  [1], [2]), yielding  $\lambda = 278,96$ , and 56 nm for 77, 200, and 300 K, respectively. Then, according to (1), the  $r_C$  in the high field region (applied voltage  $\gg k_BT/q$ ) was quantified, as shown in Fig. 4. Reproduction of the transition region between the low and high field limits was conducted (via [1, eq. (8b)]). Obviously, without adjusting any parameters, the backscattering theory works well for the demonstrated temperatures down to 77 K. To examine the quality of the simulation for the selected L of 80 nm in this letter (that is, due to the nature of the Monte Carlo simulation, lower L means less collisions as compared with the above  $\lambda$  values, which may cause unexpected results especially in the low field region), the mentioned meanfree-path was quantitatively decoupled, giving rise to quasiequilibrium electron mobility, as inserted in Fig. 4, versus temperature. Also plotted together are existing experimental data [13] for comparison. Excellent agreements result.

Fig. 4 also reveals that a low-temperature operation can improve the device's performance through the suppression of backscatterings, in agreement with above experimentally established power-law relations. For the specific operating temperature of 77 K,  $r_C$  approaches zero in the high field region. This indicates that only with such operating conditions can the ballistic transport prevail in an 80-nm-long silicon conductor. The same situations (i.e., 77 K and high drain voltage operation) have been judged [14] to encounter in an experimental device having a comparable channel length (70 nm) [15]. Finally, it is interesting to extend the aforementioned power-law relations, which were experimentally determined from a 55-nm channel length MOSFET, to lower temperatures. Given experimental  $r_C$

of about 0.4 for 298 K,  $r_C$  at 77 K was thereby projected to be 0.14, fairly higher than but close to the ballistic limit.

# IV. CONCLUSION

By means of the temperature-oriented experiment and simulation, we have confirmed the existence of a certain relation between the width of the  $k_BT$  layer and its energy-band bending. Only with such a unique relation included can the  $k_BT$  layer be significantly clarified. The presented temperature dependencies of the  $k_BT$  layer's width can thereby make clear the role of this key zone in the framework of the backscattering theory.

### REFERENCES

- [1] M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," *IEEE Electron Device Lett.*, vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [2] S. Datta, Electronic Transport in Mesoscopic Systems. Cambridge, U.K.: Cambridge Univ. Press, 1995.

- [3] M. S. Lundstrom, Fundamentals of Carrier Transport, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2000.

- [4] M.-J. Chen, H.-T. Huang, K.-C. Huang, P.-N. Chen, C.-S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, Dec. 2002, pp. 39–42.

- [5] F. Assad, Z. Ren, S. Datta, and M. S. Lundstrom, "Performance limits of silicon MOSFET's," in *IEDM Tech. Dig.*, Dec. 1999, pp. 547–550.

- [6] G. Timp, J. Bude, K. K. Bourdelle, J. Garno, A. Ghetti, H. Gossmann, M. Green, G. Forsyth, Y. Kim, R. Kleiman, F. Klemens, A. Kornblit,

- C. Lochstampfor, W. Mansfield, S. Moccio, T. Sorsch, D. M. Tennant, W. Timp, and R. Tung, "The ballistic nano-transistor," in *IEDM Tech. Dig.*, Dec. 1999, pp. 55–58.

- [7] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?," *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 95–97, Feb. 2001.

- [8] H.-L. Lin, H.-W. Chen, C.-H. Ko, C.-H. Ge, H.-C. Lin, T.-Y. Huang, W.-C. Lee, and D. D. Tang, "The impact of uniaxial strain engineering on channel backscattering in nanoscale MOSFETs," in VLSI Symp. Tech. Dig., Jun. 2005, pp. 174–175.

- [9] E. Pop, C.-O. Chui, S. Sinha, R. Dutton, and K. Goodson, "Electrothermal comparison and performance optimization of thin-body SOI and GOI MOSFETs," in *IEDM Tech. Dig.*, Dec. 2004, pp. 411–414.

- [10] [Online] Available: http://www.nanohub.purdue.edu

- [11] M.-J. Chen, H.-T. Huang, Y.-C. Chou, R.-T. Chen, Y.-T. Tseng, P.-N. Chen, and C. H. Diaz, "Separation of channel backscattering coefficients in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1409–1415, Sep. 2004.

- [12] A. Rahman and M. S. Lundstrom, "A compact scattering model for the nanoscale double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 481–489, Mar. 2002.

- [13] C. Jacoboni, C. Canali, G. Ottaviani, and A. A. Quaranta, "A review of some charge transport properties of silicon," *Solid State Electron.*, vol. 20, no. 2, pp. 77–89, Feb. 1977.

- [14] K. Natori, "Ballistic MOSFET reproduces current-voltage characteristics of an experimental device," *IEEE Electron Device Lett.*, vol. 23, no. 11, pp. 655–657, Nov. 2002.

- [15] G. A. Sai-Halasz, M. R. Wordeman, D. P. Kern, E. Ganin, S. Rishton, Z. S. Zicherman, H. Schmod, M. R. Polcari, H. Y. Ng, P. J. Restle, T. H. P. Chang, and R. H. Dennard, "Design and experimental technology for 0.1 μm gate length low-temperature operation FETs," *IEEE Electron Device Lett.*, vol. 8, no. 10, pp. 463–466, Oct. 1998.