# A Novel Four-Mask-Step Low-Temperature Polysilicon Thin-Film Transistor With Self-Aligned Raised Source/Drain (SARSD)

Kow Ming Chang, Gin Min Lin, Cheng Guo Chen, and Mon Fan Hsieh

Abstract—In this letter, a novel structure of polycrystalline-silicon thin-film transistors (TFTs) with self-aligned raised source/drain (SARSD) and a thin channel has been developed and investigated. In the proposed structure, a thick SD and a thin active region could be achieved with only four mask steps, which are less than that in conventional raised SD TFTs. The proposed SARSD TFT has a higher ON-state current and a lower OFF-state leakage current. Moreover, the ON/OFF current ratio of the proposed SARSD TFT is also higher than that of a conventional coplanar TFT.

Index Terms—Four masks, ON/OFF current ratio, polycrystalline-silicon thin-film transistor (poly-Si TFT), self-aligned raised source/drain (SARSD), thin channel.

#### I. INTRODUCTION

OW-TEMPERATURE polycrystalline-silicon (LTPS) thin-film transistors (TFTs) appear to be one of the most promising technologies for the ultimate goal of building largearea electronic systems on glass substrate [1]. In flat-panel liquid crystal, electroluminescent, and plasma displays, as well as in other applications such as high-speed printers and page-width optical scanners, polycrystalline-silicon (poly-Si) TFTs can be used to integrate peripheral driver circuits on glass for system integration [2]. In order to integrate peripheral driving circuits on the same glass substrate, both a large current drive and a high drain breakdown voltage (BV) are necessary for poly-Si TFT device characteristics. It has been previously reported that the use of a thinner active channel film is beneficial for obtaining a higher current drive [3], [4]. The use of a thin active channel layer, however, inevitably results in poor SD contact and large parasitic series resistance. An ideal TFT device structure, therefore, should consist of a thin active channel region, while maintaining a thick SD region. The thick SD region serves not only to reduce the lateral electric field, thus maintaining the BV [5], [6], but also to reduce the SD series resistance. Previous methods used to fabricate such ideal structures with thin active channel and thick SD regions, however, are not self-aligned in nature and require

Manuscript received August 23, 2006; revised October 17, 2006. The review of this letter was arranged by Editor J. Sin.

The authors are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2006.887933

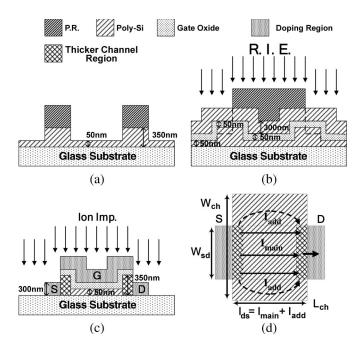

Fig. 1. (a)–(c) Schematic cross section of the major fabrication steps of the proposed n-channel SARSD TFT. (d) Schematic diagram of the proposed SARSD structure current flow.

additional masks [5], [6] when compared to conventional coplanar TFTs.

In this letter, a novel TFT with a self-aligned raised source/ drain (SARSD) structure is proposed. The new device features a thin wider active channel region and a thick SD region. The raised SD (RSD) regions are self-aligned, and no additional mask is needed.

### II. DEVICE FABRICATION

The fabrication processes of the novel n-channel poly-Si SARSD TFT were given as follows: A 350-nm-thick  $\alpha$ -Si layer for the active region was deposited by a low-pressure chemical vapor deposition (LPCVD) system using SiH\_4 at 550 °C on 500-nm thermal oxidized silicon wafers. After patterning, the thin  $\alpha$ -Si (50 nm) regions and the thick  $\alpha$ -Si (350 nm) regions were formed using reactive ion etching (RIE) at this mask step, as shown in Fig. 1(a). The widths of the thick  $\alpha$ -Si (350 nm) regions were 5  $\mu$ m. Then, the deposited  $\alpha$ -Si film was annealed in nitrogen ambient at 600 °C for 24 h to become the poly-Si film. After recrystallization, the etching damages of the channel surface were recovered, and the surface

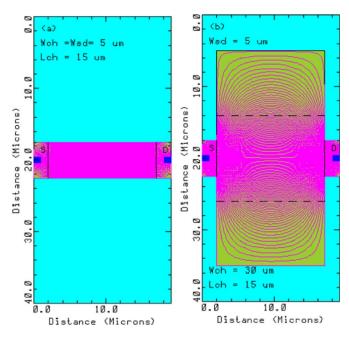

Fig. 2. Current flow lines simulated by MEDICI in (a) the conventional coplanar structure with  $L_{\rm ch}=15~\mu{\rm m}$  and  $W_{\rm ch}=W_{\rm sd}=5~\mu{\rm m}$ , and (b) the SARSD structure with  $L_{\rm ch}=15~\mu{\rm m}$ ,  $W_{\rm sd}=5~\mu{\rm m}$ , and  $W_{\rm ch}=30~\mu{\rm m}$ .

roughness is approximately 3 nm. A 50-nm plasma-enhanced chemical vapor deposition (PECVD) gate oxide layer was deposited at 350 °C, and then, a 300-nm LPCVD poly-Si gate was deposited. After defining the undoped gate region [gate mask area =  $L_{\rm ch} \times W_{\rm ch}$ , as shown in Fig. 1(d)], the remnant 50-nm oxide film and 50-nm poly-Si film would be further removed using the RIE system to form an isolated active region, as shown in Fig. 1(b) and (c). After the photoresist was removed, the gate, source, and drain regions were formed by ion implantation of phosphorous (dose =  $5 \times 10^{15}$  cm<sup>-2</sup> at 50 keV) and then activated in nitrogen ambient at 600 °C for 24 h, as shown in Fig. 1(c). It is worth pointing out that the gate region width  $W_{\mathrm{ch}}$  is larger than that of the SD region  $W_{\mathrm{sd}}$ . Therefore, a thin and wider active region would be formed below the whole of the gate region, as shown in Fig. 1(d). After the source, drain, and gate activation, the 500-nm passivation oxide was deposited by PECVD. Contact holes were opened using wet etching of the passivation oxide layer. A layer of aluminum was then deposited by thermal coater system with a thickness of 600 nm. After metal patterning, a forming gas anneal is performed at 400 °C for 30 min. The total masks of our fabrication processes are four masks, which are less than those of conventional processes in an RSD poly-Si TFT [5], [6]. For comparison, the conventional coplanar poly-Si TFTs with 50-nm channel thickness were also fabricated in the same run.

### III. RESULTS AND DISCUSSION

Fig. 1(d) shows the possible current flow paths of the proposed SARSD structure. To ensure that the current flow of the proposed SARSD structure would be as shown in Fig. 1(d), the two-dimensional numerical simulator MEDICI was used. Fig. 2 shows the simulated current flow lines of the conventional coplanar and proposed SARSD poly-Si TFT structures in

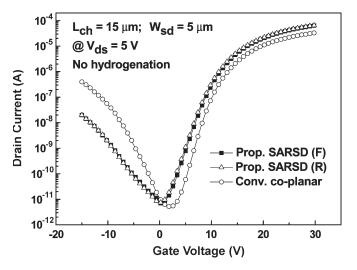

Fig. 3.  $I_{\rm ds}-V_{\rm gs}$  output characteristics of the proposed SARSD TFT in both forward mode (F) and reverse mode (R), and the conventional coplanar TFT, in which the reverse mode has the source and drain electrodes exchanged.

ON-state. The channel length and width of the simulated conventional coplanar structure are 15 and 5  $\mu$ m, respectively. From the simulation results in Fig. 2(a), the simulated current flow lines of the conventional structure are uniformly distributed in the channel region and the SD regions. However, for the proposed SARSD structure, as shown in Fig. 2(b), the current flow paths are different from the conventional sample in ON-state. It is because the channel width is wider than the SD width, and a wider channel width would obtain a higher drain current. Therefore, it can be convinced that the proposed RSD structure would obtain a higher drain current than the conventional coplanar one.

As shown in Fig. 3, the proposed SARSD TFT has higher ON-state current  $(V_{\rm gs}=30~{

m V})$  and lower OFF-state leakage current ( $V_{\rm gs} = -15 \text{ V}$ ) than the conventional TFT. In ON-state, the main reasons for a higher ON-state current are wider channel width ( $W_{\rm ch} = 30 \, \mu \rm m$ ) and smaller SD parasitic resistances [6]. On the contrary, in OFF-state, the minimum OFF-state leakage current of the proposed SARSD TFT is only slightly larger than that of the conventional TFT. It is because the leakage current is determined by the electron-hole pair generation rate in the depletion region at the drain edge. The pair generation rate is strongly dependent on the number of trap states in the forbidden gap, the lateral electric field, and the generation volume of the depletion region [7]-[9]. Although a thicker drain region causes the generation volume of the SARSD TFT (must be approximately  $W_{\rm sd}$  multiplied by the thickness of the depletion region) to increase, the maximum lateral electric field near the drain region of the proposed SARSD TFT largely dropped from 2.13 to 1.57 MV/cm due to the thick SD region [10]. At higher drain and reverse gate bias ( $V_{

m ds}=5$  V and  $V_{

m gs}=$ -15 V), the leakage current would be due to the thermionic field emission via grain boundary defects [11]. Therefore, the proposed SARSD TFT has lower OFF-state leakage current than the conventional TFT because the maximum lateral electric field near the drain region largely dropped, even though the generation volume increased. Table I lists some of the parameters of the two devices (forward-mode SARSD TFT and coplanar

TABLE I Some Parameters of SARSD in Forward-Mode and Conventional Coplanar n-Channel poly-Si TFTs Measured at  $V_{\rm ds}=5~{\rm V}$

|                            | I <sub>max</sub><br>(μ <b>A</b> ) | I <sub>min</sub><br>(pA) | I <sub>off</sub><br>(nA)<br>(V <sub>gs</sub> = -15V) | On/Off<br>Current ratio | Maximum<br>Lateral<br>E. Field<br>(MV/cm) |

|----------------------------|-----------------------------------|--------------------------|------------------------------------------------------|-------------------------|-------------------------------------------|

| Conventional co-planar TFT | 33.3                              | 5.15                     | 398                                                  | 6.4x10 <sup>6</sup>     | 2.13                                      |

| Proposed<br>SARSD TFT      | 64.8                              | 6.57                     | 19.9                                                 | 9.8x10 <sup>6</sup>     | 1.51                                      |

TFT). The ON/OFF current ratio of the proposed SARSD TFT is also slightly higher than that of the conventional one.

## IV. CONCLUSION

In this letter, a novel four-mask-step n-channel LTPS TFT with an SARSD region and a thin channel was proposed and investigated. The gate mask was used to form a large-area thin-channel region below the gate region, and the SARSD region can be formed without the additional mask step. A lower OFF-state leakage current and a higher ON/OFF current ratio can be obtained for the proposed SARSD TFT. The TFT fabrication processes are fully compatible with the conventional four-mask ones. This new TFT structure may be an attractive device structure for future high-performance large-area device applications.

#### REFERENCES

- [1] A. Kumar K. P. and J. K. O. Sin, "A simple polysilicon TFT technology for display systems on glass," in *IEDM Tech. Dig.*, 1997, pp. 515–518.

- [2] M. G. Clark, "Current status and future prospects of poly-Si devices," Proc. Inst. Electr. Eng.—Circuits Devices Syst., vol. 141, no. 1, pp. 3–8, Feb. 1999.

- [3] T. Noguchi, H. Hayashi, and T. Ohshima, "Low temperature polysilicon super-thin-film transistor (LSFT)," *Jpn. J. Appl. Phys.*, vol. 25, no. 2, pp. L121–L123, Feb. 1986.

- [4] M. Miyasaka, T. Komatsu, W. Itoh, A. Yamaguchi, and H. Ohashima, "Effects of channel thickness on poly-crystalline silicon thin film transistor," in *Proc. SSDM*, 1995, pp. 647–650.

- [5] M. Yoshimi, M. Takahashi, T. Wada, K. Kato, S. Kambayashi, M. Kemmochi, and K. Natori, "Analysis of the drain breakdown mechanism in ultra-thin-film SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 37, no. 9, pp. 2015–2021, Sep. 1990.

- [6] S. Zhang, C. Zhu, J. K. O. Sin, and P. K. T. Mok, "A novel ultrathin elevated channel low-temperature poly-Si TFT," *IEEE Electron Device Lett.*, vol. 20, no. 11, pp. 569–571, Nov. 1999.

- [7] O. K. B. Lui, M. J. Quinn, S. W.-B. Tam, T. M. Brown, P. Migliorato, and H. Ohshima, "Investigation of the low field leakage current mechanism in polysilicon TFT's," *IEEE Trans. Electron Devices*, vol. 45, no. 1, pp. 213–217, Jan. 1998.

- [8] O. K. B. Lui and P. Migliorato, "A new generation-recombination model for device simulation including the Poole–Frenkel effect and phonon-assisted tunnelling," *Solid State Electron.*, vol. 41, no. 4, pp. 575–583, 1997.

- [9] S. D. Brotherton, J. R. Ayres, and M. J. Trainor, "Control and analysis of leakage currents in poly-Si thin-film transistors," *J. Appl. Phys.*, vol. 79, no. 2, pp. 895–904, Jan. 1996.

- [10] A. Kumar K. P., J. K. O. Sin, C. T. Nguyen, and P. K. Ko, "Kink-free polycrystalline silicon double-gate elevated channel thin-film transistors," *IEEE Trans. Electron Devices*, vol. 45, no. 12, pp. 2514–2520, Dec. 1998.

- [11] C. H. Kim and K.-S. Sohn, "Temperature dependent leakage currents in polycrystalline silicon thin film transistors," *J. Appl. Phys.*, vol. 81, no. 12, pp. 8084–8090, Jun. 1997.