# High-Performance HfO<sub>2</sub> Gate Dielectrics Fluorinated by Postdeposition CF<sub>4</sub> Plasma Treatment

Woei Cherng Wu,<sup>a</sup> Chao Sung Lai,<sup>b,z</sup> Jer Chyi Wang,<sup>c</sup> Jian Hao Chen,<sup>d</sup> Ming Wen Ma,<sup>d</sup> and Tien Sheng Chao<sup>a</sup>

<sup>a</sup>Department of Electrophysics and <sup>d</sup>Department of Electronic Engineering, National Chiao Tung University, Hsinchu, Taiwan

The superior characteristics of fluorinated  $HfO_2$  gate dielectrics were investigated. Fluorine was incorporated into  $HfO_2$  thin film by postdeposition  $CF_4$  plasma treatment to form fluorinated  $HfO_2$  gate dielectrics. Secondary-ion mass spectroscopy results showed that there was a significant incorporation of fluorine atoms at the  $TaN/HfO_2$  and  $HfO_2/Si$  interface. Improvement of the gate leakage current, breakdown voltage, capacitance-voltage hysteresis, and charge trapping characteristics was observed in the fluorinated  $HfO_2$  gate dielectrics, with no increase of interfacial layer thickness. A physical model is presented to explain the improvement of hysteresis and the elimination of charge trapping. These results indicate that the fluorinated  $HfO_2$  gate dielectrics appear to be useful technology for future ultrathin gate dielectrics.

© 2007 The Electrochemical Society. [DOI: 10.1149/1.2733873] All rights reserved.

Manuscript submitted November 27, 2006; revised manuscript received February 12, 2007. Available electronically May 4, 2007.

For anticipated applications of very large scale integration (VLSI) technology, more advanced materials for gate dielectrics will be required. Although a physical gate thickness of <1 nm for a complementary metal oxide semiconductor transistor with nitride/oxynitride gate stacks has been demonstrated, continued scaling for future semiconductor technology requires an equivalent oxide thickness of less than 1.0 nm for sub-65-nm metal oxide semiconductor field-effect transistor (MOSFET) devices. However, development of a dielectric thin film with an effective oxide thickness under 1.0 nm and an acceptable leakage current level will be very difficult, due to the high direct tunneling leakage current of nitride/oxynitride gate dielectrics. As a result, high-dielectric-constant (high-k) oxide thin films are currently attracting great interest as possible alternatives to nitrided-SiO<sub>2</sub> gate dielectrics.  $^{3-5}$

Various extrinsic gate dielectrics, including  $Ta_2O_5$ ,  $Y_2O_3$ ,  $ZrO_2$ ,  $CeO_2$ ,  $SrTiO_3$ ,  $BaSrTiO_3$  (BST), and  $HfO_2$  have been extensively investigated. Among these high-k gate materials,  $HfO_2$  gate dielectrics <sup>6-8</sup> are the most popular candidate currently under study, due to their high dielectric constant (25–30), wide energy bandgap ( $\sim 5.68$  eV), and the high stability of their Si surface. At the moment, capacitance-voltage (C-V) hysteresis and charge trapping when the hafnium dioxide is applied to the MOSFET as the gate dielectrics, <sup>9-11</sup> are critical problems for future ultralarge scale integration (ULSI) technology applications of  $HfO_2$ . Therefore, various methods have been used to ameliorate these problems, including cosputtering of silicon and aluminum with hafnium to deposit hafnium silicate and aluminate dielectrics, <sup>12,13</sup> nitridation before  $HfO_2$  deposition, <sup>14</sup> and oxidizing a sputtered metal nitride such as  $HfN^{15}$  to form hafnium oxynitride (HfON) films.

Recently, fluorinated gate dielectrics have been shown to improve the  $\mathrm{SiO_2/Si}$  interface. Furthermore, fluorine incorporation into the high-k gate dielectrics has been proposed, to improve both the thermal stability, and the negative bias temperature instability (NBTI) reliability. However, characterization of key aspects of fluorinated  $\mathrm{HfO_2}$  gate dielectrics formed by  $\mathrm{CF_4}$  plasma treatment, including the thermal stability of the gate leakage current and C-V characteristics, breakdown voltage, and effective oxide thickness, has not been well developed. In addition, neither charge trapping during electrical measurement nor the temperature dependence of the gate leakage current has been investigated.

In this paper, the characteristics of fluorinated  $HfO_2$  gate dielectrics using  $CF_4$  plasma treatment were demonstrated. Fluorinated  $HfO_2$  gate dielectrics show thinner effective oxide thickness

( $\sim$ 2.2 nm), smaller C-V hysteresis (45 mV), low gate leakage current density ( $\sim$ 5 × 10<sup>-9</sup> A/cm²), high breakdown voltage ( $\sim$ -9 V), better thermal stability, good distribution of electrical performance, and less charge trapping. A physical model is proposed to comprehensively explain the mechanism for electron and hole trapping in fluorinated HfO<sub>2</sub> thin film. Furthermore, the temperature dependence of the leakage current explains why the generated traps are effectively eliminated in fluorinated HfO<sub>2</sub> gate dielectrics.

## **Experimental**

For the purposes of this research, MOS capacitors were fabricated. The silicon wafers used in this study were p-type (100) Czochralski (CZ) with a resistance of 4-7  $\Omega$  cm. Standard RCA cleaning was first performed on all samples. HfO2 thin film was then deposited by reactive radio-frequency (rf) sputter method. Deposition plasma was created by applying 150 W rf power to a 7.5 cm diam target positioned 15 cm away from the substrate. Hafnium dioxide deposition took place for 2.5 min, resulting in the formation of a 5 nm HfO2 thin film. After HfO2 thin film deposition, CF4 plasma was used to treat the HfO2 thin film to form the fluorinated HfO<sub>2</sub> gate dielectrics. Some samples were treated under CF<sub>4</sub> plasma in the plasma-enhanced chemical vapor deposition (PECVD) system, whose chamber volume is  $3.76 \times 10^5$  cm<sup>3</sup>. The cathode diameter was 40 cm, and the distance between the cathode and the holder was 4 cm. The sample was loaded into the substrate at an elevated temperature (300°C). The reactive pressure and the flow rate of the CF<sub>4</sub> gas were 600 mTorr and 500 sccm, respectively. The rf power was 40 W with CF<sub>4</sub> plasma exposure times of 1 and 5 min (termed P-1 and P-5, respectively). For the normal HfO<sub>2</sub> gate dielectrics samples (denoted as as-deposited), there was no CF<sub>4</sub> plasma treatment after the hafnium dioxide deposition. Postdeposition annealing (PDA) was performed on rapid thermal anneal (RTA) equipment at 700°C for 30 s in N<sub>2</sub> ambient. Samples with PDA treatment were called as-deposited/A, or P-1/A and P-5/A. The PDA process was used to determine the thermal stability of the as-deposited HfO<sub>2</sub> and fluorinated HfO<sub>2</sub> gate dielectrics. In a later phase of the investigation, a 50 nm TaN metal gate was also deposited by the rf sputter method. An aluminum film 300 nm thick was then deposited on the TaN gate for use as the gate electrode. Finally, the 300 nm aluminum film was evaporated from the bottom of the electrode by a thermal evaporator to form the MOS capacitors.

The effective oxide thickness (EOT) was estimated from the accumulation capacitance of the high-frequency (100 kHz) C-V measurement with a gate area of  $6.75 \times 10^{-5}$  cm<sup>2</sup>. Quantum effects were not considered. To explore CF<sub>4</sub> plasma etching effects in HfO<sub>2</sub> thin film, atomic force microscopy (AFM) was used to analyze the

<sup>&</sup>lt;sup>b</sup>Department of Electronic Engineering, Chang Gung University, Kwei-Shan, Tao-Yuan, Taiwan <sup>c</sup>Nanya Technology Corporation, Kueishan, Taoyuan, Taiwan

<sup>&</sup>lt;sup>z</sup> E-mail: cslai@mail.cgu.edu.tw

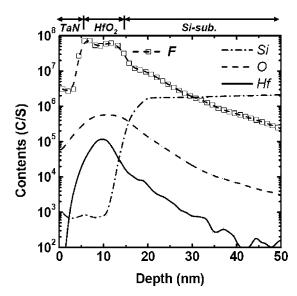

**Figure 1.** SIMS depth profile of MOS structure for fluorine oxygen, hafnium, and silicon atom distribution. The fluorine atoms were accumulated mainly at the two interfaces of the gate-oxide films.

surface morphology of the  $HfO_2$  thin film after  $CF_4$  plasma treatment. Furthermore, the content and distribution of the fluorine atoms was measured by secondary-ion mass spectroscopy (SIMS). X-ray photoelectron spectroscopy (XPS) was used to analyze the Hf-O and Hf-F bondings of the fluorinated  $HfO_2$  thin films.

#### **Results and Discussion**

Figure 1 shows the SIMS depth profiles of HfO<sub>2</sub> film with post-deposition CF<sub>4</sub> plasma treatment. The location of both the top and bottom HfO<sub>2</sub> interfaces was determined from the silicon, oxygen, and hafnium profiles. This experimental result shows that the fluorine atoms are located primarily at the two interfaces of the TaN/HfO<sub>2</sub> and HfO<sub>2</sub>/Si-substrates. The accumulation of fluorine atoms the interfaces of the gate dielectrics has been proposed in previous studies. <sup>22,23</sup> However, some fluorine atoms accumulated in the bulk HfO<sub>2</sub> thin film, as shown by the XPS analysis (Fig. 2). Thus, it appears that fluorine atoms are distributed in each of the HfO<sub>2</sub> gate

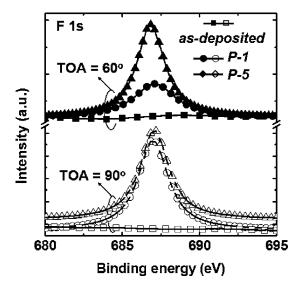

**Figure 2.** XPS analysis of the F 1s electronic spectra of as-deposited and fluorinated samples, TOAs of 60 and 90°, respectively, where the F 1s peak is at 687 eV.

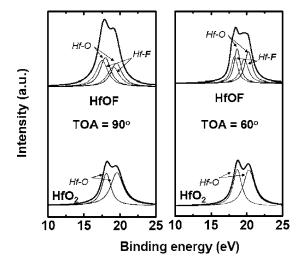

Figure 3. Hf 4f XPS spectra of as-deposited and fluorinated  $HfO_2$  thin films, respectively. Take-off angles of 60 and 90° were used to measure the XPS spectra.

dielectrics after  $CF_4$  plasma treatment. Wright et al. proposed that fluorine atoms react with Si–O bonds, and then the released oxygen atoms oxidize the  $SiO_2/Si$  interface. <sup>24</sup> We thus argue that the structural change of the gate-oxide films occurs due to the reaction between the fluorine atoms and the Si–O bonds.

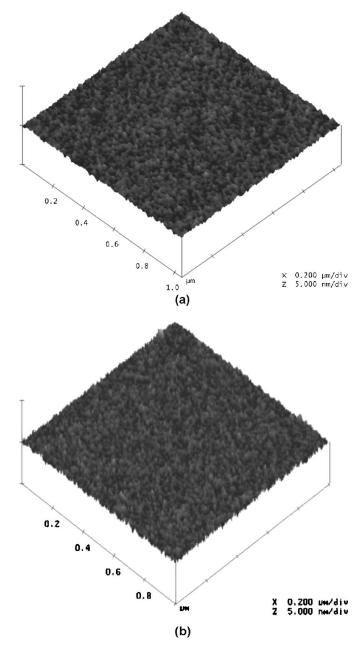

Take-off angles (TOAs) of 60 and 90° were used to measure the XPS spectra of surface and bulk HfO<sub>2</sub> thin films (Fig. 2). In Fig. 2, for all samples except the as-deposited sample, a distinct F 1s peak at 687 eV can be observed. The CF<sub>4</sub> plasma treatment processes are apparently introducing fluorine atoms into the dielectrics, as noted in the prior SIMS analysis. Furthermore, the F 1s peak of the sample with the longer CF<sub>4</sub> plasma treatment (5 min) displays a higher intensity when the TOA is 60°. This implies that the longer CF<sub>4</sub> plasma treatment introduces more fluorine at the surface of the HfO<sub>2</sub> thin films. In addition, the fluorine intensity was nearly identical in the bulk of HfO2 thin films, regardless of CF4 plasma treatment conditions (Fig. 2; TOA is 90°). Figure 3 shows the Hf 4f ESCA spectra of HfO2 and fluorinated HfO2 thin film. Two distinct peaks of Hf-O bonding, at 18.7 and 20.3 eV, were found in the asdeposited sample. Nevertheless, the as-deposited samples may also have large numbers of other types of bonding defects, which was not observed when the material is prepared. The TOA angles of 60 90° were also used to measure the XPS spectra. Compared to the Hf-O bonds in Hf 4f spectra of the HfO<sub>2</sub> thin film, the Hf 4f spectra of the fluorinated HfO<sub>2</sub> thin film is shifted roughly 0.43 eV (Fig. 3). This also shows the Hf-F bonding formation after CF<sub>4</sub> plasma treatment, as seen in Fig. 1 and 2. To investigate the plasma etching effect in HfO<sub>2</sub> thin film, we used AFM and ellipsometry to analyze the surface roughness and thickness of the HfO2 thin film with and without CF<sub>4</sub> plasma treatment. Ellipsometry indicated that the thicknesses of as-deposited and fluorinated HfO<sub>2</sub> thin films (P-5) are 5.035 and 4.994 nm, respectively. These results imply that the CF<sub>4</sub> plasma etching effect during the treatment of HfO2 thin films is negligible. In addition, the root-mean-square (rms) variations of the surfaces of the as-deposited and fluorinated HfO<sub>2</sub> thin film (P-1), extracted from the AFM images, are 1.05 and 1.74 Å, respectively (Fig. 4a and b). Furthermore, the rms of the HfO2 thin film with 5 min of CF4 plasma treatment was only 2.03 Å. These results appear to show that the CF<sub>4</sub> plasma treatment did not damage the HfO<sub>2</sub> thin film during fluorinated HfO<sub>2</sub> thin film formation.

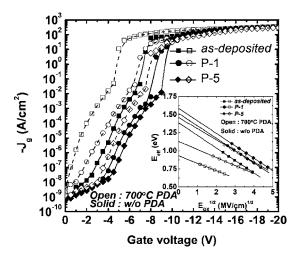

Figure 5 shows the current density vs gate voltage (J-V) characteristics of as-deposited and fluorinated  $HfO_2$  gate dielectrics. The gate leakage current of the samples after  $700^{\circ}C$  annealing increased due to dielectric film crystallization. In addition, the breakdown

Figure 4. AFM images of the surface of the  $HfO_2$  thin films (a) without  $CF_4$  plasma treatment and (b) with  $CF_4$  plasma treatment for 1 min.

voltage of the fluorinated HfO $_2$  gate dielectrics was also improved (Fig. 5). The inset in Fig. 5 depicts the close fit of all samples to the Frenkel–Poole model. The linear behavior is a further indication that the carrier transportation in both as-deposited and fluorinated HfO $_2$  is F–P emission. The effective barrier heights ( $\Phi_B$ ) were much higher for the fluorinated HfO $_2$  gate dielectrics, with and without PDA treatment (inset, Fig. 5). In addition, the Schottky emission barrier (TaN/HfO barrier) was also calculated. Because the barrier height extracted from Schottky emission was larger than the trap energy extracted from F–P conduction, the F–P conduction mechanism would dominate over the Schottky emission.

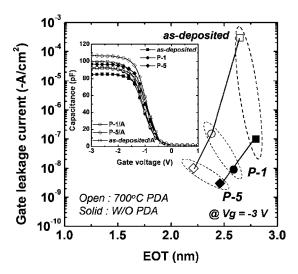

Figure 6 shows the effective oxide thickness vs gate leakage current characteristics of  $HfO_2$  gate dielectrics with and without  $CF_4$  plasma treatment and  $700^{\circ}C$  postdeposition annealing (PDA). The inset shows the C-V characteristics of all the samples. The thinner EOT extracted from C-V curves was obtained for the  $HfO_2$  gate dielectrics with  $CF_4$  plasma treatment and was further improved

**Figure 5.** C-V characteristics for the as-deposited and fluorinated  $HfO_2$  gate dielectrics with and without PDA. (Inset) The F–P curve fit for all samples. The fluorinated  $HfO_2$  gate dielectrics have a higher F–P barrier height, which increases as plasma treatment time increases.

after annealing at 700°C. The  $CF_4$  plasma treated  $HfO_2$  films appeared to possess properties superior to those of the as-deposited samples, including thin EOT and low leakage current. However, the  $HfO_2$  films, after 700°C PDA, still presented higher gate leakage current at the same EOT than the as-deposited samples, owing to the film crystallization discussed earlier.

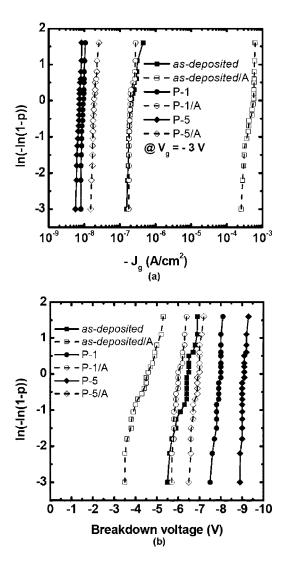

Figure 7 shows the Weibull distribution plots of the gate leakage current density at the gate voltage of -3 V and the breakdown voltage for all samples. Both the performance and uniformity distribution of the fluorinated  $HfO_2$  gate dielectrics were superior to those of the as-deposited samples.

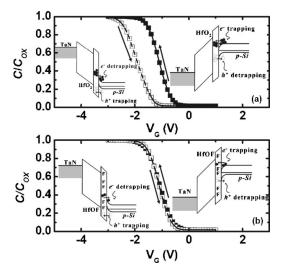

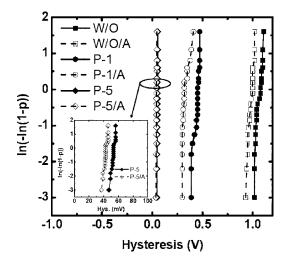

The normalized  $ilde{C}$ -V hysteresis curves of the as-deposited and fluorinated  $HfO_2$  gate dielectrics are shown in Fig. 8a and b, respectively. The C-V hysteresis of the as-deposited  $HfO_2$  gate dielectrics was 1 V, but decreased to roughly 50 mV for the fluorinated  $HfO_2$  gate dielectrics (P-5). According to the inner-interface trapping model,  $^{25}$  when the capacitor is biased at accumulation ( $V_G = -3$  V), majority carriers (holes for the p-type Si substrate) tunnel from p-Si substrate through the interfacial layer (IL) and are trapped at the inner-interface, as indicated in the inset band diagram in Fig.

**Figure 6.** The relationship between gate leakage current and EOT, extracted from the C-V curves (inset figure) for all samples. The fluorinated  $HfO_2$  gate dielectrics have lower leakage current and EOT.

**Figure 7.** The Weibull distribution of the (a) gate leakage current and (b) breakdown voltage, for the as-deposited and fluorinated HfO<sub>2</sub> gate dielectrics. A good distribution performance of the fluorinated HfO<sub>2</sub> gate dielectrics was observed.

**Figure 8.** The C-V hysteresis characteristics for the (a) as-deposited and (b) fluorinated  $HfO_2$  gate dielectrics, respectively. The inset band-diagram explains the charge trapping mechanism.

**Figure 9.** The Weibull distribution of the C-V hysteresis for all samples. Only 50 mV C-V hysteresis was observed for the fluorinated  $HfO_2$  gate dielectrics.

8a. Furthermore, when the voltage is biased at the inversion region  $(V_G=1~\rm V)$ , the trapped holes at the inner-interface will be detrapped, while at the same time the minority carriers (electrons) tunnel from the p-Si substrate and are trapped at the inner-interface. On the other hand, the shifted C-V curves are not parallel at intermediate and low voltages. A slight degradation of C-V curves in depletion region can be observed as indicated in Fig. 8a. As a result, the hysteresis phenomenon was contributed by both interface states and bulk trapping. However, for the fluorinated HfO<sub>2</sub> thin film, the number of holes and the number of electrons trapped at the innerinterface and some interface states were reduced, owing to the F atoms incorporated into the HfO<sub>2</sub> thin film (Fig. 8b, inset). This indicates that hole trapping was observed in our HfO<sub>2</sub> thin film, a finding strongly supported by the negative flat band voltage shift during the C-V hysteresis measurement.

Figure 9 displays the Weibull distribution of C-V hysteresis for all samples. The C-V hysteresis was improved by increasing the  $CF_4$  plasma treatment duration. Of all the samples, the  $HfO_2$  films with  $CF_4$  plasma treatment for 5 min, and rapid thermal annealing at  $700^{\circ}C$  for 30 s (P-5/A) exhibit the smallest C-V hysteresis, about 40 mV.

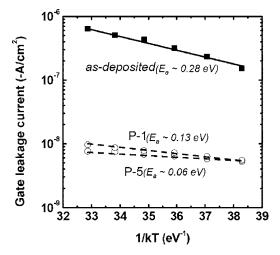

**Figure 10.** Arrhenius plots of leakage current density for the  $HfO_2$  and fluorinated  $HfO_2$  gate dielectrics. The plots were obtained from the current-voltage characteristics at Vg = -3 V measured from 303 to 353 K.

Table I. Summaries of the characteristics for all samples. The fluorinated sample exhibits superior properties in EOT, leakage current, breakdown voltage, hysteresis, and charge trapping.

|                | EOT (nm) | $Jg A/cm^2$ $@V_g = -3 V$ | $\begin{array}{c} \text{F-P } \Phi_B \\ (\text{eV}) \end{array}$ | C-V<br>Hys. (V) | $E_a$ (eV) | $-V_{BD}(V)$ | Surface rough. (Å) |

|----------------|----------|---------------------------|------------------------------------------------------------------|-----------------|------------|--------------|--------------------|

| As-deposited   | 2.8      | $1 \times 10^{-7}$        | 1.38                                                             | 1.1             | 0.28       | 6.5          | 1.05               |

| As-deposited/A | 2.68     | $5 \times 10^{-4}$        | 0.93                                                             | 1               | 0.27       | 4.8          |                    |

| P-1            | 2.62     | $9 \times 10^{-9}$        | 1.52                                                             | 0.51            | 0.13       | 8            | 1.74               |

| P-1/A          | 2.53     | $1 \times 10^{-7}$        | 1.13                                                             | 0.31            | 0.13       | 5.9          |                    |

| P-5            | 2.47     | $7 \times 10^{-9}$        | 1.58                                                             | 0.05            | 0.06       | 9            | 2.03               |

| P-5/A          | 2.21     | $1 \times 10^{-8}$        | 1.46                                                             | 0.045           | 0.06       | 7            |                    |

Figure 10 shows the Arrhenius plots of the temperature dependence leakage current density for the as-deposited and fluorinated HfO<sub>2</sub> gate dielectrics. The plots were obtained from the current voltage characteristics at  $V_G = -3$  V, measured at 303–353 K. The data fit to the relationship  $J \propto \exp(-E_a/k_BT)$ . The calculated values of the activation energies for the as-deposited sample and fluorinated samples are 0.28, 0.13 (P-1), and 0.06 eV (P-5), respectively. This apparently shows that the CF<sub>4</sub> plasma treatment effectively removed the dielectric vacancies, leading to a lower concentration of generated traps. <sup>26</sup> The temperature dependence performance of the gate leakage current for as-deposited HfO<sub>2</sub> gate dielectrics was more obvious, owing to the large concentration of generated traps (hole trapping), as illustrated in C-V hysteresis. The results of the decrease in activation energy (Fig. 10) indicate that the fluorinated HfO<sub>2</sub> gate dielectrics have a lower concentration of generated hole traps.

Table I summarizes the characteristics for all samples. The surface roughness of the  $HfO_2$  thin films was not degraded by  $CF_4$  plasma treatment. Furthermore, the fluorinated sample exhibits superior properties in EOT, leakage current, breakdown voltage, hysteresis, and elimination of deep traps.

# Conclusion

An approach to demonstrate the characteristics of fluorinated  $HfO_2$  gate dielectrics formed by  $CF_4$  plasma treatment was proposed and systematically studied. The fluorinated  $HfO_2$  thin film exhibited superior C-V and I-V performance even after high-temperature annealing. Furthermore, charge trapping occurred in C-V hysteresis, while measurement of the fluorinated  $HfO_2$  gate dielectrics was effectively improved. This technology may be applicable to  $HfO_2$  thin films for future ULSI applications.

### Acknowledgments

The authors thank the National Science Council, R.O.C., for funding this research through grant NSC-94-2215-E-182-008.

Chang Gung University assisted in meeting the publication costs of this article.

#### References

- M. L. Green, E. P. Gusev, R. Degraeve, and E. L. Garfunkel, J. Appl. Phys., 90, 2057 (2001).

- International Technology Roadmap for Semiconductors 2005 Update, The Semiconductors Industry Association (2005).

- 3. J. C. Wang, D. C. Shie, T. F. Lei, and C. L. Lee, J. Appl. Phys., 98, 024503 (2005).

- C. S. Lai, W. C. Wu, T. S. Chao, J. H. Chen, J. C. Wang, L. Tay, and N. Rowell, *Appl. Phys. Lett.*, 89, 072904 (2006).

- J. C. Wang, D. C. Shie, T. F. Lei, and C. L. Lee, Electrochem. Solid-State Lett., 6, F34 (2003).

- C. H. Choi, S. J. Rhee, T. S. Jeon, N. Lu, J. H. Sim, R. Clark, M. Niwa, and D. L. Kwong, Tech. Dig. - Int. Electron Devices Meet., 2002, 857.

- R. Choi, C. S. Kang, B. H. Lee, K. Onishi, R. Nieh, S. Gopalan, E. Dharmarajan, and J. C. Lee, VLSI Technical Symposium Digest, IEEE, p. 15 (2001).

- T. P. Ma, in Extended Abstracts of the Solid State Device and Materials, p. 30 (2004).

- 9. Z. Zhang, M. Li, and S. A. Campbell, IEEE Electron Device Lett., 26, 20 (2005).

- C. L. Cheng, C. Y. Lu, K. S. Chang-Liao, C. H. Huang, S. H. Wang, and T. K. Wang, *IEEE Trans. Electron Devices*, 53, 63 (2006).

- C. S. Lai, W. C. Wu, J. C. Wang, and T. S. Chao, Appl. Phys. Lett., 86, 022905 (2005).

- P. F. Lee, J. Y. Dai, K. H. Wong, H. L. W. Chan, and C. L. Choy, *Appl. Phys. Lett.*, 82, 2419 (2003).

- M.-H. Cho, D. W. Moo, S. A. Park, Y. K. Kim, K. Jeong, S. K. Kang, D.-H. Ko, S. J. Doh, J. H. Lee, and N. I. Lee, Appl. Phys. Lett., 84, 5243 (2004).

- S. J. Rhee, C. Y. Kang, C. S. Kang, R. Choi, C. H. Choi, M. S. Akbar, and J. C. Lee, *Appl. Phys. Lett.*, 85, 1286 (2004).

- C. S. Kang, H. J. Cho, K. Onishi, R. Nieh, R. Choi, S. Gopalan, S. Krishnan, J. H. Hari, and Jack C. Lee, *Appl. Phys. Lett.*, 81, 2593 (2002).

- G. Q. Lo, W. Ting, D. L. Kwong, J. Kuehne, and C. W. Magee, *IEEE Electron Device Lett.*, 11, 511 (1990).

- 17. P. J. Wright and K. C. Saraswat, IEEE Trans. Electron Devices, 36, 879 (1989).

- L. Vishnubhotla, T. P. Ma, H. H. Tseng, and P. J. Tobin, IEEE Electron Device Lett., 14, 196 (1993).

- 19. S. Lee and J. W. Park, J. Appl. Phys., 80, 5260 (1996).

- C. S. Lai, W. C. Wu, J. C. Wan, and T. S. Chaos, Extended Abstracts of the Solid State Device and Materials, p. 234 (2005).

- M. Inoue, S. Tsujikawa, M. Mizutani, K. Nomura, T. Hayashi, K. Shiga, J. Yugami, J. Tsuchimoto, Y. Ohno, and M. Yoneda, *Tech. Dig. - Int. Electron Devices Meet.*, 2005, 402.

- K. Seo, R. Sreenivasan, P. C. McIntyre, and Krishna C. Saraswat, Tech. Dig. Int. Electron Devices Meet., 2005, 406.

- Y. Mitani, H. Satake, Y. Nakasaki, and A. Toriumi, *IEEE Trans. Electron Devices*, 50, 2221 (2003).

- 24. P. J. Wright and K. C. Saraswat, IEEE Trans. Electron Devices, 36, 879 (1989).

- J. C. Wang, S. H. Chiao, C. L. Lee, T. F. Lei, Y. M. Lin, M. F. Wang, S. C. Chen,

C. H. Yu, and M. S. Liang, J. Appl. Phys., 92, 3936 (2002).

- 26. I. Rahat and J. Shappir, J. Appl. Phys., 76, 2279 (1994).