Materials Chemistry and Physics 45 (1996) 92-96

## Materials Science Communication

# High performance non-alloyed pseudomorphic high electron mobility transistors

C.K. Peng a,\*, W.H. Lan a, S.L. Tu a, S.J. Yang a, S.S. Chen b, C.C. Lin b

Materials R&D Center, Chung-Shan Institute of Science and Technology, P.O. Box 90008-8-6, Lung-tan, Taiwan, ROC

Institute of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan, ROC

Received 19 December 1994; accepted 25 September 1995

#### Abstract

We have studied the InAs/GaAs strained layer superlattice (SLS) structures as non-alloyed contacts applied to pseudomorphic high electron mobility transistors (PHEMTs) grown by the molecular beam epitaxy (MBE) system. Transmission line measurements with four point configurations showed that specific contact resistances between  $6.6 \times 10^{-7}$  and  $2.6 \times 10^{-6} \Omega$  cm<sup>2</sup> were obtained for the as-grown devices, with a linear correlation coefficient of 0.997. D.c. measurements of the as-grown PHEMT with 1  $\mu$ m gate showed a transconductance of 240 mS mm<sup>-1</sup>. Microwave measurements on the same device showed a cut-off frequency of 19 GHz and a maximum power gain frequency of 42 GHz. These results are comparable with those of devices with the conventional contact scheme. Meanwhile, since the non-alloying process maintains excellent surface morphology and sharp metal pad edges, AuGeNi type metals can be used in small dimension devices. In contrast, the conventionally alloyed devices showed rough surface morphology and zigzag edges, which may affect device processing and limit the usefulness of AuGeNi metal as the ohmic contact in small dimension devices.

Keywords: Strained layer superlattice; Non-alloyed contacts; Surface morphology

## 1. Introduction

Non-alloyed contact layers have attracted significant attention lately due to their superior properties in making low resistance ohmic contacts for III-V devices. Among them, InGaAs strained layers of various In compositions constitute an important category for such non-alloyed structures. It has been shown that contact resistances obtained for devices with non-alloyed contacts are comparable to, or even better than, those with conventional contacts. Meanwhile, because of the exemption of high temperature alloying processes, excellent device morphology may be maintained and simpler device processing and higher yield may be achieved.

While AuGe/Ni/Au has been used widely as a standard n-type contact metal to III-V epitaxial layers due

to the low eutectic point of AuGe alloy, the interaction of the alloy with the III-V layer underneath has led to ill defined edges which limit AuGeNi type metals for use in small dimension devices [1]. However, adoption of the non-alloyed structure may be a cure for such limitations. In addition, since the alloying mechanism is not responsible for achieving low contact resistance in such a structure, refractory metals such as Pt/Ti [2] or Al [3] can be used as the contact metal, thus expanding the flexibility of the process design and making such a contact scheme of great value for better and more stable performance.

When using a non-alloyed structure, the material that the non-alloyed structure is grown onto plays an important role in determining the contact resistance. As a general rule, material of a lower energy band and with a smaller conduction band discontinuity at the heterojunction makes a smaller energy barrier for electron transport among different layers, which leads to a better

<sup>\*</sup> Corresponding author.

n-type contact resistance and vice versa. Depending upon whether the conduction channel is composed of InGaAs, GaAs, or AlGaAs materials, non-alloyed specific contact resistances ranging between 10<sup>-8</sup> and  $10^{-5} \Omega \text{ cm}^2$  [4–6] have been obtained without annealing. Different non-alloyed structures have been studied in III-V epilayers; the major scheme includes the pure In As abrupt layer [4], the graded In GaAs layer [5], and the strained layer superlattice (SLS) composed of InAs, InGaAs, and GaAs layers, etc. [6], described in numerous publications. However, regardless of the extent of the study in using a non-alloyed structure for different device applications [7-9], there is very little published data on using an InAs/GaAs SLS as a non-alloyed structure on pseudomorphic high electron mobility transistor (PHEMT) devices.

## 2. Experimental

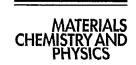

In this paper, we describe our investigatation of the application of the InAs/GaAs non-alloyed structures on PHEMT devices. The structure of the PHEMT consisted of an undoped 0.5  $\mu$ m GaAs buffer, an undoped 150 Å In<sub>0.15</sub>Ga<sub>0.85</sub>As pseudomorphic layer, a 30 Å Al<sub>0.25</sub>Ga<sub>0.75</sub>As undoped layer, a 500 Å Si doped Al<sub>0.25</sub>Ga<sub>0.75</sub>As layer of 2 × 10<sup>18</sup> cm<sup>-3</sup> doping concentration, and a 150 Å Si doped GaAs layer of 5 × 10<sup>18</sup> cm<sup>-3</sup> concentration. Above the PHEMT, a non-alloyed contact structure was grown which consisted of five periods of an InAs(10 Å)/GaAs(10 Å) SLS and finally a 100 Å InAs layer, all Si doped to 5 × 10<sup>18</sup> cm<sup>-3</sup> concentration, as shown in Fig. 1.

The samples investigated in this study were grown on (100) GaAs epi-ready undoped substrate using a Riber 32P molecular beam epitaxy (MBE) system. For outgassing, the substrate temperature was slowly increased to 620 °C for a total of about 30 min to desorb the surface oxide layer, before being brought down to 580 °C for the initiation of epitaxial growth. The entire device structure was grown at 580 °C under As-stabilized conditions, with the exception that the InGaAs channel layer was grown at 520 °C. The contact layers

Fig. 1. Device structure for the non-alloyed PHEMT. On the top was a five period superlattice of InAs/GaAs (10 Å/10 Å) followed by 100 Å of InAs layer as the non-alloyed contact structure.

were grown at between 450 and 500 °C due to the presence of the In-containing layers. The reflection of high energy electron diffraction (RHEED) showed clearly a two by four pattern, signalizing readiness for growth.

The transmission line contact structure was defined using standard photolithography and conventional wet chemical etching techniques. Mesa were formed using a phosphoric-based chemical etching solution. Contact patterns were then defined photolithographically, followed by evaporation and lift-off of AuGe/Ni/Au metals. As-grown samples; samples with 300 °C, 1 min annealing; samples with 460 °C, 1 min annealing; and the conventionally alloyed samples annealed at 460 °C for over 2 min were all prepared for comparison. Alloying of the samples was performed in a tube furnace under flowing H<sub>2</sub> for surface protection. Finally, the InAs and the underlying layers between the contacts were briefly etched to alleviate possible current conduction through these highly doped contact layers. In device processing, the same AuGe/Ni/Au metal system was used as source and drain contact metal, while Al was used as gate metal.

### 3. Results and discussion

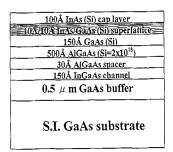

Contact resistances were measured using the wellknown extended transmission line model (ETLM). The ETLM test pattern consists of square pads of  $100 \times 100 \,\mu \text{m}$  dimensions. Each set of patterns is composed of six different gap spacings varying from 3 to 17  $\mu$ m. A four-point probe configuration was used for resistance measurements to eliminate possible errors introduced by the probe contact resistance. The specific contact resistance and sheet resistance were derived from a plot of the measured resistance versus gap spacing, using the least squares method to get a straight line fit to the experimental data. The ETLM plot is shown in Fig. 2, while the derived resistances are listed in Table 1. For the as-grown sample, from the y intercept and the slope, a contact resistance of 1.2  $\Omega$ and a transfer resistance of  $0.12 \Omega$  mm were obtained corresponding to a specific contact resistance of  $6.6 \times 10^{-7} \,\Omega$  cm<sup>2</sup>, with a linear correlation coefficient of 0.997. The slope of the straight line gave a sheet resistance of 220  $\Omega/\Box$ . For the slightly and heavily annealed samples, specific contact resistances between  $1 \times 10^{-6}$ and  $3 \times 10^{-6} \,\Omega$  cm<sup>2</sup> were obtained, while different batch processing had shown specific contact resistances in the high  $10^{-7} \Omega \text{ cm}^2$  region. By carefully carrying out the transmission line model (TLM) design and measurement process, the possible error between the model and the measured data can be made insignificant [4].

The AuGe/Ni/Au alloy has been the most used metal for making n-type ohmic contacts to III-V devices. However, the high temperature alloying process at

Fig. 2. Transmission line measurements of the device TLM pattern. Three different annealing conditions are shown, including (a) asgrown, (b) 300 °C, 1 min annealing, and (c) 460 °C, 1 min annealing. The inset shows the results after the conventional annealing treatment, where the decrease in the resistance for shorter spacing is evident.

Table 1 Transmission line measurements of the non-alloyed PHEMT samples

| M193                                  | As-grown                    | 300 °C, 1 min           | 460 °C, 1 min           |

|---------------------------------------|-----------------------------|-------------------------|-------------------------|

| $r_{\rm c} \; (\Omega \; {\rm cm}^2)$ | 6.6 × 10 <sup>-7</sup> 2.17 | 1.09 × 10 <sup>-6</sup> | 1.65 × 10 <sup>-6</sup> |

| Rs $(\Omega \; \mu {\rm m}^{-1})$     |                             | 2.14                    | 2.14                    |

440 °C or higher temperature needed for conventional contacts increases the surface roughness and causes lateral diffusion of the dopant atoms. It has been shown that annealing at 440 °C for 2 min leads to edge deterioration for a distance of up to 0.47  $\mu$ m [1], which may limit the use of the AuGeNi metal in GaAs submicron devices. For our test samples described earlier, we have taken top view pictures by optical microscope, at 800 × magnification, for comparison, as shown in Fig. 3. It is obvious that for sample (b), annealed at 300 °C for 1 min, the metal surface is as good as the as-grown samples (sample (a)), and the edges are straight and sharply defined. The surface gets rougher for sample (c), annealed at 460 °C for 1 min; however, the edges

Fig. 3b

Fig. 3d

Fig. 3. Top view of differently treated samples using an optical microscope, at 800 × magnification. The surface gets rougher at 460 °C annealing temperature, and then the edges become ill defined when the annealing lasts for longer than 2 min; (a) as-grown, (b) 300 °C, 1 min annealing, (c) 460 °C, 1 min annealing, and (d) 460 °C, >2 min annealing.

are still clearly defined. For the conventional annealing conditions of 460 °C for 2 min or longer, the surface becomes very rough and the edges zigzag. This latter phenomenon is consistent with the non-linearity of the TLM measurements, where the data for the 4  $\mu$ m, and especially the 3  $\mu$ m, spacing contact pads shows much smaller than expected resistance compared to a larger spacing contact pad, as shown in the inset of Fig. 2. On the other hand, the high linearity and low resistance TLM data of the as-grown and slightly annealed samples indicate the usefulness of the non-alloyed scheme. The uniform surface and well-defined edges of the non-alloyed metal pads may relax the limit in using AuGeNi type alloys for making low resistance ohmic contacts for even small dimension submicron devices.

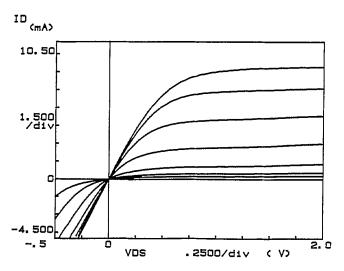

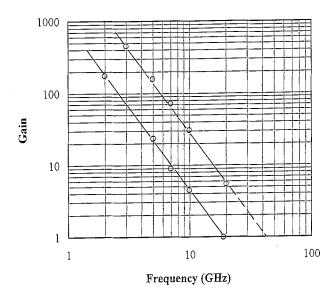

Van der Pauw Hall measurements on these nonalloyed devices showed electron mobilities of 3200 and 15 680 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and two-dimensional electron concentrations (2-DEG) of  $7.2 \times 10^{12}$  and  $3.9 \times 10^{12}$  cm<sup>-2</sup> at RT and 77 K, respectively. It should be noted that these high 2-DEG data in non-alloyed devices are partly contributed to by the non-alloyed layers. The d.c. drain current-voltage characteristics for the as-grown device with a 1 µm gate length and a source-drain spacing of  $3 \mu m$  are shown in Fig. 4. The I-V data show good pinch-off characteristics with a d.c. transconductance of 240 mS mm<sup>-1</sup> at a current level of 200 mA mm<sup>-1</sup>, and a good breakdown voltage around 6 V. The source resistance is less than 0.1  $\Omega$  mm. The S-parameter of the devices was measured using a Cascade microprobe station and a HP 8510C network analyzer. Linear extrapolation of these data is shown in Fig. 5 with a current gain cut-off frequency  $(f_t)$  around 19 GHz and a maximum oscillation frequency  $(f_{\text{max}})$  of 42 GHz. The bias voltages for this measurement were  $V_{\rm GS} = -0.3 \, {\rm V}$  and  $V_{\rm DS} = 2.0 \, {\rm V}$ . These values are com-

Fig. 4. D.c. transconductance of the as-grown non-alloyed PHEMT with 1  $\mu$ m gate length. The best gain was around 240 mS mm<sup>-1</sup>, gate biased between 0.4 V and -1.0 V at 0.2 V per step.

Fig. 5. Microwave current gain cut-off frequency ( $f_{\rm t}$ ) and power gain frequency ( $f_{\rm max}$ ) characteristics for the non-alloyed 1  $\mu m$  PHEMT.

parable with our other alloyed PHEMT devices of similar configuration but with a conventional GaAs(Si) cap layer instead of the non-alloyed contact layers.

#### 4. Conclusions

In conclusion, we have shown that the InAs/GaAs SLS can be used as an excellent non-alloyed ohmic contact for PHEMT devices. Specific contact resistances as low as  $6.6 \times 10^{-7} \,\Omega$  cm² were obtained, which are comparable to a good conventional contact with a high temperature annealing. Low contact resistances and well defined edges of the non-alloyed contact pads indicate that the limit of using AuGeNi metal in small dimension devices, due to interface interaction during alloying, can be lifted. The d.c. transconductance of the non-alloyed PHEMT was 240 mS mm<sup>-1</sup>. The current gain and the power gain cut-off frequencies were 19 and 42 GHz, respectively, for the 1  $\mu$ m gate device.

## Acknowledgements

The authors would like to thank C.J. Chang and K.F. Peng for their invaluable assistance in device fabrication and MBE growth.

## References

- [1] Y.C. Shih, M. Murakami, E.L. Wilkie and A.C. Callegari, J. Appl. Phys., 62 (1987) 582.

- [2] A. Katz, C.R. Abernathy and S.J. Pearton, Appl. Phys. Lett., 56 (1990) 1208.

- [3] M. Missous, E.H. Rhoderick and K.E. Singer, J. Appl. Phys., 59 (1986) 3189.

- [4] C.K. Peng, J. Chen, J. Chyi and H. Morkoc, J. Appl. Phys., 64 (1988) 429.

- [5] S. Kuroda, N. Harada, T. Katakami, T. Mimura and M. Abe, *IEEE Trans. Electron Devices*, 36 (1989) 2196.

- [6] C.K. Peng, G. Ji, N.S. Kumar and H. Morkoc, Appl. Phys. Lett., 53 (1988) 900.

- [7] N.S. Kumar, J.I. Chyi, C.K. Peng and H. Morkoc, Appl. Phys. Lett., 55 (1989) 570.

- [8] J.H. Huang, J.K. Abrokwah and W.J. Ooms, Appl. Phys. Lett., 61 (1992) 2455.

- [9] F. Ren, C.R. Abernathy, S.J. Pearton and P.W. Wisk, Appl. Phys. Lett., 64 (1994) 1508.