# HfSiON n-MOSFETs Using Low-Work Function HfSi<sub>x</sub> Gate

C. H. Wu, B. F. Hung, Albert Chin, *Senior Member, IEEE*, S. J. Wang, F. Y. Yen, Y. T. Hou, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang, *Fellow, IEEE*

Abstract—The authors have developed a novel high-temperature stable  $HfSi_x$  gate for high- $\kappa$  HfSiON gate dielectric. After a 1000 °C RTA, the  $HfSi_x/HfSiON$  devices showed an effective work function of 4.27 eV and a peak electron mobility of 216 cm<sup>2</sup>/V · s at 1.6-nm equivalent oxide thickness, with additional merit of a process compatible with current very large scale integration fabrication lines.

Index Terms—HfSi, HfSiON, n-MOSFETs.

## I. INTRODUCTION

O CONTINUE the very large scale integration (VLSI)  $\blacksquare$  scaling trend, the using metal gate and high- $\kappa$  gate dielectric are needed to reduce the dc power consumption and gate depletion [1]–[12]. However, one of the difficult challenges for metal-gate/high- $\kappa$  MOSFET is the large threshold voltage  $(V_t)$  by Fermi-level pinning that is opposite to scaling trend. To overcome this problem, low- and high-work-function metal gates are required to reduce the pinning effect. Previously, we have reported the  $Ir_xSi$  gate on HfAlON has high effective work-function ( $\phi_{m-\text{eff}}$ ) of 4.9 eV [12] and useful for p-MOS. For n-MOSFET, the novel TaC gate has shown low  $\phi_{m-\text{eff}}$ [1], [2]. However, the full silicidation (FUSI) gate [3]-[5], [8]-[13] for n-MOS is still needed to develop, which is due to the inherent advantage of the process compatibility with current poly-Si gate CMOS technology. In this letter, we have used the similar method of previously reported  $Ir_xSi$  for p-MOS [12] to develop the low-work-function  $HfSi_x$  gate for n-MOSFET. This is because the Hf has very low work function of 3.5 eV in the Periodic Table. The  $HfSi_x$  gate on HfSiON, formed by Hf deposition on thin amorphous Si, gives a low  $\phi_{m-\text{eff}}$  of 4.27 eV and a good electron mobility of 216 cm<sup>2</sup>/V  $\cdot$  s. In addition, the HfSi $_x$ /HfSiON can sustain a high rapid thermal annealing (RTA) temperature of 1000 °C that is compatible with current VLSI process line. Since both process and mechanism of HfSi<sub>x</sub> and Ir<sub>x</sub>Si, with respective low and high  $\phi_{m-\text{eff}}$ , are

Manuscript received April 18, 2006; revised June 5, 2006. This work was supported in part by National Science Council (NSC), Taiwan, R.O.C., under Grant 94-2215-E-006-056. The review of this letter was arranged by Editor B. Yu.

C. H. Wu and S. J. Wang are with the Institute of Microelectronics, Department of Electrical Engineering, National Cheng-Kung University, Tainan, Taiwan, R.O.C.

B. F. Hung and A. Chin are with the Department of Electronics Engineering, National Chiao-Tung University, University System of Taiwan, Hsinchu 300, Taiwan, R.O.C. (e-mail: achin@cc.nctu.edu.tw).

F. Y. Yen, Y. T. Hou, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang are with the Taiwan Semiconductor Manufacturing Corporation, Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LED.2006.880659

the same, these results indicate the high possibility to realize dual work-function metal-gate/high- $\kappa$  CMOS with large  $\phi_{m-\text{eff}}$  difference.

#### **II. EXPERIMENTAL PROCEDURE**

We have used the 12-in p-type Si wafers in this letter. After standard clean, the HfSiO was deposited by atomic-layer deposition (ALD) and the HfSiON was formed by applying direct nitrogen plasma to HfSiO surface. Then, amorphous Si with various thickness of 50 to 5 nm was deposited on HfSiON as a silicide layer and metal barrier for subsequently deposited 20-nm-thick Hf by physical vapor deposition (PVD). A Mo layer (30-nm thickness) was also deposited to cover the Hf to prevent oxidation. The MOS capacitor was formed by patterning and RTA at 1000 °C for 10 s. For n-MOSFET, additional 150-nm-thick amorphous Si was deposited on Hf/Si/HfSiON to prevent ion implantation penetration through gate, where the n<sup>+</sup> source–drain regions are formed by using a phosphorus ion implantation at 35 KeV. Then, the 1000 °C RTA was applied to activate the implanted dopant and the n-MOSFET was fabricated by this self-aligned gate first process. Since both the MOS capacitor and MOSFET follow the same high-temperature RTA, there should be no fundamental difference in gate stack even though they were covered by different Mo or poly-Si for device fabrication. Note that the FUSI  $HfSi_x$  gate is formed at high-temperature RTA and similar to previous  $Ir_xSi$  gate [12], which are different from conventional low-temperature salicide process. At such high 1000 °C RTA temperature, the fast silicidation reaching to the Si/HfSiON interface may also reduce the reaction of thin amorphous Si (5 nm) with high- $\kappa$  dielectric to cause Fermi-level pinning. For comparison, Al gated devices on HfSiON were also formed. The fabricated devices were characterized by capacitance–voltage (C-V) and current-voltage (I-V) measurements.

## **III. RESULTS AND DISCUSSION**

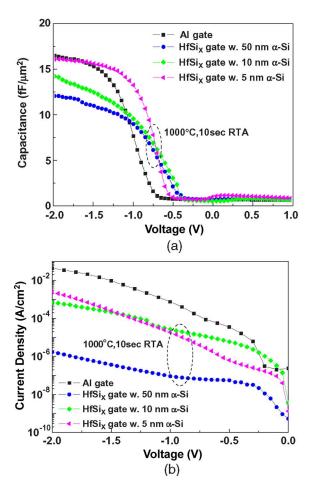

Fig. 1(a) and (b) shows the C-V and J-V characteristics for HfSi<sub>x</sub>/HfSiON and control Al/HfSiON capacitors, where the HfSi<sub>x</sub> gate was formed at 1000 °C RTA. The Al-gated capacitor with work-function of 4.1 eV was used as a reference [13] since it is known to have little Fermi-level pinning of low-temperature deposited pure metal gate on high- $\kappa$  dielectric [7]. For thicker amorphous Si of 50 and 10 nm on HfSiON, the capacitance density decreases with increasing the thickness of amorphous Si indicating in HfSi<sub>x</sub> gate on HfSiON not fully silicided.

Fig. 1. (a) C-V and (b)  $J_g-V_g$  characteristics for high-temperature RTA formed HfSi<sub>x</sub>/HfSiON and low-temperature Al/HfSiON capacitors. The device area was  $100 \times 100 \ \mu$ m. (Color version available online at http://ieeexplore.ieee.org.)

This in turn gives a higher flat-band voltage  $(V_{\rm fb})$  due to the Fermi-level pinning on high- $\kappa$  dielectric. This result is similar to the measured relative high  $\phi_{m-\text{eff}}$  of 4.5 eV in HfSi/SiO<sub>2</sub> devices [14], where the silicidation was formed at 600 °C-750 °C low-temperature RTA. In contrast, the HfSi<sub>x</sub> formed by thin 5-nm amorphous Si shows the same capacitance density with control Al gate suggesting the successful FUSI gate formation. From the C-V shift referenced to the control Al gate, an extracted  $\phi_{m\text{-eff}}$  of 4.27 eV is obtained for HfSi<sub>x</sub>/HfSiON that is suitable for n-MOS application. The low  $V_{\rm fb}$  and  $\phi_{m-{\rm eff}}$ for  $HfSi_x$  gate capacitors with 5-nm amorphous Si may be due to the Hf diffusion toward the HfSiON surface through thin amorphous Si that decreases the work function. This is the same mechanism for achieving high  $\phi_{m-\text{eff}}$  in high-workfunction metal-rich Ir<sub>x</sub>Si on high- $\kappa$  HfAlON [12]. high In addition, low leakage current of  $1.9 \times 10^{-5}$  A/cm at -1 V is measured at an equivalent oxide thickness (EOT) of  $\sim 1.6$  nm, which suggests the good thermal stability of  $HfSi_x$  gate on HfSiON dielectric even after 1000 °C RTA. Therefore, improved Fermi-level pinning, reasonable low  $\phi_{m-\text{eff}}$  of 4.27 eV and a low gate dielectric leakage current can be achieved in  $HfSi_x/HfSiON$  MOS capacitors at the same time.

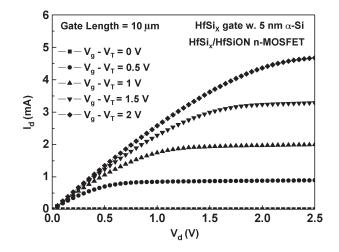

Fig. 2 shows the transistor  $I_d$ - $V_d$  characteristics as a function of  $V_g$ - $V_t$  for the 1000 °C RTA-annealed HfSi<sub>x</sub>/HfSiON

Fig. 2.  $I_d$ - $V_d$  characteristics of an HfSi<sub>x</sub>/HfSiON n-MOSFET. The amorphous Si on HfSiON was 5 nm and gate length was 10  $\mu$ m.

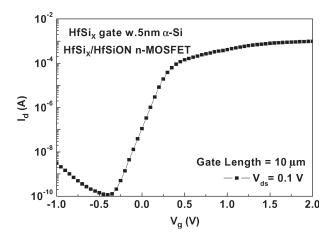

Fig. 3.  $I_d$ - $V_g$  characteristics an HfSi<sub>x</sub>/HfSiON n-MOSFET. The amorphous Si on HfSiON was 5 nm and gate length was 10  $\mu$ m.

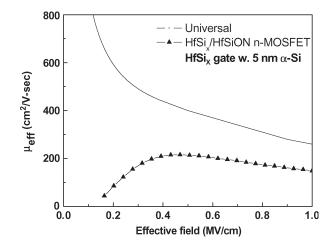

Fig. 4. Electron mobility of HfSi<sub>x</sub>/HfSiON n-MOSFETs.

n-MOSFETs. The well-behaved  $I_d-V_d$  curves indicate the good device performance by using an HfSi<sub>x</sub> gate. Fig. 3 displays  $I_d-V_g$  characteristics of the HfSi<sub>x</sub>/HfSiON n-MOSFETs. A low  $V_t$  of only 0.14 V was measured from the linear  $I_d-V_g$  plot, which is due to the low  $\phi_{m-\text{eff}}$  of 4.27 eV from the C-V measurements.

Fig. 4 shows the electron mobility extracted from the measured  $I_d-V_g$  curves of the n-MOSFETs. A peak electron mobility of 216 cm<sup>2</sup>/V · s was obtained for the HfSi<sub>x</sub>/HfSiON n-MOSFETs, which is close to published data in literature [15], [16].

# **IV. CONCLUSION**

Using the novel HfSi<sub>x</sub> gate formed by thin amorphous Si on HfSiON, good device performance has been obtained for n-MOSFETs with low  $\phi_{m-\text{eff}}$  and  $V_t$  values. This promising HfSi<sub>x</sub>/HfSiON n-MOSFET has additional merit of full process compatibility with current VLSI lines.

#### REFERENCES

- J. K. Schaeffer, C. Capasso, L. R. C. Fonseca, S. Samavedam, D. C. Gilmer, Y. Liang, S. Kalpat, B. Adetutu, H.-H. Tseng, Y. Shiho, A. Demkov, R. Hegde, W. J. Taylor, R. Gregory, J. Jiang, E. Luckowski, M. V. Raymond, K. Moore, D. Triyoso, D. Roan, B. E. White, Jr., and P. J. Tobin, "Challenges for the integration of metal gate electrodes," in *IEDM Tech. Dig.*, 2004, pp. 287–290.

- [2] H.-H. Tseng, C. C. Capasso, J. K. Schaeffer, E. A. Hebert, P. J. Tobin, D. C. Gilmer, D. Triyoso, M. E. Ramón, S. Kalpat, E. Luckowski, W. J. Taylor, Y. Jeon, O. Adetutu, R. I. Hegde, R. Noble, M. Jahanbani, C. El Chemali, and B. E. White, "Improved short channel device characteristics with stress relieved pre-oxide (SRPO) and a novel tantalum carbon alloy metal stack," in *IEDM Tech. Dig.*, 2004, pp. 821–824.

- [3] B. Tavel, T. Skotnicki, G. Pares, N. Carrière, M. Rivoire, F. Leverd, C. Julien, J. Torres, and R. Pantel, "Totally silicided (CoSi<sub>2</sub>) polysilicon: A novel approach to very low-resistive gate (~ 2Ω/□) without metal CMP nor etching," in *IEDM Tech. Dig.*, 2001, pp. 815–828.

- [4] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goollgweon, and M. R. Lin, "Transistors with dual work function metal gate by single full silicidation (FUSI) of polysilicon gates," in *IEDM Tech. Dig.*, 2002, pp. 367–370.

- [5] T. Nabatame, M. Kadoshima, K. Iwamoto, N. Mise, S. Migita, M. Ohno, H. Ota, N. Yasuda, A. Ogawa, K. Tominaga, H. Satake, and A. Toriumi, "Partial silicides technology for tunable work function electrodes on high-κ gate dielectrics-fermi level pinning controlled PtSi<sub>x</sub> for HfO<sub>x</sub>(N) pMOSFET," in *IEDM Tech. Dig.*, 2004, pp. 83–86.

- [6] C. S. Park, B. J. Cho, L. J. Tang, and D. L. Kwong, "Substituted aluminum metal gate on high-κ dielectric for low work-function and Fermi-level pinning free," in *IEDM Tech. Dig.*, 2004, pp. 299–302.

- [7] M. Koyama, Y. Kamimuta, T. Ino, A. Kaneko, S. Inumiya, K. Eguchi, M. Takayanagi, and A. Nishiyama, "Careful examination on the asymmetric V<sub>fb</sub> shift problem for Poly-Si/HfSiON gate stack and its solution by the Hf concentration control in the dielectric near the Poly-Si interface with small EOT expense," in *IEDM Tech. Dig.*, 2004, pp. 499–502.

- [8] K. Takahashi, K. Manabe, T. Ikarashi, N. Ikarashi, T. Hase, T. Yoshihara, H. Watanabe, T. Tatsumi, and Y. Mochizuki, "Dual workfunction Ni-silicide/HfSiON gate stacks by phase-controlled fullsilicidation (PC-FUSI) technique for 45 nm-node LSTP and LOP devices," in *IEDM Tech. Dig.*, 2004, pp. 91–94.

- [9] C. H. Huang, D. S. Yu, A. Chin, W. J. Chen, C. X. Zhu, M.-F. Li, B. J. Cho, and D. L. Kwong, "Fully silicided NiSi and germanided NiGe dual gates on SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Ge-On-Insulator MOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 319–322.

- [10] C. Y. Lin, M. W. Ma, A. Chin, Y. C. Yeo, C. Zhu, M. F. Li, and D. L. Kwong, "Fully silicided NiSi gate on La<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 24, no. 5, pp. 348–350, May 2003.

- [11] D. S. Yu, K. C. Chiang, C. F. Cheng, A. Chin, C. Zhu, M. F. Li, and D. L. Kwong, "Fully silicided NiSi : Hf/LaAlO<sub>3</sub>/ Smart-Cut-Ge-On-Insulator n-MOSFETs with high electron mobility," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 559–561, Aug. 2004.

- [12] C. H. Wu, D. S. Yu, A. Chin, S. J. Wang, M.-F. Li, C. Zhu, B. F. Hung, and S. P. McAlister, "High work function Ir<sub>x</sub>Si gates on HfAlON p-MOSFETs," *IEEE Electron Device Lett.*, vol. 27, no. 2, pp. 90–92, Feb. 2006.

- [13] Y.-C. Yeo, T.-J. King, and C. Hu, "Metal-dielectric band alignment and its implications for metal gate complementary metal-oxide-semiconductor technology," J. Appl. Phys., vol. 92, no. 12, pp. 7266–7271, Dec. 2002.

- [14] C. S. Park, B. J. Cho, and D. L. Kwong, "Thermally stable fully silicided Hf-Silicide metal-gate electrode," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 372–374, Jun. 2004.

- [15] A. Veloso, K. G. Anil, L. Witters, S. Brus, S. Kubicek, J.-F. de Marneffe, B. Sijmus, K. Devriendt, A. Lauwers, T. Kauerauf, M. Jurczak, and S. Biesemans, "Work function engineering by FUSI and its impact on the performance and reliability of oxynitride and Hf-silicate based MOSFETs," in *IEDM Tech. Dig.*, 2004, pp. 855–858.

- [16] S. J. Rhee, C. S. Kang, C. H. Choi, C. Y. Kang, S. Krishnan, M. Zhang, M. S. Akbar, and J. C. Lee, "Improved electrical and material characteristics of hafnium titanate multi-metal oxide n-MOSFETs with ultra-thin EOT (~ 8 Å) gate dielectric application," in *IEDM Tech. Dig.*, 2004, pp. 837–840.