Available online at www.sciencedirect.com

MATERIALS SCIENCE IN SEMICONDUCTOR PROCESSING

Materials Science in Semiconductor Processing 9 (2006) 711-715

# Comparison of InGaAs MOSFETs with germanium-on-insulator CMOS

Albert Chin<sup>a</sup>, C. Chen<sup>a</sup>, D.S. Yu<sup>a</sup>, H.L. Kao<sup>a</sup>, S.P. McAlister<sup>b,\*</sup>, C.C. Chi<sup>c</sup>

<sup>a</sup>Department of Electronics Engineering, Nano Sci. Tech. Ctr., Nat'l Chiao-Tung. University, University System of Taiwan, Hsinchu, Taiwan, ROC <sup>b</sup>Nat'l Research Council of Canada, Ottawa, Canada <sup>c</sup>Department of Physics, Nat'l Tsing Hua University, Hsinchu, Taiwan, ROC

Available online 2 October 2006

#### Abstract

High mobility channel materials such as Ge and compound semiconductors (CS) show promise for future generation MOSFETs. The challenge is to integrate these materials with a Si substrate and create good interfaces in the devices. Here we show dislocation-free CSOI and Ge-on-insulator (GOI) devices with good characteristics. The InAlAs/InGaAs/InAlAs-OI on Si MESFETs shows a mobility of 8100 cm<sup>2</sup>/V s. To reduce the leakage current an Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFET was fabricated. Good 451 cm<sup>2</sup>/V s mobility was obtained, higher than the 340 cm<sup>2</sup>/V s of GOI MOSFETs. However the marginally better mobility than GOI and 18X lower mobility than MESFETs indicate that the soft phonon scattering, high- $\kappa$  interface scattering and process variations are challenges for CS MOSFETs. In contrast, the GOI CMOS provides a simpler process and significantly higher electron and hole mobilities than its Si counterparts. (© 2006 Elsevier Ltd. All rights reserved.

Keywords: Compound semiconductor FETs; Germanium-on-insulator; InGaAs MOSFET

## 1. Introduction

To continue current VLSI scaling trends, high- $\kappa$  dielectrics and metal-gates [1–7] have to be integrated into CMOS to reduce the large leakage current and DC power consumption. However, the mobility degradation in metal-gate/high- $\kappa$ /Si CMOSFETs is a challenge. This mobility degradation is due to the ionic nature of the high- $\kappa$ dielectric, which leads to additional soft-phonon scattering. One method to overcome this problem is

fax: +16139907656.

to use strained-Si [4]; but this compromises the mobility enhancement, compared with the currently used poly-Si/SiON/strained-Si. A high mobility results in high transistor drive current, and is a key factor for achieving high circuit speeds. Thus it is desirable to improve the mobility beyond that of strained-Si devices. One candidate is Ge which shows significantly higher electron and hole mobilities compared with strained-Si. In this case, a Geon-insulator (GOI) structure is needed to reduce the transistor's off-state leakage current which arises from the small energy band gap of Ge [8–13]. III–V MOSFETs have the potential of providing even higher electron mobilities. However, the technology challenge is to integrate III–V material with Si and

<sup>\*</sup>Corresponding author. Tel.: +16139932514;

E-mail address: sean.mcalister@nrc.ca (S.P. McAlister).

<sup>1369-8001/\$ -</sup> see front matter  $\odot$  2006 Elsevier Ltd. All rights reserved. doi:10.1016/j.mssp.2006.08.066

form good interfaces in the MOSFET. Here we show the integration of a III–V material on Si, thus creating a compound semiconductor (CS) oninsulator (CSOI) device, using a process similar to that of our previous low-temperature wafer-bonded GOI [8–13]. The high electron mobility transistor (HEMT) [14–16] InAlAs/InGaAs/InAlAs-OI on Si showed a dislocation-free structure and an  $8100 \text{ cm}^2/\text{V}$  s electron mobility. For comparison we fabricated an Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFET, which gave a significantly lower mobility than the InAlAs/InGaAs HEMTs. However, the mobility value was higher than that of GOI devices [9]. The mobility improvement was limited by soft-phonon and interface scattering.

#### 2. Experimental procedure

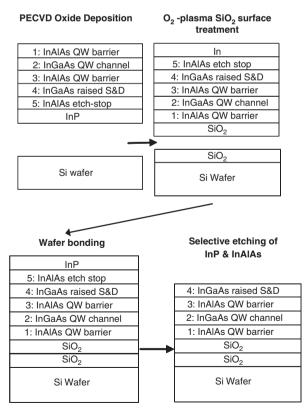

The first goal was to integrate the III–V material onto Si by forming a wafer-bonded CSOI structure, as shown in the process of Fig. 1. An inverted InAlAs/InGaAs/InAlAs HEMT structure was first grown on InP by molecular beam epitaxy (MBE) [14–16]. Then a SiO<sub>2</sub> layer was deposited on top of

Fig. 1. Schematic of the process used to form the InAlAs/ InGaAs/InAlAs-on-insulator structure.

the InAlAs and the target Si wafer. To enhance the wafer-bonding at low temperatures an  $O_2^+$  exposure was used to activate the SiO<sub>2</sub> surfaces, and the bonding was performed at 400 °C [8–12]. Then the InP substrate was thinned down followed by selective etching of the InP and InAlAs. InGaAs is a good etch stop when using an HCl-based solution, compared with InP and InAlAs. To fabricate a CSOI HEMT, the top n<sup>+</sup> InGaAs contact layer over the gate was recess-etched to the InAlAs, where the gate electrode was formed by a Ti/Au Schottky contact. Then the source–drain contacts were formed by NiGeAu deposition [16].

A high- $\kappa$ /III–V MOSFET was also investigated in this study [17]. We used MBE to grow the 20 nm-InGaAs/300 nm-InAlAs quantum-well (QW) structure on an InP substrate. Then the Al<sub>2</sub>O<sub>3</sub> gate dielectric was deposited by RF sputtering from an Al<sub>2</sub>O<sub>3</sub> source. To study the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface properties, the InGaAs surface with or without in situ atomic Al layer coverage was investigated before exposing the InGaAs to air. The Al-gate/ Al<sub>2</sub>O<sub>3</sub>/InGaAs/InAlAs MOSFET was fabricated by gate patterning, self-aligned Al/Yb deposition, and 400 °C rapid thermal annealing (RTA) to form the Schottky source-drain (SSD) contacts [18-20]. Such SSD contacts for InGaAs can avoid the difficult challenge of  $n^+$  ion implantation activation for source-drain contacts, as used in conventional CMOSFET fabrication.

## 3. Results and discussion

# 3.1. InAlAs/InGaAs/InAlAs-OI transistor

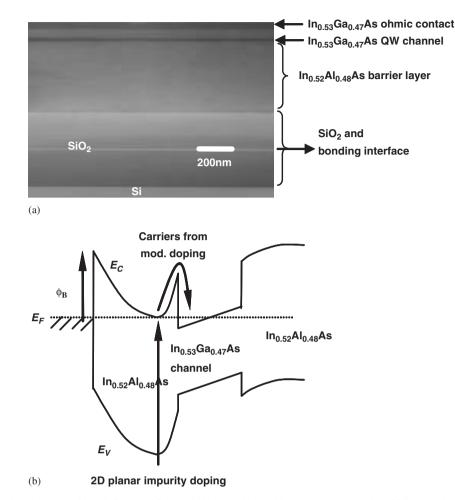

An InAlAs/InGaAs/InAlAs-OI device was examined by cross-sectional transmission electron microscopy (TEM), as shown in Fig. 2(a), where no dislocations were seen at the resolution shown—this is important for high-yield IC fabrication. The white line in the middle of the SiO<sub>2</sub> layer is due to the O<sub>2</sub>plasma treatment, which is important for low temperature (400 °C) wafer-bonding and good mechanical strength. The CSOI design, which uses an inverted HEMT layer structure, is shown in Fig. 2(b), and consists of an InAlAs barrier layer, twodimensional (2D) planar n<sup>+</sup> Si doping layer, InAlAs top QW barrier, InGaAs QW channel, and InAlAs bottom QW barrier on the SiO<sub>2</sub>/Si substrate.

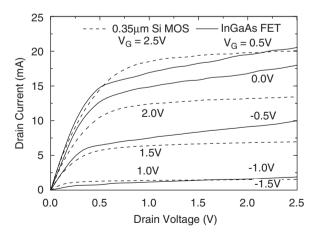

Fig. 3 shows the  $I_d$ - $V_d$  characteristics of a 1.1 µm InAlAs/InGaAs/InAlAs CSOI transistor. For comparison, data for a 0.35 µm SiO<sub>2</sub>/Si MOSFET are

Fig. 2. Cross-sectional TEM and band diagram of the InAlAs/InGaAs/InAlAs FET structure. The middle InGaAs provides the channel, confined by InAlAs barriers. The upper InGaAs in the gate region was etched before depositing the metal gate.

Fig. 3. Comparison of the  $I_d$ - $V_d$  characteristics of InAlAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As CSOI MESFETs on Si (1.1 µm × 50 µm) with 0.35 µm Si MOSFETs.

included. A high drive current of  $0.41 \text{ mA}/\mu\text{m}$  was measured, which is close to that for a  $0.35 \,\mu\text{m} \, \text{SiO}_2/\text{Si}$  MOSFET. Such a high drive current in the CSOI HEMT is due to the high electron mobility of  $8100 \,\text{cm}^2/\text{V}$ s, which was determined using Hall measurements. The carrier density was  $2.2 \times 10^{12} \,\text{cm}^{-2}$ . The mobility value is nearly an order of magnitude higher than that for conventional Si and strained-Si devices.

# 3.2. Metal-gate/high-к Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFET

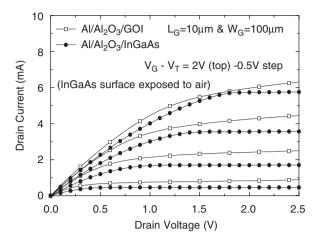

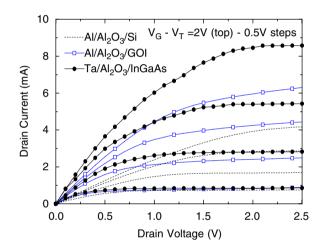

It is well known that HEMTs or MESFETs are unsuitable for VLSI circuits due to their large gate leakage current. Therefore, a high- $\kappa$ /InGaAs MOSFET structure is preferred over a HEMT design. Fig. 4 shows the  $I_d$ - $V_d$  characteristics of an Al-gate/high- $\kappa$  Al<sub>2</sub>O<sub>3</sub>/InGaAs QW MOSFET.

Fig. 4.  $I_d$ - $V_d$  characteristics of Al/Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFETs on insulating InAlAs/InP, with the InGaAs surface exposed to air.

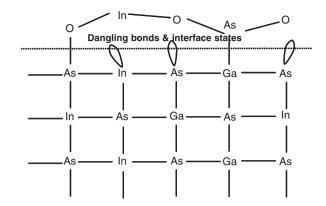

For comparison, the  $I_d$ - $V_d$  data from an Al<sub>2</sub>O<sub>3</sub>/GOI device is also shown [9]. Unfortunately, the drive current of the Al/Al<sub>2</sub>O<sub>3</sub>/InGaAs nMOSFET is even less than that of an Al/Al<sub>2</sub>O<sub>3</sub>/GOI transistor. It is known from MBE studies that the native oxides of InGaO<sub>3</sub> and As<sub>2</sub>O<sub>3</sub> on InGaAs have weak bond strengths, requiring desorption temperatures of only ~500 °C. Therefore, the poor mobility of the Al/Al<sub>2</sub>O<sub>3</sub>/InGaAs transistor may be due to these interfacial native oxides beneath the Al<sub>2</sub>O<sub>3</sub> gate dielectric, as shown in the schematic diagram in Fig. 5. Such a weakly bonded poor-quality oxide may give a high concentration of interface states by forming dangling bonds. This can limit III–V MOSFET development.

To overcome this problem the top InGaAs surface was covered by an in situ deposited Al layer a few atoms thick, which was converted to  $Al_2O_3$  after air exposure, and during subsequent  $Al_2O_3$  sputtering under  $O_2^+$  conditions. Fig. 6 shows the  $I_d-V_d$  characteristics of  $Al_2O_3/InGaAs$  MOSFETs with an in situ covered InGaAs surface. Significantly improved drain current is shown—better than the  $Al_2O_3/GOI$  and  $Al_2O_3/Si$  MOSFETs.

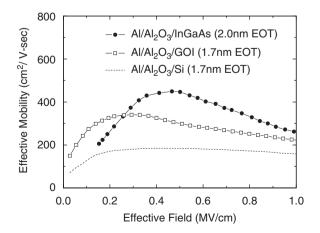

Such a drive current improvement is due to the higher electron mobility, as shown in Fig. 7. The mobility of the  $Al_2O_3/InGaAs$  transistor, with an improved interface, was  $451 \text{ cm}^2/\text{V}$  s, which is 1.3 times higher than for an  $Al_2O_3/GOI$  MOSFET, and 2.5 times higher than that for the  $Al_2O_3/\text{Si}$  device. However, this mobility in  $Al_2O_3/InGaAs$  MOSFET is still ~18 times lower than that of the HEMT, indicating that the soft-phonon and interface

Fig. 5. Schematic diagram of III–V oxide on InGaAs. Unlike  $SiO_2/Si$ , more dangling bonds may be formed with the weak  $InGaO_3$  and  $As_2O_3$  oxide on the InGaAs.

Fig. 6.  $I_d$ – $V_d$  characteristics of Al/Al<sub>2</sub>O<sub>3</sub>/InGaAs UTB MOS-FETs on insulating InAlAs/InP, with an in situ covered Al<sub>2</sub>O<sub>3</sub> on the InGaAs.

Fig. 7. Electron mobility of an  $Al_2O_3/InGaAs$  MOSFET compared with Si and GOI devices.

715

scattering are still limiting factors for the  $Al_2O_3/$ InGaAs MOSFETs, even through the interface was covered by in situ deposited Al and converted into  $Al_2O_3$ .

#### 4. Conclusions

We have fabricated defect-free InAlAs/InGaAs/InAlAs-OI on Si, and high drive current CSOI HEMTs with a high  $8100 \text{ cm}^2/\text{V}$ s mobility. The Al<sub>2</sub>O<sub>3</sub>/InGaAs MOSFET with an in situ interface treatment gave 1.3 or 2.5 times higher mobility than that of Al<sub>2</sub>O<sub>3</sub>/GOI or Al<sub>2</sub>O<sub>3</sub>/Si MOSFETs, respectively, but an inferior mobility compared with the HEMT structure. This suggests that the soft-phonon and interface scattering are the mechanisms limiting the performance.

## Acknowledgment

The authors at NCTU would like to thank the partial support by the NSC (94-2215-E-009-062) of Taiwan.

## References

- Schaeffer JK, Capasso C, Fonseca LRC, Samavedam S, Gilmer DC, Liang Y, et al. Tech Dig IEDM 2004:287.

- [2] Tseng H-H, Capasso CC, Schaeffer JK, Hebert EA, Tobin PJ, Gilmer DC, et al. Tech Dig IEDM 2004:821.

- [3] Nabatame T, Kadoshima M, Iwamoto K, Mise N, Migita S, Ohno M, et al. Tech Dig IEDM 2004:83.

- [4] Datta S, Dewey G, Doczy M, Doyle BS, Jin B, Kavalieros J, et al. Tech Dig IEDM 2003:653.

- [5] Yu DS, Chin A, Wu CH, Li M-F, Zhu C, Wang SJ, et al. Tech Dig IEDM 2005:649.

- [6] Chin A, Liao CC, Lu CH, Chen WJ, Tsai C. Tech Dig Symp VLSI 1999:135.

- [7] Chin A, Wu YH, Chen SB, Liao CC, Chen WJ. Tech Dig Symp VLSI 2000:16.

- [8] Huang CH, Yang MY, Chin A, Chen WJ, Zhu CX, Cho BJ, et al. Symp VLSI 2003:119.

- [9] Huang CH, Yu DS, Chin A, Chen WJ, Zhu CX, Li M-F, et al. Tech Dig IEDM 2003:319.

- [10] Yu DS, Chin A, Laio CC, Lee CF, Cheng CF, Chen WJ, et al. Tech Dig IEDM 2004:181.

- [11] Yu DS, Chiang KC, Cheng CF, Chin A, Zhu C, Li MF, et al. IEEE Electron Device Lett 2004;25:559.

- [12] Chin A, Kao HL, Tseng YY, Yu DS, Chen CC, McAlister SP, et al. Tech Dig ESSDERC 2005:285.

- [13] Low T, Li MF, Fan WJ, Tyam NS, Yeo Y-C, Zhu C, et al. Tech Dig IEDM 2004:151.

- [14] Chin A, Chang TY. J. Vac. Sci. Technol. B 1990;8:364.

- [15] Chin A, Chang TY, Ourmazd A, Monberg EM, Chang AM. J Cryst Growth 1991;111:466.

- [16] Chin A, Liao CC, Tsai C. IEEE Electron Device Lett 1997;18:157.

- [17] Ren F, Hong MW, Hobson WS, Kuo JM, Lothian JR, Mannaerts JP, et al. Tech Dig IEDM 1996:943.

- [18] Zhu S, Yu HY, Whang SJ, Chen JH, Shen C, Zhu C, et al. IEEE Electron Device Lett 2004;25:268.

- [19] Zhu S, Chen J, Li M-F, Lee SJ, Singh J, Zhu CX, et al. IEEE Electron Device Lett 2004;25:565.

- [20] Zhu S, Li R, Lee SJ, Li MF, Du A, Singh J, et al. IEEE Electron Device Lett 2005;26:81.