## Strain enhanced DC-RF performance of 0.13 µm nMOSFETs on flexible plastic substrate

A. Chin, H.L. Kao, C.H. Kao, C.C. Liao, Y.Y. Tseng and C.C. Chi

A 14.3% saturation current  $I_{d,sat}$  improvement and 0.75 dB minimum noise figure ( $NF_{\rm min}$ ) at 10 GHz were measured by applying  $\sim$ 0.7% tensile strain for 16 finger, 0.13  $\mu$ m RF MOSFETs with thin-body (40  $\mu$ m) substrate mounted on plastic. These excellent results for mechanical-strain on DC-RF MOSFETs are better than those of SiN-capped 90 nm strained-Si nMOSFETs and consistent with device simulations.

Introduction: To integrate the Si-base RF integrated circuits (ICs) on high-resistivity Si substrate [1] is an important technology. Since the passive devices have a poor Q-factor [1-4] arising from the low resistivity (10 Ω-cm) VLSI-standard Si substrates, integrating RF ICs on insulating plastic provides better passive devices at lower cost than those on lossy VLSI-standard Si substrates. In addition, the thin-body Si IC on plastic is useful for flexible electronics, RF ID, wireless displays and system-on-plastic [5, 6]. The thin-body Si substrate provides flexibility for applying mechanical strain. In this Letter we report the DC and RF performance of 0.13 µm thin-body (40 µm) Si MOSFETs on plastic with mechanical strain. The saturation drain current  $(I_{d,sat})$  was improved 14.3% and a 0.75 dB lower minimum noise figure ( $NF_{min}$ ) was obtained at 10 GHz for 0.13  $\mu$ m MOSFETs on plastic with  $\sim$ 0.7% tensile strain. The excellent performance is better than that for SiN-capped, 90 nm node, strained-Si nMOS (11%) [7]. Such DC-RF performance improvements were confirmed by TMA simulations for strained  $0.13\,\mu m$ MOSFETs. They arise from the thin body thickness  $(t_b)$  and high flexibility, where the surface strain increases with  $1/t_b^2$  [8]. The RF noise improvement fits well an analytical  $NF_{min}$  equation [9], and is due to the increase in the  $g_m$  and the RF gain under strain.

Experiment procedure: In this study we used 180 µm low-cost, highly-insulating polyethylene substrates, which had a resistivity of  $10^8$ – $10^9$  Ω-cm. The multiple-gate-finger 0.13 μm RF MOSFETs with microstrip line layout were designed on 8-inch wafers at an IC foundry [9]. The multiple-gate-finger structure can reduce the thermal noise generated from gate resistance. The microstrip line layout can shield the RF noise generated in the lossy Si substrate network, instead of a conventional coplanar waveguide (CPW) structure [9]. To achieve integration onto plastic, we first thinned-down the Si substrate from 500 to 40 µm using the chemical mechanical polish (CMP) process and then glued it onto a 180 µm-thick plastic (Fig. 1a). Fig. 1b shows the large surface strain on 40 μm Si substrate. Owing to the flexibility of the thinned-down Si substrate, we can apply large mechanical strain onto the Si substrate without any cracking to measure the DC and RF characteristic. Furthermore, the surface strain can be calculated using ANSYS 8.0 simulation software and the device characteristics were simulated under various applied tensile strain using TMA process-device simulation software. The DC, S-parameters and noise figure were measured using HP4155C, a HP8110 network analyser and the ATN-NP5B noise parameter measurement system, respectively [9].

Fig. 1 Image of die with multiple-gate-finger 0.13  $\mu m$  RF MOSFET on transparent plastic, and high flexibility of ~40  $\mu$ m-thick Si substrate ( $t_b$ ) under mechanical strain

a Image of die with multiple-gate-finger 0.13  $\mu m$  RF MOSFET on transparent plastic (held by hand)

Substrate of die thinned to  $\sim$ 40  $\mu m$

*b* High flexibility of ~40 μm-thick Si substrate ( $t_b$ ) under mechanical strain (proportional to  $1/t_b^2$ )

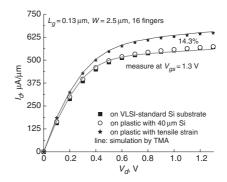

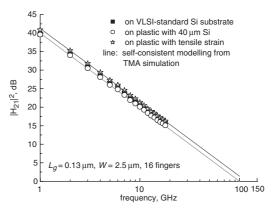

Results and discussion: The DC characteristics of 16-gate-finger 0.13 µm RF MOSFETs on a VLSI-standard Si substrate, and on plastic, are shown in Fig. 2. The  $I_d-V_d$  characteristics show almost identical before and after thinning and mounting on plastic. Similarly, little change appeared in the measured RF current gain  $|H_{21}|^2$ , as depicted in Fig. 3. It is indicated that the thinned-down process did not damage the devices. This improvement over the previous ICP etching and thinning process [5] is due to the fact that CMP technique avoids plasma damage. In addition, Figs. 2 and 3 show the modelling data using the TMA process-device simulations software. Good agreement between measured and simulated  $I_d-V_d$  and  $|H_{21}|^2$  were obtained using the accurate TMA process-device simulations on VLSI-standard Si substrate.

Fig. 2 Measured and simulated  $I_d-V_d$  for 16-gate-finger 0.13  $\mu m$  RF MOSFETs on VLSI-standard substrate and on plastic with 40  $\mu m$  Si, with or without tensile strain

Solid lines are TMA-simulated data for VLSI-standard Si substrate and on plastic under  $\sim\!0.7\%$  tensile strain

Fig. 3 Measured and simulated  $|H_{21}|^2$  against frequency for 16-gate-finger 0.13  $\mu m$  RF MOSFETs on VLSI-standard substrate and on plastic with 40  $\mu m$  Si with or without tensile strain

Line is modelled data

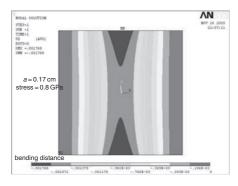

Because of the flexibility of the thinned-down Si substrate it can be subjected to large levels of strain. The large surface strain  $(\varepsilon = 3aF/bt_b^2E)$  [8] results from the applied force (F) associated with a bending distance (a) and width (b). We calculated the surface tensile strain using ANSYS 8.0 software, as shown in Fig. 4. The bending distance is about 0.17 cm when we applied 0.8 GPa stress on 40  $\mu$ m Si substrate. Therefore, tensile strain is 0.7% (=0.8 GPa/115 GPa) where the Young's modulus of Si is 115 GPa.

In this condition, we measured the  $I_d-V_{ch}$  S-parameter and  $NF_{\rm min}$ . Figs. 2 and 3 show the  $I_d-V_{ch}$  characteristic and RF current gain  $|H_{21}|^2$  of 16-gate-finger 0.13  $\mu$ m RF MOSFETs on plastic with and without tensile strain, respectively. The  $f_T$  is extracted on RF current gain  $|H_{21}|^2$  equal to 1. Under the applied 0.7% tensile strain on plastic, the  $I_{d,sat}$  increased 14.3% and the unity-gain cutoff frequency  $f_T$  increased from 103 to 118 GHz. Such improved  $I_{d,sat}$  and  $f_T$  under strain is also confirmed by TMA simulation and also shown in Figs. 2 and 3. It is indicated that the increased  $I_{d,sat}$  and  $f_T$  are the result of increased electron mobility which is the result of the reduced intervalley scattering under tensile strain [10]. A large improvement occurred compared with SiNcapped 90 nm strained-Si nMOS (11%) [7], owing to the  $1/t_b^2$  dependence of the strain for thin-body Si.

Fig. 4 Mechanical stress calculated using ANSYS 8.0 simulation software

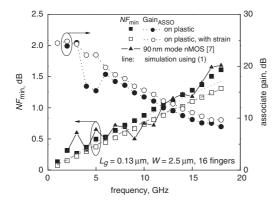

Fig. 5 shows the  $NF_{\rm min}$  and associated gain of 0.13  $\mu$ m transistors under tensile strain. The  $NF_{\rm min}$  decreased from 0.89 to 0.75 dB and the associate gain increased from 14.2 to 15.3 dB at 10 GHz. The  $NF_{\rm min}$  is lower than the unstrained case over the whole frequency range. The lower  $NF_{\rm min}$  from strain arises through [9]:

$$NF_{\min} \cong 1 + 2\gamma (1 + g_m R_g / \gamma)^{0.5} f / f_T$$

(1)

The close agreement between the measured and simulated  $NF_{\rm min}$ , as shown in Fig. 5, indicates that the lower  $NF_{\rm min}$  arises from the strain-improved  $f_T$ . The  $NF_{\rm min}$  is better than those for 90 nm node SiN-capped strained-Si nMOS [7] in Fig. 5. The large DC-RF improvements with strain are some of the advantages of thin-Si-body flexible electronics on plastic.

Fig. 5 Frequency dependence of  $NF_{min}$  and associate gain of body-thinned 16-gate-finger 0.13  $\mu m$  RF MOSFETs on plastic under strain

Conclusion: High performance was achieved for thin-body  $0.13 \, \mu m$  MOSFETs on plastic. These devices showed excellent low noise performance (0.75 dB at 10 GHz), high associated gain (15.3 dB)

and a  $14.3\%~I_{d,sat}$  increase. Such high performance RF transistors are improved by thinning the substrate and making it flexible to apply tensile strain.

Acknowledgments: We thank the Chip Implementation Center (CIC) and G.W. Huang at the National Nano-Device Lab, Taiwan, for help with RF measurements.

© The Institution of Engineering and Technology 2006 17 April 2006

Electronics Letters online no: 20061035

doi: 10.1049/el:20061035

A. Chin, H.L. Kao, C.C. Liao and Y.Y. Tseng (Department of Electronic Engineering, National Chiao Tung University, Nano Science Technology Center, University System of Taiwan, Hsinchu 30050, Taiwan, Republic of China)

E-mail: achin@cc.nctu.edu.tw

C.H. Kao (Department of Accounting Information, Takming College, Taiwan, Republic of China)

C.C. Chi (Department of Physics, National Tsing Hua University, Hsinchu, Taiwan, Republic of China)

## References

- Ohguro, T., et al.: 'Improvement of high resistivity substrate for future mixed analog-digital application'. Symp. on VLSI Tech. Dig., 2002, pp. 158–159

- Yu, D.S., et al.: 'Narrow-band band-pass filters on silicon substrates at 30 GHz', IEEE MTT-S Int. Microw. Symp. Dig., 2004, 3, pp. 1467–1470

- 3 Chin, A., et al.: 'RF passive devices on Si with excellent performance close to ideal devices designed by electro-magnetic simulation', *IED Int. Electron Device Mtg Tech. Dig.*, 8–10 December 2003, pp. 375–378

- 4 Chan, K.T., et al.: Low RF loss and noise of transmission lines on Si substrates using an improved ion implantation process', IEEE MTT-S Int. Microw. Symp. Dig., 2003, 2, pp. 963–966

- 5 Kao, H.L., et al.: 'Very low noise RF nMOSFETs on plastic by substrate thinning and wafer transfer', *IEEE Microw. Wirel. Compon. Lett.*, 2005, 15, (11), pp. 757–759

- 6 Takayama, T., et al.: 'A CPU on a plastic film substrate'. Symp. on VLSI Tech. Dig., June 2004, pp. 230–231

- 7 Ghani, T., et al.: 'A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors', IED Int. Electron Device Mtg Tech. Dig., 8–10 December 2003, nn 11 6 1–11 6 3

- 8 Zhao, W., et al.: 'Partially depleted SOI MOSFETs under uniaxial tensile strain', IEEE Trans. Electron Devices, 2004, 54, pp. 317–323

- 9 Kao, H.L., et al.: 'Modeling RF MOSFETs after electrical stress using low-noise microstrip line layout'. RF IC Symp. Dig., June 2005, pp. 157–160

- 10 Paul, D.J.: 'Si/SiGe heterostructures: from material and physics to devices and circuits', Semicond. Sci. Technol., 2004, 19, pp. R75–R108