## Study on the interface thermal stability of metal-oxide-semiconductor structures by inelastic electron tunneling spectroscopy

Chih-Feng Huang, Bing-Yue Tsui, Pei-Jer Tzeng, Lurng-Shehng Lee, and Ming-Jinn Tsai

Citation: Applied Physics Letters 88, 262909 (2006); doi: 10.1063/1.2219140

View online: http://dx.doi.org/10.1063/1.2219140

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/88/26?ver=pdfcov

Published by the AIP Publishing

### Articles you may be interested in

Aluminum, oxide, and silicon phonons by inelastic electron tunneling spectroscopy on metal-oxide-semiconductor tunnel junctions: Accurate determination and effect of electrical stress J. Appl. Phys. **96**, 5042 (2004); 10.1063/1.1775299

Thermal stability of epitaxial Pt films on Y 2 O 3 in a metal-oxide—Si structure Appl. Phys. Lett. **83**, 4758 (2003); 10.1063/1.1632541

Interface characterization of Si 3 N 4 /Si/GaAs heterostructures after high temperature annealing J. Vac. Sci. Technol. B **16**, 3032 (1998); 10.1116/1.590338

Microcrystalline oxide-incorporated new diffusion barrier for dynamic random access memory and ferroelectric random access memory capacitor electrode

J. Vac. Sci. Technol. A 15, 2781 (1997); 10.1116/1.580823

Thermal stability of Si 3 N 4 /Si/GaAs interfaces Appl. Phys. Lett. **70**, 1263 (1997); 10.1063/1.118547

# Study on the interface thermal stability of metal-oxide-semiconductor structures by inelastic electron tunneling spectroscopy

### Chih-Feng Huang<sup>a)</sup> and Bing-Yue Tsui

Department of Electronics Engineering, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu, Taiwan 300, Republic of China and Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu, Taiwan 300, Republic of China

#### Pei-Jer Tzeng, Lurng-Shehng Lee, and Ming-Jinn Tsai

Electronics Research and Service Organization, Industrial Technology Research Institute, Chutung, Hsinchu, Taiwan 310, Republic of China

(Received 25 November 2005; accepted 1 June 2006; published online 30 June 2006)

The bias polarity-dependent inelastic electron tunneling spectroscopy is employed to detect the thermal stability of the  $Ta-Pt/SiO_2/Si$  and  $Ta-Pt/HfO_2/Si$  structures. This work provides a direct evidence that the Fermi-level pinning of metal gates is counted for the generation of extrinsic states due to interface interaction. A  $Ta_2O_5$  layer forms at the  $Ta-Pt/SiO_2$  interface during thermal annealing whereas only an intermittent Ta-O bond is observed at the  $Ta-Pt/HfO_2$  interface. Although the heat of formation of  $HfO_2$  is lower than that of  $SiO_2$ , Si presumably diffuses into  $HfO_2$  layer and replaces Hf atoms during the high-temperature annealing. © 2006 American Institute of Physics. [DOI: 10.1063/1.2219140]

Metal gates are expected to replace polysilicon gates and to integrate with high dielectric constant materials beyond 45 nm technology node. Several kinds of metal gates such as pure metals, binary alloys, metal nitrides, and metal silicides have been proposed. One of the most important issues with those gates is that the effective work function  $(\phi_{m,\text{eff}})$  is thermally unstable. It is suspected that the thermal instability of  $\phi_{m,\text{eff}}$  is caused by the interface reaction between metal electrode and gate dielectric. However, no direct evidence has been reported because interface analysis is more difficult than surface analysis. The typical analysis techniques such as Fourier transform infrared spectroscopy, x-ray photoelectron spectroscopy, secondary ion mass spectroscopy, and electron spin resonance spectroscopy may not be suitable for interface analysis on a real device structure.

Recently, a promising interface analysis technique called inelastic tunneling spectroscopy (IETS) was employed to analyze the chemical bonds at the electrode and dielectric interface by detecting the interaction between tunneling electrons and phonons. <sup>9-11</sup> The IETS can further detect the interface bonding near the upper interface or lower interface of a metal-insulator-semiconductor (MIS) or metal-insulator-metal structure by using the bias polarity-dependent characteristic. <sup>11</sup> In this work, the polarity-dependent IETS technique is used to probe the thermal stability of Ta–Pt alloy/SiO<sub>2</sub>/Si and Ta–Pt alloy/HfO<sub>2</sub>/Si MIS structures.

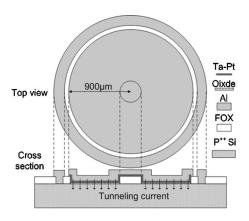

The MIS capacitors were fabricated on (100)-oriented, p-type silicon wafers with a resistivity of lower than 0.001  $\Omega$  cm. The metal electrode area was 0.024 cm<sup>2</sup>. The capacitors have a shape of two concentric rings isolated by a thick thermally grown field oxide (FOX) in order to keep a uniform electric field as shown in Fig. 1. After field oxide patterning, wafers were cleaned by the standard cleaning process followed by dipping in HF solution for 10 s. For the SiO<sub>2</sub> samples, a 1.5 nm thick SiO<sub>2</sub> layer was thermally grown in a mixture of N<sub>2</sub> and O<sub>2</sub> at 700 °C for 1 min fol-

lowed by annealing in N2 ambient at 900 °C for 10 min in the same furnace. For the HfO<sub>2</sub> samples, a 3 nm thick HfO<sub>2</sub> layer was deposited at 300 °C using HfCl<sub>4</sub> as precursor and H<sub>2</sub>O vapor as oxidant in an atomic layer deposition system. No HfO<sub>2</sub> postdeposition annealing was followed immediately. Metal gates were patterned by lift-off process. The Ta-Pt alloy was deposited in a cosputtering system to a thickness of 55 nm, and the sputtering powers of Ta and Pt targets were set to dc 30 W and rf 30 W, respectively. After the lift-off process, post-metal-annealing was performed at 500 or 800 °C in N<sub>2</sub> ambience for 30 s in the rapid thermal annealing system. This was followed by substrate contact opening using conventional lithography and wet etching processes. Finally, a 500 nm thick aluminum (Al) layer was deposited as local interconnects and probing pads by thermal evaporation. The IETS measurement was performed by a modulation technique using a lock-in amplifier. The details of the system setup can be found elsewhere. 12 Measurement was performed at 15 K and the ac modulation is 2 mV with a frequency of 5 KHz. The dc resolution is 2 mV.

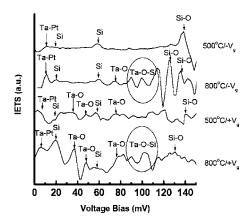

The IETS spectra of 500 and 800 °C annealed Ta-Pt/SiO<sub>2</sub>/Si samples are shown in Fig. 2. The asymmet-

FIG. 1. The schematic top view and cross section of the test structure.

a) Electronic mail: jeffhuang.ee90g@nctu.edu.tw

FIG. 2. The inelastic electron tunneling spectra of Ta-Pt/SiO<sub>2</sub>/degenerated Si samples annealed at 500 and 800 °C.

ric IETS was caused by different bias polarities. The negative gate bias qualitatively reflects the interaction between electrons and phonons near the bottom interface. 11 The signals of Si substrate and SiO<sub>2</sub> phonon modes have been well identified and analyzed by previous researchers. 11,13 The signals of Si phonons were at 20 and 59 mV and the signals of SiO<sub>2</sub> phonons ranged broadly from 130 to 170 mV. 9,11,14 Several additional peaks occurred on the 800 °C annealed sample (800 °C/ $-V_g$  in Fig. 2). The peak at 77 mV (equal to 640 cm<sup>-1</sup>) was attributed to amorphous Ta<sub>2</sub>O<sub>5</sub>. <sup>15,16</sup> The observation proved the reaction between Ta of Ta-Pt alloy and SiO<sub>2</sub>. The obvious and intense peaks between 90 and 120 mV were qualitatively attributed to deteriorated SiO2 instead of Ta<sub>2</sub>O<sub>5</sub> since the main peak of Ta–O was located only at 77 mV. Those peaks between Ta-O modes and Si-O modes represent Ta-O-Si (metal-O-Si) bonds or imperfect SiO<sub>2</sub> (SiO<sub>x</sub>) due to the chemical reaction between Ta-Pt gate and SiO<sub>2</sub>. Î7,18 The spectra at positive gate bias were more sensitive to the phonon interaction near the Ta-Pt alloy gate. In addition to the Ta–O peak at 77 mV, the other Ta–O peaks at 38 and 49 mV were also observed. 11,12 Both the 500 and 800 °C samples revealed Ta-O bond and the higher and sharper peaks of the 800 °C annealed sample indicated the growth of tantalum oxide.

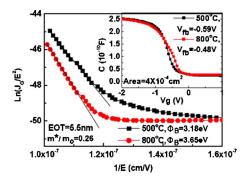

To investigate the electrical effects of chemical reaction at the interface between Ta–Pt and SiO<sub>2</sub>, the work function of Ta–Pt gate was analyzed. In Fig. 3, the barrier height of Ta–Pt electrode extracted by the Fowler-Nordheim tunneling plot increases from 3.18 to 3.65 eV as the annealing temperature increases from 500 to 800 °C. The inset shows that

FIG. 3. Fowler-Nordheim plot of the Ta-Pt/SiO<sub>2</sub> (5.5 nm)/Si structure after annealing at 500 and 800 C for 30 °C. The  $m^*/m_o$ =0.26 is used to calculate the barrier height  $(\Phi_8)$  (Ref. 24). The inset shows the relative C-V curves.

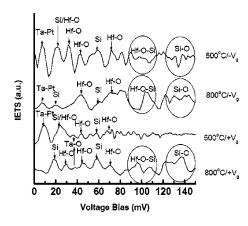

FIG. 4. The inelastic electron tunneling spectra of Ta–Pt/HfO $_2$ /degenerated Si samples annealed at 500 and 800  $^{\circ}$  C.

the equivalent oxide thickness is almost unchanged after  $800\,^{\circ}$ C annealing while the flatband voltage ( $V_{tb}$ ) changes from the -0.69 to -0.48 V. These observations imply that the effective work function is increased after  $800\,^{\circ}$ C annealing and is consistent with the published data that low work function (near the silicon conduction band) of metal gate tends to the midgap of silicon energy band after high-temperature annealing. It is believed that the Fermi-level pinning (work function offset) originates from the chemical reaction between metal gate and  $SiO_2$  gate dielectric.

Figure 4 shows the IETS spectra of the Ta-Pt/HfO<sub>2</sub>/Si samples annealed at 500 and 800 °C. Both the negative and positive biased IETS spectra were measured. The peaks were identified based on the literature values. 12,17,18 The peaks of Si-O and Hf-O-Si vibration modes of the 500 °C annealed sample were weaker than those of the 800 °C annealed sample, and those of the negative-gate-bias IETS spectra were stronger than those of the positive ones. These observations imply the growth of silicon oxide at the lower interface during high-temperature annealing, which has been clearly detected by the transmission electron microscope (TEM) inspection. The shift of the main peak of Hf–O vibration modes after high-temperature annealing was reasonably caused by the crystallization, where the main peak of the 500 °C annealed sample was located at 32 mV and was lower than the main peak of the 800 °C annealed sample located at 43 mV. <sup>18</sup> A special peak of the Hf–O vibration mode at 71 mV observed on both the 500 and 800 °C annealed samples was attributed to the hafnium silicate but not to pure HfO<sub>2</sub>. <sup>17,19</sup> This implied that the interfacial layer contained the mixture of Hf-O and O-Si bonds, i.e., Hf silicate. Another special peak at 38 mV was suspected to the Ta-O vibration mode and was only observed on the positive-gatebias IETS spectra.<sup>20</sup> The peak was small and did not grow even after high-temperature annealing. The Ta-Pt/HfO<sub>2</sub> interface was further inspected by high resolution transmission electron microscopy. An intermittent monolayer material was observed at the interface which corresponded to the weak IETS peaks of both 500 and 800 °C samples. The monolayer Ta-O bond might be formed during the Ta-Pt alloy deposition.

The reaction at the upper interface of HfO<sub>2</sub> is self-limited while the reaction at the lower interface of HfO<sub>2</sub> is continuous during the high-temperature annealing. The reactant, oxygen, surely does not come from the annealing ambient since the Ta–Pt alloy is not oxidized at the upper inter-

face. Those mean that the oxygen should come from the HfO<sub>2</sub> layer. The existence of Hf silicate sensibly implies that the oxygen comes from the broken Hf-O bond. However, the postulation that HfO<sub>2</sub> releases oxygen atoms during hightemperature annealing while the oxygen only reacts with Si but not Ta is unreasonable since the heat of formations of  $HfO_2$ ,  $Ta_2O_5$ , and  $SiO_2$  are -271, -230, and -210 Kcal/mol, respectively. Besides, the Hf-O, Ta-O, and Si-O bonds are more stable than the Si-Si bond since the bonding energies of Hf-O, Ta-O, Si-O, and Si-Si are 801.7, 799.1, 799.6, and 326.8 KJ/mol, respectively. 21 Therefore, it is presumed that the oxygen is not thermally decomposed from the HfO<sub>2</sub>, but it is more reasonable that the Si atom diffuses into the HfO<sub>2</sub> layer from the Si substrate and directly replaces the Hf atom. <sup>21–23</sup> On the other hand, it is difficult for Ta atom to diffuse into the HfO2 layer, and HfO2 is more stable than Ta<sub>2</sub>O<sub>5</sub> so that only an intermittent Ta-O bond forms at the Ta-Pt/HfO<sub>2</sub> interface. While the Ta-Pt alloy is deposited on the SiO<sub>2</sub>, the lower heat of formation of Ta<sub>2</sub>O<sub>5</sub> than that of  $SiO_2$  results in a more stable  $Ta_2O_5$ .

In summary, IETS spectroscopy provides a direct inspection of thermal instability at the interface of the MIS structure. The analysis of results provides a direct evidence that the Fermi-level pinning of Ta–Pt metal gates on  $\mathrm{SiO}_2$  is counted for the generation of extrinsic states due to the formation of the tantalum oxide. The  $\mathrm{Ta-Pt/HfO}_2$  interface is more thermally stable than the  $\mathrm{HfO}_2/\mathrm{Si}$  interface. Hf silicate formation during thermal annealing is detected at the latter interface by our IETS analysis.

This work is supported by the National Science Council of Taiwan, Republic of China under Contract No. NSC-94-2215-E-009-004.

- <sup>2</sup>D. Ha, P. Ranade, Y.-K. Choi, J.-S. Lee, T.-J. King, and C. Hu, Jpn. J. Appl. Phys., Part 1 **42**, 1979 (2003).

- <sup>3</sup>P. Xuan and J. Bokor, IEEE Electron Device Lett. **24**, 634 (2003).

- <sup>4</sup>B.-Y. Tsui and C. F. Huang, IEEE Electron Device Lett. **24**, 153 (2003).

- <sup>5</sup>J. Westlinder, T. Schram, L. Pantisano, E. Cartier, A. Kerber, G. S. Lujan, J. Olsson, and G. Groeseneken, IEEE Electron Device Lett. **24**, 550 (2003).

- <sup>6</sup>C. Ren, H. Y. Yu, J. F. Kang, Y. T. Hou, M.-F. Li, W. D. Wang, D. S. H. Chan, and D.-L. Kwong, IEEE Electron Device Lett. **25**, 123 (2004).

- <sup>7</sup>H. Y. Yu, C. Ren, Y.-C. Yeo, J. F. Kang, X. P. Wang, H. H. H. Ma, M.-F. Li, D. S. H. Chan, and D.-L. Kwong, IEEE Electron Device Lett. **25**, 337 (2004).

- <sup>8</sup>M. S. Joo, B. J. Cho, N. Balasubramanian, and D.-L. Kwong, IEEE Electron Device Lett. 25, 716 (2004).

- <sup>9</sup>W.-K. Lye, E. Hasegawa, T.-P. Ma, R. C. Barker, Y. Hu, J. Kuehne, and D. Frystak, Appl. Phys. Lett. **71**, 2523 (1997).

- <sup>10</sup>P. Balk, S. Ewert, S. Schmitz, and A. Steffen, J. Appl. Phys. **69**, 6510 (1991)

- <sup>11</sup>W. He and T. P. Ma, Appl. Phys. Lett. **83**, 2605 (2003).

- <sup>12</sup>Y. Wang, R. R. Mallik, and P. N. Henriksen, Rev. Sci. Instrum. **64**, 890 (1993).

- <sup>13</sup>A. G. Chynoweth, R. A. Logan, and D. E. Thomas, Phys. Rev. **125**, 877 (1962)

- <sup>14</sup>G. Salace, C. Petit, and D. Vuilaume, J. Appl. Phys. **91**, 5896 (2002).

- <sup>15</sup>R. A. B. Devine, Appl. Phys. Lett. **68**, 1924 (1996).

- <sup>16</sup>H. Ono and K.-I. Koyanagi, Appl. Phys. Lett. 77, 1431 (2000).

- <sup>17</sup>K. T. Queeney, M. K. Weldon, J. P. Chang, Y. J. Chabal, A. B. Gurevich, J. Sapjeta, and R. L. Opila, J. Appl. Phys. **87**, 1322 (2000).

- <sup>18</sup>D. A. Neumayer and E. Cartier, J. Appl. Phys. **90**, 1801 (2001).

- <sup>19</sup>M. A. Quevedo-Lopez, J. J. Chambers, M. R. Visokay, A. Shanware, and L. Colombo, Appl. Phys. Lett. 87, 12902 (2005).

- <sup>20</sup>D.-G. Park, T.-H. Cha, K.-Y. Lim, H.-J. Cho, T.-K. Kim, S.-A. Jang, Y.-S. Suh, V. Misra, I.-S. Yeo, J.-S. Roh, J. W. Park, and H.-K. Yoon, Tech. Dig. Int. Electron Devices Meet. **2001**, 671.

- <sup>21</sup>Periodic table of elements by The University of Sheffield and WebElements Ltd., UK, http://www.webelements.com/

- <sup>22</sup>T. H. Moo, M.-H. Ham, and J.-M. Myoung, Appl. Phys. Lett. **86**, 102903 (2005).

- <sup>23</sup>J.-C. Lee, S.-J. Oh, M. Cho, C. S. Hwang, and R. Jung, Appl. Phys. Lett. 84, 1305 (2004).

- <sup>24</sup>D. K. Schroder, Semiconductor Material and Device Characterization, 2nd ed. (Wiley, New York, 1998), p. 393.

<sup>&</sup>lt;sup>1</sup>International Technology Roadmap for Semiconductors (ITRS), 2003 Edition (Semiconductor Industry Association (SIA), 2003), http://public.itrs.net