# Novel Dual-Metal Gate Technology Using Mo–MoSi<sub>x</sub> Combination

Tzung-Lin Li, Wu-Lin Ho, Hung-Bin Chen, Howard C.-H. Wang, Chun-Yen Chang, *Life Fellow, IEEE*, and Chenming Hu, *Fellow, IEEE*

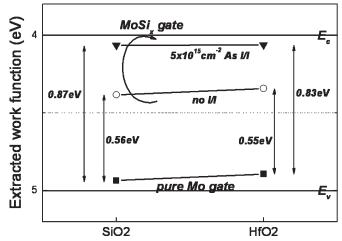

Abstract-A novel dual-metal gate technology that uses a combination of Mo-MoSi<sub>x</sub> gate electrodes is proposed. An amorphous-Si/Mo stack was fabricated as a gate electrode for the n-channel device. It was thermally annealed to form  $MoSi_x$ . Pure Mo served as the gate electrode for the p-channel device. The work functions of MoSi<sub>x</sub> and pure Mo gates on SiO<sub>2</sub> are 4.38 and 4.94 eV, respectively, which are appropriate for devices with advanced transistor structures. The small increase in the work function (< 20 meV) and the negligible equivalent oxide thickness variation (< 0.08 nm) after rapid thermal annealing at 950 °C for 30 s also demonstrate the excellent thermal stabilities of Mo and MoSi<sub>x</sub> on SiO<sub>2</sub>. Additional arsenic ion implantation prior to silicidation was demonstrated further to lower the work function of MoSi<sub>x</sub> to 4.07 eV. This approach for modulating the work function makes the proposed combination of  $Mo-MoSi_x$  gate electrodes appropriate for conventional bulk devices. The developed dual-metal-gate technology on HfO2 gate dielectric was also evaluated. The effective work functions of pure Mo and undoped MoSi<sub>x</sub> gates on HfO<sub>2</sub> are 4.89 and 4.34 eV, respectively. A considerable work-function shift was observed on the high- $\kappa$  gate dielectric. The effect of arsenic preimplantation upon the work function of the metal silicide on HfO2 was also demonstrated, even though the range of modulation was a little reduced.

${\it Index\ Terms} \hbox{--} \hbox{--Dual-metal\ gate,\ molybdenum,\ silicide,\ thermal\ stability.}$

# I. INTRODUCTION

CCORDING to the International Roadmap for Semiconductors (ITRS) [1], the introduction of high- $\kappa$  gate-dielectric materials and dual-metal-gate electrodes with appropriate work functions will be required in the near future to reduce gate-leakage current [2]–[4] and eliminate boron penetration and polydepletion effect [4], [5]. For conventional bulk devices, the required work functions  $(\Phi_m)$  of n- and p-channel devices are about 4 and 5 eV, respectively. However, the required  $\Phi_m$  values for n- and p-channel devices with advanced transistor structures, such as FinFET or ultrathin-body (UTB) MOSFETs, are about 4.4–4.6 and 4.8–5.0 eV, respectively [6]. Since the work function of the metals cannot easily be modulated, a straightforward dual-metal gate CMOS process has been proposed, but it degrades the integrity of the gate

Manuscript received September 8, 2005; revised March 2, 2006. This work was supported by the Taiwan Semiconductor Manufacturing Company under Contract 94C222. The review of this paper was arranged by Editor S.-I. Kimura.

T.-L. Li, W.-L. Ho, H.-B. Chen, and C.-Y. Chang are with the Institute of Electronics, National Chiao-Tung University, Hsinchu 30050, Taiwan, R.O.C. (e-mail: tlli.ee89g@nctu.edu.tw).

H. C.-H. Wang and C. Hu are with the Taiwan Semiconductor Manufacturing Company, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TED.2006.874227

dielectric by exposing it to the metal etchant [7]. A novel dualmetal-gate technology based on the full silicidation (FUSI) of polysilicon gates has also been reported [8]-[10], and dopants in the polysilicon are believed to be responsible for providing the difference between the work functions of n- and p-type metal-silicide (MeSi) gates [11], [12]. The major advantage of the FUSI method is the ease of process integration. Moreover, since the source/drain dopant activation annealing will be performed prior to silicide formation, the requirement for the thermal stability of MeSi can be alleviated. Thermal treatment prior to silicidation process, however, results in the incomplete elimination of boron penetration in p-channel devices [13]. Additionally, the impurity doping dose has been reported not to help modulate the  $\Phi_m$  of FUSI-MeSi, such as NiSi and PtSi, on HfON high- $\kappa$  gate dielectric because of the Fermilevel pinning effect [14]. Consequently, the FUSI gate on high- $\kappa$  gate dielectric becomes single work function metalgate candidate and its application is strictly limited. Therefore, Nabatame et al. presented a partial silicides technology that uses n<sup>+</sup>-polysilicon and n-type MeSi as gate electrodes for n- and p-channel devices, respectively [14]. This approach, however, suffers from the poly depletion effect in n-channel devices.

The Hf–Si bond has been suggested to be responsible for the pinning effect and the large device threshold voltages observed in polysilicon and FUSI gates with an Hf-based gate dielectric [15]. The Hf-Si bond is likely to have been formed during the deposition of polysilicon and may not be eliminated by subsequent annealing or silicidation process [16]. The amount of Hf-Si bonds, which strongly depends on the type and quality of the gate/dielectric interface, becomes the key parameter in controlling the Fermi-level pinning effect. The suppression of the pinning effect by replacing HfO2 with Si-rich Hf-silicates [16]–[19] or Al-incorporating HfAlON [20], [21] has been proposed. Also, the use of capping layer such as SiO<sub>2</sub> [19] or  $Al_2O_3$  [16] on the high- $\kappa$  gate dielectric has been reported to reduce effectively the Hf-Si interaction. These improvements, however, come at the expense of a large equivalent oxide thickness (EOT), a reduced average dielectric constant and poor scalability. In addition to the use of the capping layer and the modulation of the Hf concentration in Hf-based high- $\kappa$ gate dielectric, a novel retardation of the pinning effect has been proposed using phase-controlled FUSI (PC-FUSI) gates [22], [23]. Although a negligible  $\Phi_m$  difference between NiSi and Ni<sub>3</sub>Si can be obtained on SiO<sub>2</sub>, a small (about 0.25-0.33 eV)  $\Phi_m$  difference can be achieved on Hf-based high- $\kappa$ gate dielectric, and is believed to be caused by Fermi-pinning

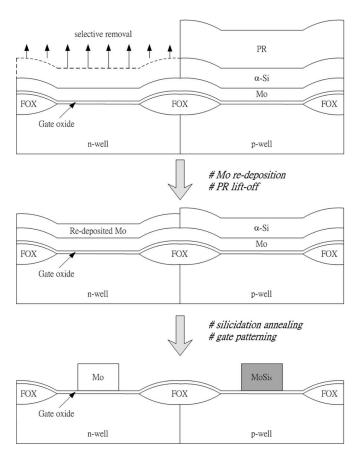

Fig. 1. Schematic illustration of the proposed novel dual-metal-gate technology that uses the combination of  $Mo-MoSi_x$  gate electrodes.

relaxation associated with the metal-rich silicide (Ni<sub>3</sub>Si), which reduces the number of Hf–Si bonds at the gate-dielectric interface.

This work proposes the use of a combination of  $Mo-MoSi_x$ gate electrodes for dual-metal-gate technology. In view of the process integration, the MoSi<sub>x</sub> gate was formed by the FUSI of the  $\alpha$ -Si/Mo/gate-dielectric stack to prevent the exposure of the gate dielectric in the channel region to the metal etchant. The extracted  $\Phi_m$  values for  $MoSi_x$  and as-deposited pure Mo gates on SiO<sub>2</sub> are appropriate for devices with advanced transistor structures. The small increase in  $\Phi_m$  and the negligible variation in EOT after rapid thermal annealing (RTA) at 950 °C demonstrate the superior thermal stabilities of Mo and MoSi<sub>x</sub> on SiO<sub>2</sub>. Implanting additional arsenic prior to silicidation process can further lower the  $\Phi_m$  of MoSi<sub>x</sub> to make it suitable for n-channel bulk devices. The combination of pure Mo and MoSi<sub>x</sub> gates on HfO<sub>2</sub> was also demonstrated to provide a considerable  $\Phi_m$  difference. Moreover, n-type MoSi<sub>x</sub> can still have a lower  $\Phi_m$  value than undoped MoSi<sub>x</sub> on HfO<sub>2</sub>, even though the range of the work-function modulation is a little smaller than that on  $SiO_2$ .

# II. EXPERIMENTS

Fig. 1 schematically depicts the proposed novel dual-metalgate technology that combines Mo and  $MoSi_x$ . The first layer metal and  $\alpha$ -Si are deposited over the entire wafer in sequence on the gate dielectric. A noncritical lithography step is performed, and an appropriate wet-etching recipe should be investigated to remove selectively the  $\alpha$ -Si from the p-MOS side. The redeposition of Mo in the p-MOS region is needed after the selective removal of  $\alpha$ -Si, to equalize the thickness of the gate electrode across the entire wafer. Consequently, potential gate patterning and spacer formation challenges can be prevented. Since only Mo remains in the p-MOS region, it solely determines the work function of the p-MOS gate electrode. The remaining  $\alpha$ -Si/Mo stack in the n-MOS region will be subsequently transformed into molybdenum silicide and determine the work function of the n-MOS gate electrode. In this process, the gate dielectric in the channel region will not be exposed to the metal etchant, therefore, the side effects encountered in the straightforward dual-metal-gate technology [7] can be prevented. Notably, the thermal stability of the selected metal film on the gate dielectric should be sufficiently high to ensure that no interaction occurs between the metal and the gate dielectric during the silicidation and following hightemperature processes. The (110) Mo gate has been reported to have a work function that is appropriate for the p-channel device [24], [25] and exhibits high thermal stability (1000 °C) on the SiO<sub>2</sub> gate dielectric [26]. Accordingly, pure Mo will be adopted as the first-layer metal so that the  $\Phi_m$  value and the thermal stability of the formed  $MoSi_x$  become the main issue.

MOS capacitors with Mo/gate dielectric/n-Si and  $\alpha$ -Si/ Mo/gate dielectric/n-Si structures were fabricated on 6-in Si wafers. After the local-oxidation-of-silicon (LOCOS) isolation, thermal SiO<sub>2</sub> (3, 6, and 9 nm) or metal organic chemical vapor deposition (MOCVD) HfO<sub>2</sub> (5, 7.5, and 10 nm) was deposited as the gate dielectric. According to the ITRS, the thickness of the gate electrode must be reduced as the MOSFET devices are miniaturized [1]. To meet this criterion, a thin (10 nm) layer of Mo was sputter deposited on top of the gate dielectrics for all samples. Some samples were followed by sputter deposition of  $\alpha$ -Si (25 nm). The gate electrodes were then patterned by reactive ion etching (RIE) using Cl<sub>2</sub>-based chemistry. After the gate-electrode patterning, some of the samples with an  $\alpha$ -Si/Mo/gate-dielectric stack were then subjected to arsenic implantation  $(1\times 10^{15}, 5\times 10^{15}~\text{cm}^{-2}).$  The low implantation energy (10 keV), corresponding to a projected implant-range  $(R_p)$  value of one half of the thickness of the  $\alpha$ -Si layer, was employed to avoid the direct implantation of dopants into the channel region. Samples with an  $\alpha$ -Si/Mo/gate-dielectric stack were then subjected to successive RTA (600 °C, 1 min. + 700 °C, 1 min. + 800 °C, 1 min.) in  $N_2$  ambient for  $MoSi_x$  formation. All samples were then subjected to 950 °C RTA for 30 s to evaluate the thermal stabilities of the gate electrodes. The flatband voltage  $(V_{\rm FB})$  and EOT were extracted from the measured capacitance-voltage (C-V) curve using the quantum mechanical C-V (QMCV) simulator [27]. The  $\Phi_m$  values of the gate electrodes were then extrapolated from the  $V_{\rm FB}$ -EOT plots by setting the electron affinity  $(\chi)$  of the Si substrate to 4.05 eV.

# III. RESULTS AND DISCUSSION

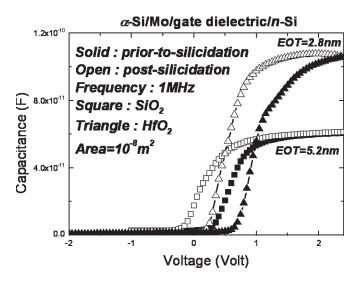

Fig. 2 shows the C–V characteristics of the capacitor (MOSCAP) devices gated by  $\alpha$ -Si/Mo stack before and after

Fig. 2. C-V characteristics of MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub> (or HfO<sub>2</sub>)/n-Si structure before and after silicidation annealing.

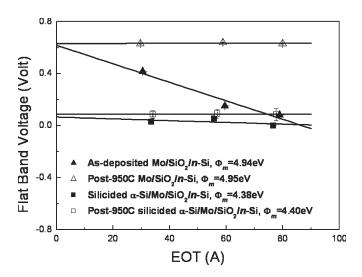

Fig. 3.  $V_{\rm FB}$  versus EOT plots of Mo and MoSi $_x$  gated MOSCAP devices before and after 950 °C RTA for thermal-stability evaluation.

silicidation annealing. A negative postsilicidation flatband voltage shift without EOT variation can be observed for both  $\mathrm{SiO}_2$  and  $\mathrm{HfO}_2$  gate dielectrics. The change in the work function of the gate electrode and the reduction of the fixed charge can contribute to the flat-band voltage shift.

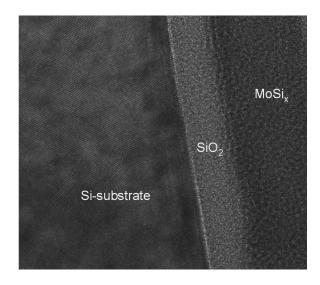

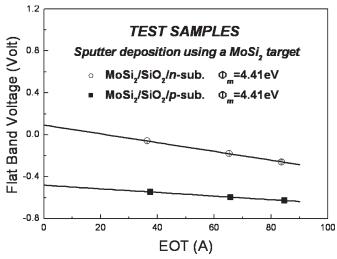

Fig. 3 reveals that both as-deposited Mo/SiO $_2$  and post-silicidation  $\alpha$ -Si/Mo/SiO $_2$  samples exhibit linear behavior in  $V_{\rm FB}$ -EOT plots. The large fixed oxide charge density in the as-deposited Mo/SiO $_2$  sample may be caused by the damage done by sputtering and can be reduced by high-temperature annealing. The  $\Phi_m$  values of the as-deposited pure Mo film and the formed MoSi $_x$  on SiO $_2$  are extracted to be 4.94 and 4.38 eV, respectively, so the  $\Phi_m$  difference is 0.56 eV. Moreover, the small increase in  $\Phi_m$  (Mo: 10 meV; MoSi $_x$ : 20 meV) along with the negligible EOT variation (Mo: 0.08 nm; MoSi $_x$ : 0.06 nm) after RTA at 950 °C demonstrates the excellent thermal stabilities of Mo and MoSi $_x$  films on SiO $_2$ . Fig. 4 shows the TEM image of the postsilicidation sample, confirming the smooth gate electrode/SiO $_2$  interface.

Fig. 4. TEM image of the postsilicidation  $\alpha$ -Si/Mo/SiO<sub>2</sub> stack.

Fig. 5. Work-function extraction of MoSi<sub>2</sub> films that were sputter deposited on SiO<sub>2</sub> using the MoSi<sub>2</sub> target.

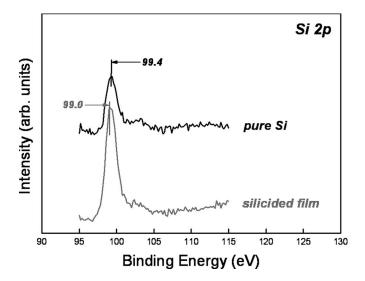

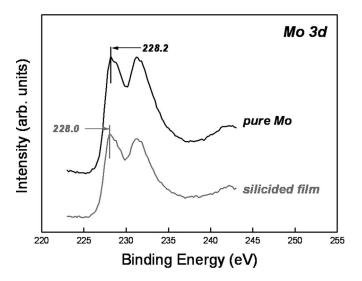

MoSi<sub>2</sub> has been reported to be likely the only silicide phase observed for the Mo:Si = 1 : 2 stacked samples annealed at a temperature of higher than 600 °C [28]. MOSCAP devices gated by the sputtering deposition of MoSi2 using the MoSi2 target were also fabricated. The  $V_{\rm FB}$  versus EOT plots of MoSi<sub>2</sub>/SiO<sub>2</sub>/n-Si and MoSi<sub>2</sub>/SiO<sub>2</sub>/p-Si structures yielded the work function of the MoSi<sub>2</sub> film that was sputter deposited on SiO<sub>2</sub> using the MoSi<sub>2</sub> target at 4.41 eV, regardless of the dopant of the substrate, as shown in Fig. 5. Moreover, the X-ray photoelectron spectroscopy (XPS) analysis was also performed to estimate the chemical condition of the silicided film. Figs. 6 and 7 compare the Si 2p and Mo 3d spectra of the silicided films with those of pure Si and pure Mo, respectively. The binding energies that correspond to the Si 2p spectrum of pure Si and the silicided film obtained in this paper were 99.4 and 99.0 eV, respectively. Similarly, the binding energies that correspond to the Mo 3d spectrum of pure Mo and the silicided film were 228.2 and 228.0 eV, respectively. Both the binding energy that corresponds to the Si 2p spectrum of the pure Si film and that

Fig. 6. XPS analysis shows that the binding energy, which corresponds to Si 2p spectrum, of the silicided films is 0.4 eV lower than that of the pure Si.

Fig. 7. XPS analysis shows that the binding energy, which corresponds to Mo 3d spectrum, of the silicided films is 0.2 eV lower than that of the pure Mo.

which corresponds to the Mo 3d spectrum of the pure Mo film are strongly consistent with the reported handbook data [29]. Furthermore, a downward shift in the binding energy of 0.4 eV for the silicided films is observed from the Si 2p spectra. The magnitude of this shift is close to the value previously reported for MoSi<sub>2</sub> (-0.3 eV) [30]. Similarly, a downward shift in the binding energy of 0.2 eV for silicided films is observed from Mo 3d spectra, and the magnitude of the binding-energy shift corresponds closely to the previously reported values (-0.2 eV) [31]. Accordingly, we speculate that MoSi<sub>2</sub> is the main constituent of the MoSi<sub>x</sub> film formed in this paper, and the full silicidation of the Mo layer is responsible for the large shift in the work function after silicidation annealing.

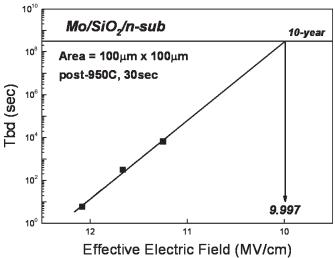

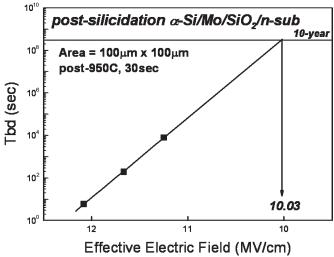

The constant voltage stressing (CVS) method was employed to generate the ten-year lifetime projections of Mo/SiO $_2$  (2.3 nm) and postsilicidation  $\alpha$ -Si/Mo/SiO $_2$  (2.4 nm) devices at room temperature for oxide integrity evaluation. Figs. 8 and 9 show that pure Mo and MoSi $_x$  gates have superior time dependence.

Fig. 8. TDDB lifetime projection of the Mo/SiO $_2$  device. Superior TDDB characteristic for pure Mo gate annealed by 950  $^{\circ}\text{C}$  RTA for 30 s is demonstrated.

Fig. 9. TDDB lifetime projection of the postsilicidation  $\alpha$ -Si/Mo/SiO $_2$  device. Superior TDDB characteristic for the MoSi $_x$  gate annealed by 950 °C RTA for 30 s is demonstrated.

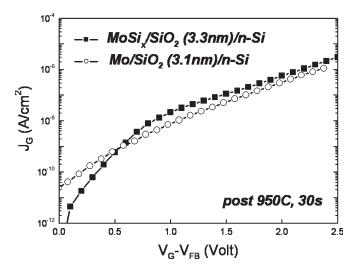

dent dielectric breakdown (TDDB) characteristics, respectively, after 950 °C RTA for 30 s. Fig. 10 compares the accumulation leakage-current densities of Mo/SiO<sub>2</sub>/n-Si and postsilicidation  $\alpha$ -Si/Mo/SiO<sub>2</sub> devices to investigate further the possible metal interdiffusion into the oxide or channel region following hightemperature annealing. Both devices were annealed by 950 °C RTA for 30 s, and the  $MoSi_x/SiO_2$  device exhibited slightly higher leakage-current density than the Mo/SiO<sub>2</sub> device. This increase in the leakage current may be caused by the additional thermal budget required for the formation of metal silicide. Notably, pure Mo has been demonstrated as a p<sup>+</sup>-polysiliconcompatible gate candidate for PMOS with negligible metal contamination and metal diffusion [32]. The comparable TDDB characteristics and leakage-current densities of pure Mo and MoSi<sub>x</sub> gated devices also reveal that the silicidation process required for the formation of MoSi<sub>x</sub> will not severely degrade the device performance or oxide integrity.

Fig. 10. Accumulation leakage-current densities of Mo/SiO $_2$ /n-Si and MoSi $_x$ /SiO $_2$ /n-Si devices annealed by 950  $^{\circ}$ C RTA for 30 s.

Fig. 11.  $V_{\rm FB}$  versus EOT plots of postsilicidation  $\alpha$ -Si/Mo gated MOSCAP devices with  $(5 \times 10^{15}~{\rm cm}^{-2})$  and without arsenic preimplantation.

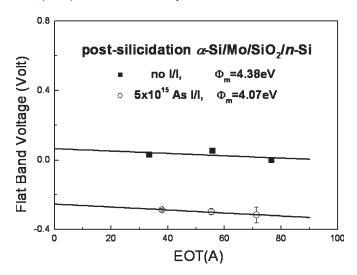

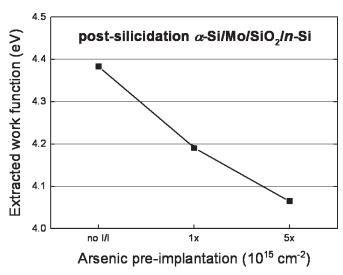

Fig. 11 indicates that postsilicidation  $\alpha$ -Si/Mo/SiO<sub>2</sub> with and without arsenic preimplantation exhibit linear  $V_{\rm FB}$  versus EOT plots. A parallel shift in the  $V_{\rm FB}$  versus the EOT plot is observed. Evidently, the incorporation of low-energy arsenic preimplantation indeed leads to the modulation of the work function, rather than the channel dopant-induced adjustment in the threshold voltage. Fig. 12 summarizes the effect of the arsenic preimplantation dosage upon the magnitude of the workfunction modulation. The extracted  $\Phi_m$  values of  $\mathrm{MoSi}_x$  on  $SiO_2$  with the preimplantation of  $1 \times 10^{15}$  and  $5 \times 10^{15}$  cm<sup>-2</sup> doses of arsenic are 4.19 and 4.07 eV, respectively. Although the introduction of arsenic impurities has been demonstrated to expand the difference between the  $\Phi_m$  of MoSi<sub>x</sub> and pure Mo, and to extend the range of applications of the proposed approach from devices with advanced structures to conventional bulk devices; the exact mechanism of the modulation of the work function by the preimplantation of As is still under investigation.

Fig. 13 plots the dependence of  $\Phi_m$  on the gate-dielectric material. Effective  $\Phi_m$  values of pure Mo and MoSi $_x$  gates on

Fig. 12. Dependence of  $\Phi_m$  values of postsilicidation  $\alpha$ -Si/Mo/SiO $_2$  gated MOSCAP devices on doses of arsenic preimplantation.

Fig. 13. Dependence of  $\Phi_m$  values on gate-dielectric material.

HfO<sub>2</sub> are reduced slightly to 4.89 and 4.34 eV, respectively, while maintaining a large  $\Phi_m$  difference of 0.55 eV, regardless of the underlying gate-dielectric materials. This observation is consistent with the results of Lee et al. [33]. Notably, arsenic preimplantation can still lower the effective  $\Phi_m$  value of MoSi<sub>2</sub> on the  $HfO_2$  gate dielectric. The effective  $\Phi_m$  of  $MoSi_x$  on  $HfO_2$  with the preimplantation of arsenic at a dose of  $5 \times$  $10^{15}$  cm<sup>-2</sup> is found to be 4.06 eV, which is 0.28 eV lower than that of the undoped sample. As mentioned above, preimplantation of impurities does not help modulate the  $\Phi_m$  of FUSI gates on the HfO<sub>2</sub> gate dielectric because of the Fermi-level pinning effect [14]. By contrast, the possibility of  $\Phi_m$  modulation using the dopant preimplantation is still maintained herein, even though a small reduction (0.03 eV) in the modulation range can be observed. This improvement may be attributed to the use of Mo as the first-layer metal, which effectively separates most Si atoms from the gate/HfO2 interface prior to its participation in silicidation. The formation of Hf-Si bonds during  $\alpha$ -Si deposition or silicidation annealing is noticeably mitigated, and the pinning effect, which is believed to be caused by the Hf-Si interaction, can be less pronounced.

### IV. CONCLUSION

This work presented a novel dual-metal gate technology for gating with Mo and  $\operatorname{MoSi}_x$ . On the  $\operatorname{SiO}_2$  gate dielectric,  $\operatorname{Mo-MoSi}_x$  combination can be appropriate not only for devices with advanced transistor structures but also for conventional bulk devices if arsenic preimplantation is adopted. The thermal stabilities of pure Mo and  $\operatorname{MoSi}_x$  on  $\operatorname{SiO}_2$  were also evaluated to be higher than 950 °C. The effective  $\Phi_m$  of pure Mo or  $\operatorname{MoSi}_x$  gate on  $\operatorname{HfO}_2$  is found to be slightly lower than that on  $\operatorname{SiO}_2$ . Nevertheless, the difference between  $\Phi_m$  of Mo and that of undoped  $\operatorname{MoSi}_x$  is independent of the underlying gate-dielectric material. Arsenic preimplantation still affects the modulation of the  $\Phi_m$  of the metal silicide on  $\operatorname{HfO}_2$ , even though the modulation range is slightly smaller than that on  $\operatorname{SiO}_2$ .

### ACKNOWLEDGMENT

The authors would like to thank the UC Berkeley Device Group for the use of QMCV simulator.

### REFERENCES

- [1] Semiconductor Industry Association, International Technology Roadmap for Semiconductors—Front-End Process, 2004.

- [2] E. M. Vogel, K. Z. Ahmed, B. Hornung, W. K. Hensen, P. K. McLarty, G. Lucovsky, J. R. Hauser, and J. Wortman, "Modeled tunnel currents for high dielectric constant dielectrics," *IEEE Trans. Electron Devices*, vol. 45, no. 6, pp. 1350–1355, Jun. 1998.

- [3] Q. Lu, D. Park, A. Kalnitsky, C. Chang, C.-C. Cheng, S. P. Tay, T.-J. King, and C. Hu, "Leakage current comparison between ultrathin Ta<sub>2</sub>O<sub>5</sub> films and conventional gate dielectrics," *IEEE Electron Device Lett.*, vol. 19, no. 9, pp. 341–342, Sep. 1998.

- [4] B. Cheng, M. Cao, Ř. Rao, A. Inani, P. V. Voorde, W. M. Greene, J. M. C. Stork, Z. Yu, P. M. Zeitzoff, and J. C. S. Woo, "The impact of high-κ gate dielectrics and metal gate electrodes on sub-100 nm MOSFET's," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1537–1544, Jul. 1999.

- [5] Y. Abe, T. Oishi, K. Shiozawa, Y. Tokuda, and S. Satoh, "Simulation study on comparison between metal gate and polysilicon gate for subquarter-micron MOSFET's," *IEEE Electron Device Lett.*, vol. 20, no. 12, pp. 632–634, Dec. 1999.

- [6] L. Chang, S. Tang, T. J. King, J. Bokor, and C. Hu, "Gate length scaling and threshold voltage control of double-gate MOSFETs," in *IEDM Tech. Dig.*, 2000, pp. 719–722.

- [7] Q. Lu, Y. C. Yeo, P. Ranade, H. Takeuchi, T. J. King, and C. Hu, "Dual-metal gate technology for deep-submicron CMOS transistors," in *VLSI Symp. Tech. Dig.*, 2000, pp. 72–73.

- [8] M. Qin, V. M. C. Poon, and S. C. H. Ho, "Investigation of polycrystalline nickel silicide films as a gate material," *J. Electrochem. Soc.*, vol. 148, no. 5, pp. G271–G274, May 2001.

- [9] J. Kedzierski, E. Nowak, T. Kanarsky, Y. Zhang, D. Boyd, R. Carruthers, C. Cabral, R. Amos, C. Lavoie, R. Roy, J. Newbury, E. Sullivan, J. Benedict, P. Saunders, K. Wong, D. Canaperi, M. Krishnan, K.-L. Lee, B. A. Rainey, D. Fried, P. Cottrell, H.-S. P. Wong, M. Ieong, and W. Haensch, "Metal-gate FinFET and full-depleted SOI devices using total gate silicidation," in *IEDM Tech. Dig.*, 2002, pp. 247–250.

- [10] W. P. Maszara, Z. Krivokapic, P. King, J.-S. Goo, and M.-R. Lin, "Transistors with dual work function metal gates by single full silicidation (FUSI) of polysilicon gates," in *IEDM Tech. Dig.*, 2002, pp. 367–370.

- [11] J. H. Sim, H. C. Wen, J. P. Lu, and D. L. Kwong, "Dual work function metal gates using full nickel silicidation of doped poly-Si," *IEEE Electron Device Lett.*, vol. 24, no. 10, pp. 631–633, Oct. 2003.

- [12] J. Yuan and J. C. S. Woo, "Tunable work function in fully nickel-silicided polysilicon gates for metal gate MOSFET applications," *IEEE Electron Device Lett.*, vol. 26, no. 2, pp. 87–89, Feb. 2005.

- [13] C. Cabral, Jr., J. Kedzierski, B. Linder, S. Zafar, V. Narayanan, S. Fang, A. Steegen, P. Kozlowski, R. Carruthers, and R. Jammy, "Dual workfunction fully silicided metal gates," in VLSI Symp. Tech. Dig., 2004, pp. 184–185.

- [14] T. Nabatame, M. Kadoshima, K. Iwamoto, N. Mise, S. Migita, M. Ohno, H. Ota, N. Yasuda, A. Ogawa, K. Tominaga, H. Satake, and A. Toriumi, "Partial silicides technology for tunable work function electrodes on high-κ gate dielectrics—Fermi level pinning controlled PtSi<sub>x</sub> for HfO<sub>x</sub>(N) pMOSFET," in *IEDM Tech. Dig.*, 2004, pp. 83–86.

- [15] C. Hobbs, L. Fonseca, V. Dhandapani, S. Samavedam, B. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcia, D. Roan, L. Lovejoy, R. Rai, L. Hebert, H. Tseng, B. White, and P. Tobin, "Fermi level pinning at the PolySi/metal oxide interface," in *VLSI Symp. Tech. Dig.*, 2003, pp. 9–10.

- [16] E. Cartier, V. Narayanan, E. P. Gusev, P. Jamison, B. Linder, M. Steen, K. K. Chan, M. Frank, N. Bojarczuk, M. Copel, S. A. Cohen, S. Zafar, A. Callegari, M. Gribelyuk, M. P. Chudzik, C. Cabral, Jr., R. Carruthers, C. D'Emic, J. Newbury, D. Lacey, S. Guha, and R. Jammy, "Systematic study of pFET Vt with Hf-based gate stacks with poly-Si and FUSI gates," in VLSI Symp. Tech. Dig., 2004, pp. 44–45.

- [17] M. Koyama, Y. Kamimuta, T. Ino, A. Kaneko, S. Inumiya, K. Eguchi, M. Takayanagi, and A. Nishiyama, "Careful examination on the asymmetric Vfb shift problem for poly-Si/HfSiON gate stack and its solution by the Hf concentration control in the dielectric near the poly-Si interface with small EOT expense," in *IEDM Tech. Dig.*, 2004, pp. 499–502.

- [18] E. P. Gusev, C. Cabral, Jr., B. P. Linder, Y. H. Kim, K. Maitra, E. Cartier, H. Nayfeh, R. Amos, G. Biery, N. Bojarczuk, A. Callegari, R. Carruthers, S. A. Cohen, M. Copel, S. Fang, M. Frank, S. Guha, M. Gribelyuk, P. Jamison, R. Jammy, M. Ieong, J. Kedzierski, P. Kozlowski, V. Ku, D. Lacey, D. LaTulipe, V. Narayanan, H. Ng, P. Nguyen, J. Newbury, V. Paruchuri, R. Rengarajan, G. Shahidi, A. Steegen, M. Steen, S. Zafar, and Y. Zhang, "Advanced gate stacks with fully silicided (FUSI) gates and high-κ dielectrics: Enhanced performance at reduced gate leakage," in IEDM Tech. Dig., 2004, pp. 79–82.

- [19] K. G. Anil, A. Veloso, S. Kubicek, T. Schram, E. Augendre, J.-F. de Marneffe, K. Devriendt, A. Lauwers, S. Brus, K. Hensen, and S. Biesemans, "Demonstration of fully Ni-silicided metal gates on HfO<sub>2</sub> based high-κ gate dielectrics as a candidate for low power applications," in VLSI Symp. Tech. Dig., 2004, pp. 190–191.

- [20] M. Kadoshima, A. Ogawa, M. Takahashi, H. Ota, N. Mise, K. Iwamoto, S. Migita, H. Fujiwara, H. Satake, T. Nabatame, and A. Toriumi, "Fermi level pinning engineering by Al compositional modulation and doped partial silicide for HfAlO<sub>x</sub>(N) CMOSFETs," in VLSI Symp. Tech. Dig., 2005, pp. 70–71.

- [21] C. S. Park, B. J. Cho, L. J. Tang, and D.-L. Kwong, "Substituted aluminum metal gate on high-κ dielectric for low work function and Fermi-level pinning free," in *IEDM Tech. Dig.*, 2004, pp. 299–302.

- [22] M. Terai, K. Takahashi, K. Manabe, T. Hase, T. Ogura, M. Saitoh, T. Iwamoto, T. Tatsumi, and H. Watanabe, "Highly reliable HfSiON CMOSFET with phase controlled NiSi (NFET) and Ni<sub>3</sub>Si (PFET) FUSI gate electrode," in VLSI Symp. Tech. Dig., 2005, pp. 68–69.

- [23] J. A. Kittl, A. Veloso, A. Lauwers, K. G. Anil, C. Demeurisse, S. Kubicek, M. Niwa, M. J. H. van Dal, O. Richard, M. A. Pawlak, M. Jurczak, C. Vrancken, T. Chiarella, S. Brus, K. Maex, and S. Biesemans, "Scalability of Ni FUSI gate processes: Phase and Vt control to 30 nm gate lengths," in VLSI Symp. Tech. Dig., 2005, pp. 72–73.

- [24] P. Ranade, Y.-K. Choi, D. Ha, A. Agarwal, M. Ameen, and T.-J. King, "Tunable work function molybdenum gate technology for FDSOI-CMOS," in *IEDM Tech. Dig.*, 2002, pp. 363–366.

- [25] T. L. Li, C. H. Hu, W. L. Ho, H. C.-H. Wang, and C. Y. Chang, "Continuous and precise work function adjustment for integratable dual metal gate CMOS technology using Hf-Mo binary alloys," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1172–1179, Jun. 2005.

- [26] R. Beyers, "Thermodynamic considerations in refractory metal-siliconoxygen systems" *J. Appl. Phys.*, vol. 56, no. 1, pp. 147–152, Jul. 1, 1984

- oxygen systems," *J. Appl. Phys.*, vol. 56, no. 1, pp. 147–152, Jul. 1, 1984. [27] K. J. Yang, Y.-C. King, and C. Hu, "Quantum effect in oxide thickness determination from capacitance measurement," in *VLSI Symp. Tech. Dig.*, 1999, pp. 77–78.

- [28] J. M. Liang and L. J. Chen, "Interfacial reactions and thermal stability of ultrahigh vacuum deposited multilayered Mo/Si structures," J. Appl. Phys., vol. 79, no. 8, pp. 4072–4077, Apr. 15, 1996.

- [29] J. F. Moulder, W. F. Stickle, P. E. Sobol, and K. D. Bomben, *Handbook of X-ray Photoelectron Spectroscopy*, J. Chastain, Ed. Eden Prairie, MN: Physical Electronics Division, Perkin-Elmer Corporation, 1992.

- [30] J. M. Slaughter, A. Shapiro, P. A. Kearney, and C. M. Falco, "Growth of molybdenum on silicon: Structure and interface formation," *Phys. Rev. B*, vol. 44, no. 2, pp. 3854–3863, 1991.

- [31] N. Ohishi, H. Yanagisawa, K. Sasaki, and Y. Abe, "Initial silicide formation process of Mo/(100) Si system prepared using an ultrahigh-vacuum sputtering system," *Electron. Commun. Jpn., Part 2, Electron.*, vol. 84, no. 3, pp. 71–78, 2001.

- [32] R. Lin, Q. Lu, P. Ranade, T.-J. King, and C. Hu, "An adjustable work function technology using Mo gate for CMOS devices," *IEEE Electron Device Lett.*, vol. 23, no. 1, pp. 49–51, Jan. 2002.

- [33] J. H. Lee, Y.-S. Suh, H. Lazar, R. Jha, J. Gurganus, Y. Lin, and V. Misra, "Compatibility of dual metal gate electrodes with high- $\kappa$  dielectrics for CMOS," in *IEDM Tech. Dig.*, 2003, pp. 323–326.

**Tzung-Lin Li** was born in Pingtung, Taiwan, R.O.C., on April 2, 1976. He received the B.S. degree in electrical engineering from the National Central University, Chungli, Taiwan, R.O.C., in 1998 and the M.S. degree from the Institutes of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 2000, where he is currently working toward the Ph.D. degree.

His current research interest is focused on the study and investigation of metal gate technology for nanodevices.

**Wu-Lin Ho** received the B.S. degree in industrial education from the National Taiwan Normal University, Taipei, Taiwan, R.O.C., in 1998 and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 2005.

In 2005, he joined Taiwan Semiconductor Manufacturing Company Ltd. (TSMC), Hsinchu, where he has been engaged in research and development of memory device technologies.

**Hung-Bin Chen** was born in Kaohsiung, Taiwan, R.O.C., on July 15, 1981. He received the B.S. degree in physics from the National Chung Hsing University, Taichung, Taiwan, R.O.C., in 2004. He is currently working toward the Ph.D. degree in the Institutes of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

His current research interest is focused on the study and investigation of metal-gate technology for nanodevices.

**Howard C.-H. Wang** received the B.S. and Ph.D. degrees in electronic engineering from the National Chiao-Tung University, Taiwan, R.O.C., in 1992 and 2002, respectively.

He joined Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) in 1995, where he was initially responsible for process integration for 0.5- and 0.6- $\mu$ m technology. Between 1997 and 2002, he was involved in the device design (front-end integration) for 0.18- $\mu$ m, 0.15- $\mu$ m, 0.13- $\mu$ m, and 90-nm technology in Advanced Device Technology Department

at TSMC. Since 2002, he has been a Manager in Exploratory Technology Development-1 Department under the supervision of Dr. C. Hu. He is currently working on the development of high- $\kappa$  gate dielectric, metal gate, and strained-Si technologies for sub-65-nm-node CMOS-device technology. He holds 13 U.S. patents and has authored and coauthored 15 papers in technical journals and conferences.

Dr. Wang is a member of the CMOS Devices subcommittee for International Electron Devices Meeting (IEDM) in 2004 and 2005.

Chun-Yen Chang (S'69–M'70–SM'81–F'88–LF'05) received the B.S. degree in electrical engineering from Cheng Kung University, Tainan, Taiwan, R.O.C., in 1960. He pursued advanced studies at the Institute of Electronics of National Chiao-Tung University (NCTU), Hsinchu, Taiwan, R.O.C., where he worked on an M.S. thesis on tunneling in semiconductor–superconductor junctions. His Ph.D. dissertation, entitled *Carrier transport across metal-semiconductor barrier*, was completed in 1969 and was published in 1970. It is

cited as a pioneering paper in this field.

He has contributed to microelectronics and optoelectronics, including the invention of the method of low-pressure metal-organic chemical vapor deposition using tri-ethyl-gallium to fabricate LED, laser, microwave transistors, Zn-incorporation of SiO<sub>2</sub> for stabilization of power devices, and nitridation of SiO2 for ultralarge scale integrations, etc. He has devoted himself to education and academic research for more than 40 years. During 1962 through 1963, he was in the military service at NCTU establishing the first Taiwanese experimental TV transmitter. In 1963, he joined to NCTU to serve as an Instructor establishing the High-Vacuum Laboratory. In 1964, he and his colleague established the Semiconductor Research Center at NCTU in April 1965, and the first IC in August 1966. In 1968, he published the first Taiwanese semiconductor paper in an international journal Solid State Electronics. In the same year, he was invited by Prof. L. J. Chu, a Webster Chair Professor at Massachusetts Institute of Technology, to join the NCTU Ph.D. program. In 1969, he became a Full Professor teaching solid-state physics, quantum mechanics, and semiconductor devices and technologies. In 1987, he became Dean of Research, in 1987–1990, Dean of Engineering, in 1990-1994, and Dean of Electrical Engineering and Computer Science, in 1994-1995. Simultaneously, he was the Founding President of National Nano Device Laboratories (NDL) from 1990 to 1997. Then, he became Director of Microelectronics and Information Systems Research Center (MIRC) of NCTU, in 1997-1998. In August 1, 1998, he was appointed The President of NCTU by NCTU and Ministory of Education (MOE) search committees. He is currently National Chair, Professor, and The President of NCTU. He has supervised more than 300 M.S. and 50 Ph.D. degree students. They are now founders of most high-technology enterprises in Taiwan, namely United Microelectronics Corporation (UMC), Taiwan Semiconductor Manufacturing Company Ltd. (TSMC), Winbond, MOSEL, Acer, and Leo, among others.

Dr. Chang is a member of Academia Sinica, and Foreign Associate of National Academy of Engineering, USA.

Chenming Hu (S'71–M'76–SM'83–F'90) received the B.S. degree from Taiwan University, Taiwan, R.O.C., in 1968, and the M.S. and Ph.D. degrees in electrical engineering from the University of California (UC), Berkeley, in 1970 and 1973 respectively.

He is Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) Distinguished Chair Professor in the Department of Electrical Engineering and Computer Sciences at UC Berkeley. From 2001 to 2004, he was Chief Technology Officer of TSMC. He was Co-founder of Celestry Design Technologies.

Dr. Hu is a member of the National Academy of Engineering and Academia Sinica. He received the 1997 IEEE Jack Morton Award for contributions to MOSFET reliability physics, the 2001 IEEE Solid State Circuits Award for codeveloping the industry standard MOSFET model Berkeley Short-channel IGFET Model (BSIM), and the 2000 Defense Advanced Research Project Agency (DARPA) outstanding research award for codeveloping FinFET, a promising next-generation transistor structure.