### Annealing temperature effect on the performance of nonvolatile HfO 2 Si-oxide-nitrideoxide-silicon-type flash memory

Yu-Hsien Lin, Chao-Hsin Chien, Chun-Yen Chang, and Tan-Fu Lei

Citation: Journal of Vacuum Science & Technology A 24, 682 (2006); doi: 10.1116/1.2174021

View online: http://dx.doi.org/10.1116/1.2174021

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvsta/24/3?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Silicon-oxide-high- -oxide-silicon memory using a high- Y 2 O 3 nanocrystal film for flash memory application J. Vac. Sci. Technol. A **27**, 700 (2009); 10.1116/1.3151816

Metal-oxide-high- k -oxide-silicon memory structure using an Yb 2 O 3 charge trapping layer Appl. Phys. Lett. **93**, 183510 (2008); 10.1063/1.3021360

Achieving 1 nm capacitive effective thickness in atomic layer deposited Hf O 2 on In 0.53 Ga 0.47 As Appl. Phys. Lett. **92**, 252908 (2008); 10.1063/1.2952826

Formation of stacked oxide/ Y 2 Ti O 5 /oxide layers for flash memory application Appl. Phys. Lett. **91**, 062909 (2007); 10.1063/1.2768630

Performance improvement of flash memories with Hf O x N y Si O 2 stack tunnel dielectrics J. Vac. Sci. Technol. B **24**, 1683 (2006); 10.1116/1.2207153

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

## Annealing temperature effect on the performance of nonvolatile HfO<sub>2</sub> Si-oxide-nitride-oxide-silicon-type flash memory

#### Yu-Hsien Lin

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 300, Republic of China

#### Chao-Hsin Chiena)

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 300, Republic of China and National Nano Device Laboratory, Hsinchu, Taiwan 300, Republic of China

#### Chun-Yen Chang and Tan-Fu Lei

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 300, Republic of China

(Received 12 August 2005; accepted 17 January 2006; published 4 May 2006)

In this article, we demonstrate the effect of the postdeposition annealing for the HfO<sub>2</sub> trapping layer on the performance of the Si-oxide-nitride-oxide-silicon-type flash memories. It was found that the memory window becomes larger while the retention and endurance characteristics get worse as the annealing temperature increases. This was ascribed to the larger amount and the shallower energy levels of the crystallization-induced traps as compared to the traps presented in the as-fabricated HfO<sub>2</sub> film. Finally, in the aspect of disturbances, we show only insignificant read, drain, and gate disturbances presented in the three samples in the normal operation. © 2006 American Vacuum Society. [DOI: 10.1116/1.2174021]

#### I. INTRODUCTION

Poly-Si-oxide-nitride-oxide-silicon (SONOS)-type flash memories have recently attracted much attention for the application in the next-generation nonvolatile memories.1 Based on discrete storage nodes, the SONOS-type flash memories have the potential for achieving high program/ erase speed, low programing voltage, low-power performance, large memory window, excellent retention, endurance, and disturbance characteristics.<sup>2-6</sup> Hafnium oxide (HfO<sub>2</sub>) is considered to be a promising candidate for the charge trapping layer for the SONOS-type flash memory instead of  $Si_3N_4$  film.<sup>7</sup> The high- $\kappa$  dielectric film, HfO<sub>2</sub>, is expected to have better charge trapping characteristics than the conventional Si<sub>3</sub>N<sub>4</sub> films for sufficient density of trap states and deep trap energy level to achieve longer retention time.<sup>8,9</sup> This feature makes HfO<sub>2</sub> be more helpful in scaling the tunnel oxide for enhancing the performance and more suitable for the development of the SONOS-type memory with multibit operation. 10,11 However, using HfO<sub>2</sub> film as the trapping layers has the issue of lateral migration of trapped electrons and then leads to degraded retention.<sup>12</sup>

In this article, we investigated the performances of the  $HfO_2$  SONOS-type flash memories by changing postdeposition annealing temperatures for the  $HfO_2$  trapping layer. Besides, we show that the high- $\kappa$  dielectric film such as  $HfO_2$  can trap electron and hole for the trapping characteristics.

#### II. DEVICES FABRICATION

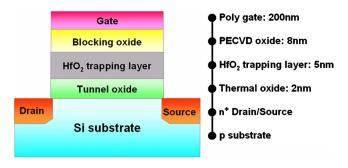

The fabrication process of the HfO<sub>2</sub> SONOS-type flash memory is shown in Fig. 1. A 2 nm direct tunneling oxide

<sup>a)</sup>Electronic mail: chchien@mail.ndl.org.tw

682

was thermally grown on a (100)-oriented p-type Si substrate. A 5 nm amorphous  $HfO_2$  layer was subsequently deposited by electron beam evaporation method with pure  $HfO_2$  (99.9% pure) targets. Next, the samples were subject to rapid thermal annealing (RTA) through  $N_2$  gas at 600 and 900 °C for 1 min. A blocking oxide of about 8 nm was then deposited by plasma-enhanced chemical vapor deposition (PECVD) followed by poly-Si deposition and gate patterning to complete the gate stack formation of the  $HfO_2$  SONOS-type flash memory devices.

### III. CHARACTERIZATION RESULTS AND DISCUSSION

#### A. Devices operation

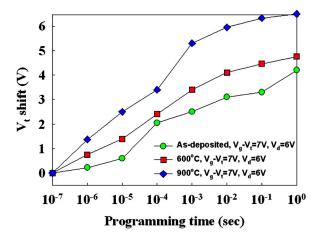

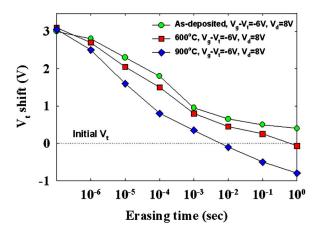

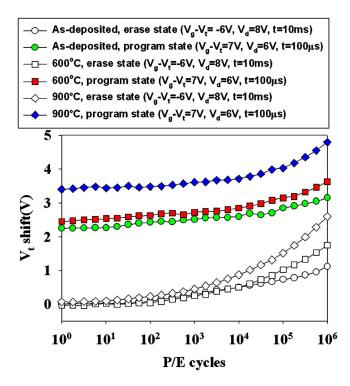

Figures 2 and 3 show the programing and erasing characteristics, respectively, with different pulse widths for the HfO<sub>2</sub> SONOS-type flash memories with different post-HfO<sub>2</sub>-deposition annealing temperatures. All devices described in this article had dimensions of  $L/W=1/2 \mu m$ . We used channel hot-electron injection for the programing with the bias condition at  $V_g - V_t = 7 \text{ V}$  and  $V_d = 6 \text{ V}$  and band-toband hot-hole injection for erasing with the bias condition at  $V_g - V_t = -6 \text{ V}$  and  $V_d = 8 \text{ V}$ . Based on the discrete charge storage of HfO<sub>2</sub> trapping layer, the feasibility of 2 bit operation can be achieved with proper bias scheme. We can employ forward and reverse reads to detect the information stored in the programed bit 1 and bit 2, respectively. This means that we can program 1 bit and read the information using a reverse read scheme. We have added Table I to summarize the bias conditions for 2 bit operation. For the temperature effect, it was clearly observed that the programing

Fig. 1. Schematic cross section and process flow of the  $HfO_2$  SONOS-type flash memory device.

speed and the memory window increase when the annealing temperature increases. In addition, with the annealing temperature increases, the erasing speed increases but slight overerasure can be observed. We speculate that this is due to the crystallization-induced trap generation. As well known, the HfO<sub>2</sub> trapping layers will crystallize after high temperature annealing. The defects along the grain boundaries are thought being able to act as the extra trapping sites

Fig. 2. Programing characteristics of the HfO<sub>2</sub> SONOS-type flash memories. It was clearly observed that the programing speed and the memory window increase when the annealing temperature increases.

Fig. 3. Erasing characteristics of the HfO<sub>2</sub> SONOS-type flash memories. With the annealing temperature increases, the erasing speed increases and shows little overerasure.

TABLE I. Summary of the bias conditions for two-bit operation in the memory cell.

|       |                                         | Program<br>(V) | Erase (V) | Read<br>(V) |

|-------|-----------------------------------------|----------------|-----------|-------------|

| Bit 1 | $V_g - V_t$                             | 7              | -6        | 3           |

|       | $egin{array}{c} V_d \ V_s \end{array}$  | 6<br>0         | 8<br>0    | 0<br>>2     |

| Bit 2 | $V_g - V_t$                             | 7              | -6        | 3           |

|       | $egin{aligned} V_d \ V_s \end{aligned}$ | 0<br>6         | 0<br>8    | >2<br>0     |

and, therefore, larger memory window can be obtained. From the results of x-ray diffraction (XRD) analysis, we did see that the degree of crystallization becomes more significant upon increasing temperature (not shown). Since the  $V_t$  are 2.7, 2.2, and 1.8 V for the as-deposited, 600 and 900 °C-annealed devices, respectively, we then conclude that the generated crystallization-induced traps inside the HfO<sub>2</sub> trapping layer are hole-trap-like, which fact can explain the result shown in Fig. 3 that the more severe overerasure upon increasing annealing temperature has been Owing to the nature of discrete charge storage sites in the high- $\kappa$  gate dielectrics, we can easily achieve 2 bit storage in one single memory device by just reversing source and drain. <sup>16</sup>

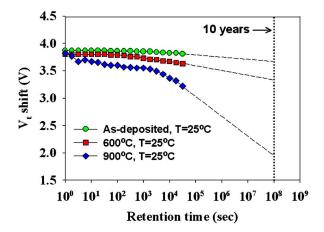

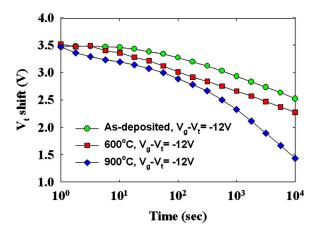

Figure 4 illustrates the retention characteristics for all HfO<sub>2</sub> SONOS-type flash memories. The retention time of the memory with as-deposited HfO<sub>2</sub> trapping layer can be up to 10<sup>8</sup> s for 10% charge loss. However, it was significantly degraded as the annealing was employed and the situation became worse as the temperature increased. We have calculated the activation energy of the traps in the HfO<sub>2</sub> nanocrystals for the fresh device. Activation energy tracing is used widely to characterize the Arrhenius relation extracted from the temperature dependence of charge loss in a nonvolatile memory as a function of time. For a given charge-loss threshold criterion (in our case, 20%), the failure rates obtained at higher

Fig. 4. Erasing characteristics of the  $HfO_2$  SONOS-type flash memories at room temperature T=25 °C. The 900 °C-annealed device shows the worst retention performance.

Fig. 5. Endurance characteristics of the  $HfO_2$  SONOS-type flash memories. The 900 °C-annealed device shows larger memory window but worse endurance performance in the same condition.

temperatures (125–200 °C), and five numbers for every temperature, can then be extrapolated to the nominal operating condition. The extracted activation energies are 2.45, 1.78, and 0.96 eV for the as-deposited, 600 and 900 °C-annealed samples, respectively. Therefore, we thought that the post-deposition annealing will induce more traps with shallower energy level in the trapping layer, which give rise to larger memory window and poor charge retention.

The endurance performances after 10<sup>6</sup> P/E cycles are shown in Fig. 5. Again, the rate of memory window narrowing increases upon increasing annealing temperature. As we know, the narrowing is mainly coming from charge gain. Because of the use of ultrathin tunnel oxide, there is only very minute amount of trapped charges generated during operation in the tunnel oxide. 18 Hence, we attribute this to the residual charges along the grain boundaries because these highly localized induced traps are more difficult to remove unless their positions are coincided to overlap with the hothole injection. Figure 6 shows the vertical charge migration characteristics with applying  $V_g$ - $V_t$ =-12 V at room temperature 25 °C. Consistent with the former result, the vertical charge migration is exacerbated by increasing annealing temperature. With the annealing temperature increases, the more vertical charge loss was found. It can be explained by more leakage path in the grain boundary of crystallized HfO2 in the high annealing temperature.

#### **B.** Disturbances

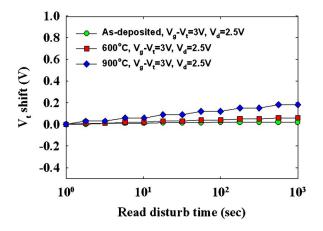

Figure 7 shows the read disturb induced erase-state threshold voltage instability in a localized HfO<sub>2</sub> SONOS-

Fig. 6. Vertical migration characteristics of HfO<sub>2</sub> SONOS-type flash memories. Consistent with the former result, the vertical charge migration is exacerbated by increasing annealing temperature.

type flash memory cell for three samples. To allow for 2-bit operation, the applied bitline voltage in a reverse-read scheme must be sufficiently large (>1.5 V) for being able to "read through" the trapped charge in the neighboring bit. Relatively large read bitline voltage may cause unwanted electron injection and then results in a significant threshold voltage shift of the neighboring bit. For our measurement, the gate and drain biases were applied and the source was grounded. The results clearly show that almost no read disturbance appears for the low voltage reading operation of  $V_g$ - $V_t$ =3 V and  $V_d$ =2.5 V in our HfO<sub>2</sub> flash memory.

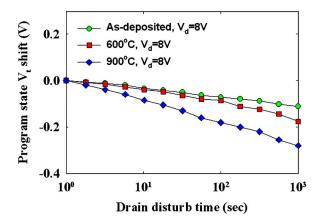

Figure 8 shows the programing drain disturbance of our  $HfO_2$  SONOS-type flash memories. The same drain voltages  $(V_d=8 \text{ V})$  were applied in the programing drain disturbance measurements at room temperature  $(T=25 \, ^{\circ}\text{C})$ . Upon the increasing annealing temperature, the more drain disturbances were observed. The storage charge leakage path along the grain boundaries induces more drain disturbances for the annealed devices. After 1000 s at 25  $^{\circ}\text{C}$ , we have sufficiently drain the disturb margin  $(<0.3 \, \text{V})$  for the three annealed samples.

Fig. 7. Read disturbance characteristics of  $HfO_2$  SONOS-type flash memories. No significant  $V_t$  shift for all samples even after 1000 s at 25 °C.

Fig. 8. Drain disturbance characteristics of HfO2 SONOS-type flash memories. After 1000 s at 25 °C, only 0.4 V drain disturb margin is observed for the 900 °C-annealed devices.

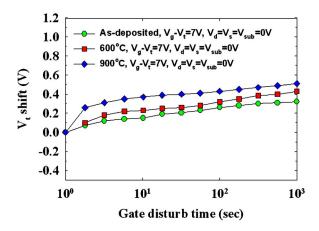

Figure 9 shows the gate disturb characteristics in the erasing state. Gate disturbance may occur during programing for the cells sharing a common wordline while one of the cells is being programed. We measured the gate disturbance with the condition at  $V_g$ - $V_t$ =7 V and  $V_d$ = $V_s$ = $V_{sub}$ =0 V for the three annealed samples. With the annealing temperature increases, the more gate disturbances were observed. A large amount of trap generates in the high temperature annealing that induces more gate disturbances for the annealed devices. Only 0.5 V threshold voltage shift has been observed for the 900 °C annealed devices after 1000 s stressing. Such good gate disturb characteristic with such thin tunnel oxide can be explained by using the serial capacitor voltage divider model with

Fig. 9. Gate disturbance characteristics of HfO<sub>2</sub> SONOS-type flash memories. Only 0.5 V threshold voltage shift has been observed for the 900 °Cannealed devices after  $V_g$ - $V_t$ =7 V and  $V_s$ = $V_d$ = $V_{sub}$ =0 V, 1000 s stressing.

small voltage drop at the tunnel oxide. In summary, we have good read, drain, and gate disturbances for the as-deposited, 600 and 900 °C-annealed samples.

#### IV. CONCLUSION

In this article, we have investigated the effect of postdeposition annealing temperature on the performance of the resultant HfO2 SONOS-type flash memories. Higher temperature treatment can have large memory windows due to the crystallization-induced trap generation, but can lead to poorer retention and endurance performances. Moreover, we found that the HfO2 trapping layer can trap both electrons and holes. No significant read, drain, and gate disturbances were observed for the three samples. HfO2 SONOS-type flash memory is considered to be a promising candidate for the flash memory devices application.

#### **ACKNOWLEDGMENT**

This project was sponsored by the National Science Council of Taiwan, Republic of China (Contract No. 942215E009070).

<sup>1</sup>M. H. White, D. A. Adams, and J. Bu, IEEE Circuits Devices Mag. 16, 22 (2000).

<sup>2</sup>T. S. Chen, K. H. Wu, H. Chung, and C. H. Kao, IEEE Electron Device Lett. 25, 205 (2002).

<sup>3</sup>T. Sugizaki et al., Proceedings of the IEEE Non-Volatile Semiconductor Memory Workshop, February 2003 (unpublished), pp. 60-61.

<sup>4</sup>T. Baron, B. Pellissier, L. Perniola, F. Mazen, J. M. Hartmann, and G. Polland, Appl. Phys. Lett. 83, 1444 (2003).

<sup>5</sup>R. Ohba, N. Sugiyama, K. Uchida, J. Koga, and A. Toriumi, IEEE Trans. Electron Devices 49, 1392 (2002).

<sup>6</sup>R. Muralidhar et al., Tech. Dig. - Int. Electron Devices Meet. **2003**, 601. <sup>7</sup>Y. N. Tan, W. K. Chim, W. K. Choi, M. S. Joo, T. H. Ng, and B. J. Cho, Tech. Dig. - Int. Electron Devices Meet. 2004, 889.

<sup>8</sup>W. J. Zhu, T.-P. Ma, T. Tamagawa, J. Kim, and Y. Di, IEEE Electron Device Lett. 23, 97 (2002).

<sup>9</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

<sup>10</sup>Y.-H. Lin, C.-H. Chien, C.-T. Lin, C.-Y. Chang, and T.-F. Lei, IEEE Electron Device Lett. 26, 154 (2005).

<sup>11</sup>D. Montanari, J. Van Houdt, D. Wellekens, G. Vanhorebeek, L. Haspeslagh, L. Deferm, G. Groeseneken, and H. E. Maes, Proceedings of the IEEE Nonvolatile Memory Technology Conference, June 1996 (unpublished), pp. 80–83.  $^{\rm 12}$  T. Sugizaki et al., Proceedings of the VLSI Symposium Technology Digest

Technical Papers, 2003 (unpublished), pp. 27-28.

<sup>13</sup>W. J. Tsai, C. C. Yeh, N. K. Zous, C. C. Liu, S. K. Cho, T. Wang, S. C. Pan, and C. Y. Lu, IEEE Trans. Electron Devices 51, 434 (2004).

<sup>14</sup>C.-C. Yeh IEEE Electron Device Lett. **25**, 643 (2004).

<sup>15</sup>T. Yamaguchi, H. Satake, and N. Fukushima, Tech. Dig. - Int. Electron Devices Meet. 2001, 663.

<sup>16</sup>Y.-W. Chang, T.-C. Lu, S. Pan, and C.-Y. Lu, IEEE Electron Device Lett. **25**, 95 (2004).

<sup>17</sup>B. De Salvo, G. Ghibaudo, G. Pananakakis, G. Reimbold, F. Mondond, B. Guillaumot, and P. Candelier, IEEE Trans. Electron Devices 46, 1518

<sup>18</sup>E. F. Runnion, S. M. Gladstone, R. S. Scott, Jr., D. J. Dumin, L. Lie, and J. C. Mitros, IEEE Trans. Electron Devices 44, 993 (1997).