# A 13.56 MHz 40 mW CMOS High-Efficiency Inductive Link Power Supply Utilizing On-Chip Delay-Compensated Voltage Doubler Rectifier and Multiple LDOs for Implantable Medical Devices

Chung-Yu Wu, Fellow, IEEE, Xin-Hong Qian, Student Member, IEEE, Ming-Seng Cheng, Yu-An Liang, and Wei-Ming Chen, Member, IEEE

Abstract—In this paper, a 13.56 MHz CMOS near-field inductive link power supply (ILPS) that can deliver 20 mA output current for implantable medical devices (IMDs) is proposed and fabricated. In the proposed ILPS, the pair of inductive link coils is constructed in the spiral shape with a ferrite core to save space and increase efficiency. Experimental results have shown that the near-field coils can transmit power at the resonant frequency of 13.56 MHz with the transmission efficiency up to 76.3%. The CMOS power regulator is composed of active voltage doubler rectifier (VD) and lowdropout regulators (LDOs). In the active VD with the comparator, the input offset voltage is adjustable for delay compensation and a start-up control circuit is added to achieve robust start-up mechanism. On-chip delay compensation control with SR-latches is proposed to prevent from error glitch switching on offset voltage control and achieve accurate delay compensation so that the reverse current conduction can be avoided and the efficiency can be increased. Three fully-integrated LDOs with rectifier output voltage of 2 V to 1.8 V are realized for analog (ALDO), digital (DLDO), and reference-voltage (RLDO) circuits. Thus the performance of individual LDO can be optimized. The measured output ripple voltage of the active VD is 10.4 mV. The power conversion efficiency (PCE) is 85% under 20 mA output current. The measured dropout voltage is 384 mV. As compared with other designs, the proposed ILPS has lower ripple voltages, lower dropout voltage, and higher PCE.

Index Terms—Active voltage doubler rectifier, fully-integrated LDOs, implantable medical devices, inductive link power supply, 13.56 MHz ISM band.

# I. INTRODUCTION

N RECENT years, implantable medical devices (IMDs) have become more and more important in the treatment of intractable diseases or disorders, especially neurological

Manuscript received January 25, 2014; revised May 07, 2014 and July 27, 2014; accepted August 15, 2014. Date of publication September 29, 2014; date of current version October 24, 2014. This paper was approved by Guest Editor Zhihua Wang. This work was supported in part by the Ministry of Science and Technology (MOST), R.O.C., under project MOST 103-2220-E-009-006, MOST 103-2220-E-009-001, and in part by the "Aim for the Top University Plan" under Biomedical Electronics Translation Research Center of National Chiao Tung University and Ministry of Education, Taiwan, R.O.C.

The authors are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu City 300, Taiwan. They are also with the Biomedical Electronics Translational Research Center, National Chiao Tung University, Hsinchu City 300, Taiwan (e-mail: peterwu@mail.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2014.2356459

ones. Such neural prosthetic IMDs utilize electrical pulses to stimulate neural cells and restore neural functions. Several examples are cochlear implants [1], retinal prostheses [2], and closed-loop epilepsy control [3]. These IMDs usually have high power consumption greater than several mWs. Since they are implanted into the human body, a long-term reliable power supply is required to avoid the frequent surgery for the battery replacement. However, current battery technology cannot sustain for an enough long time. Therefore wireless power transfer can be a useful solution for IMDs [4]. The near-field inductive energy transfer has become the most widely used method for the neural prosthetic IMDs to recharge the chargeable battery or directly provide the required power from medium to high levels [1]–[3].

A near-field inductive link power supply (ILPS) can be divided into three different parts as: power amplifier, near-field coils, and power regulator. The power amplifier amplifies the RF signal to drive the near-field coils. The near-field coils transmit the RF signal through the skin. In the design of near-field coils, the coil size which could be confined by the physical sizes of IMDs, is an important design factor that mainly determines both power conversion efficiency (PCE) and maximum transmission distance. The power regulator which converts the received signal into DC voltage to supply the IMD, consists of low-dropout regulators (LDOs) and active rectifier or passive rectifier [5]. In the reported CMOS ILPSs [3], [6]–[11], active rectifiers with power MOS devices, comparators and control circuits are adopted to convert AC power into DC power. Since the power MOS devices has both turn-on and turn-off delay times, the comparators should accurately control switch timing to obtain proper forward current conduction and avoid reverse current conduction. Thus the efficiency can be increased. Several techniques have been proposed for the delay compensation [3], [7]–[11]. In [7], the negative feedback control is used to compensate only the turn-off delay. But the PCE is degraded obviously with the increased output loading. The active rectifier using offset-controlled high speed comparators was proposed in [8], where both turn-on delay and turn-off delay are compensated by using off-chip control signals. Such off-chip control signals are not feasible for IMDs.

It is known that the input voltage of a full-wave active rectifier must be larger than its output DC voltage. As compared with that of a full-wave active rectifier, the input voltage of an active

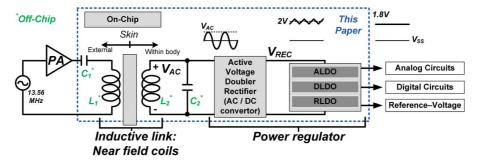

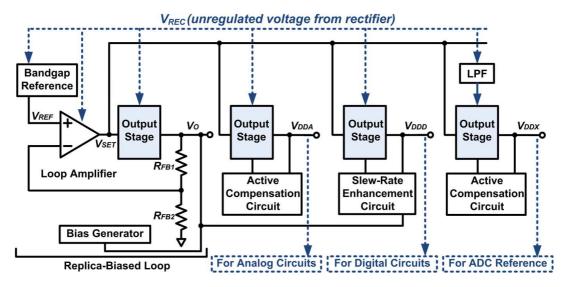

Fig. 1. The block diagram of the proposed ILPS.

voltage doubler rectifier (VD) can be lower than its output DC voltage, leading to more reliable operation in the weakly coupled inductive link environment. Active VDs using offset-controlled comparators were proposed in [9], [10], where turn-on and turn-off delay compensation requires off-chip control signals. Moreover, their dropout voltages are large. In [11], the zero-crossing-point (ZCP) prediction (or phase-lead method) is proposed to compensate the switching delay in active rectifiers without comparators. Since it doesn't have comparators to control power transistors, a delay unit is needed to provide accurate timing. The measured power efficiency is 82% at 400  $\Omega$  output loading and 41 mW output power.

The LDO provides a stable power supply for the system-on-chip (SoC). The SoC chip typically consists of analog front-end circuits, digital circuits, and SAR ADC with a reference voltage. It is found that a single LDO is difficult to satisfy the different performance requirements of analog, digital, and reference-voltage circuits. Moreover, the number of off-chip components such as capacitors and resistors should be restricted in IMDs. Thus, high performance fully-integrated LDOs with low power dissipation and small chip area are required.

In the IMD implanted into human brain for epilepsy detection and stimulation [3], the near-field ILPS is the best choice. In this paper, a CMOS ILPS is proposed and fabricated in 0.18  $\mu m$  CMOS process technology to supply the voltage of the SoC in the above IMD [12]. The proposed ILPS is operated at the industrial, scientific, and medical (ISM) band (13.56 MHz) and capable of delivering 20 mA output current. An active VD with fully on-chip delay-compensated comparators and peaking current source is designed to avoid the use of external control signals. The peaking current source is used to decrease the supply voltage dependence of bias current [13]. The signal voltage received by the receiver coil is 1.192 V. The dropout voltage of active VD is 384 mV with the voltage conversion ratio of 1.67. The measured PCE of active VD is 85% at 40 mW output power on 100  $\Omega$  load.

In the proposed ILPS, the fully-integrated multiple LDOs are used to generate stable 1.8 V output voltage for analog (ALDO), digital (DLDO), and reference-voltage (RLDO) circuits. Therefore, the performance of individual LDO can be optimized and the output cross talk from DLDO can be isolated. The measured ripple voltages of active VD, ALDO, DLDO, and RLDO output are 10.4 mV, 5.9 mV, 72.4 mV, and 1.5 mV, respectively. The measured PCE of the power regulator is 74.8% under 20 mA output current.

This paper is organized as follows. In Section II, the system architecture and circuit design of the proposed ILPS are described. The experimental results are shown in Section III. Finally, the conclusion is given in Section IV.

# II. SYSTEM ARCHITECTURE AND CIRCUIT DESIGN

# A. System Architecture

Fig. 1 shows the block diagram of the proposed ILPS which is composed of the coils for power transmission, active VD, and fully-integrated multiple LDOs. The active VD is used to obtain the required DC voltage with less AC voltage so that the inductive magnetic energy through body tissue can be reduced to avoid the risk of tissue damage. Finally, the LDO is used to regulate the unregulated DC voltage from the active VD into a stable voltage for the IMD.

To determine the specifications of ILPS, the maximum current loading of each sub-block of the SoC for epilepsy detection and stimulation must be considered. The sub-blocks of SoC include analog front-end amplifiers (AFEA), SAR ADC, biosignal processor (BSP), MedRadio-band transceiver, and stimulator [3]. Depending on the circuit operation, the sub-blocks are further divided into analog, digital (sample-data), and reference. Then their maximum transient loading currents of 0.56 mA, 17.2 mA, and 1 mA are obtained in analog, digital, and reference circuits, respectively. The total transient loading current is 18.76 mA. Therefore, the maximum driving current capability of the proposed ILPS is designed to be 20 mA. The maximum driving current capabilities of the proposed ALDO, DLDO, and RLDO are 5 mA, 20 mA, and 1.5 mA, respectively.

# B. Near-Field Coil Design

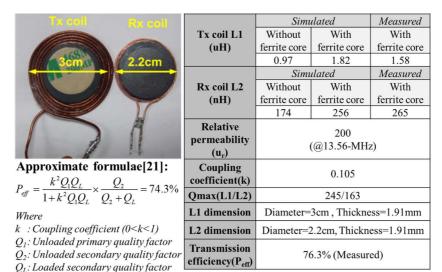

Since the coil structure affects quality (Q) factor, coupling coefficient (k), and inductance, it must been carefully chosen to suit the implanted devices [14]–[16]. For the seizure control IMD [3], spiral coils are chosen for inductive link. The implant size cannot exceed 2.5 cm in diameter and transmission distance is about 1 cm. The cylindrical ferrite cores are placed into the coil center to increase the Q factor. The use of ferrite core as a magnet has been used in cochlear implant device [1] and proved its feasibility.

Under these conditions, both Tx and Rx are designed. The design and simulation procedure is described below.

Firstly, the outer (inner) diameter of the implanted Rx coil is chosen as 2.2 cm (2 cm) with 2 turns of AWG 25 wires. Then the number of turns and the radius of Tx coil are determined through

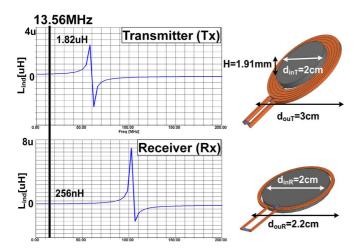

Fig. 2. HFSS simulation results on inductances of the Tx and Rx coils with ferrite cores. The coil sizes are also given, where H is height of ferrite core.

the HFSS simulation to achieve the maximum coupling coefficient and transmission efficiency. The outer (inner) diameter of Tx coil is determined as 3 cm (2 cm) with 5 turns of AWG 18 wires. Finally, the coil inductances are simulated.

Fig. 2 shows the HFSS simulation results on inductances of Tx and Rx coils with ferrite cores. Below the self-resonant frequency, the inductance of Rx coil is 256 nH at 13.56 MHz whereas that of Tx coil is 1.82  $\mu$ H. The electric behavior of coil is like that of a capacitor showing negative inductance when the frequency is greater than self-resonant frequency.

#### C. Active Voltage Doubler Rectifier (VD)

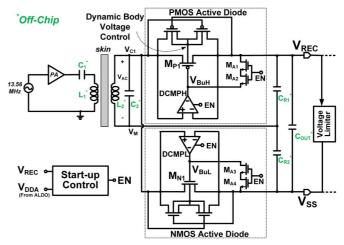

The circuit structure of the active VD is shown in Fig. 3, which consists of NMOS active diode, PMOS active diode, start-up control, two symmetrical delay-compensated comparators (DCMPH and DCMPL) with delay compensation control, dynamic body voltage control circuits, voltage limiter, and offchip filtering capacitors  $C_{R1}$ ,  $C_{R2}$ , and  $C_{OUT}$ , which are 0.1  $\mu F$ SMD capacitors. In Fig. 3,  $C_1$  (89 pF) and  $C_2$  (520 pF) are used to make the resonant frequency at 13.56 MHz. The voltage limiter limits the output voltage V<sub>REC</sub> of active VD to a maximum value of 2.5 V (nominal value of 2 V) in case the input power of the active VD is too large. The dynamic body voltage control circuit with two auxiliary transistors is used to automatically connect the body of power MOS device to the suitable potential so that both body-effect and substrate leakage of power MOS device can be eliminated. For example, the p-type dynamic body voltage control circuit connects the body of power transistor M<sub>P1</sub> to the highest voltage between the input and output voltages. Similarly, the body of power transistor  $M_{\rm N1}$  can be connected to the lowest voltage dynamically by n-type dynamic body voltage control circuit.

Since the large power transistors  $M_{\rm P1}$  and  $M_{\rm N1}$  in Fig. 3 have larger parasitic capacitances, their turn-on delay and turn-off delay when driven by the output voltages  $V_{\rm BuH}$  and  $V_{\rm BuL}$  of the delay-compensated comparators DCMPH and DCMPL, reduce the conduction time and induce the reverse current. Thus the delays have to be compensated by DCMPH and DCMPL. The detailed structures of DCMPH and DCMPL are shown in

Fig. 3. The circuit structure of VD.

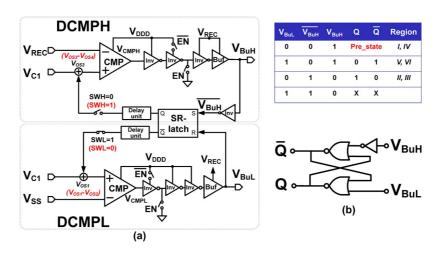

Fig. 4(a). As can be seen from Fig. 4(a), the delay-compensated comparator DCMPH (DCMPL) consists of a delay compensation control path, a comparator CMP, three inverters, and a buffer to generate the output voltages  $V_{BuH}$  ( $V_{BuL}$ ). The output voltages  $V_{\rm BuH}$  and  $V_{\rm BuL}$  are connected to the delay compensation control path formed by a SR-latch and a delay unit to dynamically generate suitable offset voltages to compensate both turn-on and turn-off delay times. They are powered from DLDO output voltage (V<sub>DDD</sub>). The structure and the operation table of the SR-latch is shown in Fig. 4(b). The use of SR-latch can prevent from the error offset voltage switching due to the noise of input voltage in the comparators. Thus accurate delay compensation can be achieved. The delay unit is used to provide a suitable delay to accurately control the offset switching for exact delay compensation. In Fig. 4(a), when the switch SWH = 0(SWL = 1), the positive offset voltage  $V_{OS3}$   $(V_{OS1})$  is generated at the input of the comparator CMP in DCMPH (DCMPL). When the switch SWH = 1 (SWL = 0), the negative offset voltage  $V_{\rm OS3} - V_{\rm OS4}~(V_{\rm OS1} - V_{\rm OS2})$ , where  $V_{\rm OS3} < V_{\rm OS4}$  $(V_{OS1} < V_{OS2})$ , is generated at the input of the comparator in DCMPH (DCMPL). The generation of these offset voltages will be explained later with the comparator circuit.

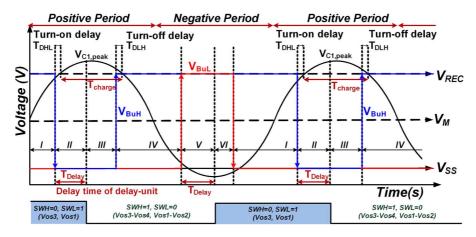

In Fig. 5, the steady state operational waveforms of DCMPH and DCMPL in Figs. 3 and 4 is described in the following.

**Region I**:  $V_{\rm C1} + V_{\rm OS3} < V_{\rm REC}, V_{\rm C1} + V_{\rm OS1} > V_{\rm SS}.$  In this region, the output voltage  $V_{\rm BuH}$  of DCMPH is at high level whereas  $V_{\rm BuL}$  of DCMPL is at low level. As may be seen from Fig. 3, the power transistor  $M_{\rm P1}$  and  $M_{\rm N1}$  are turned off and  $C_{\rm R1}$  and  $C_{\rm R2}$  are not charged. The SR-latch in DCMPH (DCMPL) is in the previous state and SWH = 0 (SWL = 1) to maintain the positive input offset of the comparator CMP in DCMPH (DCMPL) at  $V_{\rm OS3}$  ( $V_{\rm OS1}$ ) as shown in Fig. 4.

**Region II**:  $V_{\rm C1} + V_{\rm OS3} > V_{\rm REC}, V_{\rm C1} + V_{\rm OS1} > V_{\rm SS}.$   $V_{\rm BuH}$  is pulled low and  $M_{\rm P1}$  is turned on after the turn-on delay  $T_{\rm DHL}$  to charge  $C_{\rm R1}$  and keep  $V_{\rm C1} \approx V_{\rm REC}.$   $V_{\rm BuL}$  is still at low level, thus the output state of SR-latch Q  $(\bar{Q})$  is 1 (0). The SWH (SWL) is changed to 1 (0) after the delay  $T_{\rm Delay}$  of the delay unit shown in Fig. 4. The offset voltage  $V_{\rm OS3}$   $(V_{\rm OS1})$  is changed to the negative offset voltage

Fig. 4. The circuit structures of (a) DCMPH, DCMPL, and (b) SR-latch.

Fig. 5. Steady-state operational waveforms of DCMPH and DCMPL.

$V_{\rm OS3} - V_{\rm OS4} \ (V_{\rm OS1} - V_{\rm OS2})$  where  $V_{\rm OS3} < V_{\rm OS4} \ (V_{\rm OS1} < V_{\rm OS2})$  as shown in Fig. 4.

**Region III**:  $V_{C1} + (V_{OS3} - V_{OS4}) > V_{REC}$ ,  $V_{C1} + (V_{OS1} - V_{OS2}) > V_{SS}$ .  $V_{BuH}$  is still low and  $M_{P1}$  is on to charge  $C_{R1}$ .

$\begin{array}{ll} \textit{Region IV} \colon V_{\rm C1} + (V_{\rm OS3} - V_{\rm OS4}) &< V_{\rm REC}, \, V_{\rm C1} + \\ (V_{\rm OS1} - V_{\rm OS2}) > V_{\rm SS}, \, V_{\rm BuH} \, \text{is pulled to a high level} \\ \text{nearly equal to} \, V_{\rm REC}. \, \text{In Fig. 3}, \, M_{\rm P1} \, \text{is turned off after the} \\ \text{turn-off delay} \, T_{\rm DLH} \, \, \text{and no conduct current is generated} \\ \text{to charge} \, C_{\rm R1}. \end{array}$

**Region VI**:  $V_{C1} + V_{OS3} < V_{REC}$ ,  $V_{C1} + V_{OS1} < V_{SS}$ . After the power transistor  $M_{N1}$  is turned off, the operational period is moved to **Region I**.

As may be realized from Figs. 3 and 4, when  $V_{\rm BuH}$  is changed from high to low, the positive input offset voltage  $V_{\rm OS3}$  in the comparator CMP in DCMPH is changed to the negative offset voltage  $V_{\rm OS3}-V_{\rm OS4}$  after the delay time  $T_{\rm Delay}$  of the delay unit. The delay time  $T_{\rm Delay}$  is designed to avoid the malfunc-

tion that  $V_{\rm BuH}$  might be switched back to high immediately to stop charging output capacitor and introduce voltage ripple if the offset voltage changes to negative instantly without delay to make  $V_{\rm C1} + (V_{\rm OS3} - V_{\rm OS4}) < V_{\rm REC}.$  Similarly, when  $V_{\rm BuL}$  is changed from low to high, the input offset voltage  $V_{\rm OS1} - V_{\rm OS2}$  of DCMPL is changed to  $V_{\rm OS1}$  after  $T_{\rm Delay}.$  This can avoid the malfunction that  $V_{\rm BuL}$  might be switched back to low immediately to turn off  $M_{\rm N1}$  and cause ripples.

The received voltage  $V_{\rm AC}~(=V_{\rm C1}-V_{\rm M})$  of the near-field coil could generate a large ringing voltage  $\Delta V_{\rm ring}$  when the power transistor  $M_{\rm P1}$  is turned off in Region IV. If  $V_{\rm C1}+\Delta V_{\rm ring}+V_{\rm OS3}>V_{\rm REC}$ , the power transistor  $M_{\rm P1}$  would be turned on again. Thus to prevent the incorrect switching, the delay compensation control is designed to maintain the same offset voltage  $V_{\rm OS3}-V_{\rm OS4}$  even after  $V_{\rm BuH}$  is switched from low to high. The offset voltages  $V_{\rm OS3}~(V_{\rm OS1}-V_{\rm OS2})$  and  $V_{\rm OS3}-V_{\rm OS4}~(V_{\rm OS1})$  make the turn-on and turn-off points exactly at  $V_{\rm C1} \geq V_{\rm REC}~(V_{\rm C1} \leq V_{\rm SS})$  and  $V_{\rm C1} \leq V_{\rm REC}~(V_{\rm C1} \geq V_{\rm SS})$ , respectively. The control signals SWH and SWL can be generated from the SR-latch as shown in Fig. 4(b). Moreover, the delay compensation is performed fully on-chip without any off-chip control signals.

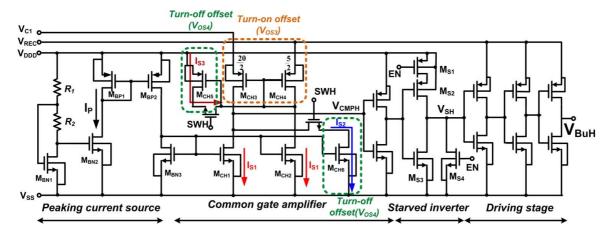

The CMOS circuit of the comparator CMP with inverters and buffer (driving stage) in DCMPH is shown in Fig. 6. Similar

Fig. 6. The CMOS circuit of the comparator, inverters and buffer (driving stage) in the DCMPH.

circuit is also used in DCMPL. As seen in Fig. 6, the circuit consists of a common gate amplifier  $(M_{\rm CH1}-M_{\rm CH4})$  where the source terminals of  $M_{\rm CH3}$  and  $M_{\rm CH4}$  are the input terminals of  $V_{\rm C1}$  and  $V_{\rm REC}$ , three stages of inverters to drive the large gate capacitance of power transistor  $M_{\rm P1}$ , and two offset control switches driven by SWH. The PMOS common-gate topology is adopted to achieve a high comparison speed because of the low input impedance.

In Fig. 6,  $\rm M_{CH3}$  and  $\rm M_{CH4}$  are designed with different sizes to produce the positive input offset voltage  $\rm V_{OS3}$  and compensate the turn-on delay. The simulated value of  $\rm V_{OS3}$  is 505 mV. To produce the negative input offset voltage  $\rm V_{OS3} - \rm V_{OS4}$ , the control signal  $\rm SWH = 1$  and the current of  $\rm M_{CH5}$  ( $\rm M_{CH6}$ ) is added to (subtracted from) that of  $\rm M_{CH4}$  ( $\rm M_{CH3}$ ). The simulated value of  $\rm V_{OS3} - \rm V_{OS4}$  is  $\rm -184$  mV. In the DCMPL, the simulated value of  $\rm V_{OS1}$  ( $\rm V_{OS1} - \rm V_{OS2}$ ) is 75 mV ( $\rm -394$  mV). These offset voltages are designed to generate the exact turn-on and turn-off points.

Since the supply voltage  $V_{\rm DDD}$  from DLDO is not kept constant before steady state, the peaking current source which is insensitive to  $V_{\rm DDD}$ , is designed to provide stable bias currents  $I_{\rm P}$ ,  $I_{\rm S1}$ , and  $I_{\rm S2}$  as shown in Fig. 6. According to the HSPICE simulation results, the variation of the current  $I_{\rm P}$  in the peaking current source in Fig. 6 is only 16% when  $V_{\rm DDD}$  changes from 1.3 V to 1.8 V. This leads to 15.6% maximum variation of the offset voltages  $V_{\rm OS1}$ ,  $V_{\rm OS2}$ ,  $V_{\rm OS3}$ , and  $V_{\rm OS4}$  in both DCMPH and DCMPL.

Since the proposed ILPS is used in the implanted medical devices, the temperature variations are not large when implanted. Only process and supply voltage variations are considered. Under different process corners and variations, the variations of delay compensation are investigated through 5-corner and Monte Carlo HSPICE simulations. The results show that the relative errors on the turn-on (turn-off) delay compensation with respect to the total turn-on time of both power transistors are within +3.7% and -0.6% (+12.1% and -16.1%). The simulated PCE is still greater than 86.1%. If only Monte Carlo variation is considered, the errors are smaller. Under 10% variations of the power supply  $V_{\rm DDD}$ , the simulated errors on the turn-on (turn-off) delay compensation are within +3.7%

Fig. 7. The schematic of start-up control circuit.

Fig. 8. The pie chart of power dissipation in the proposed active VD.

and -0.8% (+14.7% and -22.7%). The simulated PCE is slightly decreased to 85.5%.

Under the same Monte Carlo simulation as above, the mean values of the simulated dropout voltage is 402.8 mV and the simulated variations on the dropout voltage are within 12.4% and -10.1%. Under 10%  $V_{\rm DDD}$  variations, the variations

Fig. 9. The block diagram of the supply system with three LDOs.

are within 17.2% and -20.3%. Thus the PV variations of the dropout voltage are acceptable.

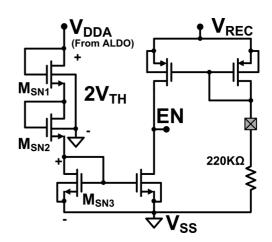

It is crucial to self-start the active VD because the comparators are powered by  $V_{\rm DDD}$  and  $V_{\rm REC}\,=\,V_{\rm DDD}\,=\,0$  V initially. To solve the start-up problem, a start-up control circuit shown in Fig. 7 is designed to sense both  $V_{\rm REC}$  and analog V<sub>DDA</sub> from ALDO and generate the voltage EN nearly equal to  $V_{\rm REC}$  when  $V_{\rm DDA}$  is low. With EN high, which is nearly equal to  $V_{REC}$ , the current starved inverter  $M_{S1} - M_{S4}$  in Fig. 6 blocks the incorrect  $V_{\rm SH}$  and turns on the switches  $M_{\rm A1}$  –  $M_{A4}$  in Fig. 3. The  $M_{A1}-M_{A4}$  are medium Vt ( $V_{TH,m}\approx$ 0.27 V) devices that can be turned on easily when  $V_{REC}$  is in low voltage. Thus in the start-up period, both  $M_{P1}$  and  $M_{N1}$  are connected as MOS diodes to form a passive VD. Until  $V_{\rm DDA}$  >  $2V_{\mathrm{TH}} + V_{\mathrm{TH0}}$  where  $V_{\mathrm{TH0}}$  is the threshold voltage of normal Vt ( $V_{TH0} \approx 0.43 \text{ V}$ ) devices under zero substrate bias and  $V_{TH}$  is the threshold voltage with substrate bias,  $M_{SN1} - M_{SN3}$ are operated in saturation region to pull the voltage level of EN equal to  $V_{SS}$ . Then the rectifier is operated in the normal active

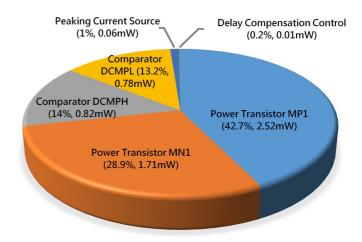

The total power consumption of the proposed active VD is 5.9 mW by simulation and its pie chart showing the power dissipations of each component is given in Fig. 8. When the output power of active VD is 40 mW, the power dissipations on the power transistors  $\rm M_{P1}$  and  $\rm M_{N1}$  are 2.52 mW (42.7%) and 1.71 mW (28.9%), respectively. The dissipations on DCMPH and DCMPL are 0.82 mW (14%) and 0.78 mW (13.2%), respectively. The dissipation on the peaking current source is 0.06 mW (1%) and that on the delay compensation control circuits is 0.01 mW (0.2%). The simulated PCE is 86.9%.

When the output power of the active VD is reduced to 4 mW, the power transistors dissipate 0.38 mW and the other circuits dissipate 1.6 mW in total. The simulated PCE is decreased to 63.3%. This sets a lower limit of the VD output power.

#### D. Low-Dropout Regulators (LDOs)

The block diagram of the supply system with fully-integrated multiple LDOs is shown in Fig. 9 [3] where a replica-biased

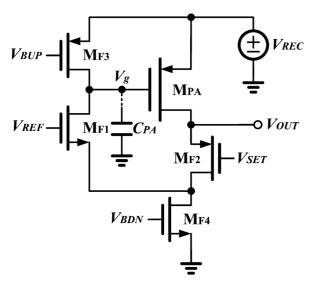

loop and three local regulation loops for analog, digital, and reference-voltage circuits. V<sub>REC</sub> is the unregulated input voltage from the rectifier.  $V_{\rm O}, V_{\rm DDA}, V_{\rm DDD}$ , and  $V_{\rm DDX}$  are the output voltages of replica-biased loop, ALDO, DLDO, and RLDO, respectively. The replica-biased loop is used to generate stable bias voltage  $V_{\rm SET}$  for other regulation loops. The output stage is basically based on the flipped voltage follower (FVF) [17]. The main advantage of the FVF is the reduced output impedance by shunt feedback connection, which is the key for obtaining good regulation and achieving frequency compensation. In Fig. 10,  $V_{\rm REC}$  is the unregulated input voltage,  $V_{\rm OUT}$  is the regulated output such as  $V_O$ ,  $V_{DDA}$ ,  $V_{DDD}$ , and  $V_{DDX}$ , and  $V_{BUP}$  and  $V_{\mathrm{BDN}}$  are bias voltages. When there is a variation at  $V_{\mathrm{OUT}}$ detected by the source of  $M_{F2}$ , the voltage difference between  $V_{\mathrm{OUT}}$  and control voltage  $V_{\mathrm{SET}}$  introduces an error signal. The error signal is then amplified by two cascaded common-gate amplifier by M<sub>F1</sub> and M<sub>F2</sub> in order to adjust the gate overdrive voltage of the pass transistor  $M_{\rm PA}$ . Finally, the drain current of  $M_{\mathrm{PA}}$  alters to compensate the output voltage  $V_{\mathrm{OUT}}$ . Since the FVF-based output stage has a low output resistance, the loop stability can be guaranteed.

In this design, the FVF-based output stage is adopted in each LDO. Therefore, the fast output voltage regulation is achieved by three local regulation loops. The ALDO, DLDO, and RLDO are responsible for driving analog circuits, digital circuits, and ADC reference,

With the separated ALDO, DLDO, and RLDO, the characteristic of each LDO can be optimized to supply the specified sub-block of an IMD. To power analog circuits, ALDO should generate an accurate DC voltage supply which has good line and load regulation. Besides, a high bandwidth in the power-supply rejection (PSR) is also required to protect the noise-sensitive blocks like VCOs and pre-amplifiers from the coupled input supply noise. Moreover, the output transient current should be minimized to reduce the disturbance on the power-line of the ALDO.

To power digital circuits such as DSP, fast transient response in DLDO is essentially important. Meanwhile, the DLDO must

Fig. 10. The schematic of the output stage based on FVF.

be able to handle a large and steep supply current change. Nevertheless, the digital circuitry is assumed to have greater tolerance to supply variations. Consequently,  $\pm 10\%$  of line voltage variations and load variations is acceptable. Generally, the slew-rate (SR) limit is the dominant factor in the transient performance of capacitor-free LDOs. Thus, the slew-rate enhancement (SRE) circuit is essentially required for the DLDO.

The RLDO is specially designed to generate a stable reference voltage for a 10-bit SAR ADC. A good isolation of RLDO is mandatory. Since any disturbance on the reference voltage directly degrades the ADC resolution, the disturbance should be smaller than 1/2 LSB (about 0.88 mVp-p). Moreover, the fixed load current is assumed to be negligible. Therefore, a passive low-pass filter (LPF) can be added to further reduce the supply noises.

The output stage of each LDO is exactly the same but with different aspect ratios according to their requirements in driving capabilities. Through the topology, each regulation loop can be optimized individually to satisfy different requirement and avoid cross-interferences especially from DLDO. The multiple LDOs have 2 V to 1.8 V output voltages and maximum DC output currents are 5 mA, 20 mA, and 1.5 mA in ALDO, DLDO, and RLDO, respectively.

#### III. EXPERIMENTAL RESULTS

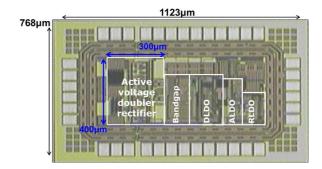

The proposed ILPS was successfully fabricated in TSMC 1P6M 0.18  $\mu m$  CMOS process. The whole chip photograph including the proposed active VD, multiple LDOs, and bandgap reference is shown in Fig. 11. The chip area is 1123  $\mu m \times 768~\mu m$ , including the pads. The Rx coil should be close to the chip to reduce the parasitic line inductance. The input power of Tx coil is measured and the measured transmission efficiency of coils is used to estimate the PCE of active VD.

The fabricated chip is directly bonded on printed circuit board (PCB), since the chip-on-board method can have smaller parasitic inductance and resistance. It should be noted that larger

Fig. 11. The chip micrograph.

Fig. 12. The experimental setup for the measurement of the fabricated ILPS.

parasitic inductances on bond wires could seriously increase the output ripples and degrade the rectifier performance or cause malfunction.

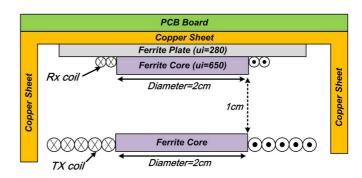

Since the ILPS transfers the power at 13.56 MHz, the larger magnetic field could influence the sensitive components on the PCB to generate larger output voltage ripples on the LDOs. Several simple and effective techniques of magnetic field shielding is proposed [18], [19].

The experimental setup is show in Fig. 12 where the environment is shielded by the copper metal planes. The ferrite plane is placed between Rx coil and PCB board so that the electromagnetic (EM) flux does not leak through the metal plate and better EM shielding can be achieved. At the ferrite-copper boundary, the H-field is nearly tangential and confined inside in the ferrite plate. The normal component of the H-field emitted into the copper is very small, so is the eddy current loss due to the H-field.

## A. Ferrite Core Spiral Coils

Table I is the measurement result of the near-field coils. With the ferrite cores, the inductances, quality factors, and maximum transmission efficiency of the coils are significantly increased. The inductances of coils are measured by impedance analyzer. The relative permeability  $(u_r)$  of ferrite cores at 13.56 MHz is shown in the data sheet from the manufacturer. The diameter of the Tx coil is 3 cm and that of the Rx coil is 2.2 cm. The near-field coils with ferrite cores have the measured transmission efficiency of 76.3% which is slightly higher the calculation one (74.3%) and better than the previous work (22% [16], 29.9% [20]).

TABLE I

THE PERFORMANCE OF THE NEAR-FIELD COILS

Fig. 13. The input waveform of active VD and the output voltage of DCMPL.

Fig. 14. The waveform of the start-up mechanism.

# B. Active Voltage Doubler Rectifier (VD)

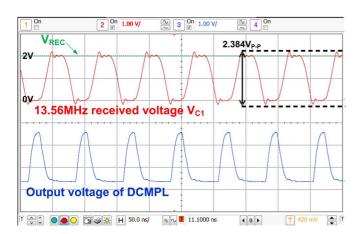

The proposed active VD can output 2 V DC voltage and have a low dropout voltage ( $|V_{\rm DS,MP1}| + V_{\rm DS,MN1}$ ) of 384 mV. Thus the required voltage amplitude of  $V_{\rm C1}$  is 2.384 V as shown in Fig. 13. The lower dropout voltage is obtained by delay compensation control and peaking current source. The turn-on and turn-off delay compensations reduce charging current obviously and cause lower dropout voltage. Furthermore, the peaking current source stabilizes bias current so that the comparators have fixed turn-on and turn-off offset voltages without external control. This also improves dropout voltage.

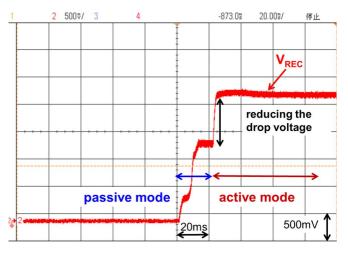

The measured start-up characteristic of the active VD is shown in Fig. 14 where  $V_{\rm REC}$  rises from 0 V to 2.3 V during 20 ms. After the start-up period, the active VD changes from passive mode to active mode.

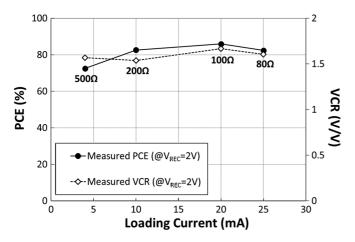

The measured Tx power with 20 mA loading and  $R_{\rm L}=100~\Omega$  at power regulator is 61.69 mW. The PCE is derived as 40 mW/(61.69 mW  $\times$  76.3%) = 85%, where 76.3% is the measured transmission efficiency of the near-field coils. The

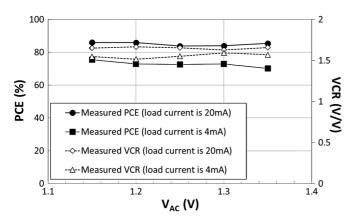

variations of measured PCE and VCR  $(V_{\rm REC}/V_{\rm AC})$  versus output loading currents from 25 mA to 4 mA are shown in Fig. 15 where different  $R_{\rm L}$  are indicated. As can be seen from Fig. 15, if the current loading is reduced to 4 mA (8 mW) with  $V_{\rm REC}=2\,V$ , the VCR is slightly reduced to 1.55 and the PCE is decreased to 72.5%. If the current loading is increased to 25 mA (50 mW), the VCR is slightly reduced to 1.61 and the PCE to 82.4%. In Fig. 16, the measured PCE and VCR versus  $V_{\rm AC}$  from 1.15 V to 1.35 V with  $R_{\rm L}=100~\Omega$  and the loading currents of 20 mA and 4 mA are plotted. As can be seen from Fig. 16, both PCE and VCR have small variations.

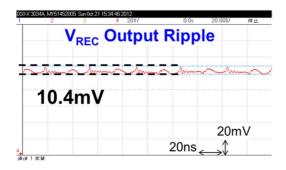

The measured voltage output ripple of the fabricated active VD is shown in Fig. 17. Since the near-field coils are close to the active VD in the experimental setup, the additional 13.56 MHz noise is coupled into the output node  $V_{\rm REC}$  of active VD. The measured active VD output peak-to-peak ripple is 10.4 mV under 20 mA output current. Since the DLDO output voltage  $(V_{\rm DDD})$  is the supply the comparator in the active VD, under

Fig. 15. The variations of measured PCE and VCR  $(V_{\rm REC}/V_{\rm AC})$  versus output loading currents with different  $R_{\rm L}$  .

Fig. 16. The measured PCE and VCR versus  $V_{\rm AC}$  with  $R_{\rm L}=100~\Omega$

Fig. 17. The voltage output ripple of proposed active VD.

the maximum transient current of 3 mA in DLDO, the voltage ripple of VD is slightly increased.

The main contributing factors to a low ripple at  $V_{\rm REC}$  are exact delay compensation, chip-on-board method with low parasitic bonding-wire inductances, and the shielding of Rx coil.

# C. Low-Dropout Regulators (LDOs)

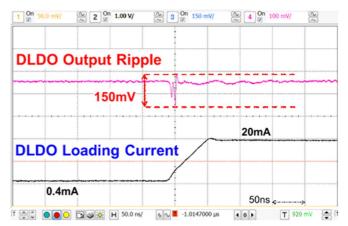

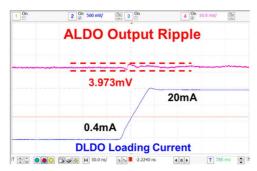

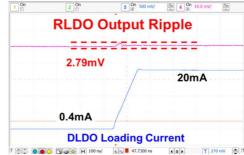

Fig. 18 shows the measurement results of transient load regulation of DLDO. When the loading current of DLDO changed from light load of 0.4 mA to heavy load of 20 mA, the corresponding ripple voltage is 150 mV. With the same loading current variance of the DLDO, the output voltage variations

Fig. 18. The measurement result of transient load regulation of DLDO.

are only 3.973 mV and 2.79 mV for ALDO and RLDO, respectively, are shown in Fig. 19. Both ALDO and RLDO have low crosstalk noise from DLDO. The measured PSR of ALDO, DLDO, and RLDO in 10 kHz (27 MHz) are -74 dB, -52 dB, and -66 dB (-7 dB, -1 dB, and -31 dB), respectively. The multiple LDOs have current efficiencies of 95.93%, 98.75% and 91.95% in ALDO, LDO and RLDO, respectively. The PCE of multiple LDOs can be calculated as

$$\begin{split} \text{PCE} &= \frac{I_{\text{Load}} \times V_{\text{DDD}}}{\left(I_{\text{Load}} + I_{Q}\right) \times V_{\text{IN}}} \\ &= \text{average current efficiency} \times \frac{1.8}{2} \\ &= \frac{5 \times 95.93\% + 20 \times 98.75\% + 1.5 \times 91.95\%}{5 + 20 + 1.5} \\ &\times \frac{1.8}{2} = 88\%. \end{split} \tag{1}$$

The performance comparison with other reported CMOS delay-compensated 13.56 MHz active rectifiers is given in Table II. As compared with [8]–[10], where both turn-on delay and turn-off delay are compensated by using off-chip control signals, the proposed VD delivers 20 mA output current while maintaining the lower dropout voltage of 384 mV which is smaller than those in the previous works (700 mV [8], 1.3 V [9], 520 mV [10]). The PCE of 85% is higher than others. It also provides a lower output peak-to-peak ripple (10.4 mV) than those in the previous works ( $\approx$  80 mV [8],  $\approx$  50 mV [9],  $\approx$  22 mV [10]).

The main reasons of lower ripple in the designed LDOs are the lower ripples in VD as well as the separated LDOs to reduce the cross-talk effect.

# IV. CONCLUSION

An ILPS circuit for IMD with hand winding coils, integrated rectifier, and multiple LDOs has been proposed and fabricated in TSMC 0.18  $\mu$ m CMOS technology. To enhance quality factor and magnetic flux, the near-field coils with ferrite cores is designed. The spiral coils with ferrite core have the measured transmission efficiency of 76.3%. The active VD with on-chip delay compensated comparators is designed to avoid the use of external control signals.

Fig. 19. The measurement results of (a) ALDO and (b) RLDO output isolation.

${\bf TABLE~II} \\ {\bf Comparison~of~Measured~Performance~of~CMOS~Active~Rectifiers}$

| Parameters                                | 2011<br>T-CAS I[8]                                                          | 2012<br>ISSCC[9]                   | 2013<br>TBCAS[10]                                        | This work                        |

|-------------------------------------------|-----------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------|----------------------------------|

| Technology                                | 0.5-μm CMOS                                                                 | 0.5-μm CMOS                        | 0.5-μm CMOS                                              | 0.18-μm CMOS                     |

| Structure                                 | Active rectifier                                                            | Active voltage doubler rectifier   | Active voltage doubler rectifier                         | Active voltage doubler rectifier |

| Delay compensation                        | On delay&<br>Off delay                                                      | On delay&<br>Off delay             | On delay&<br>Off delay                                   | On delay&<br>Off delay           |

| Chip area<br>(Without PAD)                | 0.18mm <sup>2</sup>                                                         | 0.585mm <sup>2</sup>               | 0.144mm <sup>2</sup>                                     | 0.12mm <sup>2</sup>              |

| Input amplitude V <sub>AC</sub>           | 3.8V                                                                        | 2.2V                               | 1.46V                                                    | 1.192V                           |

| Output voltage V <sub>REC</sub>           | $3.12V @R_L = 500\Omega$                                                    | $3.1 \text{V } @R_L = 500 \Omega.$ | $2.4 \text{V } @\text{R}_{\text{L}} = 1 \text{K} \Omega$ | 2V @R <sub>L</sub> =100Ω         |

| Maximum output current                    | 6.24mA                                                                      | 6.2mA                              | 2.4mA                                                    | 20mA                             |

| Rectifier output power                    | ~20mW                                                                       | ~20mW                              | ~5.8mW                                                   | 40mW                             |

| Operating frequency                       | 13.56MHz                                                                    | 13.56MHz                           | 13.56MHz                                                 | 13.56MHz                         |

| Dropout voltage                           | 700mV                                                                       | ~1.3V                              | ~520mV                                                   | 384mV                            |

| Rectifier output voltage ripple           | 80mV                                                                        | ~50mV                              | ~22mV                                                    | 10.4mV                           |

| Average V <sub>REC</sub> /V <sub>AC</sub> | 0.82                                                                        | 1.41                               | 1.64                                                     | 1.67                             |

| Power conversion efficiency(PCE)          | $80.2\%$ @R <sub>L</sub> = $500\Omega$ (70% @R <sub>L</sub> = $150\Omega$ ) | 70% @R <sub>L</sub> =500Ω          | 79% @R <sub>L</sub> =1KΩ (68% @R <sub>L</sub> =150Ω)     | 85% @R <sub>L</sub> =100Ω        |

For further PCE improvement, the multiple LDOs is adopted to fit different power needs in different circuits of IMDs. The measured PCE of VD is 85% at 40 mW output power on 100  $\Omega$  load. The measured ripple voltages of rectifier, ALDO, DLDO, and RLDO output are 10.4 mV, 5.9 mV, 72.4 mV, 1.5 mV, respectively. The 74.8% whole chip PCE is achieved, that is the multiplication of PCEs of active VD and multiple LDOs.

The exact delay compensation, chip-on-board method with low parasitic bonding-wire inductances, and the shielding of Rx coil leads to low ripple voltages in rectifier whereas the low ripple of rectifier and the separated LDOs with less cross-talk makes low ripple voltages in the three LDOs.

The proposed ILPS has been integrated with the epilepsy control SoC and successfully tested in rats.

# ACKNOWLEDGMENT

The authors would like to thank National Chip Implementation Center (CIC) for technical support and chip fabrication.

# REFERENCES

P. T. Bhatti and K. D. Wise, "A 32-site 4-channel high-density electrode array for a cochlear prosthesis," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2965–2973, Dec. 2006.

- [2] A. Rothermel, L. Liu, N. P. Aryan, M. Fischer, J. Wuenschmann, S. Kibbel, and A. Harscher, "A CMOS chip with active pixel array and specific test features for subretinal implantation," *IEEE J. Solid-State Circuits*, vol. 44, no. 1, pp. 290–300, Jan. 2009.

- [3] W.-M. Chen *et al.*, "A fully integrated 8-channel closed-loop neural-prosthetic CMOS SoC for real-time epileptic seizure control," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 232–247, Jan. 2014.

- [4] T.-J. Sun, X. Xie, and Z.-H. Wang, Wireless Power Transfer for Medical Microsystems. New York, NY, USA: Springer, 2013.

- [5] P. Li and R. Bashirullah, "A wireless power interface for rechargeable battery operated medical implants," *IEEE Trans. Circuits Syst. II, Ex*press Briefs, vol. 54, no. 10, pp. 912–916, Oct. 2007.

- [6] J. Yoo, L. Yan, S. Lee, Y. Kim, and H. Yoo, "A 5.2 mW self-configured wearable body sensor network controller and a 12 μW 54.9% efficiency wirelessly powered sensor for continuous health monitoring system," *IEEE J. Solid-State Circuits*, vol. 45, no. 1, pp. 178–188, Jan. 2010.

- [7] Y.-H. Lam, W.-H. Ki, and C.-Y. Tsu, "Integrated low-loss CMOS active rectifier for wirelessly powered devices," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 53, no. 12, pp. 1378–1382, Dec. 2006.

- [8] H. Lee and M. Ghovanloo, "An integrated power-efficient active rectifier with offset-controlled high speed comparators for inductively-powered applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 8, pp. 1749–1760, Aug. 2011.

- [9] H. Lee and M. Ghovanloo, "An adaptive reconfigurable active voltage doubler/rectifier for extended-range inductive power transmission," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2012, pp. 286–288.

- [10] H. Lee and M. Ghovanloo, "A high frequency active voltage doubler in standard CMOS using offset-controlled comparators for inductive power transmission," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 3, pp. 213–224, Jun. 2013.

- [11] T.-J. Sun, X. Xie, G.-L. Li, Y.-K. Gu, Y.-D. Deng, and Z.-H. Wang, "A two-hop wireless power transfer system with an efficiency-enhanced power receiver for motion-free capsule endoscopy inspection," *IEEE Trans. Biomed. Eng.*, vol. 59, no. 11, pp. 3247–3254, Nov. 2012.

- [12] X.-H. Qian, M.-S. Cheng, and C.-Y. Wu, "A CMOS 13.56 MHz high-efficiency low-dropout-voltage 40 mW inductive link power supply utilizing on-chip delay-compensated voltage doubler rectifier and multiple LDOs for implantable medical devices," in *Proc. IEEE Asia Solid-State Circuits Conf.*, 2013, pp. 257–260.

- [13] Y. Lu, W.-H. Ki, and J. Yi, "A 13.56 MHz CMOS rectifier with switched-offset for reversion current control," in *IEEE Symp. VLSI Circuits Dig.*, 2011, pp. 246–247.

- [14] K. Finkenzeller, RFID-Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification, 2nd ed. Hoboken, NJ, USA: Wiley, 2003.

- [15] S. Ramo, J. R. Whinnery, and T. V. Duzer, Fields and Waves in Communication Electronics, 3rd ed. Hoboken, NJ, USA: Wiley, 1994.

- [16] R. R. Harrison, "Designing efficient inductive power links for implantable devices," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2007, pp. 2080–2083.

- [17] J. Ramirez-Angulo, R. G. Carvajal, A. Torralba, J. Galan, A. P. Vega-Leal, and J. Tombs, "The flipped voltage follower: A useful cell for low-voltage low-power circuit design," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2002, pp. 615–618.

- [18] S.-C. Tang, S.-Y. Hui, and S.-H. Chung, "Evaluation of the shielding effects on printed-circuit-board transformers using ferrite plates and copper sheets," *IEEE Trans. Power Electron.*, vol. 17, no. 6, pp. 1080–1088, Nov. 2002.

- [19] Y.-P. Su, X. Liu, and S.-Y. Hui, "Extended theory on the inductance calculation of planar spiral windings including the effectof doublelayer electromagnetic shield," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 2052–2061, Jul. 2008.

- [20] M. Ghovanloo and S. Atluri, "A wide-band power-efficient inductive wireless link for implantable microelectronic devices using multiple carriers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 10, pp. 2211–2221, Oct. 2007.

- [21] M. W. Baker and R. Sarpeshkar, "Feedback analysis and design of RF power links for low-power bionic systems," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 1, pp. 28–38, Mar. 2007.

Chung-Yu Wu (S'76–M'76–SM'96–F'98) was born in 1950. He received the M.S. and Ph.D. degrees from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 1976 and 1980, respectively. In addition, he conducted visiting research at the University of California, Berkeley, CA, USA, in summer of 2002.

Since 1980, he has served as a consultant to hightech industry and research organizations and has built up strong research collaborations with high-tech industries. From 1980 to 1983, he was an Associate

Professor at National Chiao Tung University. During 1984 to 1986, he was a Visiting Associate Professor in the Department of Electrical Engineering, Portland State University, Portland, OR, USA. Since 1987, he has been a Professor at National Chiao Tung University. From 1991 to 1995, he was rotated to serve as the Director of the Division of Engineering and Applied Science on the National Science Council, Taiwan. From 1996 to 1998, he was honored as the Centennial Honorary Chair Professor at National Chiao Tung University. Currently, he is the Chair Professor at National Chiao Tung University. He has published more than 300 technical papers in international transactions/journals and conferences. He also has 45 patents including 22 U.S. patents. His research interests are implantable biomedical integrated circuits and systems, intelligent

bio-inspired sensor systems, RF/microwave communication integrated circuits, neural network, analog/mixed-signal integrated circuits, and nanoelectronics.

Dr. Wu is a member of Eta Kappa Nu and Phi Tau Phi Honorary Scholastic Societies. He was a recipient of the IEEE Fellow Award in 1998 and Third Millennium Medal in 2000. In Taiwan, he received numerous research awards from the Ministry of Education, National Science Council, and professional foundations.

**Xin-Hong Qian** (S'13) received the B.S. degree from the Department of Electronic Engineering, Chang Gung University, Taoyuan, Taiwan, in 2010. He is currently pursuing the Ph.D. degree in the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests are wireless power and data transmission, and power management ICs..

Ming-Seng Cheng received the B.S. degree from the Department of Electrical Engineering, National Chung Cheng University, Chiayi, Taiwan, in 2010, and the M.S. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 2012.

He is now an R&D electronic engineer at Mstar Semiconductor, Inc., R.O.C.

**Yu-An Liang** received the B.S. degree in electro-physics from National Chiao Tung University, Hsinchu, Taiwan, in 2009, and the M.S. degree from the Institute of Electronics, National Chiao Tung University, in 2011.

He is now an R&D electronic engineer at Mstar Semiconductor, Inc., R.O.C.

circuits design.

Wei-Ming Chen (M'13) received the B.S. degree in electro-physics from National Chiao Tung University, Hsinchu, Taiwan, in 2003, and the M.S. and Ph.D. degrees from the Institute of Electronics, National Chiao Tung University, in 2005 and 2013, respectively.

He is now an Assistant Research Fellow at Biomedical Electronics Translational Research Center (BETRC), National Chiao Tung University. His research interests include biomedical electronics, medical device integration and analog integrated