Home Search Collections Journals About Contact us My IOPscience

# Bipolar tri-state resistive switching characteristics in Ti/CeO<sub>x</sub>/Pt memory device

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Chinese Phys. B 23 126101

(http://iopscience.iop.org/1674-1056/23/12/126101)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 21/07/2015 at 09:32

Please note that terms and conditions apply.

# Bipolar tri-state resistive switching characteristics in Ti/CeO<sub>x</sub>/Pt memory device

M. Ismail<sup>a)b)†</sup>, M. W. Abbas<sup>a)</sup>, A. M. Rana<sup>a)</sup>, I. Talib<sup>a)</sup>, E. Ahmed<sup>a)</sup>, M. Y. Nadeem<sup>a)</sup>, T. L. Tsai<sup>b)</sup>, U. Chand<sup>b)</sup>, N. A. Shah<sup>c)</sup>, M. Hussain<sup>d)</sup>, A. Aziz<sup>a)</sup>, and M. T. Bhatti<sup>a)</sup>

a) Department of Physics, Bahauddin Zakariya University, Multan-60800, Pakistan

(Received 21 May 2014; revised manuscript received 4 July 2014; published online 10 October 2014)

Highly repeatable multilevel bipolar resistive switching in  $\text{Ti/CeO}_x/\text{Pt}$  nonvolatile memory device has been demonstrated. X-ray diffraction studies of  $\text{CeO}_2$  films reveal the formation of weak polycrystalline structure. The observed good memory performance, including stable cycling endurance and long data retention times (>  $10^4$  s) with an acceptable resistance ratio ( $\sim 10^2$ ), enables the device for its applications in future non-volatile resistive random access memories (RRAMs). Based on the unique distribution characteristics of oxygen vacancies in  $\text{CeO}_x$  films, the possible mechanism of multilevel resistive switching in  $\text{CeO}_x$  RRAM devices has been discussed. The conduction mechanism in low resistance state is found to be Ohmic due to conductive filamentary paths, while that in the high resistance state was identified as Ohmic for low applied voltages and a space-charge-limited conduction dominated by Schottky emission at high applied voltages.

Keywords: multilevel resistive switching, Schottky emission, cerium oxide, oxygen vacancy

**PACS:** 61.05.cp, 73.40.Rw, 73.50.-h, 77.22.Jp **DOI:** 10.1088/1674-1056/23/12/126101

### 1. Introduction

Nonvolatile memory for multilevel storage has been extensively exploited in portable electronic products. [1-4] However, traditional nonvolatile floating gate memory devices have confronted some physical limits as they are continuously scaled down. [5-7] Resistive random access memory (RRAM) is being considered as one of the potential candidates for development of the next generation nonvolatile memory because of its advantages such as low energy consumption, high density, simple device structure, and intrinsic fast switching speed. [8-10] RRAM devices are based on conductor dielectric-conductor sandwich structures which can reversibly be switched between two distinct resistance states by applying appropriate voltage. [11,12] In contrast to the conventional memory switching between the two resistance states (HRS and LRS), another kind of switching is also possible where device resistance switches between three or more levels, known as multilevel resistive switching (RS). Multilevel RS enhances storage capability which eventually leads to higher packing density of memory.<sup>[13]</sup> Many researchers have studied multilevel set/reset and tri-state RRAM devices based on rare earth/transition metal oxides. [14-17] Multilevel resistive states are usually achieved either by controlling the current compliance during the SET process or by limiting the amplitude of the voltage pulse during the RESET process. However, in our device (present study), tri-level resistance states were achieved via controlling the set and reset voltages. That is why physical

In this study, multilevel bipolar RS characteristics in the nonstoichiometric  $CeO_x$ -based RRAM device with different top electrode as reported earlier<sup>[15,16]</sup> are being demonstrated. Bipolar resistive switching behavior in our Ti/ $CeO_x$ /Pt memory device retains stable resistance ratio of approximately  $\sim 10^2$  with switching response for more than  $3 \times 10^2$  cycles. It is expected that the top electrode reacts with the  $CeO_2$  layer and forms an interfacial  $TiO_x$  layer. This oxygen-rich top interface area might play a key role in the formation and rupture of conductive filaments during multilevel resistive switching.

#### 2. Experimental procedure

In this work, Ti/CeO $_2$ /Pt-based MIM sandwich structures were fabricated. Ceria (CeO $_2$ ) films of 30 nm were deposited

b) Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan, China c) Thin Films Technology Research Laboratory, Department of Physics, COMSATS Institute of Information Technology, Islamabad-45320, Pakistan d) Center for High Energy Physics, University of Punjab, Lahore-54590, Pakistan

origin of multilevel resistive switching is different in dissimilar devices. The multilevel bipolar switching in Cu/TaO<sub>x</sub>/Pt device has been reported by Yang *et al.*<sup>[17]</sup> which was suggested due to the coupling effect between existing resistive switching mechanisms. On the other hand, a research group at Peking University has explained the multilevel bipolar resistance switching mechanism in Al/CeO<sub>x</sub>/Pt device<sup>[15,16]</sup> in terms of formation and rupture of conducting filaments composed of oxygen vacancies. Therefore, a deep understanding of characteristics and mechanism of multilevel set/reset resistive switching in oxide-based memory structures is still a challenge to be addressed for potential nonvolatile RRAM applications.

$<sup>^{\</sup>dagger} Corresponding \ author. \ E-mail: \ is mail malikbzu 10@gmail.com$

on Pt/Ti/SiO<sub>2</sub>/Si substrates at room temperature using radio frequency (rf) magnetron sputtering of a ceramic CeO2 target. Ceria film was prepared at a fixed rf power of 100 W and with argon:oxygen (6:12) flow rate of 20 sccm. The working pressure during deposition was kept at 10 mTorr (1 Torr =  $1.33322 \times 10^2$  Pa). To complete the metal-insulator-metal structure, a 50-nm thick Ti top electrode was deposited by electron beam evaporation at ambient temperature with a diameter of 150 µm patterned through a metallic shadow mask. Pt film (20 nm) was used to avoid the oxidation of Ti electrode and to prevent it from scratching by the probe during electrical characterization. Electrical characteristics of the fabricated CeO<sub>2</sub>-based resistive memory devices were measured at room temperature by Agilent B1500A semiconductor parameter analyzer. During electrical characterization, the bias voltages were applied to the Ti top electrode (TE) while the Pt bottom electrode (BE) was grounded. Crystal structure of the CeO<sub>2</sub> thin films was characterized by X-ray diffraction (XRD) in the  $2\theta$  range of  $20^{\circ}$ – $80^{\circ}$ .

#### 3. Results and discussion

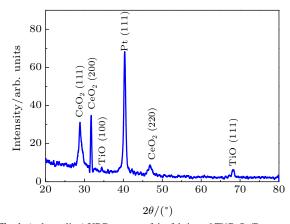

Figure 1 shows typical 3°-glancing angle XRD spectrum of CeO<sub>2</sub>-based RRAM device fabricated on Pt/Ti/SiO<sub>2</sub>/Si substrate. It depicts some broad peaks indicating that CeO<sub>2</sub> film possesses weak polycrystalline structure having only (111), (200), and (220) reflections corresponding to the diffraction angles 28.5°, 33.08°, and 47.5° respectively, yielding "fluorite cubic structure of CeO<sub>2</sub>" (JCPDS #: 34-0394). The broadening of preferred orientation (111) reflection may be caused by the significant reduction in grain size<sup>[18]</sup> as well as very small thickness of CeO<sub>2</sub> film (30 nm). In addition, a few weak reflections are also visible in this spectrum which can be assigned to (100), (111) planes of TiO (JCPDS #: 82-0803). This fact might lead to the formation of a thin TiO<sub>x</sub> interfacial layer. Such a kind of layer has been observed

**Fig. 1.** (color online) XRD pattern of the fabricated  $\text{Ti/CeO}_x/\text{Pt}$  memory device at room temperature.

by Zhao *et al.*<sup>[19]</sup> in Ti/Dy<sub>2</sub> O<sub>3</sub>/Pt device (also confirmed by TEM analysis), because Ti possesses strong oxygen affinity so oxygen ions from adjacent oxide layers tend to migrate to Ti/CeO<sub>2</sub> interface yielding a weak polycrystalline TiO<sub>x</sub> interlayer.

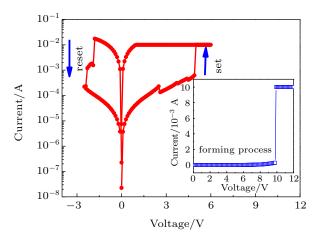

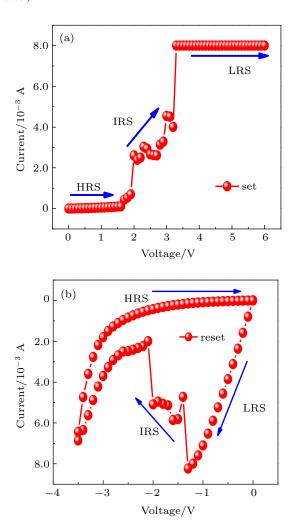

Figure 2 illustrates the current–voltage (I-V) characteristics of the Ti/CeO<sub>x</sub>/Pt memory device which exhibits tri-stable resistive switching behavior. Initially, a forming process is required for triggering the fresh CeO2-based device to demonstrate the reversible resistive switching behavior, as shown in the inset of Fig. 2. It is believed that in this initial step, a positive voltage ( $\sim 12 \text{ V}$ ) applied to the top electrode strongly attracts oxygen ions and causes the formation of oxygen vacancies in the bulk of CeO2 layer. These positively charged oxygen vacancies align along the direction of current flow under the influence of the initial voltage sweep, create conducting filamentary path(s) between the two electrodes causing a sudden rise of current analogous to soft breakdown. This process, known as "electroforming" occurs at 9.85 V under the compliance current of 10 mA. After the forming process, a negative voltage sweep (0 V to -3 V) switches the device from low resistance state (LRS) to intermediate resistance state (IRS) at about -1.9 V, and then to high resistance state (HRS) at  $\sim -2.5$  V. In the proceeding positive bias sweep (0 V to +6 V), an abrupt rise in current occurs again at a specific voltage of 5.1 V (set voltage), indicating the switching of resistance from HRS to LRS. Obviously, our Ti/CeO<sub>x</sub>/Pt device requires the same switching polarity in each set or reset cycle; as a positive bias induces the low resistance set state (LRS) and negative bias is responsible for the intermediate resistance state and hence the high resistance reset state (HRS). This tristable resistance switching behavior is reversible and controllable. Figure 3 shows multilevel set and reset resistive switching in a more convenient way. By sweeping the bias from 0 V to +6 V, a two-step set process is observed (Fig. 3(a)): "set-1" switches the device from HRS to IRS at voltage of 1.9 V,  $(V_{\text{set-1}})$ , while "set-2" further switches the device from intermediate resistance state to low resistance state at 3.2 V  $(V_{\text{set-2}})$ . A current compliance of 10 mA was adopted to protect the device from hard dielectric breakdown. In order to switch the device back to HRS, biasing voltage with reverse polarity is necessary. The reset process in Fig. 3(b) is also divided into two steps; "reset-1" switches the device from LRS to IRS at  $-1.3 \text{ V} (V_{\text{reset-1}})$ , and "reset-2" from IRS to HRS at  $-3.5 \text{ V} (V_{\text{reset-2}})$ . These results propose that the as-deposited CeO<sub>2</sub> devices have some meta-stable IRSs. To obtain multi-bit resistive random access memory (RRAM) device, these multilevel SET and RESET processes may be useful.[3,20]

**Fig. 2.** (color online) Typical bipolar tri-state resistive switching I-V characteristics of Ti/CeO<sub>x</sub>/Pt device (Inset illustrates initial forming process).

Fig. 3. (color online) Multilevel (a) set and (b) reset process in the  $\text{Ti/CeO}_x/\text{Pt}$  RRAM device.

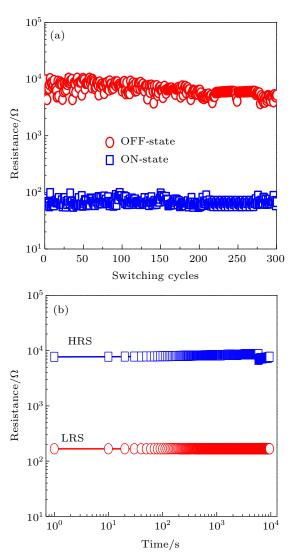

The endurance properties of our Ti/CeO<sub>x</sub>/Pt memory device are shown in Fig. 4(a). The HRS and LRS were both extracted at 0.3 V. It is worth mentioning that both HRS and LRS are stable over successive  $3 \times 10^2$  switching cycles at room temperature. The ratio of resistances between the two memory states is approximately  $10^2$ . To further demonstrate the

stability of resistive switching properties, data retention was determined by measuring the current level of our device in the ON- and OFF-states over a long period of time (>  $10^4$  s) at room temperature. The results shown in Fig. 4(b) clearly illustrate that both the LRS and HRS are stable for about  $3.5 \times 10^3$  s with well-resolved ON/OFF ratio of  $\sim 100$  with a slight degradation in HRS during last 500 s. This slight deterioration in retention behavior might be due to local damage of the active layer.

**Fig. 4.** (color online) Reliability of the proposed  $CeO_x$ -based RRAM: (a) The endurance characteristics for up to 300 cycles measured at  $V_{\rm read} = 0.3 \text{ V}$  for Ti/CeO<sub>x</sub>/Pt device, (b) retention characteristics of the Ti/CeO<sub>x</sub>/Pt device.

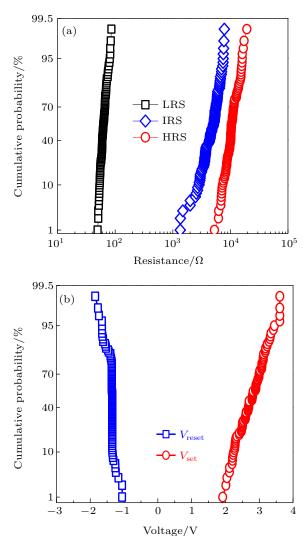

Figure 5(a) shows the statistical distributions of resistance in HRS, IRS, and LRS in dc sweeping modes. The distribution range of HRS, IRS, and LRS of our devices are from 49.7  $\Omega$  to 86.2  $\Omega$ ,  $1.3 \times 10^3$   $\Omega$  to  $7.8 \times 10^3$   $\Omega$ , and  $5.2 \times 10^3$   $\Omega$  to  $1.9 \times 10^4$   $\Omega$  respectively. It is quite evident that the fluctuations in the HRS, IRS, and LRS are very small. Figure 5(b) shows typical cycle-to-cycle variation of the switching parameters of Ti/CeO<sub>x</sub>/Pt device. The statistical data is taken over first 100 dc endurance cycles. Cumulative probability plot

for the set/reset voltages shows relatively uniform distribution with small Weibull slope as most values for the set voltage ( $V_{\rm set}$ ) range between 1.92 V and 3.62 V while for reset voltage ( $V_{\rm reset}$ ) they are mostly concentrated between -1.0 V and -1.90 V. The  $V_{\rm set}$  and  $V_{\rm reset}$  distributions demonstrate relatively stable turn-on and turn-off processes.

**Fig. 5.** (color online) (a) Statistical distributions of the resistances in HRS, IRS, and LRS measured during the voltage sweep operation up to 300 cycles in  $\text{Ti/CeO}_2/\text{Pt}$  device, (b) statistical voltage distributions ( $V_{\text{set}}$  and  $V_{\text{reset}}$ ) operated by bipolar resistive switching operations for the  $\text{Ti/CeO}_1/\text{Pt}$  device.

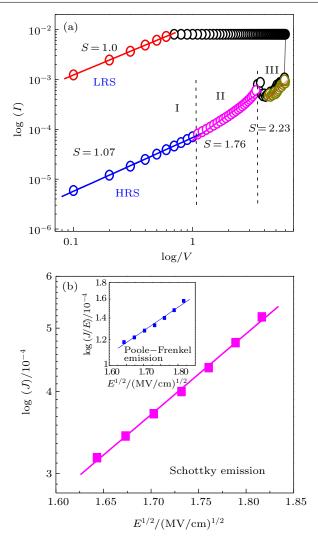

To elucidate the resistive switching behavior of our Ti/CeO<sub>x</sub>/Pt device, electrical conduction properties in both the HRS and LRS were analyzed systematically. Plots of  $\log I$ – $\log V$  in the positive bias region are shown in Fig. 6(a). Conduction in the LRS is Ohmic because the I–V curve is linear with a slope of  $\sim$  1, which is typically due to the creation of conductive filaments in  $\text{CeO}_x$  layer. However, at the HRS, the I–V characteristics are much more complicated and can be divided into three parts; within the low voltage range < 0.9 V (region-I) slope of  $\log I$ – $\log V$  plot is 1.07 which indicates Ohmic conduction due to thermally generated free electrons. [21] This may also be due to filamentary conduction

**Fig. 6.** (color online) (a) The double logarithmic I-V plots of both HRS and LRS for the  $Ti/CeO_x/Pt$  device. (b) Schottky emission linear fit curve at high voltage region in the HRS (Inset does not follow the Poole–Frenkel emission at high voltage region in the HRS).

of the accumulated oxygen vacancies into cerium oxide layer. [22] Moreover, Ohmic conduction is expected due to partial filling of traps during weak injection of charge carriers<sup>[23]</sup> from the bottom electrode Pt. On the other hand, in region-II, slope of log I-log V plot is 1.76 which might lead to trapfilling region because of increasing the injected electrons with applied bias which are captured by the traps (oxygen vacancies etc.) in the  $CeO_x$  layer. As traps in the  $CeO_x$  are all occupied by injected carriers, current enters into region-III. In addition, at the same time the Ti/CeO<sub>x</sub> interface keeps on extracting oxygen ions, thereby increasing the domain of oxygen vacancies (traps) in the bulk of CeO<sub>x</sub>. This may lead to the intermediate state, where either current decreases or remains almost constant. But in region-III, on further increasing the applied bias, more electrons will be injected from the Pt electrode because the bulk CeO<sub>x</sub> layer is incapable of supplying the excess electrons, as a result the space charge begins to form the injecting electrode interface. Thus in the high voltage region-III (> 2 V), the conduction mechanism may be attributed to trap-controlled space-charge-limited current

(SCLC). [24] Moreover, in region-III (with a slope of 2.23), the better linearity of  $\log(J)$  versus  $E^{1/2}$  plot as compared to that of  $\log(J/E)$  versus  $E^{1/2}$  plot and the mechanism discussed above indicate that the conduction mechanism is more consistent with Schottky emission as compared to Poole–Frenkel mechanism. [25]

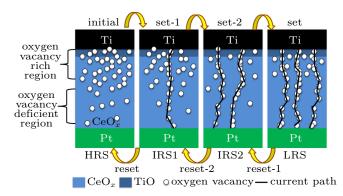

Based on the above analyses, the multilevel set and reset bipolar resistive switching in Ti/CeO<sub>x</sub>/Pt device is schematically illustrated in Fig. 7. Multilevel set and reset characteristics can be well explained based on the nonstoichiometric distribution characteristics of oxygen vacancies in Ti/CeO<sub>x</sub>/Pt device. CeO<sub>2</sub> is a material with multiple oxidation states (+3 and +4). The weak polycrystalline nature of ceria films may create variations in the lattice strain which could initiate interplay between the two oxidation states resulting in the formation of oxygen vacancies as a charge compensation. In fact the formation energy at oxide surface is relatively low, so the concentration of oxygen vacancies at the surface can be expected to be higher than that in the bulk of the sandwiched oxide. [26] Moreover, as Ti is capable to reduce CeO<sub>2</sub> so probability of a relatively richer density of oxygen vacancies near the Ti/CeO<sub>x</sub> interface is rather enhanced. While being nobel metal, the bottom electrode (Pt) is incapable of creating an appreciable amount of oxygen vacancies near the Pt/CeO<sub>x</sub> interface. The resulting non-uniform density of oxygen vacancies in the oxide layer leads to bipolar resistive switching in  $Ti/CeO_x/Pt$  device. Furthermore, the formation of  $TiO_x$  layer seems to play a significant role in the distribution and movement of oxygen vacancies as well as in the conductive filament formation/rupture. As fresh RRAM device needs the electroforming process before showing any reversible resistance switching. During forming process, the positive voltage stress applied at the top electrode pushes the positively charged oxygen vacancies from the TiO/CeO<sub>x</sub> interface into the vacancy deficient CeO<sub>x</sub> bulk to form separated line-pattern conductive filaments. This happens because oxygen vacancies have ability to distribute themselves in line-pattern between electrodes rather than an interconnected network of filaments and are separated from one another due to impulsive interactions. [15,27,28] In the subsequent reset process, the negative bias applied to top electrode pulls oxygen vacancies back to the TiO/CeO<sub>x</sub> interface from the bulk and oxygen ions towards the bulk, thus rupturing the filament(s) as illustrated in Fig. 7. The filamentary model explains the multilevel resistive switching mechanism as well. Because of the asymmetric distribution of oxygen vacancies in the active oxide layer, a filament after its formation in the set step is not likely to increase in scale. That is why the resistance of the device with only one filament may be intermediate until some additional filaments are formed at other locations when stronger biasing voltage is applied. The formation of multiple, and mutually separated, percolation paths between the two electrodes switches the device from the intermediate resistance state to low resistance state. It is noteworthy that if filamentary conduction paths were mutually connected (interconnected network of filaments), there would be practically no difference in resistance levels of the LRS and the IRS.

**Fig. 7.** (color online) Illustration of the proposed physical model to explain bipolar switching mechanism in the  $CeO_x$ -based RRAM device for the multilevel set and reset processes.

## 4. Conclusion

Nonstoichiometric CeO<sub>x</sub>-based memory device successfully demonstrated multilevel set/reset bipolar resistive switching behavior. X-ray diffraction pattern confirmed that nature of the CeO<sub>2</sub> films is weak polycrystalline as well as the formation of a thin TiO layer. The observed multilevel stable intrinsic resistance states of CeO<sub>x</sub> could be attributed to formation of separated line-pattern oxygen vacancy filaments in the CeO<sub>x</sub> film. The conduction mechanism in the LRS is of Ohmic type, whereas in HRS it can be explained by Ohmic and trap-controlled space-charge-limited conduction dominated by Schottky emission. The reliability of resistive switching characteristics and data retention ( $10^4$  s) were also verified at room temperature. The multilevel resistive switching in Ti/CeO<sub>x</sub>/Pt devices may be considered for multi-bit memory storage applications. The highly stable switching behavior in Ti/CeO<sub>x</sub>/Pt device has a great potential for nonvolatile memory applications.

# Acknowledgments

The authors acknowledge the financial support by Higher Education Commission (HEC), Islamabad Pakistan. The authors are also grateful to Prof. Dr. T. Y. Tseng, Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan for providing experimental facilities and useful suggestions.

#### References

[1] Tsai C T, Chang T C, Chen S C, Lo I, Tsao S W, Hung M C, Chang J J, Wu C Y and Huang C Y 2010 Appl. Phys. Lett. 96 242105

- [2] Chen T C, Chang T C, Tsai C T, Hsieh T Y, Chen S C, Lin C S, Hung M C, Tu C H, Chang J J and Chen P L 2010 Appl. Phys. Lett. 97 112104

- [3] Chen M C, Chang T C, Huang S Y, Chang K C, Li H W, Chen S C, Lu J and Shi Y 2009 Appl. Phys. Lett. 94 162111

- [4] Chen Y C, Chang T C, Li H W, Chen S C, Lu J, Chung W F, Tai Y H and Tseng T Y 2010 Appl. Phys. Lett. 96 262104

- [5] Chang T C, Jian F Y, Chen S C and Tsai Y T 2011 Mater. Today 14 608

- [6] Chen S C, Chang T C, Liu P T, Wu Y C, Lin P S, Tseng B H, Shy J H, Sze S M, Chang C Y and Lien C H 2007 IEEE. Electron Dev. Lett. 28 809

- [7] Chen W R, Chang T C, Yeh J L, Sze S M and Chang C Y 2008 Appl. Phys. Lett. 92 152114

- [8] Ismail M, Huang C Y, Panda D, Hung C J, Tasi T L, Jeing J H, Lin C A, Chand U, Rana A M, Ahmed E, Talib I, Nadeem M Y and Tseng T Y 2014 Nano-scale Res. Lett. 9 45

- [9] Waser R and Aono M 2007 Nat. Mater. 6 833

- [10] Tseng T Y and Sze S M 2012 An Introduction to Nonvolatile Memories, in Materials, Devices and Applications, ed. Tseng T Y and Sze S M (Am. Sci. Publ., CA, USA), Vol. 1, Chap. 1, pp. 1–9

- [11] Park I S, Kim K R, Lee S and Ahn J 2007 Jpn. J. Appl. Phys. 46 2172

- [12] Kang Y H, Choi J H, Lee T I, Lee W and Myoung J M 2011 Solid State Commun. 151 1739

- [13] Panda D, Dhar A and Ray S K 2010 J. Appl. Phys. 108 104513

- [14] Acharyya D, Hazra A, Dutta K, Gupta R K and Bhattacharyya P 2013 Semicond. Sci. Technol. 28 125001

- [15] Liu L F, Hou Y, Yu D, Chen B, Gao B, Tian Y, Han D D, Wang Y, Kang J F and Zhang X 2012 IEEE. International Conference on Electron Devices and Solid State Circuit (EDSSC), December 3–5, 2012, Bangkok, pp. 1–3

- [16] Sun X, Sun B, Liu L, Xu N, Liu X, Han R, Kang F, Xiong G and Pan T P 2009 IEEE. Electron Dev. Lett. 30 334

- [17] Yang Y C, Chen C, Zeng F and Pan F 2010 J. Appl. Phys. 107 093701

- [18] Younus A, Chu D and Li S 2012 J. Phys. D: Appl. Phys. 45 355101

- [19] Zhao T H, Wei F, Zhang X and Du J 2013 Solid-State Electron. 89 12

- [20] Kang Y, Verma M, Liu T and Orlowski M K 2012 ECS Solid State Lett. 1 Q48

- [21] Kim H D, An H M and Kim T G 2012 IEEE. Trans. Electron Dev. 59

- [22] Chen C, Yang Y C, Zeng F and Pan F 2010 Appl. Phys. Lett. 97 083502

- [23] Pan T M and Lu C H 2013 Mater. Chem. Phys. 139 437

- [24] Kao K C and Huang W 1981 *Electrical Transport in Solids* (Oxford: Pergamon) Vol. 14, p. 150

- [25] Kim H D, Yun M. J, Lee J H, Kim K H and Kim T G 2014 Sci. Rep. 4 4614

- [26] Cho B, Song S, Ji Y, Kim T W and Lee T 2011 Adv. Funct. Mater. 21

- [27] Liu T, Verma M, Kang Y and Orlowski M K 2013 IEEE. Electron Dev. Lett. 34 108

- [28] Jameson J R, Gilbert N, Koushan F, Saenz J, Wang J, Hollmer S and Kozicki M N 2011 Appl. Phys. Lett. 99 063506