## O<sub>2</sub>-Plasma Passivation Effects on Polysilicon Thin Film Transistors Using Ion Plating Method

### Ching-Fa Yeh, Tai-Ju Chen,\* and Ming-Tyang Lin

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan

#### Jiann-Shiun Kao

Precision Instrument Development Center, National Science Council, Taiwan

#### ABSTRACT

A novel method has been developed for efficiently reducing defect density in polysilicon thin film transistors using ion plated oxides as capping layers. The characteristics of these novel thin film transistors are superior to those of thin film transistors with plasma-enhanced chemical vapor deposited tetraethylorthosilicate capping oxides due to an in situ  $O_2$ -plasma passivation effect during ion plating oxide deposition. The passivation effect of a  $NH_3$  plasma on the novel devices was also studied. The in situ ion plating  $O_2$  plasma shows a better passivation efficiency on trap states than the  $NH_3$  plasma. Polysilicon thin film transistors with ion plating capping oxides are hardly degraded even when stressed with a bias of 20~V at  $100^{\circ}C$ .

#### Introduction

It is well known that polycrystalline silicon (poly-Si) films have a high concentration of grain boundary defects as well as intragrain defects. As a result of the high density of trapping states in poly-Si films, it has been found necessary to passivate them to improve poly-Si thin film transistor (TFT) performance. 1,2 Various technologies have been proposed to reduce trapping states in poly-Si films, such as hydrogenation,1-4 O<sub>2</sub> plasma,5 and NH<sub>3</sub> plasma.6 So far, the most popular passivation procedure has been to expose devices to hydrogen plasma. However, it takes a long time to achieve satisfactory performance, and the improvement shows a tendency to saturate.4 In addition, hydrogenated TFTs are quite prone to reliability problems due to carrier-induced trap states in poly-Si channels.7 These shortcomings greatly limit the practical application of H<sub>2</sub>-plasma passivation. In recent years, the passivation effect of an O2 plasma has attracted much attention because of its better passivation efficiency and stability.<sup>5</sup> It has been suggested that O<sub>2</sub>-plasma treatment can improve the performance of poly-Si TFTs by passivating deep states and tail states. Furthermore, it has been reported that after an O<sub>2</sub>-plasma treatment, subsequent treatment with a H<sub>2</sub> plasma was even more efficient in passivating trap states in poly-Si films.<sup>5</sup>

Recently, a low-temperature ion plating (IP) method has been proposed to prepare high-performance oxide films. IP oxide has been shown to be feasible for application as a poly-Si TFT gate insulator, and to contribute to excellent device characteristics. Since an O<sub>2</sub> plasma is present in the chamber during IP oxide deposition, it can be expected to have the effect of trap-state passivation on the poly-Si layer. In this paper, we try to apply IP oxides as capping layers on poly-Si TFTs, and investigate passivation effects owing to the in situ O<sub>2</sub> plasma. The passivation of dangling bonds is examined by electron spin resonance (ESR) measurement. NH<sub>3</sub>-plasma passivation effects and the reliability of the novel poly-Si TFTs are also studied.

#### Experimental

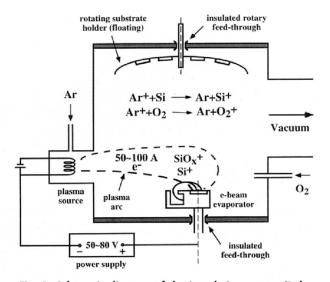

Preparation of IP oxide.—IP oxide films were prepared using the ion-plating system (Balzers BAP 800),  $^{9,12,13}$  shown in Fig. 1. The starting silicon material was evaporated using an electron-beam evaporator. Simultaneously the evaporator crucible served as the anode for an argon plasma discharge. The high arc current was 56 A, while the low arc voltage ( $V_{arc}$ ) was 66 V and the anode-to-ground voltage ( $V_{anode}$ ) was 46 V. Argon at 3.9 mbar in the plasma

source cavity was ionized by the heated filament, and it was at  $3.4 \times 10^{-4}$  mbar in the deposition chamber. Oxygen gas was let directly into the deposition chamber to fix the deposition pressure at  $1.1 \times 10^{-3}$  mbar, while the base pressure was  $3.6 \times 10^{-5}$  mbar. The evaporant (Si) and the reactive gas (O2) were activated and ionized by the argon plasma. The substrate holder was electrically isolated from the ground chamber without an applied bias, i.e., it was allowed to float. The substrate gathered electrons from the plasma sheath, and then obtained a negative selfbias  $(V_s)$  of -10 to -20 V (the body of the plasma). This negative bias accelerated the positive ions of the evaporant (Si), the reactive gas (O2), and the argon plasma onto the surface of the substrate, and the film formed. The positive ions tended to neutralize the received electrons, but the substrate was able to gather additional electrons from the plasma sheath immediately. The IP oxide film was deposited at a rate of 0.2 nm/s. No heater was applied to the substrate holder during deposition.

In conventional IP system the degree of ionization is too low to effectively deposit film, so the accelerating voltage must be rather high (generally 3  $\sim$  5 kV with a current density of 0.3  $\sim$  0.8 mA/cm²) to supply sufficient energy.  $^{14.15}$  In addition, the small quantity of ions is also disadvantageous for a reactive gas process. To overcome these prob-

Fig. 1. Schematic diagram of the ion-plating system (Balzers BAP 800).

<sup>\*</sup> Electrochemical Society Student Member.

lems, a new IP system of BAP 800 has been developed. <sup>16</sup> In this new system the evaporant and the reactive gas can be effectively ionized and activated by a low-voltage (50  $\sim$  80 V) high-current (50  $\sim$  100 A) plasma arc. The arc current can be controlled directly, while the resultant arc voltage is also monitored. With respect to ground, a positive potential (V<sub>anode</sub>) of 40  $\sim$  60 V is applied to anode. It is recommended to have a potential difference of +20 V between V<sub>arc</sub> and V<sub>anode</sub>. Positive ions (Ar, evaporant, and reactive gas) will be accelerated to the substrate holder owing to a negative self-bias (–10 to –20 V) V<sub>s</sub> = V<sub>p</sub> – V<sub>f</sub>, where V<sub>p</sub> and V<sub>f</sub> are the plasma and the substrate floating potential, respectively. The film quality is thus improved because of high-energy atoms and the high-reactivity plasma. <sup>17</sup>

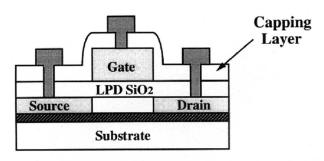

Fabrication of poly-Si TFTs.—Conventional co-planar N-channel poly-Si TFTs were prepared using the following procedures. The cross-sectional structure of the poly-Si TFTs is shown in Fig. 2. A 100 nm thick low-pressure chemical vapor deposition (LPCVD) amorphous Si layer was deposited on thermal oxide at 550°C using SiH<sub>4</sub> gas. Recrystallization was performed at 600°C for 24 h using the solid-phase crystallization (SPC) method. A 40 nm thick liquid-phase deposited (LPD) oxide layer $^{18}$  was grown on the island-patterned SPC layer at 18°C, and then densified at 600°C for 1 h in O2 ambient. A 300 nm thick poly-Si layer was deposited using the LPCVD method at 620°C. After the poly-Si gates were patterned, the source/drain and gate regions were implanted with phosphorus ions (40 keV,  $5 \times 10^{15}$  cm<sup>-2</sup>) by self-aligned technology. Dopant activation was performed at 600°C for 24 h in N2 ambient. The 500 nm thick capping layer was deposited at a rate of 0.2 nm/s for about 42 min using the IP method. The temperature of the substrate was 23°C at the beginning of the IP oxide deposition process, and increased to 110°C at its end. After contact holes were opened, aluminum electrodes were prepared and sintered at 400°C for 30 min in N<sub>2</sub> ambient. The maximum processing temperature was 620°C

For comparison, poly-Si TFTs with 32.5 nm thick LPD gate oxides and 500 nm thick tetraethyl orthosilicate (TEOS) capping oxides were prepared. The TEOS oxide was deposited at 300°C using the plasma-enhanced CVD (PECVD) method. Hydrogenation by the NH $_3$ -plasma treatment was performed in a parallel-plate reactor at 300°C with a power density of 0.7 W/cm $^2$ .

ESR measurements.—The dangling bond density in poly-Si films was measured by room-temperature ESR absorption spectra (X-band) before and after the in situ  $\rm O_2$ -plasma treatment. Poly-Si films were prepared by the LPCVD method at 620°C to a thickness of 300 nm onto thermally oxidized Si-wafer. IP oxide was directly deposited on the poly-Si films, and then annealed at 400°C for 30 min in  $\rm N_2$  ambient. This is because devices were sintered after metallization in TFT fabrication processes. The deposition condition of IP oxide was the same as that of the IP capping oxide for poly-Si TFTs. Before ESR measurements, the IP oxide and the back side poly-Si/thermal oxide were removed.

Fig. 2. Cross-sectional structure of the poly-Si TFTs.

Table I. Physicochemical and electrical properties of IP and thermal oxides.

| Ion plating oxide     | Thermal oxide                                                  |

|-----------------------|----------------------------------------------------------------|

| 1056                  | 1076                                                           |

| 1.483                 | 1.463                                                          |

| 4.9                   | 2.0                                                            |

| $8.5	imes10^{-10}$    | $1.1 	imes 10^{-9}$                                            |

| 9.3                   | 9.4                                                            |

| 4.5                   | 3.9                                                            |

| -0.67                 | -1.68                                                          |

| $1.83 \times 10^{10}$ | $4.50 	imes 10^9$                                              |

|                       | $1056$ $1.483$ $4.9$ $8.5 \times 10^{-10}$ $9.3$ $4.5$ $-0.67$ |

#### **Results and Discussion**

IP oxide characteristics.—Table I summarizes the typical physicochemical and electrical properties of 97 nm thick IP oxide deposited at room temperature. Those of thermal oxide ( $\sim$ 97 nm) grown in dry  $O_2$  at 1000°C are also shown for comparison. These two kinds of oxides were all prepared on 3 in. p-type (100)Si substrates. The thickness and the refractive index were measured by ellipsometer, while the chemical structure was analyzed by Fourier transform infrared spectrophotometer (FTIR). The etching rate was examined with P-etch solution (48% HF: 70%  $HNO_3$ :  $H_2O = 3:2:60$ ) at room temperature. To investigate the electrical properties of these oxides, metal-oxide-silicon (MOS) capacitors with aluminum gates were prepared. The current-voltage (I-V) and capacitance-voltage (C-V) characteristics were measured with an HP4145B and a Keithley Package 82 system, respectively.9 The IP oxides have a lower FTIR stretching frequency, a higher refractive index, a higher P-etch rate, and a higher dielectric constant. These features suggest that IP oxide is a high-density material with strained bonds.<sup>9,19</sup> The electrical properties of IP oxide are comparable to those of thermal oxide, and include low leakage current, high dielectric breakdown field, and few oxide charges. These excellent properties suggest that IP oxide is feasible for application as a capping layer in poly-Si TFTs.

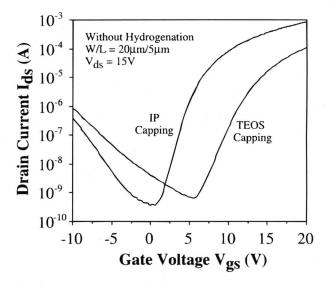

Characteristics of poly-Si TFTs with IP oxides as capping layers.—Figure 3 shows the transfer characteristics of both poly-Si TFTs (W/L =  $20/5~\mu m$ ) with IP and with TEOS oxides as capping layers, respectively. The charac-

Fig. 3. Typical transfer characteristics ( $I_{ds}$ - $V_{gs}$ ) at  $V_{ds}=15$  V for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers without hydrogenation.

Table II. Device characteristic parameters for poly-Si TFTs (W/L =  $20/5~\mu m$ ) with IP and with TEOS capping layers before and after  $8~h~NH_3$ -plasma treatment.

| Capping<br>layer | NH <sub>3</sub> -<br>plasma<br>treatmen | t (V)               | S.S.<br>(V/dec) | $ m I_{on}/I_{off}$                      | $\mu_{FE}$ (cm <sup>2</sup> /V s) | N <sub>t</sub> (cm <sup>-2</sup> )             |

|------------------|-----------------------------------------|---------------------|-----------------|------------------------------------------|-----------------------------------|------------------------------------------------|

| IP               | <br>No                                  | 4.23                | 0.94            | $4.10 \times 10^{6}$                     | 24.3                              | $1.05 \times 10^{13}$                          |

| TEOS             | 8 h<br><b>N</b> o                       | $\frac{2.33}{11.0}$ | $0.77 \\ 1.61$  | $3.18 \times 10^6$<br>$2.09 \times 10^6$ | $25.6 \\ 9.71$                    | $8.37 \times 10^{12}$<br>$2.70 \times 10^{13}$ |

| 1200             | 8 h                                     | 5.49                | 0.84            | $4.75 \times 10^{6}$                     | 14.4                              | $1.05 \times 10^{13}$                          |

teristics were measured at  $V_{ds}$  = 15 V before hydrogenation. The IP capped device obviously exhibits better performance than that of the TEOS capped device, even when the TEOS capped device has a thinner LPD gate insulator. The key characteristic parameters of the two samples are summarized in Table II. Compared to the TEOS capped device, the IP capped device shows a smaller threshold voltage (V<sub>th</sub>) of 4.23 V, a smaller subthreshold swing (S.S.) of 0.94 V/dec, a higher on/off current ratio ( $I_{on}/I_{off}$ ) of 4.10  $\times$  10 $^6$ , and a higher field-effect mobility ( $\mu_{\text{FE}}$ ) of 24.3 cm²/V s. It is evident that the use of IP capping oxides indeed improves the performance of poly-Si TFTs. The above-mentioned superior device characteristics suggest that the IP capped device has a lower trap-state density (N<sub>t</sub>) in the poly-Si channel. We can further calculate the effective trap-state density using the modified Levinson theorem.  $^{20,21}$  The  $N_{\rm t}$  in the IP capped device is  $1.05 \times 10^{13}$  cm<sup>-2</sup>, while it is  $2.70 \times$ 10<sup>13</sup> cm<sup>-2</sup> in the TEOS capped device. We believe that the decrease in N<sub>t</sub> for the IP capped device can be attributed to the effect of in situ O2-plasma passivation during the deposition of IP capping oxides.

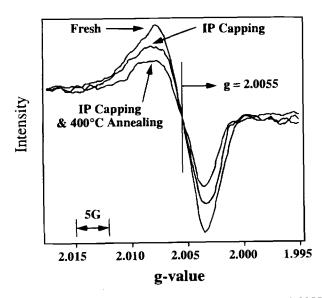

To directly evaluate the variation of defects after the in situ O2-plasma treatment, dangling bond density in poly-Si films was also measured using ESR. Figure 4 shows the ESR absorption spectra with a resonance at g = 2.0055 for the poly-Si films before and after capping IP oxide. The ESR signal intensity decreases after capping IP oxide, which indicates the reduction of the spin density  $(N_s)$  in poly-Si films.  $N_s$  is  $6.68\times 10^{18}~cm^{-3}$  for the fresh specimen (before capping IP oxide), while it is  $5.32 imes 10^{18}$ cm<sup>-3</sup> for the IP capped specimen before annealing. It is evident that Si dangling bonds decrease after capping IP oxide. Moreover,  $N_s$  is further reduced to  $3.12 \times 10^{18}$  cm  $^{-3}$ for the IP capped specimen after 400°C annealing. The anneal enhances oxygen diffusion and passivation efficiency. Hence, we can demonstrate that ÎP capping oxide indeed possesses passivation effects.

Fig. 4. ESR absorption spectra with a resonance at g=2.0055 for the poly-Si films before and after capping IP oxide.

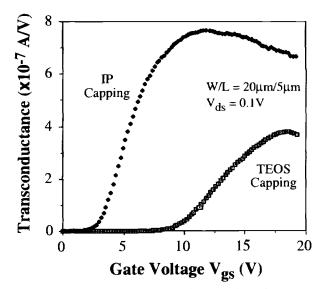

Fig. 5. Transconductance (Gm) as a function of gate bias at  $V_{\rm ds}=0.1$  V for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers.

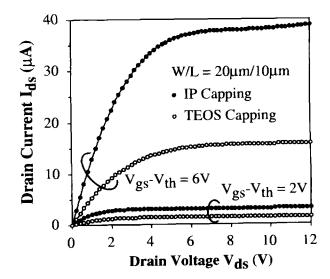

Figure 5 shows transconductance (Gm) as a function of gate bias measured at  $V_{ds} = 0.1 \text{ V}$  for both IP capped and TEOS capped poly-Si TFTs (W/L =  $20/5 \mu m$ ). The maximum Gm is  $7.6 \times 10^{-7}$  A/V for the IP capped device, while it is  $3.8 \times 10^{-7}$  A/V for the TEOS capped device. In addition, the gate voltage yielding the maximum Gm is also comparatively small for the IP capped device. Figure 6 shows the output characteristics ( $I_{ds}$ - $V_{ds}$ ) with  $V_{gs}$ - $V_{th}=2$  V and 6 V for both IP capped and TEOS capped devices  $(W/L = 20/10 \mu m)$ . In the curves of IP capped device, both the high slope in the linear region and the high saturation current imply that channel conductance is high. Generally in poly-Si TFTs, the transport of free carriers between the grains is impeded by the potential barrier owing to the trap states at the grain boundaries.<sup>22,23</sup> The lower barrier height makes On-state performance respond much faster to the applied gate and drain biases. In the IP capped device, the increases in transconductance and channel conductance can be attributed to the lowering of barrier height due to the reduction of trap-state density.

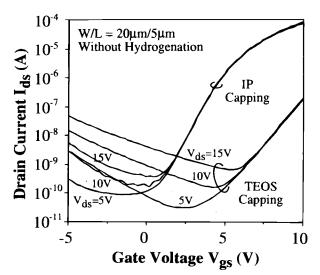

Figure 7 shows the transfer characteristics in the low gate bias region at  $V_{\rm ds}=5,\,10,\,{\rm and}\,\,15$  V for both IP capped

Fig. 6. Output characteristics ( $I_{ds}$ - $V_{ds}$ ) with  $V_{qs}$ - $V_{th}$  as a parameter for poly-Si TFTs (W/L = 20/10  $\mu$ m) with IP and with TEOS oxides as capping layers.

and TEOS capped poly-Si TFTs without hydrogenation  $(W/L = 20/5 \mu m)$ . In the case of  $V_{ds} = 5 V$ , the IP capped device shows a rather flat leakage characteristic independent of gate bias except for a higher minimum leakage current  $(I_{min})$ . The minimum leakage current is dominated by the channel resistance.<sup>24</sup> In this region, the barrier height that transfer carriers have to surmount at the grain boundary will govern the magnitude of the minimum leakage current. The higher the barrier height, the lower the minimum leakage current observed. Because there is a lower trap-state density in the IP capped device, the barrier height and thus the channel resistance are lower than those in the TEOS capped device. Thus,  $I_{min}$  is a little higher in the IP capped device. When the drain voltage was increased to 15 V,  $I_{min}$  was dominated by Frenkel-Poole emission in the drain junction depletion region.24 Frenkel-Poole emission current is contributed by field-enhanced thermal excitation of trapped holes in the valence band. Owing to the lower trap-state density, the IP capped device exhibited a lower leakage current than the TEOS capped device at  $V_{ds} = 15 \ V$ . In addition, when the drain bias was increased, the leakage current in the IP capped device also showed a smaller variation due to its lower trap-state density.

Some authors have reported that for poly-Si TFTs an O<sub>2</sub>plasma-treatment cannot passivate grain boundary defects according to the unchanged ESR signals of defect density. The O2 plasma can only clean the device surface and grow a thin SiO<sub>2</sub> layer, which can reduce the surface leakage current.<sup>25</sup> However, our studies show that the improvement in IP capped TFTs is assuredly due to the in situ O<sub>2</sub>-plasma passivation effect. As shown in Fig. 4, the reduced spin density owing to capping IP oxide indicates that the IP process possesses passivation effects. In addition, to clarify the influences of IP process and surface cleaning, we also prepared a IP/TEOS capped TFT sample. After capping IP oxide on TFTs and annealing at 400°C for 30 min in N<sub>2</sub> ambient, we removed the IP oxide using HF solution and then deposited TEOS capping oxide. For the TEOS capped TFT, we also ever removed the native oxide on the surface before capping TEOS oxide. It means that the IP/TEOS capped TFT and the TEOS capped TFT have the same surface conditions. We found that the IP/TEOS capped TFT and the IP capped TFT exhibit almost the same characteristics. It reveals that for the IP/TEOS capped TFT the trap states have been effectively reduced even though the IP capping oxide is removed. We can conclude that for the IP capped TFTs the improvement is due to the IP plasma treatment instead of the surface cleaning.

It has been reported that the passivation during O<sub>2</sub>-plasma treatment is due to the incorporation of hydrogen,

Fig. 7. Transfer characteristics ( $l_{ds}$ - $V_{gs}$ ) in low gate bias region at  $V_{ds}=5$ , 10, and 15 V for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers without hydrogenation.

which is activated by electron-impact dissociation of water vapor.  $^{26}$  In the BAP 800 IP system, the residual water pressure is about  $10^{-7}$  mbar at a base pressure of  $4\times10^{-5}$  mbar at  $23^{\circ}\text{C}$ , while it is about  $10^{-9}$  mbar at the substrate temperature of  $300^{\circ}\text{C}$ . We also prepared IP capped TFTs with the deposition of IP oxide at  $300^{\circ}\text{C}$ . TFTs with high-temperature IP oxide exhibit more excellent characteristics than those with room-temperature IP oxide. It is hard to believe that the hydrogen passivation will occur in such low residual water pressure. In addition, generally the hydrogen-passivated dangling bonds are easily broken at annealing temperature greater than  $400^{\circ}\text{C}.^{5,27,28}$  However, as shown in Fig. 4, the dangling bonds decrease after  $400^{\circ}\text{C}$  annealing. We conclude that the passivation effect during IP process can be attributed to the in situ  $O_2$  plasma.

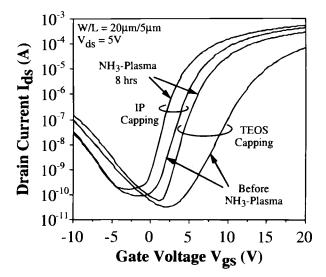

Effects of NH<sub>3</sub>-plasma passivation.—The poly-Si TFTs in this research were exposed to the NH3 plasma for trapstate passivation to further improve their performance. Figure 8 shows the typical transfer characteristics of both IP capped and TEOS capped poly-Si TFTs before and after an 8 h NH $_3$ -plasma treatment at  $V_{\rm ds}=5$  V (W/L =  $20/5 \mu m$ ). Device performances were both improved after this 8 h NH<sub>3</sub>-plasma treatment. The key characteristic parameters after the NH<sub>3</sub>-plasma treatment are also summarized in Table II. Although the improvement in the TEOS capped devices is more apparent after the NH<sub>3</sub>plasma treatment, in total the characteristics of IP capped devices are still superior to those of TEOS capped devices. For both IP capped and TEOS capped TFTs, the minimum leakage current did not well decrease after 8 h NH<sub>3</sub>-plasma treatment. It can be attributed to the insufficient passivation time. Generally,  $I_{min}$  is dominated by the total resistance in active layer. The total resistance is composed of the junction resistance at the drain junction and the channel resistance. When the passivation is insufficient,  $I_{\min}$  is dominated by the channel resistance. The decrease of trap states after  $NH_3$ -plasma treatment can result in the reduction in barrier height. The lower the barrier height, the lower the channel resistance, and then the higher  $I_{min}$  is observed. However, after NH3-plasma passivation the leaky junction depletion can also be passivated resulting in an increased junction resistance. When the passivation is sufficient, the junction resistance can become larger than the channel resistance. In that case,  $\boldsymbol{I}_{\!\scriptscriptstyle{min}}$  can be dominated by the junction resistance and become reduced. 4,29-31

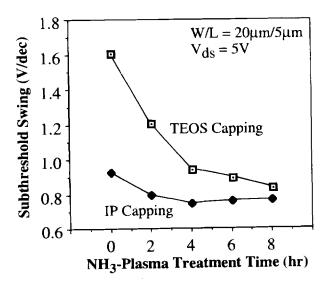

Figure 9 shows a comparison of subthreshold swing between IP capped and TEOS capped devices as a function of NH $_3$ -plasma passivation time. It was found that the improvement in the IP capped device saturated after 2 h.

Fig. 8. Transfer characteristics ( $I_{ds}$ - $V_{gs}$ ) at  $V_{ds}=5$  V for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers before and after 8 h NH<sub>3</sub>-plasma treatment.

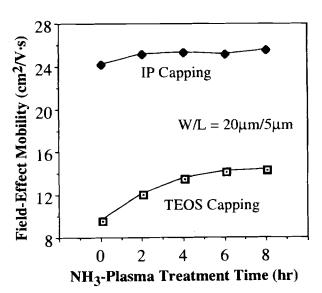

However, there was a dramatic improvement in subthreshold swing for the TEOS capped device when the NH3-plasma passivation time was increased. The threshold voltage change tendencies for both types of device after the NH<sub>3</sub>plasma treatment were similar to those for subthreshold swing. The apparent improvement in S.S. and  $V_{th}$  for TEOS capped devices can be attributed to a reduction of midgap deep states after NH<sub>3</sub>-plasma passivation.<sup>4,32</sup> The improvement for IP capped devices appears smaller and quickly saturated because many deep states were passivated by the in situ O2 plasma during IP capping oxide deposition, and only some residual deep states could be further passivated by the NH<sub>3</sub>-plasma treatment. Figure 10 shows the changes in field-effect mobility as a function of NH3-plasma passivation time for IP capped and TEOS capped devices. The gradual increase in  $\mu_{\text{FE}}$  for the TEOS capped devices indicates that some tail states were passivated by the NH<sub>3</sub>-plasma treatment.<sup>3,32</sup> However, the improvement saturated after the 8 h NH3-plasma treatment, and the saturated  $\mu_{FE}$  was still smaller than that of the as-fabricated IP capped device. This indicates that the in situ O<sub>2</sub>-plasma treatment can more effectively passivate the tail states in the poly-Si films than the NH<sub>3</sub>-plasma treatment. Hence, the subsequent NH<sub>3</sub>-plasma treatment nearly has no influence on  $\mu_{\text{FE}}$  for IP capped devices. The above results support the feasibility of fabricating excellent poly-Si TFTs without additional hydrogenation.

For PECVD TEOS capped TFTs, it must be clarified whether the requirement of more hydrogen passivation is due to PECVD TEOS charge damage. If there is serious charge damage during PECVD TEOS process, the characteristics of IP/TEOS capped TFTs will be worse than those of IP capped TFTs. However, we did not find this phenomenon. Therefore, the PECVD TEOS charge damage can be ignored.

Stability of in situ  $O_2$  plasma passivation.—The stability of poly-Si TFTs is of significant importance from a long-term operation standpoint. It has been reported that  $H_2$ -plasma treated devices exhibited higher degradation rates than  $O_2$ -plasma treated devices.<sup>5</sup> In this section, the stability of as-fabricated IP capped TFTs and  $NH_3$ -plasma treated TEOS capped TFTS is investigated.

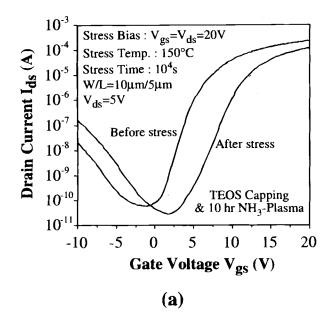

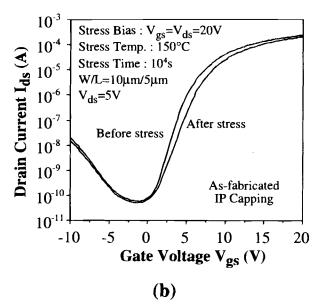

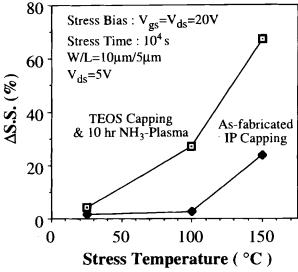

To accelerate degradation and investigate thermal stability, both the as-fabricated IP capped devices and the 10 h NH<sub>3</sub>-plasma treated TEOS capped devices were stressed with  $V_{\rm ds}=V_{\rm gs}=20$  V at  $150^{\circ}{\rm C}.$  Figure 11 (a) and (b) show the changes in transfer characteristics for the two devices before and after stressing for  $10^4$  s. The degradation of the TEOS capped devices is very noticeable. The S.S. increased from 0.82 to 1.27 V/dec, while the  $V_{\rm th}$

Fig. 9. Subthreshold swing as a function of NH $_3$ -plasma passivation time for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers.

Fig. 10. Field-effect mobility as a function of NH $_3$ -plasma passivation time for poly-Si TFTs (W/L = 20/5  $\mu$ m) with IP and with TEOS oxides as capping layers.

increased from 5.30 to 8.87 V because high-temperature dc stressing appears to break the Si-H bonds, resulting in additional trap states generated at grain boundaries.7,23 Hence, the stressing degrades the S.S. and V<sub>th</sub> characteristics of the TEOS capped devices toward prehydrogenated values. On the other hand, the degradation of the as-fabricated IP capped devices was slight because of the higher bond strength of Si-O bonds over that of Si-H bonds.34-36 Hence, fewer additional trap states were generated during high-temperature dc stressing for devices treated with in situ O2-plasma passivation. Figure 12 shows the subthreshold swing degradation rate ( $\Delta S.S.$ ) as a function of stress temperature for the as-fabricated IP and the NH<sub>3</sub>plasma treated TEOS capped devices under stressing at V<sub>ds</sub>  $V_{\mbox{\tiny gs}} =$  20 V for  $10^4$  s.  $\Delta S.S.$  for the  $NH_3\mbox{-plasma}$  treated TEOS capped device appears very sensitive to and seriously affected by the stressing temperature. However,  $\Delta S.S.$  for the IP capped device appears rather stable until the temperature exceeded 100°C. From this result, it can be concluded that the novel poly-Si TFTs with IP capping oxides indeed exhibit good stability even when stressed at high temperatures and high biases.

#### Conclusions

Poly-Si TFTs with IP oxides as capping layers exhibit excellent performance, which is due to in situ O2-plasma passivation effect during IP process, not the material of IP oxide itself. The in situ  $O_2$ -plasma treatment effectively reduces the trap states in poly-Si films, resulting in a threshold voltage of 4.23 V, a subthreshold swing of 0.94 V/dec, a field-effect mobility of 24.3 cm<sup>2</sup>/V s, and an On/Off current ratio of  $4.10 \times 10^6$  without hydrogenation. Poly-Si TFTs with IP capping oxides also show a small increase in leakage current as drain bias is increased. Because most of the trap states (particularly the tail trap states) are passivated by the O2 plasma, the improvement provided by the NH3-plasma treatment of poly-Si TFTs with IP capping oxides is not very evident. It is feasible to fabricate these novel poly-Si TFTs without additional hydrogenation. The novel devices also show superior stability even under stressing at 100°C with high  $V_{\rm gs}$  and  $V_{\rm ds}.$

#### Acknowledgment

This study was supported by the National Science Council, Taiwan, under Contract No. NSC 85-2215-E-009-036, and also partly supported by Precision Instrument Development Center, National Science Council, Taiwan.

Fig. 11. Changes in transfer characteristics ( $I_{ds}$ - $V_{gs}$ ) under stress of  $V_{ds}=V_{gs}=20$  V for  $10^4$  s at  $150^{\circ}$ C for (a) TEOS capped devices after NH $_3$ -plasma treatment, and (b) as-fabricated IP capped devices (W/L =  $10/5~\mu m$ ).

Manuscript submitted January 14, 1997; revised manuscript received October 10, 1997.

National Chiao-Tung University assisted in meeting the publication costs of this article.

#### REFERENCES

- 1. A. Mimura, K. Miyata, T. Suzuki, Y. Hosokawa, H. Kawakami, N. Konishi, Y. A. Ono, K. Ono, and J. Ohwada, IEEE Trans. Electron Devices, 36, 351 (1989)

- 2. T. I. Kamins and P. J. Marcoux, IEEE Electron Device *Lett.*, **1**, 159 (1980).

- 3. S. D. Brotherton, J. R. Ayres, and N. D. Young, Solid-

- S. D. Brotherton, 3. R. Ayres, and W. D. Toung, Some-State Electron., 34, 671 (1991).

I.-W. Wu, T.-Y. Huang, W. B. Jackson, A. G. Lewis, and A. Chiang, IEEE Electron Device Lett., 12, 181

- 5. H. N. Chern, C. L. Lee, and T. F. Lei, IEEE Trans. Elec-

- tron Devices, 40, 2301 (1993). 6. F. S. Wang, M. J. Tsai, and H. C. Cheng, IEEE Electron Device Lett., 16, 503 (1995).

Fig. 12. Subthreshold swing degradation rates (ΔS.S. (%)) under stresses of  $V_{ds}=V_{gs}=20$  V for  $10^4$  s at 25, 100, and 150°C for TEOS capped devices after NH<sub>3</sub>-plasma treatment and as-fabricated IP capped devices (W/L =  $10/5~\mu m$ ).

- 7. I.-W. Wu, W. B. Jackson, T.-Y. Huang, A. G. Lewis, and A. Chiang, *ibid.*, **11**, 167 (1990).

- 8. M. Hack, A. G. Lewis, and I.-W. Wu, IEEE Trans. Elec-

- tron Devices, 40, 890 (1993).

9. C. F. Yeh, T. J. Chen, C. L. Fan, and J. S. Kao, IEEE Electron Device Lett., 17, 421 (1996).

10. N. M. Johnson, D. K. Biegelsen, and M. D. Moyer, Appl.

- N. M. Johnson, D. K. Biegeisen, and M. D. Moyer, Appl. Phys. Lett., 40, 882 (1982).

H. Kakinuma, M. Mohri, M. Sakamoto, and T. Tsuruoka, J. Appl. Phys., 70, 7374 (1991).

H. K. Pulker, J. Vac. Sci. Technol., A10, 1669 (1992).

K. H. Guenther, B. Loo, D. Burns, J. Edgell, D. Windham, and K. H. Muller, ibid., A7, 1436 (1989).

D. M. Mattox, J. Vac. Sci. Technol., 10, 47 (1973).

D. M. Mattox in Ion Plating and Allied Technologies.

- 15. D. M. Mattox, in Ion Plating and Allied Technologies,

- p. 1 (1979). 16. H. K. Pulker, in *Thin Film Technologies III*, p. 138,

- SPIE-Int. Soc. Opt. Eng. (1988). 17. A. J. Waldorf, J. A. Dobrowolski, B. T. Sullivan, and L.

- M. Plante, Appl. Opt., 32, 5583 (1993).

18. C. F. Yeh, S. S. Lin, C. L. Chen, and Y. C. Yang, IEEE

- Electron Device Lett., 14, 403 (1993). 19. C. F. Yeh, T. J. Chen, C. L. Fan, and J. S. Kao, in *Inter*national Conference on Solid State Device and Mate-

- rial (SSDM), p. 491 (1995).

20. J. Levinson, G. Este, M. Rider, P. J. Scanlon, F. R. Shepherd, and W. D. Westwood, J. Appl. Phys., 52, 1193 (1982).

- R. E. Proano, R. S. Misage, and D. G. Ast, *IEEE Trans. Electron Dev.*, **36**, 1915 (1989).

J. Y. T. Seto, *J. Appl. Phys.*, **46**, 5247 (1975).

G. Baccarani, B. Ricco, and G. Spadini, *ibid.*, **49**, 5565 (1976).

- (1978).

- (1976).

24. C. F. Yeh, T. Z. Yang, C. L. Chen, T. J. Chen, and Y. C. Yang, Jpn. J. Appl. Phys., 32, 4472 (1993).

25. N. H. Nickel, P. Mei, and J. B. Boyce, IEEE Trans. Electron Devices, 42, 1559 (1986).

26. N. H. Nickel, A. Yin, and S. J. Fonash, Appl. Phys.

- Lett., 65, 3099 (1994).

27. J. D. Bernstein, S. Qin, C. Chan, and T.-J. King. IEEE

- Trans. Electron Devices, 43, 1876 (1996).

- 28. M. Cao, T. Zhao, K. C. Saraswat, and J. D. Plummer, ibid., **42**, 1134 (1995)

- 29. F. Qian, D. M. Kim, H. K. Park, and J. L. Sachitano, F. Glain, D. M. Rim, H. K. Fark, and J. D. Sachitano, ibid., 35, 2439 (1987).

K. Ono, T. Aoyama, and N. Konishi, and K. Miyata, ibid., 39, 792 (1992).

D. L. Chen, D. W. Greve, and A. M. Guzman, ibid., 33, 270 (1992).

- 270 (1986).

- B. A. Khan, R. Pandya, *ibid.*, 37, 1727 (1990).

S. Banerjee, H. Shichijo, R. Sundaresan, and S. Malhi, *ibid.*, 35, 152 (1988).

- 34. R. L. David, CRC Handbook of Chemistry and Physics:

A Read-Reference Book of Chemical and Physical Data, 73rd ed., p. 9, Chemical Rubber Co. Press., Florida (1992).

35. K. P. Hubert and G. Herzber, Molecular Spectra and

Molecular Structure Constants of Diatomic Molecules, Van Nostrand, New York (1979).

J. B. Pedley and E. M. Marshall, J. Phys. Chem. Ref. Data, 12, 967 (1984).

# Boron Diffusion in Compressively Stressed Float Zone-Silicon Induced by Si<sub>3</sub>N<sub>4</sub> Films

Y. Zaitsu, T. Shimizu, J. Takeuchi, S. Matsumoto, M. Yoshida, T. Abe, and E. Araid

<sup>a</sup>Faculty of Science and Technology, Keio University, 3-14-1 Hiyoshi, Yokohama 223, Japan

<sup>b</sup>Kyusyu Institute of Design, Shiobaru, Minami-ku, Fukuoka 815, Japan

<sup>c</sup>Shin-Etsu Handotai Company, Limited, SEH Research and Development Center, 2-13-1 Isobe, Annaka, Gunma 379-01, Japan

<sup>d</sup>Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466, Japan

#### ABSTRACT

The effect of stress during annealing induced by  $Si_3N_4$  films on boron diffusion in float zone-silicon has been studied and a correlation between vacancy concentration and compressive strain in the substrate has been clarified. From the results of  $Si_3N_4$  film thickness and annealing temperature dependence on both boron diffusivity and stress in the substrates, boron diffusion was found to be retarded and the substrate was found to have high stress, having elastic compressive strain during annealing under  $Si_3N_4$  films. These results indicate that excess vacancies are generated by elastic compressive strain, causing the retardation of interstitial-mediated diffusion of boron.

#### Introduction

Silicon nitride  $(Si_3N_4)$  films have been used as an oxidation mask and passivation materials in ultra-large-scale integration (ULSI) process technology.  $Si_3N_4$  films deposited on Si have high stress and produce effects on Si substrates such as the generation of dislocations<sup>1</sup> during thermal annealing.

With the shrinkage of device dimensions, precise control of dopant profiles in the substrate becomes more and more important. Therefore, it is very important to study the effects of stress in the films on both the Si substrate surface and on dopant diffusion.

It is known that chemical vapor deposition (CVD) silicon nitride films develop intrinsic stress during deposition and thermal stress during annealing, influencing dopant diffusion. Ahn et al. reported retarded diffusion of P, enhanced diffusion of Sb, and an increase in the shrinkage rate of extrinsic stacking faults in float zone (FZ)-Si under the low-pressure CVD (LPCVD)  $\mathrm{SiN}_x$  films by varying the stress level in the films with different values of x. Osada et al. investigated retarded diffusion of boron in FZ-Si under electron cyclotron resonance (ECR) plasma CVD  $\mathrm{Si}_3\mathrm{N}_4$  films by changing annealing temperature, annealing time, and the film thickness in detail.

These reports suggest that stress of  $\mathrm{Si}_3N_4$  films disturbs the point defect concentration in the silicon substrate during annealing. However, stress of  $\mathrm{Si}_3N_4$  films was measured only after the film deposition. The change of the intrinsic stress of the films and the actual stress during annealing have not been taken into consideration.

In this study, we first investigated the stress of  $\mathrm{Si}_3\mathrm{N}_4$  films deposited by ECR plasma CVD on FZ-Si as a function of the film thickness and the thermal history. Then, the effect of stress induced by  $\mathrm{Si}_3\mathrm{N}_4$  films on boron diffusion in FZ-Si was studied by changing  $\mathrm{Si}_3\mathrm{N}_4$  film thickness and annealing temperature. Correlation between the stress at the surface of the Si substrate and the retardation of boron diffusion has been clarified from these results. Retarded diffusion of boron will be discussed in terms of the excess vacancy generation.

#### Experimental

Substrates used were p-type, 525  $\mu m$  thick (100) FZ-Si with resistivity of 4  $\sim$  6  $\Omega$  cm for the measurement of boron diffusion and the observation of defects at the sur-

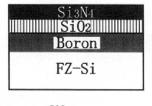

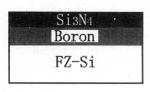

face of the substrates.  $SiO_2$  films with thickness of 50 nm were grown in dry O2 at 1000°C for 60 min on samples. Boron ions were implanted into samples through SiO<sub>2</sub> with a dose of  $3 \times 10^{13}$ /cm<sup>2</sup> at 20 keV. This dose affirmed the socalled intrinsic conditions, in which the carrier concentration is smaller than the intrinsic carrier concentration at annealing temperatures. Samples were annealed in N2 at 900°C for 30 min to remove the ion implantation induced damage. After removing SiO2 films at the back side and at the top side selectively, Si<sub>3</sub>N<sub>4</sub> films were deposited on samples at the top side by ECR plasma CVD at 100°C using SiH<sub>4</sub> and N<sub>2</sub>. ECR plasma CVD allows to the deposition of thin films at lower temperature at low gas pressures in the range of  $10^{-5}$  to  $10^{-3}$  Torr, and does not need any thermal reaction.4 Using this CVD system, high quality Si<sub>3</sub>N<sub>4</sub> films can be obtained. The thickness of Si<sub>3</sub>N<sub>4</sub> films was set to be 50, 100, 160, 430, and 790 nm. The structure of samples is shown in Fig. 1. The areas masked with SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub> films and masked with Si<sub>3</sub>N<sub>4</sub> films were defined as the ON-area and the N-area, respectively.

Substrates used for the measurement of displacement were p-type, 625  $\mu m$  thick (100) FZ-Si with resistivity of 11 to 25  $\Omega$  cm. They were mirror-polished at both sides and cut into a strip with length of 8 cm and width of 1 cm.  $\mathrm{Si}_3\mathrm{N}_4$  films were deposited on the Si substrate by ECR plasma CVD with the same conditions mentioned above. The structure of the samples was the same structure as the N area shown in Fig. 1.

Thermal annealing was performed for all samples in  $N_2$  at temperatures ranging from 900 to 1100°C for 360 min. Boron profiles were measured by secondary ion mass spectroscopy (SIMS ATOMIKA 6500). Stressed-induced

ON-area

N-area

Fig. 1. Cross-sectional view of samples.