# Impact of STI on the Reliability of Narrow-Width pMOSFETs With Advanced ALD N/O Gate Stack

Steve S. Chung, *Fellow, IEEE*, Chang-Hua Yeh, Hsin-Jung Feng, Chao-Sung Lai, Jiuun-Jer Yang, Chi-Chun Chen, Ying Jin, Shih-Chang Chen, *Member, IEEE*, and Mong-Song Liang, *Fellow, IEEE*

Abstract-For the first time, a shallow trench isolation (STI)-induced enhanced degradation in pMOSFETs for ultrathin gate oxide devices has been observed. The  $\mathcal{I}_D$  degradation is enhanced as a reduction in the gate width and the hot carrier (HC) or negative bias temperature instability (NBTI) effect. Extensive studies have been compared for atomic layer deposition (ALD)-grown and plasma-treated oxide pMOSFETs. Different temperature dependences were observed. At room temperature, hole trap is dominant for the device degradation, in which holetrap-induced  $V_T$  is significant, whereas at high temperature under NBTI stress, interface trap becomes more significant, which dominates the device  $I_D$  degradation. In addition, the  $V_T$  rolloff can be modeled as a width narrowing effect specifically for STI. More importantly, the NBTI-induced interface/oxide traps are strongly related to the hydrogen and N<sub>2</sub> content in the gate oxide formation process. The interface trap generation is suppressed efficiently using the ALD-grown gate oxide. These results provide a valuable guideline for the understanding of the HC and NBTI reliabilities in an advanced ALD-grown gate oxide processes/devices.

*Index Terms*—Atomic layer deposition (ALD), gate stack, narrow-width effect, negative bias temperature instability (NBTI), shallow trench isolation (STI).

### I. INTRODUCTION

N PREVIOUS studies [1], for the previous-generation quarter-micrometer CMOS technology, in which the gate oxide is larger than 30 Å, narrow-width shallow trench isolation (STI) exhibits severe degradation after hot-carrier (HC) stress with a reducing gate width. The degradation of pMOSFETs was attributed to an off-state leakage current increase [2] and channel-length shortening [3] because electron trapping exists for a thicker gate oxide. In comparison, for a very thin gate oxide (< 20 Å), the hole trap is the dominant mechanism instead, which leads to an off-state current reduction which is good. However, there are several other issues that become significant with device scaling. According to experimental observations, devices with the STI structure exhibit different degradation mechanisms at various temperatures. Generally, the negative bias temperature instability (NBTI) in pMOSFETs is attributed to the generation of interface traps and oxide trap charges [4].

Manuscript received October 16, 2004; revised July 6, 2005. This work was supported by a Taiwan Semiconductor Manufacturing Company (TSMC) joint development project under Contract 91C209 and in part by the National Science Council under Grant NSC92-2215-E009-058.

S. S. Chung and H.-J. Feng are with the Department of Electronic Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

C.-H. Yeh, C.-S. Lai, and J.-J. Yang are with the Department of Electronic Engineering, Chang-Gung University, Taoyuan 333, Taiwan, R.O.C.

C.-C. Chen, Y. Jin, S.-C. Chen, and M.-S. Liang are with Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TDMR.2006.871415

So far, none has been reported on the enhanced degradation of narrow-width devices in relation to the NBTI effect, especially for a very high-end atomic layer deposition (ALD) gate oxide stack.

In this paper, the aforementioned enhanced degradation at both room temperature (HC effect) and high-temperature stressing (NBTI) has been demonstrated on an advanced ultrathin ALD gate nitride/oxide (N/O) stack. Furthermore, to get more insight into the detailed degradation mechanism, a unique neutralization technique on the oxide charges has been provided, which allows us to identify the generation of interface traps and oxide trap charges. Various experiments have been conducted to confirm that ALD is effective in suppressing the enhanced degradation effect.

## II. DEVICE PREPARATION

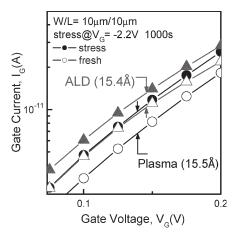

The devices were prepared based on the 90-nm foundry technology. The ALD N/O gate stack was prepared by an advanced remote plasma-enhanced ALD (RPEALD) technique with less H-precursor and  $\rm N_2$  content [5]. The control sample with a heavily plasma-nitrided oxide served as a reference. The ALD and plasma samples have an equivalent oxide thickness (EOT) of 15.4 and 15.5 Å, respectively. The devices with a masked gate length of 0.15  $\mu m$  and various gate widths were used for the reliability measurement.

### III. RESULTS AND DISCUSSION

### A. Narrow-Width Effect at Room Temperature

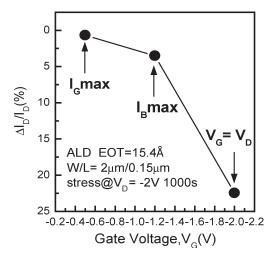

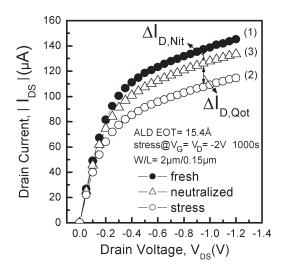

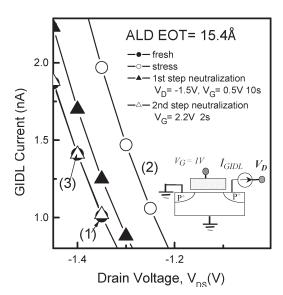

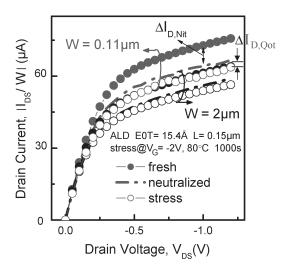

Fig. 1 shows the measured device drain-current degradation after the HC stress for pMOSFETs, including  $I_{G,\text{max}}$ ,  $I_{B,\text{max}}$ , and  $V_G = V_D$  stress conditions, respectively. It is generally known that the largest degradation in the ultrathin gate oxide thickness device occurs at  $V_G = V_D$  stress as expected. Fig. 2 shows one set of measured drain-current at  $V_G = -2$  V for a device with a width  $W=2~\mu\mathrm{m}$  before and after  $V_G=$  $V_D = -2$  V stresses. The fresh device curve is represented by curve (1), whereas a decrease of the current is represented by curve (2) for the device after the stress. The decrease of the drain-current for devices after the stress can be regarded as an increase of the threshold voltage with the generation of interface trap  $N_{\rm it}$  and hole trap  $Q_{\rm ot}$ . The steps in Fig. 3 will help us clarify the generation of either  $N_{\rm it}$  or  $Q_{\rm ot}$ . First, for a fresh device, the drain-current at  $V_G = -2$  V (curve (1) in Fig. 2) and the gate-induced drain leakage (GIDL) current (curve (1)

Fig. 1. Drain–current degradation of the thin oxide ALD device under  $I_{G,\max}$ ,  $I_{B,\max}$ , and  $V_G=V_D$  stresses, respectively.

Fig. 2. Drain–current at  $V_G=-2$  V for the device before stress [curve (1)], after stress [curve (2)], and after neutralization is completed [curve (3)]. The stress condition is given at  $V_G=V_D=-2$  V. Note that the  $\Delta I_D$  caused by  $Q_{\rm ot}$  is larger than that due to  $N_{\rm it}$ .

in Fig. 3) are measured. Then, both currents are measured after the device was stressed for 1000 s under  $V_G = V_D = -2$  V.

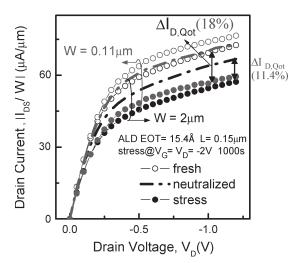

Here, we see a clear shift of the GIDL curve to the right, i.e., curve (2). This shift corresponds to a positive threshold voltage shift  $V_T$ , caused by  $Q_{ot}$ , which is an indication of the positive oxide trap. Consequently, a neutralization process is performed by injecting electrons from the substrate into the gate oxide as shown in two steps [6] and with bias conditions given in the figure to fill those positive traps. Here, we see that a shift of the GIDL current, curve (2), will be moved back to curve (3) and then aligned with the fresh one, curve (1). In Fig. 2, the difference of  $I_D$  between curves (1) and (3) shows the effect of the generated  $N_{\rm it}$ , whereas the difference between curves (2) and (3) gives the effect of the generated  $Q_{ot}$ . From the aforementioned GIDL measurement technique, we can accurately separate the contribution of the interface trap and oxide trap to the drain-current degradations. In a similar manner, we can obtain the same set of curves for narrower width devices, and their comparison with a wide device is given in Fig. 4. In Fig. 3, the

Fig. 3. GIDL currents for the fresh, stressed, and after neutralized. A two-step neutralization is achieved by hot-electron injection to eliminate hole traps.

Fig. 4. Comparison of the measured drain–currents for devices with W=0.11 and 2  $\mu$ m. Note that the generated  $Q_{\rm ot}$  is enhanced for narrow-width devices.

contribution of oxide traps  $Q_{\rm ot}$  to the drain–current degradation  $\Delta I_{D,Q_{\rm ot}}$  is much larger when compared with that contributed from the generation of interface traps  $\Delta I_{D,N_{\rm it}}$ . These results show that the HC degradation depends mostly on the oxide traps, whereas it depends weakly on the generated interface traps with reducing gate width. It is believed that there are only few oxide traps in the ultrathin gate oxide device. Consequently, a much larger generated  $Q_{\rm ot}$  found here should mainly depend on the high nitride density in the gate oxide. Obviously, we can see an enhancement of the  $Q_{\rm ot}$  with reducing channel width, i.e., a device with  $W=0.11~\mu{\rm m}$  has a larger shift (18%) of  $I_{D,Q_{\rm ot}}$  as compared with that with  $W=2~\mu{\rm m}$  (11.4%).

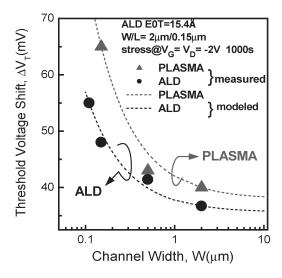

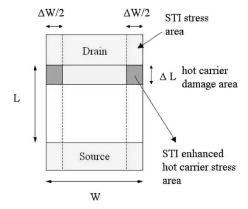

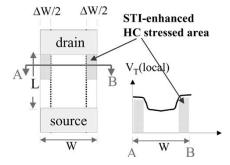

To further study the variation of the threshold voltage with the device gate width, we plotted  $\Delta V_T$  as a function of the channel width (solid circles) in Fig. 5, from which we can see a large enhancement of the narrow-width effect. This is attributed to the STI mechanical stress as reported in [3]. We know that the STI-enhanced HC stress degradation area is

Fig. 5. Calculated threshold voltage shift as a function of width, where the comparison between two different gate oxide processes is also shown.

Fig. 6. Model to show the STI damage area, which can be used to predict the  $V_T$  shift for devices over a wide range of gate widths.

confined in the edge region of the STI such that the STI edge ratio (i.e., the ratio of the edge region to the total gate width) of a narrower width device is larger. In other words, the threshold voltage shift at the STI edge as caused by the quality of the STI or the mechanical stress is believed to be much larger than that at the channel center, as shown in Fig. 6. Therefore, HC stress degradation is enhanced for a reduction of the channel width and hence induces a larger threshold voltage shift.

To predict the STI effect for the different channel-width devices, from more than two sets of measured  $V_T$  and calculated  $V_T$  (solid symbols in Fig. 5) for different widths and from the following equation, we can calculate the  $V_T$  at another gate width. Here, the total variation of the threshold is given by

$$\{\Delta V_{\rm te} \times \Delta W + \Delta V_{\rm tc} \times (W - \Delta W)\} \times \frac{\left(\frac{\Delta L}{L}\right)}{W} = \Delta V_T \tag{1}$$

where

$\Delta V_{\rm te}$  threshold voltage shift in the STI edge;

$\Delta V_{\rm tc}$  threshold voltage shift in the channel center;

$\Delta V_T$  total threshold voltage shift in the whole channel;

$\Delta L$  length of the HC damage area;

$\Delta W$  STI edge width;

L, W device channel length and width.

Fig. 7. Measured gated-diode currents for two different gate widths, where the first peak shift in the gated-diode currents shows the generation of more oxide traps for a narrow-width device.

In the preceding equation, the total threshold voltage shift  $\Delta V_T$  is a combination of  $\Delta V_{\rm tc}$  from the channel center region and  $\Delta V_{\rm te}$  from the gate edge region. Assume  $\Delta L$  and  $\Delta W$  are the same for two different gate-width devices, and from two known values of  $\Delta V_T$  measured at two different gate widths, we may calculate  $\Delta V_{\rm te}$  and  $\Delta V_{\rm tc}$  for any gate width according to (1) such that the total  $\Delta V_T$  can be calculated.

The aforementioned method has an advantage of predicting the degradation  $V_T$  for devices over a wide range of gate widths. To further identify whether this  $V_T$  is caused by the STI effect, we measured the gated-diode currents [7] for two different gate-width devices as shown in Fig. 7. The first peak shift to the left is a result of width reduction because the first peak in the gated-diode measurement is an indication of the generated  $Q_{ot}$ , which causes the threshold voltage shift. As commonly known, the increase of the peak currents (the difference between the fresh and stressed ones, e.g., the peaks at  $V_G = 1.7 \text{ V}$ ) implies the generation of  $N_{\rm it}$  after the HC stress. According to the results of the gated-diode measurement in this figure, obviously, the increment of the gated-diode current is larger for narrowgate-width devices. This further shows that not only  $Q_{\mathrm{ot}}$  was generated but also  $N_{\rm it}$  was increased as a result of width reduction. Therefore, the STI-enhanced degradation in narrowwidth devices can be further justified via this gated-diode measurement.

To show a higher gate oxide quality of ALD, the result for the control sample (plasma-treated device) is also shown for comparison in Fig. 5. Note that the  $V_T$  rolloff is much worse for the plasma-treated sample. It is commonly believed to be due to a much higher density of the nitrogen in the gate oxide, which induces much larger degradation of oxide traps after the HC stress.

# B. Observation of Narrow-Width-Dependent NBTI Effect

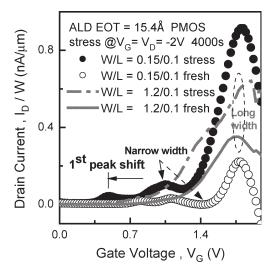

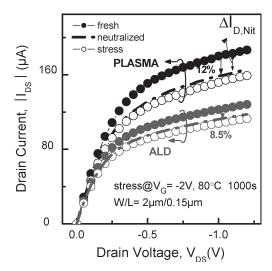

To investigate the width dependence of the NBTI effect, Fig. 8 shows the measured drain-currents for two different gate-width devices, where the measurement step is similar to

Fig. 8. NBTI measurement. The drain–current for the device with W=0.11 and  $2~\mu \rm m$  before stress, after stress, and after neutralization are completed. Note that the  $\Delta I_D$  caused by  $N_{\rm it}$  is dominant.

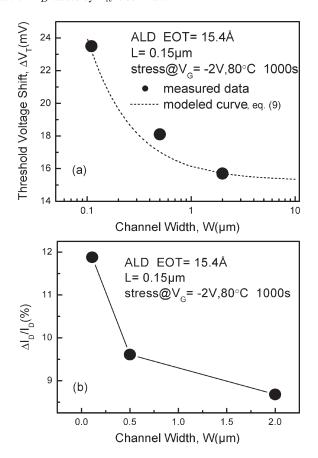

Fig. 9. (a) Threshold voltage shift caused by the NBTI-induced interface traps. (b)  $I_D$  degradation caused by the NBTI-induced interface traps.

that given in Fig. 2. As a result of the recovery of  $V_T$  after turning off the NBTI stress, it was found by comparing the data with the dashed lines and the open circles that  $Q_{\rm ot}$  becomes smaller. Therefore,  $N_{\rm it}$  will become the dominant factor of the drain–current degradation as well as the  $V_T$  shift. Here, the drain–current degradation  $\Delta I_{D,N_{\rm it}}$  becomes much larger from the comparison of the dashed lines and solid circles.  $Q_{\rm ot}$  is nearly negligible here. It is attributed to the near interface oxide

Fig. 10. Drain-current before and after NBTI stress and the comparison for two different gate oxide processes. ALD has much better reliability.

Fig. 11. Illustration of the width narrowing model, in which the shaded area is still OFF when the channel begins to conduct.

traps, which are recovered in a very thin gate oxide. Therefore, we plot in Fig. 9(a) and (b) the enhancement of the  $V_T$  rolloff and  $I_D$  due to the generated  $N_{\rm it}$  only. In other words, the observed  $Q_{\rm ot}$  after NBTI becomes weaker compared with the generated  $N_{\rm it}$  at an elevated temperature, and the interface traps become the dominant mechanism for the  $I_D$  degradation. The narrow-width-dependent NBTI degradations for two different gate oxide processes are shown in Fig. 10.

### C. Further Insight of the Trap Generation and the Model

To reasonably explain the observed enhancement effect caused by the STI, for the first time, a model called width narrowing, which is different from that in [3], is proposed in Fig. 11. In a comparison between a wide- and a narrow-width device, after the HC stress, the STI corner exhibits an area where the channel beneath this region has a larger local threshold voltage due to the positive hole trap  $(Q_{\rm ot})$ -induced damage, in which a larger local threshold voltage is observed at the gate edge. If the local threshold voltage shift is sufficiently high, it results in an effective width,  $W-\Delta W$ , such that  $\Delta V_T$  is enhanced for a narrower width device [Figs. 5 and 9(a)]. Another most important implication from Fig. 8 is showing that the NBTI effect will generate more interface traps  $N_{\rm it}$  for a narrower device as a result of the STI effect. By combining the two preceding factors, the result and physical mechanism

Fig. 12. Comparison of the hydrogen release between ALD and plasma samples. Note that ALD has lower  $H_2$  content and hence a slower  $H_2$  removal rate.

in an ultrathin gate oxide device are quite different from the last-generation quarter-micrometer generation devices in that the degradation comes from the channel shortening [3] or electron traps.

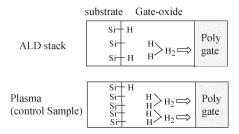

The mechanisms related to an  $N_{\rm it}$  increase and a  $Q_{\rm ot}$  relaxation after NBTI are more interesting and can be drawn as follows

- 1) Both  $N_{\rm it}$  and  $Q_{\rm ot}$  are caused by the hydrogen release from the surface toward the polygate [8], [9]. The generation of  $N_{\rm it}$  is smaller for ALD because ALD has less hydrogen content (see the comparison in Fig. 12) and hence a slower release rate of  $H_2$ .

- 2) The hole trap generation can be measured by the low-voltage stress-induced leakage current (LV-SILC) method [10] with results given in Fig. 13, where we see that ALD exhibits smaller SILC and hence smaller hole traps, smaller SILC, and  $V_T$  (Fig. 5).

- 3) Resulting from the recovery of  $V_T$  or  $Q_{\rm ot}$  (Fig. 10, especially under NBTI), the  $N_{\rm it}$  in the plasma sample is aggravated due to a heavier  $N_2$  content at the interface as hole traps are moved back to the substrate.

We therefore have the following conclusions.

- 1) NBTI and HCI device degradations are enhanced with reducing gate width, which show the STI effect.

- 2) Under NBTI stress, ALD exhibits much less  $N_{\rm it}$  generation and hence much better reliability compared with plasma film.

- 3) Gate oxide formation process with ALD is proved to be more reliable than that of the plasma film in terms of the HC stress effect (at room temperature) and NBTI reliabilities (at high temperature).

## IV. CONCLUSION

The origins of enhanced drain—current degradation and its dependence on the narrow-width effect in pMOSFETs have been extensively studied. New results on the HC- and NBTI-stress-induced device degradations in scaled STI pMOSFETs have been reported. The separation of the degradation type, including interface trap and oxide trap via a so-called neutralization step and GIDL measurement, is proposed to verify the generated oxide trap and interface trap.

For the evaluation of the HC and NBTI reliabilities, different temperature dependences are observed. At room temperature, from the HC test, the hole trap is dominant for the device  $V_T$  shift, whereas the interface trap is more significant and

Fig. 13. LV-SILC measurement at low  $V_G$ , which shows that much more  $N_{\mathrm{it}}$ 's are generated near the conduction band for plasma-treated sample.

responsible for the  $I_D$  degradation after NBTI stress at high temperature. Moreover, the  $V_T$  rolloff can be well explained by a width narrowing effect physically, and a quantitative model is further proposed. Results have clearly shown that the generated interface/oxide traps are strongly related to the hydrogen and  $N_2$  content in the gate oxide formation process. Therefore, the results provide us a useful guideline for understanding the HC-and NBTI-related reliabilities in an advanced gate N/O stack 60 nm and beyond CMOS processes/devices.

### REFERENCES

- M. Nishigohri, K. Ishimaru, M. Takahashi, Kayama, F. Matsuoka, and M. Kinugawa, "Anomalous hot-carrier induced degradation in very narrow channel nMOSFET's with STI structure," in *IEDM Tech. Dig.*, 1996, pp. 881–884.

- [2] L. P. Chiang, L. Y. Huang, N. K. Zous, and T. Wang, "Stress induced subthreshold current hump in short gate-length pMOSFET's with shallow trench isolation," in *Extended Abstract SSDM*, 1999, pp. 16–17.

- [3] S. S. Chung, S. J. Chen, W. J. Yang, and J. J. Yang, "A new physical and quantitative width dependent hot carrier model for shallow-trench-isolated CMOS devices," in *Proc. IRPS*, Orlando, FL, 2001, pp. 419–424.

- [4] S. S. Chung, D. K. Lo, J. J. Yang, and T. C. Lin, "Localization of NBTI-induced oxide damage in direct tunneling regime gate oxide pMOSFET using a novel low gate- leakage gated-diode (L<sup>2</sup> GD) method," in *IEDM Tech. Dig.*, 2002, pp. 513–516.

- [5] C. C. Chen, T. L. Lee, D. Y. Lee, V. S. Chang, H. C. Lin, S. C. Chen, T. Y. Huang, and M. S. Liang, "Remote plasma-enhanced atomic layer deposition (RPEALD) nitride/oxide gate dielectric for sub-65 nm low standby power CMOS application," in *VLSI Symp. Tech. Dig.*, 2003, pp. 141–142.

- [6] C. Y. Lu and K. S. Chang-Liao, "Minimized constrains for lateral profiling of hot-carrier-induced oxide charges and interface traps in MOSFETs," in *Proc. VLSI-TSA*, 2003, pp. 49–51.

- [7] S.-J. Chen, T.-C. Lin, D.-K. Lo, J.-J. Yang, S. S. Chung, T.-Y. Kao, R.-Y. Shiue, C.-J. Wang, and Y.-K. Peng, "An improved interface characterization technique for a full-range profiling of oxide damage in ultra-thin gate oxide CMOS devices," in *Proc. IRPS*, Dallas, TX, Mar. 30–Apr. 4, 2003, pp. 203–207.

- [8] S. Mahapatra, P. B. Kumar, and M. A. Alam, "A new observation of enhanced bias temperature instability in thin gate oxide p-MOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 337–340.

- [9] S. Tsujikawa, K. Watanabe, R. Tsuchiya, K. Ohnishi, and J. Yugami, "Experimental evidence for the generation of bulk traps by negative bias temperature stress and their impact on the integrity of direct-tunneling gate dielectrics," in VLSI Symp. Tech. Dig., 2003, pp. 139–140.

- gate dielectrics," in *VLSI Symp. Tech. Dig.*, 2003, pp. 139–140.

[10] P. E. Nicollian, M. Rodder, D. T. Grider, P. Chen, R. M. Wallace, and S. V. Hattangady, "Low voltage stress-induced-leakage-current in ultrathin gate oxides," in *Proc. IRPS*, 1999, pp. 400–404.

**Steve S. Chung** (SM'83–M'85–SM'95–F'06) received the Ph.D. degree in electrical engineering from the University of Illinois at Urbana-Champaign in 1985. His Ph.D. thesis advisor was the world-famous scholar and CMOS coinventor Prof. C. T. Sah.

In 2001, he was a Research Visiting Scholar at Stanford University, Stanford, CA. Between 2004 and 2005, he was the first Department Head of the EECS Honors Program to promote a new undergraduate program for academic excellence at the

National Chiao-Tung University (NCTU), Hsinchu, Taiwan, R.O.C., where he has served since 1987. He is currently a Chair Professor at NCTU and also a UMC Research Chair Professor. He was also a Consultant to Taiwan Semiconductor Manufacturing Company (TSMC) and UMC on developing CMOS and Flash memory technologies. He has published more than 140 journal and conference papers, 1 textbook, and holds more than 18 patents in CMOS and Flash memory. His current research areas include CMOS device technology, Flash memory technology, reliability characterization and modeling, etc.

Dr. Chung is an elected AdCom Member, a Distinguished Lecturer, a Regions/Chapters Vice-Chair of the EDS, and the Editor of IEEE ELECTRON DEVICE LETTERS (EDL). He has served on the committees of premiere conferences, e.g., VLSI Technology, IEDM, IRPS, IPFA, etc. For the first time in Taiwan history, at the 50th anniversary of the IEEE, the ED Taipei chapter was awarded the 2002 EDS Chapter of the Year Award under his leadership as the Chapter Chair. He was awarded the Outstanding Research Award for excellence in research three times, as well as ranking the Top-PI in 2003, from the National Science Council, Taiwan, R.O.C. He was also granted both the Distinguished EE Professor and Engineering Professor by the Engineering Societies of Taiwan.

Chang-Hua Yeh received the B.S. and M.S. degrees in electronic engineering from the Chung-Gung University, Taoyuan, Taiwan, R.O.C., in 2002 and 2004, respectively. His thesis was codirected by Prof. S. S. Chung of the National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

He is currently with the Research and Development Division, Nanya Technology Corporation, Taoyuan, Taiwan, R.O.C., focusing on the development of DRAM. His interests are in the areas of MOSFET device reliability and characterization.

**Hsin-Jung Feng** received the B.Sc. degree in electrical engineering from the National Central University, Taoyuan, Taiwan, R.O.C., in 2001 and the M.Sc. degree in electronic engineering from the National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 2004. His thesis was on the development of a charge pumping technique for ultrathin gate oxide CMOS devices.

Chao-Sung Lai was born in I-Lan, Taiwan, R.O.C., on May 20, 1969. He received the B.Sc. and Ph.D. degrees from the National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 1991 and 1996, respectively.

In 1996, he joined the National Nano Device Laboratory, Hsinchu, Taiwan, R.O.C., where he was engaged in the research of silicon-on-insulator devices. In 1997, he was an Assistant Professor at the Chang Gung University and Tao-Yuan, Taiwan, R.O.C., where he was engaged in the research of the

characterization and reliability of deep submicron MOSFETs, nitrided thin gate oxides, shallow trench isolation, and the modeling of the dielectrics' reliability. Since 1997, he has been a Consultant for the 0.18- $\mu$ m Logic Team at the Nanya Technology Corporation, Taoyuan, Taiwan, R.O.C. In 2001, he was an Associate Professor. In 2001, he was a Visiting Scholar in Prof. C. Hu's group at the University of California-Berkeley.

Dr. Lai won the Lam Award in 1997.

**Jiuun-Jer Yang** received the B.Sc. degree from the National Cheng-Kung University, Tainan, Taiwan, R.O.C., in 1989, and the M.Sc. and Ph.D. degree from the National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 1991 and 1995, respectively, all in electrical engineering.

From 1995 to 1997, he was with the Technology Development Center, Winbond Electronics Corporation, Hsinchu, Taiwan, R.O.C., working on technology computer-aided design, device design, and reliability engineering. From 1997 to 2000, he was

with the Worldwide Semiconductor Manufacturing Corporation, Hsinchu, Taiwan, R.O.C., where he worked first at the Technology Development Center, and then switched to the Fab working on device characterization, yield enhancement, and process integration. From 2000 to 2003, he was an Assistant Professor at the Department of Electronic Engineering and Institute of Semiconductor Technology, Chang-Gung University, Taiwan, R.O.C. He is currently with the Semiconductor Manufacturing International Corporation, Beijing, China, in charge of northern-site quality and reliability engineering division. His research interests include device integration, process/device modeling and simulation, and reliability study of advanced technologies.

**Chi-Chun Chen** received the B.S., M.S., and Ph.D. degrees in electronics engineering from the National Chiao-Tung University (NCTU), Taiwan, R.O.C., in 1996, 1997, and 2000, respectively.

At NCTU, his research was focused on the process-related oxide reliability of ultrathin gate oxides. In 2000, he joined the Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan, R.O.C., where he was responsible for the HDPCVD process for STI and ILD gapfill, thin gate oxide process, and Cu CMP process for 0.13-μm logic

process development in the 300-mm pilot line. From 2001 to 2004, he worked on the research and development of advanced gate stack process. He is currently the Project Manager of the Advanced Module Technology Division of the Research and Development organization. He is responsible for gate stack module development, including wet clean and surface preparation, thermal process, oxynitride/poly gate stack process, and related metrology technologies. He has authored or coauthored about 40 technical papers in the advanced semiconductor process area, especially in gate dielectrics-related process. He also holds more than ten patents in semiconductor manufacturing technologies.

**Ying Jin** was born in Beijing, China. He received the Ph.D. degree in semiconductor physics from Peking University, Beijing, China.

He was a Research Fellow at the City University of Hong Kong, where he was responsible for the diffusion module of Research and Development at the Chartered Semiconductor Manufacturing Ltd., Singapore. In 2002, he joined the Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan, R.O.C., where he is currently the Project Manager at the Advanced Module Technology Di-

vision, responsible for advanced gate stack process, such as high-k/metal gate, for 45-nm and beyond devices.

**Shih-Chang Chen** (M'00) was born in Taiwan, R.O.C. He received the B.S., M.S., and Ph.D. degrees in electrical and electronics engineering from Hosei University, Tokyo, Japan.

In 1986, he joined the VLSI Research and Development Center, Oki Electric Industry Company, Ltd., Tokyo, Japan, where he worked on gate electrode and interconnect process technologies development, employing refractory metals and their silicides/nitrides for very large scale integrations. He was also in charge of the process development of high-k capaci-

tor and electrode films for high-density DRAMs. Afterward, he was responsible for the process development of advanced interconnects employing copper and low-k materials until January 2000. In February 2000, he joined the Worldwide Semiconductor Manufacturing Corporation, Hsinchu, Taiwan, R.O.C., where he was responsible for all advanced process technology developments at the Advanced Process Technology Division, Technology Development Center. In July 2000, he joined the Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan, R.O.C., where he is currently the Deputy Director and is responsible for the advanced front-end process at the Advanced Module Technology Division. His research interests include advanced front-end-of-the-line process development, including ultrathin gate oxide or high-k gate stacks, strained Si process, and ultrashallow junction formation for 65-nm and beyond devices.

Mong-Song Liang (F'06) received the B.S. and M.S. degrees from the National Cheng-Kung University, Taiwan, R.O.C., in 1975 and 1977, respectively, and the Ph.D. degree from the University of California (UC), Berkeley, in 1983, all in electrical engineering and computer sciences.

At UC Berkeley, his research was on the scaling of ultrathin gate dielectrics and on device reliability physics. In 1983, he joined the Advanced Micro Devices, Sunnyvale, CA, where he worked on nonvolatile memory technologies (EEPROM and

EPROM). From 1988 to 1992, he was with the Mosel Electronics Corporation, Sunnyvale, CA, where he worked on SRAM technology development. In 1992, he jointed the Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan, R.O.C. He worked on DRAM and embedded memory technology (Emb-DRAM, Emb-SRAM, and Emb-Flash) development. He was the Director of the Memory Division of the Research and Development organization until 1998. He is currently the Director of the Advanced Module Technology Division of the Research and Development organization. He is responsible for all advanced modules development, including etch, thin film, diffusion, CMP, and Cu/low-k interconnect.