# An Assessment of Single-Electron Effects in Multiple-Gate SOI MOSFETs With 1.6-nm Gate Oxide Near Room Temperature

Wei Lee, Student Member, IEEE, Pin Su, Member, IEEE, Hou-Yu Chen, Chang-Yun Chang, Ke-Wei Su, Sally Liu, and Fu-Liang Yang

Abstract—This letter provides an assessment of single-electron effects in ultrashort multiple-gate silicon-on-insulator (SOI) MOS-FETs with 1.6-nm gate oxide. Coulomb blockade oscillations have been observed at room temperature for gate bias as low as 0.2 V. The charging energy, which is about 17 meV for devices with 30-nm gate length, may be modulated by the gate geometry. The multiple-gate SOI MOSFET, with its main advantage in the suppression of short-channel effects for CMOS scaling, presents a very promising scheme to build room-temperature single-electron transistors with standard silicon nanoelectronics process.

Index Terms—CMOS, coulomb blockade oscillation, multiple gate, silicon-on-insulator (SOI), single-electron effect, single-electron transistor.

## I. INTRODUCTION

O ENABLE low-power electronics in the next generation, building single electron transistors (SETs) with at 1.1. building single electron transistors (SETs) with standard silicon nanoelectronics process is a very attractive approach [1], [2], [6]. Especially, the SETs compatible with existing CMOS device architectures are potentially important for high-density memory cells. Table I lists several studies of silicon-based SETs with MOS structures, and reveals that downsizing the SET is essential to achieving the Coulomb blockade oscillation (CBO). The main challenges are the control of tunnel barriers [3], [4] and the suppression of short-channel effects [1]. Boeuf et al. [6] has demonstrated controlled single-electron effects using nonoverlapped extensions acting as tunnel barriers. M. Peters et al. [1] showed significant CBO using multiple-gate silicon-oninsulator (SOI) MOSFETs to overcome the short-channel effect. Although both studies represent attractive schemes to build SETs on large-scale wafers, the operating temperature is low (less than about 5 K).

To allow high-temperature operation, the size of the SET needs to be further reduced [1]–[7], [12]. The suppression of short-channel effects, therefore, is especially critical to enabling single-electron tunneling at elevated temperature in the scaled MOSFET. In this letter, we control the short-channel effect for

Manuscript received December 2, 2005. This work was supported in part by the National Science Council of Taiwan, R.O.C., under Contract NSC94-2215-E-009-049. The review of this letter was arranged by Editor B. Yu.

W. Lee and P. Su are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail:pinsu@mail.nctu.edu.tw)

H.-Y. Chen, C.-Y. Chang, K.-W. Su, S. Liu, and F.-L. Yang are with the Taiwan Semiconductor Manufacturing Company, Hsinchu 300, Taiwan, R.O.C. Digital Object Identifier 10.1109/LED.2006.870240

TABLE I SEVERAL STUDIES ON SINGLE-ELECTRON EFFECTS IN MOS STRUCTURES

|                                | this work | [1]     | [2]    | [3]    | [4]     | [5]     | [6]     | [7]      |

|--------------------------------|-----------|---------|--------|--------|---------|---------|---------|----------|

| type                           | N-Fin     | N-Fin   | N-SET  | SET    | N-SEQDT | Acc-SET | NP-Bulk | N-bulk   |

| T <sub>ox</sub> (nm)           | 1.6       | 25      | 6      | 30     | 25      | 10      | 2~3     | 2.4~3.8  |

| L (nm)                         | 30        | 200     | 40     | 50~200 | dot     | ~100    | 16~27   | 50~100   |

| W (nm)                         | 25        | 100~500 | 15     | 20     | 16      | >50     | 280     | 1000~400 |

| H (nm)                         | 40        | 100     | 25     | 30     | 32      | 10      |         |          |

| C <sub>g</sub> (aF)            | 20~30     | 5.2     | 2      | 3~5    | 1.7     | 27      | 66      | 46~80    |

| $\Delta V_{g}\left( mV\right)$ | 17        | ~31     | 400    | 50~30  | 1400    | 6       | 9~6     | 3.5~2    |

| Temp. (K)                      | <300      | 1.8     | <250   | 300    | 300     | <10     | <5      | <5       |

| lithography                    | optical   | E-beam  | E-beam | E-beam | E-beam  | E-beam  | optical |          |

devices with gate length down to 30 nm using thin oxide and multiple-gate SOI structures [9], [10]. Our device structure features nonoverlapped gate to source and drain. We conduct an assessment of single-electron effects in our multiple-gate SOI MOSFETs with 1.6-nm gate oxide near room temperature.

# II. DEVICES

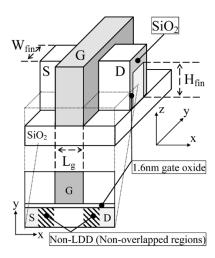

Our transistors, as shown in Fig. 1, were fabricated on p-type SIMOX SOI wafers using optical lithography as described in [10]. The Si-body thickness,  $H_{\rm fin}$ , was thinned down to about 40 nm by thermal oxidation. The fin-width,  $W_{\rm fin}$ , was defined by wet-etching and is about 25 nm. After  $W_{\rm fin}$  was developed, the 1.6-nm gate oxide was thermally grown. The ultra-thin gate oxide contributes to not only the suppression of short-channel effects, but also the gate-dot coupling strength of the SET [2].

The gate length  $L_g$  was defined by *in situ* heavily doped  $\rm n^+$  poly-silicon gate and ranges from 30 to 40 nm. Without the light doping drain (LDD) implantation, the composite spacer of silicon oxide and nitride was deposited and anisotropically etched. The undoped regions under the spacers separate the inversed carriers from source/drain and act as electrostatic tunnel barriers as depicted in Fig. 1. Finally, heavily-doped  $\rm n^+$  source/drain was made. It is worth noting that the parasitic source/drain resistance, which may determine the tunnel barrier [5], depends on  $H_{\rm fin}$  and  $W_{\rm fin}$  in this multiple-gate SOI structure.

# III. RESULTS AND DISCUSSIONS

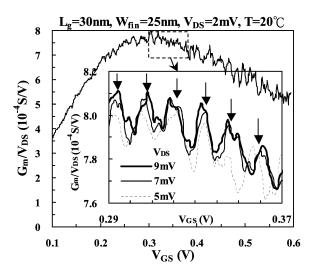

Fig. 2 shows the  $G_m$ – $V_G$  characteristics measured by HP4156B in a low-noise probe station at room temperature ( $T=20^{\circ}\mathrm{C}$ ) for the device with  $L_g=30$  nm and  $W_{\mathrm{fin}}=25$  nm. Periodic oscillations in  $G_m$ , an indication of the CBO [2], [4], [8], [13], can be seen starting from  $V_G\sim0.2~\mathrm{V}$ .

Fig. 1. Multiple-gate FinFET SOI structure investigated in this work and its cross-sectional view along the channel direction showing the nonoverlapped gate to source/drain regions.

Fig. 2. Periodic oscillations occur in  $G_m/V_{DS}$  vs.  $V_{GS}$  for the device with  $L_g=30$  nm and  $W_{\rm fin}=25$  nm at T=20 °C.  $G_m$  is extracted by  $dI_D/dV_G$  and shows a period of 17 mV.

For an SET, the ability to produce CBO at low gate bias is important to low-power applications [2]. We have also noted that the periodic oscillations can be reproduced from sample to sample, and the peaks of each period for the same device may be repeated at the same gate bias. It can be seen from the inset of Fig. 2 that the oscillating period is about 17 mV. For devices with large dimensions under the same measurement system, nevertheless, only the thermal noise can be seen. In addition, we have confirmed that the effect of source accuracy [16] is not responsible for the observed periodic oscillation.

To further analyze the periodic oscillation in  $G_m$ , both the discrete fast Fourier transform (FFT) [11] and the histogram of the directly counted peak-to-peak spacing  $(\Delta V_G)$  [5], [6] in the  $G_m$ - $V_G$  characteristics can be applied. The power spectrum density of FFT, shown in Fig. 3(a), may represent the intensity of the corresponding periodic signal plus the period counts of  $\Delta V_G$  [Fig. 3(b)]. It can be confirmed from Fig. 3 that the observed conductance oscillation in Fig. 2 indeed has a period of 17 mV.

Fig. 3. Both (a) the fast Fourier transform (FFT) and (b) the histogram of the directly counted peak-to-peak spacing  $(\Delta V_G)$  confirm that the period in Fig. 2 is 17 mV.

The period of conductance oscillation,  $\Delta V_G$ , represents the charging energy and is related to the gate capacitance by  $e/C_q$ [12], [20]. From  $e/C_g=17~\mathrm{mV}$  and the gate capacitance per unit area  $(C_g/A_{\text{eff}} \sim 1.3 \times 10^{-6} \text{ F/cm}^2)$ , we may deduce an effective area of the dot,  $A_{\rm eff} \sim 7.1 \times 10^{-12} \ {\rm cm^2},$  which is about a factor of three smaller than the total gate area of our FinFET device  $(2H_{\rm fin}L_g=24\times 10^{-12}~{\rm cm}^2)$ . Note that similar discrepancy has also been observed in [6]. Besides uncertainties of process control in very small geometries, the discrepancy between the deduced effective area  $(A_{\text{eff}})$  and the total gate area of our device  $(2H_{\rm fin}L_g)$  may stem mainly from the junction capacitance [14], [15]. In other words, the quantum dot in our device may no longer be considered as a disk-like island but rather a three-dimensional box. In addition, the shape of this three-dimensional box may be deformed by  $V_G$  because the tunnel barriers may be electrostatically modulated by  $V_G$ . Therefore, the oscillating period,  $\Delta V_G$ , is a distribution instead of a fixed value. As shown in Fig. 3(b), our measured  $\Delta V_G$ can be described by Gaussian distribution [6], [17]–[19] with  $\langle \Delta V_G \rangle \sim 17$  mV and sd $\sim 3.5$  mV ( $\langle \Delta V_G \rangle$ : mean, sd: standard deviation). Moreover, the normalized width of the distribution,  $\operatorname{sd}/\langle \Delta V_G \rangle$ , is about 0.2. Similar results have also been obtained in [6] and [19].

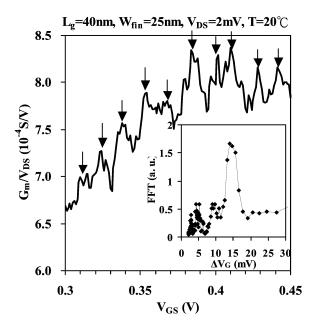

Fig. 4 shows the  $G_m$ – $V_G$  characteristics for the device with  $L_g=40$  nm and  $W_{\rm fin}=25$  nm at  $T=20\,^{\circ}{\rm C}$ . The phenomenon of  $G_m$  oscillation can still be seen. Moreover, we have noted that the oscillating period,  $\Delta V_G$ , is about 15 mV, as shown in the inset of Fig. 4, for all the devices with this size. Compared with the 17-mV period for  $L_g=30$  nm (Fig. 3), the decreased  $\Delta V_G$  for  $L_g=40$  nm may be attributed to the increased  $C_g$ . This geometrical dependence of charging energy indicates that the observed single-electron effect is controlled by the gate geometry rather than the disordered potential landscape demonstrated in the multiple-gate SOI structures of [1].

# IV. CONCLUSION

We have conducted an assessment of single-electron effects in ultrashort multiple-gate SOI MOSFETs with 1.6-nm gate

Fig. 4. Periodic oscillations occur in  $G_m/V_{DS}$  versus  $V_{\rm GS}$  for the device with  $L_g=40\,$  nm and  $W_{\rm fin}=25\,$  nm at  $T=20\,$  °C. Smaller peak-to-peak spacing ( $\Delta V_G=15\,$  mV) from the FFT can be seen.

oxide. Coulomb blockade oscillations have been observed at room temperature for gate bias as low as 0.2 V. The charging energy may be modulated by the gate length of the MOSFET. The multiple-gate SOI structure, with its main advantage in the suppression of short-channel effects for CMOS scaling, presents a very promising scheme to build room-temperature single-electron transistors with standard silicon nanoelectronics process.

# ACKNOWLEDGMENT

The authors are grateful to anonymous referees for critical reading of the manuscript and valuable feedback.

### REFERENCES

- M. G. Peters, S. G. de Hartog, J. I. Dijkhuis, O. J. A. Buyk, and L. W. Molenkamp, "Single electron tunneling and suppression of short-channel effects in submicron silicon transistors," *J. Appl. Phys.*, vol. 84, no. 9, pp. 5052–5056, Nov. 1998.

- [2] Y.-M. Wan, K.-D. Huang, C.-L. Sung, and S.-F. Hu, "Transport properties of ultra thin oxide gated Si SET near room temperature," in *Proc. 5th IEEE Conf. Nanotechnol.*, Jul. 2005, pp. 750–753.

- [3] Y. Takahashi, H. Namatsu, K. Kurihara, K. Iwadate, M. Nagase, and K. Murase, "Size dependence of the characteristics of Si single-electron transistors on SIMOX substrates," *IEEE Trans. Electron Devices*, vol. 43, no. 8, pp. 1213–1217, Aug. 1996.

- [4] L. Zhuang, L. Guo, and S. Y. Chou, "Silicon single-electron quantum-dot transistor switch operating at room temperature," *Appl. Phys. Lett.*, vol. 72, no. 10, pp. 1205–1207, Mar. 1998.

- [5] X. Jehl, M. Sanquer, G. Bertrand, G. Guégan, S. Deleonibus, and D. Fraboulet, "Silicon single electron transistors with SOI and MOSFET structures: The role of access resistances," *IEEE Trans. Nanotechnol.*, vol. 2, no. 12, pp. 308–313, Dec. 2003.

- [6] F. Boeuf, X. Jehl, M. Sanquer, and T. Skotnicki, "Controlled single-electron effects in nonoverlapped ultra-short silicon field effect transistors," *IEEE Trans. Nanotechnol.*, vol. 2, no. 9, pp. 144–148, Sep. 2003.

- [7] M. Sanquer, M. Specht, L. Ghenim, S. Deleonibus, and G. Guegan, "Coulomb blockade in low-mobility nanometer size Si MOSFETs," *Physi. Rev. B*, vol. 61, no. 11, pp. 7249–7252, Mar. 2000.

- [8] H. Matsuoka, T. Ichiguchi, T. Yoshimura, and E. Takeda, "Coulomb blockade in the inversion layer of a Si metal-oxide-semiconductor fieldeffect transistor with a dual-gate structure," *Appl. Phys. Lett.*, vol. 64, no. 5, pp. 586–588, Jan. 1994.

- [9] Z. Krivokapic, C. Tabery, W. Maszara, Q. Xiang, and M.-R. Lin, "High performance 45 nm CMOS technology with 20 nm multi-gate devices," in *Proc. Int. Conf. Solid State Dev. Mater.*, Sep. 2003, pp. 760–760.

- [10] F.-L. Yang, H.-Y. Chen, F.-C. Chen, Y.-L. Chan, K.-N. Yang, C.-J. Chen, H.-J. Tao, Y.-K. Choi, M.-S. Liang, and C. Hu, "35 nm CMOS FinFETs," in *Symp. on VLSI Tech. Dig.*, 2002, pp. 104–105.

- [11] J. H. P. Scott-Thomas, S. B. Field, M. A. Kastner, H. I. Smith, and D. A. Antoniadis, "Conductance oscillations periodic in the density of a onedimensional electron gas," *Phys. Rev. Lett.*, vol. 62, no. 5, pp. 583–586, Jan. 1989.

- [12] Y. Takahashi, M. Nagase, H. Namatsu, K. Kurihara, K. Iwdate, Y. Nakajima, S. Horiguchi, K. Murase, and M. Tabe, "Conductance oscillations of a Si single electron transistor at room temperature," in *IEDM Tech. Dig.*, 1994, pp. 938–940.

- [13] Y. Omura, K. Kurihara, Y. Takahashi, T. Ishiyama, Y. Nakajima, and K. Izumi, "50-nm channel nMOSFET/SIMOX with ultrathin 2- or 6-nm thick silicon layer and their significant features of operations," *IEEE Electron Device Lett.*, vol. 18, no. 5, pp. 190–196, May 1997.

- [14] S. M. Goodnick and J. Bird, "Quantum-effect and single-electron devices," *IEEE Trans. Nanotechnol.*, vol. 2, no. 12, pp. 368–385, Dec. 2003

- [15] A. A. M. Staring, H. van Houten, C. W. J. Beenakker, and C. T. Foxon, "Coulomb-blockade oscillations in disordered quantum wires," *Phys. Rev. B, Condens. Matter*, vol. 45, no. 16, pp. 9222–9236, Apr. 1992.

- [16] Overcoming the Measurement Challenges of Advanced Semiconductor Technologies—DC, Pluse, and RF-From Modeling to Manufacturing, 1st ed: Keithley, 2005, pp. 102–103.

- [17] F. Simmel, D. Abusch-Magder, D. A. Wharam, M. A. Kastner, and J. P. Kotthaus, "Statistics of the coulomb-blockade peak spacings of a silicon quantum dot," *Phys. Rev. B, Condens. Matter*, vol. 59, no. 16, pp. 10 441–10 444, Apr. 1999.

- [18] R. O. Vallejos, C. H. Lewenkopf, and E. R. Mucciolo, "Coulomb blockade peak spacing fluctuations in deformable quantum dots: A further test of random matrix theory," *Phys. Rev. Lett.*, vol. 81, no. 3, pp. 677–680, Jul. 1998.

- [19] R. Berkovits, "Absence of bimodal peak spacing distribution in the coulomb blockade regime," *Phys.Rev. Lett.*, vol. 81, no. 10, pp. 2128–2131, Sep. 1998.

- [20] K. K. Likharev, "Single-electron devices and their applications," *Proc. IEEE*, vol. 87, no. 4, pp. 606–632, Apr. 1999.