# Characterization of Programmed Charge Lateral Distribution in a Two-Bit Storage Nitride Flash Memory Cell by Using a Charge-Pumping Technique

Shaw-Hung Gu, Tahui Wang, Senior Member, IEEE, Wen-Pin Lu, Wenchi Ting, Yen-Hui Joseph Ku, and Chih-Yuan Lu, Fellow, IEEE

Abstract—In this paper, we use a modified charge pumping technique to characterize the programmed charge lateral distribution in a hot electron program/hot hole erase, two-bit storage nitride Flash memory cell. The stored charge distribution of each bit over the source/drain junctions can be profiled separately. Our result shows that the second programmed bit has a broader stored charge distribution than the first programmed bit. The reason is that a large channel field exists under the first programmed bit during the second bit programming. Such a large field accelerates channel electrons and causes earlier electron injection into the nitride. In addition, we find that programmed charges spread further into the channel as program/erase cycle number increases.

Index Terms—Charge pumping (CP), cycling stress, programmed charge distribution, two-bit storage nitride Flash cell.

### I. INTRODUCTION

TITRIDE-BASED trapping storage Flash memory has received much interest recently for its smaller bit size, simpler manufacturing process, and no drain-induced turnon [1], [2]. In a conventional SONOS cell, programmed charges are stored uniformly in a nitride layer. This SONOS concept has recently evolved into a localized trapping and two-bit storage cell, such as NROM [3] and Nbit [4] technologies. These special-type nitride Flash cells resemble a standard MOS transistor except that the gate oxide is replaced by an oxide-nitride-oxide gate dielectric stack. Two bits operation can be achieved by placing programmed charges in the nitride layer locally above the source or the drain junction by channel hot electron program and band-to-band hot hole erase. A reverse read scheme is employed to maximize the effect of the stored charge on the threshold voltage window [3]. Because of a symmetrical cell structure and a nonconductive storage element, the Nbit technology has been engineered to take advantage of a higher packing density memory array without compromising device endurance, performance and reliability.

In two-bit operation, the control of programmed charge lateral distribution of each bit is a major concern for the scalability

Manuscript received May 4, 2005; revised July 27, 2005. This work was supported by the National Science Center, Taiwan, R.O.C., under Contract NSC 92-2215-E-009-056. The review of this paper was arranged by Editor S. Kimuro.

S.-H. Gu and T. Wang are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. (e-mail: twang@cc.nctu.edu.tw).

W.-P. Lu, W. Ting, Y.-H. J. Ku and C.-Y. Lu are with the Macronix International Company Ltd., Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TED.2005.860632

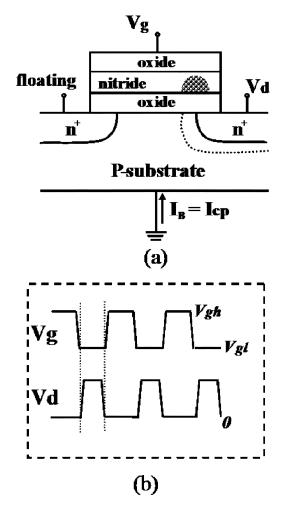

Fig. 1. (a) Schematic diagram of a two-bit storage nitride Flash cell and (b) CP measurement waveform. The dashed line in the substrate represents the depletion region caused by  $V_d$ . The thickness of the ONO gate stack is 9 (top oxide), 6, and 6 nm, respectively.

of this memory cell. The stored electrons at the first bit will affect the threshold voltage of the second bit in reverse read and vice versa. This phenomenon is referred to as the second bit effect [5] and is closely related to programmed charge lateral spread. Furthermore, the lateral spread of stored charges in nitride will result in the degradation of erase capability or erase speed due to a spatial mismatch between stored electrons and injected holes during erase [6]. For these reasons, comprehensive understanding of programmed charge spatial distribution is

of vital importance in the optimization of the cell structure and operation bias.

Attempts have been made in the past to characterize the trapped charge distribution in a NROM cell [7], [8]. Larcher et al. used an inverse modeling approach to extract programmed charge distribution from measured current–voltage (I-V) characteristics [7]. This method, however, suffers from some drawbacks, such as lack of precise information on device doping profile and extensive numerical calculation to reach a consistent solution between stored charge distribution and measurement result.

In this paper, we will use a modified charge-pumping (CP) technique [9] to probe the lateral distribution of programmed charges at the source and drain junctions separately without using computer simulation. The devices and measurement setup throughout this study will be described in Section II. The CP current for single bit storage and two-bit storage will be shown in Section III. Program/erase cycling stress effect on stored charge distribution will be also examined.

#### II. EXPERIMENTAL

The nitride Flash cells used in this paper have a gate length of 0.5  $\mu$ m and a gate width of 1.0  $\mu$ m. The thickness of each ONO layer is 9 nm (top oxide), 6 nm (nitride) and 6 nm (bottom oxide). The cell intrinsic threshold voltage ( $V_t$ ) is about 1.6 V where  $V_t$  is defined as the gate voltage when the drain current is 1  $\mu$ A at a reverse read voltage of 1.6 V. Channel hot electron program and band-to-band hot hole erase accompanied by a reverse read scheme are adopted to achieve two-bit per cell operation.

In CP measurement, the voltage waveforms at gate and drain terminals supplied by a two-channel pulse generator are illustrated in Fig. 1. The employment of a dual-channel pulse generator can circumvent the misalignment of gate and drain signal. The gate pulse has a fixed high level  $(V_{\rm gh})$  and a variable low level  $(V_{\rm gl})$ . The  $V_{\rm gh}$  is sufficiently high  $(V_{\rm gh}=6~{\rm V}$  here) to ensure that the entire channel at program state is inverted.

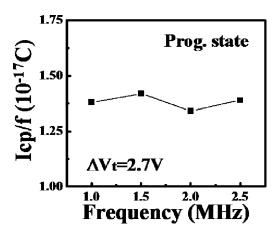

The CP current, named hereafter  $I_{\rm cp}$ , is measured at the substrate. To probe the lateral extent of programmed charge in the drain side (or the source side),  $V_d$  (or  $V_s$ ) is adjusted to modulate the drain (or source) depletion width while  $V_s$  (or  $V_d$ ) is left floating. In this way, there is no channel current and thus no impact ionization induced substrate current in CP measurement. Besides, the  $V_d$  is 180° phase-shifted with respect to  $V_q$  so that the drain signal is applied only during the interface-trap  $(N_{it})$  electron emptying period. Because the length of the channel hot electron injection region (i.e., programmed region) is only about a few nanometers [9],  $I_{\rm cp}$ contributed by interface traps in the programmed region is very low and close to the measurement limit of the current setup. Therefore, a higher frequency of 2.5 MHz with 50% duty cycle and rise/fall times of 15 ns each is selected in CP measurement. To make sure the measured  $I_{\rm CD}$  is still reliable at this frequency, the frequency dependence of normalized CP current at program state is shown in Fig. 2. The constant  $I_{\rm cp}/f$  confirms the validity of the CP measurement.

Fig. 2. Dependence of normalized CP current  $(I_{\rm cp}/f)$  on measurement frequency. In CP measurement, the  $V_t$  window  $(\Delta V_t)$  is 2.7 V and  $I_{\rm cp}$  is measured at  $V_{\rm gl}=2.5$  V.

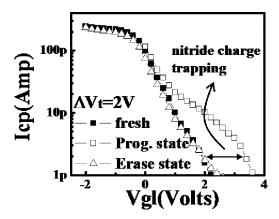

Fig. 3.  $I_{\rm CP}$  versus  $V_{\rm gl}$  in a fresh cell, in program state and in erase state, respectively. The  $V_t$  window  $(\Delta V_t)$  is 2 V.  $V_d$  in CP measurement is 0 V.

## III. MEASUREMENT RESULT AND DISCUSSION

# A. Single-Bit Storage

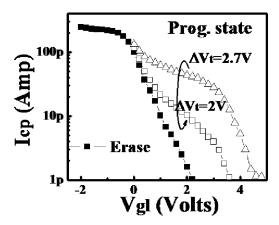

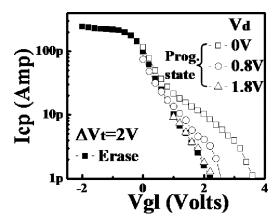

Fig. 3 shows the  $I_{\rm cp}$  versus  $V_{\rm gl}$  curves in a virgin cell, after programming only, and after one P/E cycle, respectively. Only the first bit (drain side) is P/E cycled and the  $V_d$  in CP measurement is 0 V. The threshold voltage window ( $\Delta V_t$ ) is 2 V. The  $I_{\rm cp}$  in a virgin cell and in erase state are almost identical, whereas a noticeable  $I_{\rm cp}$  bump at program state is noticed. This  $I_{\rm cp}$  bump is attributed to a local increase of channel threshold voltage due to negative nitride charge trapping. To verify the nitride charge storage effect, the  $I_{\mathrm{cp}}$  characteristics for two different threshold voltage windows,  $\Delta V_t = 2 \text{ V}$  and 2.7 V, are compared in Fig. 4. As expected, the larger threshold voltage window exhibits a larger  $I_{\rm cp}$  bump due to more stored electrons. The dependence of the program-state  $I_{\rm cp}$  bump on  $V_d$  in charge pumping measurement is shown in Fig. 5. The  $I_{\rm CD}$  bump is suppressed as  $V_d$  increases. The reason is that the drain depletion region increases with  $V_d$ . At a sufficiently large  $V_d$  (in this Fig. 1.8 V), interface traps underneath the program charges are completely "masked" by the drain depletion region. Thus, these interface traps can no longer go through inversion-accumulation cycles in CP measurement and do not contribute to  $I_{\rm cp}$ . As a result, the program-state  $I_{\rm cp}$  bump is totally suppressed. Our

Fig. 4.  $I_{\rm cp}$  versus  $V_{\rm gl}$  for different  $V_t$  window. The program state  $I_{\rm cp}$  bump increases with  $V_t$  window due to more injected charges.

Fig. 5.  $I_{\rm cp}$  versus  $V_{\rm gl}$  with different  $V_d$  in CP measurement. The program-state  $I_{\rm cp}$  bump decreases with  $V_d$ . The  $V_t$  window is 2 V.

result here implies that a  $V_d$  about 1.8 V is necessary in reverse read to avoid completely the second bit effect.

## B. Two-Bit Storage

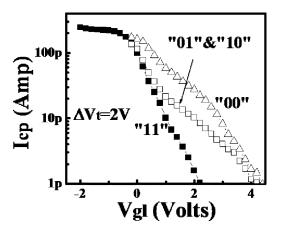

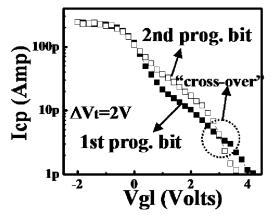

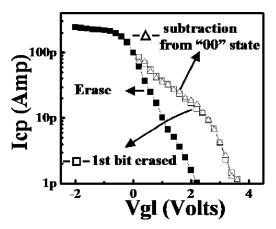

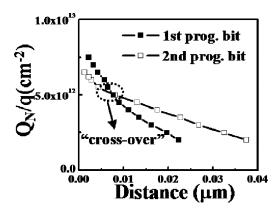

The Nbit cell stores two bits at different locations (drain-side and source-side). Each bit within a cell serves as binary unit of data that is totally mapped to four states in a memory cell. The  $I_{\rm CD}$  of the four states corresponding to "11," "10," "01" and "00" are shown in Fig. 6. "00" denotes both bits in program state. "10" (or "01") denotes the drain-side bit in erase state (or in program state) and the source-side bit in program state (or in erase state). To explore the influence of the programming sequence on trapped charge spatial profile, the CP measurement is performed after each bit is programmed. Fig. 7 shows the  $I_{cp}$  of the first programmed bit and the second programmed bit, respectively. Here, the  $I_{\rm cp}$  of the second programmed bit is obtained in two ways. One is to measure  $I_{cp}$  after the first bit is erased. The second approach is to subtract the fist bit  $I_{cp}$  from the "00" state  $I_{\rm cp}$ . Fig. 8 compares the second bit  $I_{\rm cp}$  from the above two approaches and the result is almost the same. It should be emphasized that a crossover of the first bit and the second bit  $I_{\rm cp}$  in Fig. 7 is observed. This suggests that the second programmed bit has a wider charge distribution but a smaller peak density. The reason will be discussed later. To profile the nitride stored charge lateral distribution, a technique similar to [9] is performed. In

Fig. 6.  $I_{\rm cp}$  versus  $V_{\rm gl}$  of the four states of two-bit storage. "11" represents both bits in erase-state and "10" represents one bit in erase-state and one bit in program-state.

Fig. 7. Comparison of the  $I_{\rm cp}$  versus  $V_{\rm gl}$  of the first programmed bit and the secondly programmed bit. The second bit  $I_{\rm cp}$  is measured with the first bit erosed

Fig. 8. Comparison of the second bit  $I_{\rm cp}$ - $V_{\rm gl}$  from two approaches. One is to measure  $I_{\rm cp}$  after the first bit is erased. The second approach is to subtract the fist bit  $I_{\rm cp}$  from the "00" state  $I_{\rm cp}$ .

profiling, we make the following assumptions. First, we assume that a fresh cell has uniform interface trap density  $(N_{\rm it})$  along the channel [9]. The CP current thus should have a linear dependence on channel position x

$$x = \frac{I_{\rm cp}(V_{\rm gl})}{I_{\rm cp,max}} L_{\rm ch} \tag{1}$$

Fig. 9. Lateral profiling of the programmed charge distribution of the first programmed bit and the secondly programmed bit. A uniform interface trap distribution along the channel is assumed.  $I_{\rm cp,max}$  in (1) is 195 pA.

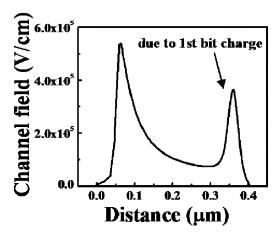

Fig. 10. Simulated channel field distribution in second bit programming from 2-D device simulation. x=0 is at the n<sup>+</sup> source edge and x=0.4 is at the n<sup>+</sup> drain edge.  $V_s=6.5$  V and  $V_g=11$  in second bit programming.

where x=0 is defined at the edge of the source or drain junction.  $L_{\rm ch}$  is the channel length and  $I_{\rm cp,max}$  denotes the saturated CP current. The second assumption is that  $N_{\rm it}$  generation after one program/erase (P/E) cycle is negligible. Based on these assumptions, the nitride charge distribution is deduced as follows:

$$Q_N(x) = \frac{C_{\text{ONO}}}{q} (V_{\text{gl}} - V_{\text{ti}})$$

(2)

where  $Q_N(x)$  is the nitride charge density at the position x, and  $V_{\rm ti}$  stands for the threshold voltage of a fresh device. Fig. 9 depicts the extracted stored charge distribution of the first programmed bit and the second programmed bit versus a distance from the source/drain junction. The stored charges extend into the channel about tens of nanometers. This result is in agreement with the simulation in [7]. In addition, the CP measurement result shows that the second programmed bit exhibits a broader distribution but a smaller peak density. To explain this result, a two-dimensional device simulation is performed. A rectangular charge distribution with a width of 30 nm and a charge density of  $1.6 \times 10^{19}$  cm<sup>-3</sup> is used. Fig. 10 shows the lateral channel electric field distribution in the second bit programming. A large channel field exists not only in the programmed region but also in the first bit region (drain side). Such a large field in the first bit region will accelerate channel electrons from the drain and cause

Fig. 11. Difference in  $I_{\rm cp}$  between program-state and erase-state as a function of drain bias for the first bit and source bias for the second bit. The  $\Delta I_{\rm cp}$  is obtained from Figs. 6 and 7 at  $V_{\rm gl}=1.6~{\rm V}$ .

Fig. 12. Difference in  $I_{\rm CP}$  between program state and erase state as a function of  $V_d$  in CP measurement at various P/E cycle numbers.  $\Delta I_{\rm CP}$  is measured at  $V_{\rm gl}=1.6$  V and is normalized to its value at  $V_d=0$  V to take into account interface trap creation in cycling.

earlier hot electron injection into the nitride, thus resulting in a broader second bit distribution. Finally, we would like to remark that (2) and consequently Fig. 9 are derived from a simplified one-dimensional model. For a narrow charge distribution by hot electron programming, (2) only serves as a first-order approximation. Accurate profiling of programmed charge distribution requires a more complicated 2-D model.

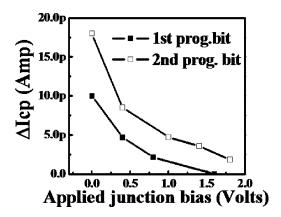

The programmed charge lateral extent can be also probed by varying  $V_d$  (or  $V_s$ ) in CP measurement. Fig. 11 shows the difference in  $I_{\rm CP}$  between program state and erase state versus  $V_d$  (or  $V_s$ ).  $\Delta I_{\rm CP}$  is measured at  $V_{\rm gl}=1.6$  V. The second programmed bit needs a larger junction bias to "mask" the programmed charge. The same conclusion that the second bit has a broader charge distribution is obtained.

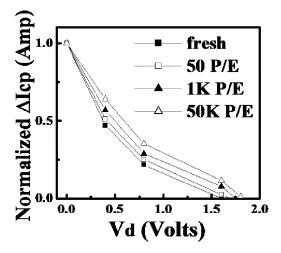

## C. P/E Cycling Stress Effect

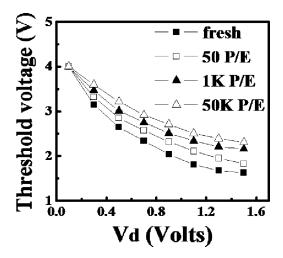

The P/E cycling stress effect on programmed charge distribution is examined in Fig. 12 by using the variable  $V_d$  method. The  $V_t$  window keeps the same during cycling. Again, the  $\Delta I_{\rm cp}$  is measured at  $V_{\rm gl}=1.6$  V and is normalized to its value at  $V_d=0$  V to compensate for interface trap creation effect for different cycling stress. It has been reported that hot-carrier stress

Fig. 13. Threshold voltage versus reverse read  $V_d$  for different cycle numbers.

created oxide traps spread toward the channel with stress time [10], [11]. Such traps, especially positively charged traps, can effectively lower the  $\mathrm{Si/SiO_2}$  injection barrier [12], [13] and enhance the electron injection probability. Therefore, as cycle number (stress time) increases, the hot electron injection region expands toward the channel due to the spread of the bottom oxide damaged region. A larger  $V_d$  in CP measurement is necessary to screen programmed charge at a larger cycle number. The consequence of the broadening of programmed charge distribution is the degradation of the second bit effect. Fig. 13 shows the threshold voltage versus  $V_d$  in reverse read for different cycle numbers. The second bit effect is apparently worsened with increasing cycle number.

## IV. CONCLUSION

We have characterized the programmed charge lateral distribution in a two-bit storage nitride Flash cell by a channel hot electron program. The CP measurement reveals that the charge distribution of each bit extends into the channel for tens of nanometers. This suggests the possibility of further scaling down the nitride Flash cell with respect to the overlap of two bit charges. Our paper also shows that the charge distribution of the second programmed bit is influenced by the stored charge of the first bit. A broader second bit charge distribution is obtained.

#### ACKNOWLEDGMENT

The authors would like to thank MXIC, Taiwan, R.O.C. for providing technical support.

#### REFERENCES

- [1] M. H. White, "On the go with SONOS," *IEEE Circuits Devices Mag.*, vol. 16, no. 1, p. 22, Jan. 2000.

- [2] M. K. Cho and D. M. Kim, "High performance SONOS memory cells free of drain turn-on and over-erase: Compatibility issue with current Flash technology," *IEEE Electron Device Lett.*, vol. 21, no. 5, pp. 399–401, May 2000.

- [3] B. Eitan, P. Pavan, I. Bloom, E. Aloni, A. Frommer, and D. Finzi, "NROM: A novel localized trapping, 2-bit nonvolatile memory cell," *IEEE Electron Device Lett.*, vol. 21, no. 7, pp. 543–545, Jul. 2000.

- [4] W. J. Tsai, N. K. Zous, C. J. Liu, C. C. Liu, C. H. Chen, T. Wang, S. Pan, and C.-Y. Lu, "Data retention behavior of a SONOS type two-bit storage Flash memory cell," in *IEDM Tech. Dig.*, 2001, pp. 719–722.

- [5] Y. W. Chang, T. C. Lu, S. Pan, and C.-Y. Lu, "Modeling for the second-bit effect of a nitride-based trapping storage Flash EEPROM cell under two-bit operation," *IEEE Electron Device Lett.*, vol. 25, no. 1, p. 95, Jan. 2004.

- [6] W. J. Tsai, N. K. Zous, M. H. Chou, S. Huang, H. Y. Chen, Y. H. Yeh, M. Y. Liu, C. C. Yeh, T. Wang, J. Ku, and C.-Y. Lu, "Cause of erase speed degradation during two-bit per cell operation of a trapping nitride storage Flash memory cell," in *Proc. Int. Reliability Phys. Symp.*, 2004, pp. 522–526.

- [7] L. Larcher, G. Verzellesi, P. Pavan, E. Lusky, I. Bloom, and B. Eitan, "Impact of programming charge distribution on threshold voltage and subthreshold slope of NROM memory cells," *IEEE Trans. Electron De*vices, no. 11, pp. 1939–1946, Nov. 2002.

- [8] S. H. Gu, M. T. Wang, C. T. Chan, N. K. Zous, C. C. Yeh, W. J. Tsai, T. C. Lu, T. Wang, J. Ku, and C.-Y. Lu, "Investigation of programmed charge lateral spread in a two-bit nitride storage Flash memory cell by using a charge pumping technique," in *Proc. Int. Reliability Phys. Symp.*, 2004, pp. 639–640.

- [9] C. Chen and T. P. Ma, "Direct lateral profiling of hot-carrier-induced oxide charge and interface traps in thin gate MOSFET's," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 512–520, Apr. 1998.

- [10] W. Chen and T. P. Ma, "Oxide charge buildup and spread-out during channel-hot-carrier injection in N-MOSFET's," *IEEE Electron Device Lett.*, vol. 13, no. 4, pp. 319–321, Apr. 1992.

- [11] M. G. Ancona, N. S. Saks, and D. Mccarthy, "Lateral distribution of hot-carrier-induced interface traps in MOSFET's," *IEEE Trans. Electron Devices*, vol. ED-35, no. 11, pp. 2221–2228, Nov. 1988.

- [12] N. K. Zous, Y. J. Chen, C. Y. Chin, W. J. Tsai, T. C. Lu, M. S. Chen, W. P. Lu, T. Wang, S. Pan, and C. Y. Lu, "An endurance evaluation method for Flash EEPROM," *IEEE Trans. Electron Devices*, vol. 51, no. 6, pp. 720–725, Jun. 2004.

- [13] J. Wu, L. F. Register, and E. Rosenbaum, "Trap-assisted tunneling current through ultrathin oxide," in *Proc. Int. Reliability Phys. Symp.*, 1999, pp. 389–395.

Shaw-Hung Gu was born in Taipei, Taiwan, R.O.C. on August 11, 1977. He received the B.S. degree from Chang-Gung University, Taoyuan, Taiwan, R.O.C., in 1999, and the M.S. degree in electronics engineering from the National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., in 2001. Currently, he is pursuing the Ph.D. degree at the same university.

His research interest focuses on the physics and characterization of nonvolatile memory, especially in nitride-based storage memory and thin oxide reliability.

**Tahui Wang** (S'85–M'86–SM'94) was born in Tao-Yuan, Taiwan, R.O.C., on May 3, 1958. He received the B.S.E.E. degree from the National Taiwan University, Taipei, Taiwan, R.O.C. and the Ph.D. degree in electrical engineering from the University of Illinois, Urbana-Champaign, in 1980 and 1985, respectively.

From 1985 to 1987, he was with Hewlett-Packard Laboratories, Palo Alto, CA, where he was engaged in the development of GaAs HEMT devices and circuits. Since 1987, he has been with the Department

of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., where he is currently a Professor. His research interests include hot carrier phenomena characterization and reliability physics in VLSI devices, RF CMOS devices, and nonvolatile semiconductor devices.

Dr. Wang was granted the Best Teacher Award by the Ministry of Education, Taiwan, R.O.C. He has served as technical committee member of many international conferences, among them IEDM, IRPS, and VLSI-TSA. He was an invited speaker at the 2003 IEDM on the topic of nitride Flash reliability.

Wen-Pin Lu was born in Ilan, Taiwan, R.O.C. on December 20, 1967. He received the B.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. and the M.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, R.O.C. in 1990 and 1992, respectively.

He joined Macronix International Company, Ltd., Hsinchu, Taiwan, R.O.C. in 1994 as a Device Engineer. From 1994 to 1999, he worked on device analysis of nonvolatile memory, especially in

floating-gate Flash memory. Since 2000, he has been engaged in the development of PACAND Flash memory technology, and has accomplished a 0.18 and 0.15  $\mu$ m method of delivering. He is presently responsible for the nitrite-based Nbit technology integration at Macronix.

Wenchi Ting received the Ph.D. degree in electrical engineering from the University of Texas at Austin.

He has been involved with developing SRAM, EPROM, EEPROM, Flash, and embedded Flash technologies. He is currently a Senior Director at Macronix International Company, Ltd., Hsinchu, Taiwan, R.O.C., focusing on developing silicon-nitride trapping based nonvolatile memory processes.

Yen-Hui Joseph Ku received the B.S. degree in electrical engineering from National Cheng-Kung University, Tainan, Taiwan, in 1979, and the M.S. and Ph.D. degrees in electrical and computer engineering from the University of Texas at Austin in 1983 and 1988, respectively. His research was on the self-aligned silicide and shallow junction formation for deep submicrometer device application.

In 1987, he joined Rapro Technology, Fremont, CA, as a cofounder with responsibility for RTPCVD reactor design and process development. From 1991

to 1992, he was with Paradigm Technology, San Jose, CA, where he worked on 0.35- $\mu$ m 4-Mb SRAM technology development. In 1992, he joined LSI Logic, Santa Clara, CA, where he worked on advanced logic technology development and served as Integration Manager of the R&D Division until 1997. He later joined the Technology Development Division of Macronix International Company, Ltd., Hsinchu, Taiwan, R.O.C. He currently leads the Technology Development Center and is responsible for the development of advanced nonvolatile memory and embedded SOC technologies. He has published more than 30 papers in technical journals and conferences.

**Chih-Yuan Lu** (M'77–SM'84–F'94) received the B.S. degree from National Taiwan University, Taipei, Taiwan, R.O.C., in 1972, and the Ph.D. degree in physics from Columbia University, New York, in 1977

From 1978 to 1983, he was an Associate Professor and was promoted to Full Professor, National Chiao-Tung University, Hsinchu, Taiwan. In 1983, he was with North Carolina State University, Raleigh, as a Visiting Associate Professor and Adjunct Research Staff Member of the Microelectronic Center of North

Carolina (MCNC), Research Triangle Park. In 1984, he joined AT&T Bell Laboratories, where he was engaged in very high voltage bipolar-CMOS-DMOS (BCDMOS) IC technology for telecommunication applications, CMOS DRAM technology, laser programmable redundancy, and submicron CMOS ULSI technology. He joined the Electronics Research and Service Organization, Industrial Technology Research Institute, Hsinchu, (ERSO/ITRI) in late 1989 as a Deputy General Director responsible for semiconductor and integrated circuit operation, especially the Grand Submicron Project. This project later successfully developed Taiwan's first 8-in CMOS submicrometer manufacturing technology with high-density DRAM/SRAM as technology vehicles. In late 1994, he was the Cofounder of Vanguard International Semiconductor Corporation, Hsinchu, which is a spinoff memory IC company from ITRI's Submicrometer Project. He was the Vice President of Operations, Vice President of Research and Development, and later President from 1994 to 1999. He brought Vanguard from a research and development laboratory to a U.S. \$400 million sales company that went IPO in 1998. He is currently Chairman and CEO of Ardentec Corporation, Hsinchu, a VLSI testing service company, and also serves Macronix International Company (MXIC), Ltd., Hsinchu, as a Senior Vice President/CTO. He led MXIC's technology development team to successfully achieve the state-of-the-art nonvolatile memory technology and embedded SoC technology, now, MXIC is the top nonvolatile semiconductor company in Taiwan. He has published more than 100 technical papers and has been granted 123 international patents. He also authored more than 30 articles in science education and R&D policy in magazines and newspapers. He served as the President of Science Monthly from 1978 to 1983.

Dr. Lu was the Executive Secretary and Managing Director of the Board and Board Director since 1998 for the Physical Society of Taiwan. from 1981 to 1984. He has been Vice-Chairman and then Chairman of IEEE Electron Devices Society, Taipei Chapter, from 1991 to 1996, and Board Director and Supervisor of IEEE Section since 1996. He is a member of many honor societies, including Sigma Pi Sigma, Phi Tau Phi, and Phi Lambda. He is a life member of the American Physical Society, the Physical Society of ROC, the Chinese Institute of Engineers, and CIE-USA. He received the National Science and Technology Achievement Award from the Prime Minister of Taiwan in 1994. In 1995, he was awarded the National Invention Award, and in 2002, he was awarded the most prestigious semiconductor award in Taiwan—the Pan Wen Yuan Award.