**Simulation study of 14-nm-gate III-V trigate field effect transistor devices with

$\text{In}_{1-x}\text{Ga}_x\text{As}$  channel capping layer**

Cheng-Hao Huang and Yiming Li<sup>1</sup>

Citation: [AIP Advances](#) **5**, 067107 (2015); doi: 10.1063/1.4922190

View online: <http://dx.doi.org/10.1063/1.4922190>

View Table of Contents: <http://aip.scitation.org/toc/adv/5/6>

Published by the [American Institute of Physics](#)

---

---

# Simulation study of 14-nm-gate III-V trigate field effect transistor devices with $\text{In}_{1-x}\text{Ga}_x\text{As}$ channel capping layer

Cheng-Hao Huang<sup>1,2</sup> and Yiming Li<sup>1,2,3,a</sup>

<sup>1</sup>Parallel and Scientific Computing Laboratory, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>2</sup>Institute of Communications Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>3</sup>Department of Electrical and Computer Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

(Received 10 March 2015; accepted 18 May 2015; published online 2 June 2015)

In this work, we study characteristics of 14-nm-gate InGaAs-based trigate MOSFET (metal-oxide-semiconductor field effect transistor) devices with a channel capping layer. The impacts of thickness and gallium (Ga) concentration of the channel capping layer on the device characteristic are firstly simulated and optimized by using three-dimensional quantum-mechanically corrected device simulation. Devices with  $\text{In}_{1-x}\text{Ga}_x\text{As}/\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$  channels have the large driving current owing to small energy band gap and low alloy scattering at the channel surface. By simultaneously considering various physical and switching properties, a 4-nm-thick  $\text{In}_{0.68}\text{Ga}_{0.32}\text{As}$  channel capping layer can be adopted for advanced applications. Under the optimized channel parameters, we further examine the effects of channel fin angle and the work-function fluctuation (WKF) resulting from nano-sized metal grains of NiSi gate on the characteristic degradation and variability. To maintain the device characteristics and achieve the minimal variation induced by WKF, the physical findings of this study indicate a critical channel fin angle of  $85^\circ$  is needed for the device with an averaged grain size of NiSi below  $4 \times 4 \text{ nm}^2$ . © 2015 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [<http://dx.doi.org/10.1063/1.4922190>]

## I. INTRODUCTION

Silicon-based metal-oxide-semiconductor field effect transistor (MOSFET) devices face various challenges on materials, structural innovation, and process improvement. High-speed MOSFET devices could be realized by using InGaAs related materials owing to their high electron mobility.<sup>1</sup> Recent studies on III-V FETs have shown fascinating characteristics from thin-channel planner MOSFETs.<sup>2,3</sup> III-V junctionless FET devices have also been reported for even superior on/off-state current ratio.<sup>4,5</sup> InGaAs/InAlAs is one of highly attractive III-V materials due to little lattice mismatch<sup>6</sup> and outstanding heterojunction transport property.<sup>7</sup> III-V materials have the higher electron mobility than silicon one which can increase the driving current. However, the leakage current will be increased at the same time. Consequently, proper channel capping or barrier layers<sup>8–11</sup> will be beneficial for device applications. However, the effect of channel capping layers on electircal and physical characteristics of the aforementioned devices has not been clearly investigated.

In this work, we study the impact of the thickness ( $T_{\text{cap}}$ ) and the mole fraction ( $x$ ) of gallium (Ga) of channel capping layer on physical and electrical characteristics of 14-nm  $\text{In}_{1-x}\text{Ga}_x\text{As}$  /  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$  /  $\text{In}_{0.52}\text{Al}_{0.48}\text{As}$  / InP trigate MOSFET on silicon substrate. Notably, devices with high- $\kappa$ /metal gate (HKMG) have attracted great attention.<sup>12–19</sup> Owing to similarity in materials

<sup>a</sup>Corresponding Author. Professor Yiming Li. E-mail: [ymli@faculty.nctu.edu.tw](mailto:ymli@faculty.nctu.edu.tw)

of capping layer  $\text{In}_{1-x}\text{Ga}_x\text{As}$  and channel layer  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$ , the explored new device could be fabricated. By considering physically noticeable parameters of short-channel effect (SCE): on-/off-state current ( $I_{\text{on}}/I_{\text{off}}$ )  $> 1.7 \times 10^6$ , subthreshold swing (SS)  $< 72 \text{ mV/dec}$ , and drain-induced barrier lowering (DIBL)  $< 55 \text{ mV/V}$  simultaneously, we will find the feasible range of  $T_{\text{cap}}$  and  $x$  for high-performance device applications, where the threshold voltage ( $V_{\text{th}}$ ) is targeted at 160 mV. After that, metal gates may introduce a random fluctuation source, so-called the work-function fluctuation (WKF)<sup>20-23</sup> owing to the dependency of work function (WK) on the random orientation of nano-sized metal grain.<sup>24</sup> Such uncontrollable grain orientations result in random WK of metal during fabrication period.<sup>23,25</sup> Many studies concerning WKF on silicon-based planar devices have been reported,<sup>20,21,24</sup> but researches about the WKF on III-V MOSFETs<sup>26</sup> have not been well explored. Theoretically, ideally rectangular shape of the trigate may not always guarantee because of limitations of the fabrication process in III-V MOSFET devices. The process distortion comes from lithography processes and etching steps causes significant SCEs and degrades the device performance.<sup>27,28</sup> Therefore, we further discuss characteristic variation resultin from different channel fin angle and WKF of gate metal.

This paper is organized as follows. Section II introduces the device structure and simulation settings. Section III reports the impact of the thickness of  $\text{In}_{1-x}\text{Ga}_x\text{As}$  capping layer and the mole fraction of Ga on III-V trigate MOSFET and discusses the WKF-induced and channel-fin-angle-variability for the achieved optimal devices including the fluctuation suppression and the proper channel fin angle to be adopted. Finally, we draw conclusions and suggest future work.

## II. DEVICE CONFIGURATION AND SIMULATION METHODOLOGY

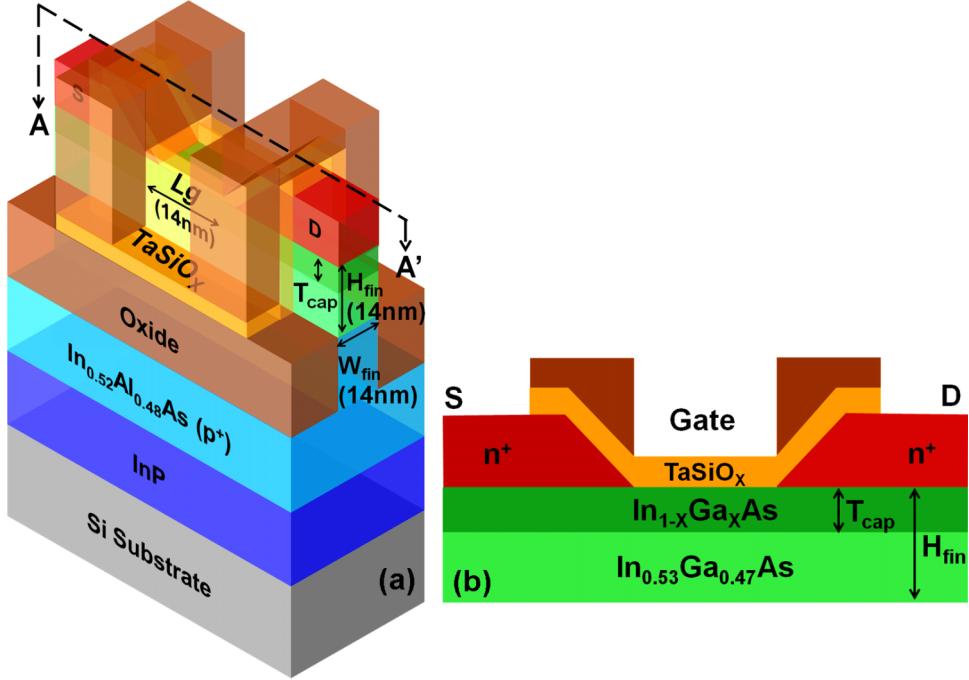

Figure 1(a) shows a 3D-plot of the InGaAs-based trigate MOSFET. Above the silicon substrate is the 1- $\mu\text{m}$ -thick InP then the 1.5- $\mu\text{m}$ -thick p-type doped by beryllium  $1 \times 10^{15} \text{ cm}^{-3}$   $\text{In}_{0.52}\text{Al}_{0.48}\text{As}$  buffer layer follows, and undoped  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$  channel layer is applied. The channel capping layer of  $\text{In}_{1-x}\text{Ga}_x\text{As}$  with different  $x$  and  $T_{\text{cap}}$  is covered with  $\text{TaSiO}_x$ . Source/drain is doped by silicon as n-type dopant. Figure 1(b) is a cross-sectional view along the cutting line AA', where the intrinsic channel is  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}$  with a capping layer of  $\text{In}_{1-x}\text{Ga}_x\text{As}$ . The adopted parameters, such as effective oxide thickness, work function, and doping concentrations, are listed in Table I, where  $T_{\text{cap}}$  varies from 0 to 5 nm and  $x$  is from 0.27 to 0.42.

To minimize the random dopant fluctuation,<sup>29</sup> undoped  $\text{In}_{1-x}\text{Ga}_x\text{As}$  capping layer above channel is studied. Optimal channel capping layer of  $\text{In}_{1-x}\text{Ga}_x\text{As}$  will be discussed subject to the aforementioned SCE parameters. The 3D drift-diffusion model and density-gradient equations are solved numerically at the same time for including quantum mechanical effects. The band gaps of the relevant binary compounds are functions of temperature T:

$$E_g(\text{InAs}) = 0.36 - \frac{2.760 \times 10^{-4} T^2}{T + 93}, \quad (1)$$

$$E_g(\text{GaAs}) = 1.42 - \frac{5.405 \times 10^{-4} T^2}{T + 204}, \quad (2)$$

and the band gap of ternary compound depending on composition fraction  $x$  is given by:<sup>30</sup>

$$E_g(\text{In}_{1-x}\text{Ga}_x\text{As}) = 0.36 + 0.629x + 0.436x^2. \quad (3)$$

The scattering which causes the mobility degradation is dominated by phonon scattering and the high normal field inside capping layers. The acoustic mobility due to acoustic phonon scattering is

$$\mu_{ac} = \frac{B}{F_{\perp}} + \frac{C(N_i/N_0)^{\lambda}}{F_{\perp}^{1/3}(T/300K)^k}, \quad (4)$$

where  $B$  and  $C$  are the fitting parameters.<sup>31</sup> Notably, the acoustic mobility is inversely proportional to the effective masses which are incorporated into the fitting parameters.<sup>31</sup> The contribution

FIG. 1. (a) 3D structure of the explored III-V trigate MOSFET. (b) Zoom-in cross-sectional view of the device, along the cutting line AA' in (a).

TABLE I. Parameters used for the simulated devices.

|                                                                             |                         |

|-----------------------------------------------------------------------------|-------------------------|

| Effective oxide thickness (nm)                                              | 0.52                    |

| Gate work function (eV)                                                     | 4.9                     |

| In <sub>1-x</sub> Ga <sub>x</sub> As (S/D layer) (cm <sup>-3</sup> )        | 1x10 <sup>19</sup> (Si) |

| In <sub>1-x</sub> Ga <sub>x</sub> As (capping layer) (cm <sup>-3</sup> )    | Undoped                 |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As (channel) (cm <sup>-3</sup> )      | Undoped                 |

| In <sub>0.52</sub> Al <sub>0.48</sub> As (buffer layer) (cm <sup>-3</sup> ) | 1x10 <sup>15</sup> (Be) |

| InP (cm <sup>-3</sup> )                                                     | 1x10 <sup>16</sup> (Be) |

attributed to surface roughness scattering is given by:

$$\mu_{sr} = \left( \frac{(F_{\perp}/F_{ref})^2}{\delta} + \frac{F_{\perp}^3}{\eta} \right)^{-1}. \quad (5)$$

These surface contributions to the mobility are then combined with the bulk mobility  $\mu_b$ :

$$\frac{1}{\mu_{low}} = \frac{1}{\mu_b} + \frac{D}{\mu_{ac}} + \frac{D}{\mu_{sr}}. \quad (6)$$

The reference field  $F_{ref} = 1$  V/cm ensures a unitless numerator in Eq. (5).  $F_{\perp}$  is the transverse electric field normal to the semiconductor-insulator interface.  $D = \exp(-y/l_{crit})$  (where  $y$  is the distance from the interface and  $l_{crit}$  is a fit parameter) is used to describe the damping that switches off the inversion layer from the interface. The other parameters are listed in Table II.

Devices will be operated under high electric fields; the drift velocity of carrier is no longer proportional to the electric field and will be saturated. To describe this, the high-field mobility model<sup>32</sup> is further considered:

$$\mu_F = \frac{\mu_{low}}{\left[ 1 + \left( \frac{\mu_{low} F}{v_{sat}} \right) \beta_F \right]^{1/\beta_F}}, \quad (7)$$

TABLE II. List of the adopted parameters.

| Coefficients      | Electrons          | Holes                   | Unit                                       |

|-------------------|--------------------|-------------------------|--------------------------------------------|

| $B$               | $9.5 \times 10^8$  | $9.925 \times 10^6$     | cm/s                                       |

| $C$               | $1.16 \times 10^4$ | $2.947 \times 10^3$     | $\text{cm}^{5/3}/(\text{V}^{2/3}\text{s})$ |

| $N_0$             | 1                  | 1                       | $\text{cm}^{-3}$                           |

| $\lambda$         | 0                  | 0.0317                  | 1                                          |

| $k$               | 1                  | 1                       | 1                                          |

| $\delta$          | $1 \times 10^{14}$ | $2.0546 \times 10^{14}$ | V/s                                        |

| $\eta$            | $2 \times 10^{20}$ | $2.0546 \times 10^{30}$ | $\text{V}^2/(\text{cmxs})$                 |

| $l_{\text{crit}}$ | $1 \times 10^{-6}$ | $1 \times 10^{-6}$      | cm                                         |

where the low-field mobility  $\mu_{\text{low}}$  is calculated from Eq. (6), the exponent  $\beta_F$ ,  $v_{\text{sat}}$ , and the driving force  $F$  are given by

$$\beta_F = \beta_0 \left( \frac{T}{T_0} \right)^{\beta_{\text{exp}}}, \quad (8)$$

$$v_{\text{sat}} = A_{\text{vsat}} - B_{\text{vsat}} \left( \frac{T}{T_0} \right), \quad (9)$$

and

$$F_c = \vec{E} \cdot \left( \frac{\vec{j}_c}{|j_c|} \right), \quad (10)$$

where  $T$  denotes the lattice temperature, and the  $\vec{j}_c$  is the electron or hole current vector. Detail parameters are listed in Table III.

The traps placed at the high- $\kappa$  gate oxide-InGaAs interface are distributed within a narrow gap near the conduction band edge. They are acceptor type and negatively charged when occupied, where the density of interface traps is  $4 \times 10^{11} \text{ eV}^{-1} \text{cm}^{-2}$ .<sup>33</sup> By solving a set of 3D quantum-mechanically corrected device transport equations,<sup>34-38</sup> the current density, the carrier's density, the electric field, and related physical quantities are calculated for the entire device structure. The drain voltage of 0.8 V and the gate voltage varying from -0.2 to 0.8 V are supplied. The constant current method that the drain current sets at 100 nA/ $\mu\text{m}$  is used to extract the threshold voltage ( $V_{\text{th}}$ ).

Devices will suffer work-function fluctuation because the dependency of work function on the random orientation of nano-sized metal grain. Nickel has very high work function, and its compounds are usually used for metal gate. It has three orientations and each orientation has its corresponding work function with certain probability. It has been reported that the nickel silicide (NiSi) work function can be adjusted to 4.9 eV,<sup>39</sup> and the compounds usually have a strong correlation with the original materials. Therefore, we assume that nickel silicide has three kinds of work function with the corresponding probabilities. The work functions are 4.75, 4.85, and 5.05 eV with the probabilities: 30%, 30%, and 40%, respectively. First, under the optimal case of thickness and composition of the capping layer, we partition the gate metal into many sub-regions. Second, randomly generate work function in the sub-region according to the probability distribution of

TABLE III. List of the adopted parameters.

| Coefficients         | Electrons         | Holes             | Unit |

|----------------------|-------------------|-------------------|------|

| $\beta_0$            | 2                 | 2                 | 1    |

| $\beta_{\text{exp}}$ | 0                 | 0                 | 1    |

| $A_{\text{vsat}}$    | $4.5 \times 10^7$ | $1 \times 10^7$   | cm/s |

| $B_{\text{vsat}}$    | $5 \times 10^6$   | $3.6 \times 10^6$ | cm/s |

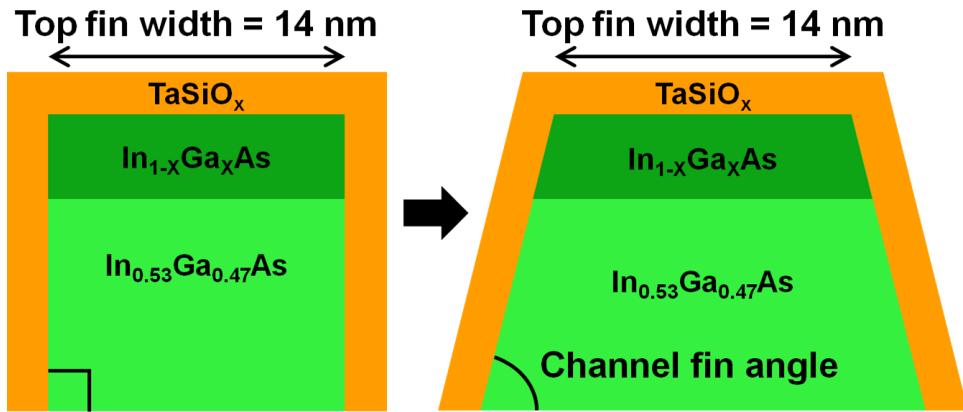

FIG. 2. The cross-sectional views of the rectangular and trapezoidal channel with 14-nm top-fin width. The channel fin angle is defined on it.

orientation. Finally, generate samples and solve a set of 3D quantum transport equations, where details of WKF simulation follow one of our recent works.<sup>40</sup> Theoretically, ideally right-angle shape (channel fin angle = 90°) of the trigate may not always guarantee because of limitations of the fabrication process in trigate III-V MOSFET devices. Therefore, according to the optimized case of thickness and composition of the channel capping layer above, we do further analyze the effect of process variation on the characteristic variability for the device with non-ideal cross-sectional channel shapes (i.e., devices with different channel fin angles). The device with trapezoidal-shaped channels is shown in Fig. 2, where the top-fin width is fixed at 14 nm and the channel fin angle varies from 70° to 90°. We calibrate all simulation cases having the same threshold voltage to explore the characteristic degradations owing to SCEs on trapezoidal-shape devices and WKF with different channel fin angles.

### III. RESULTS AND DISCUSSION

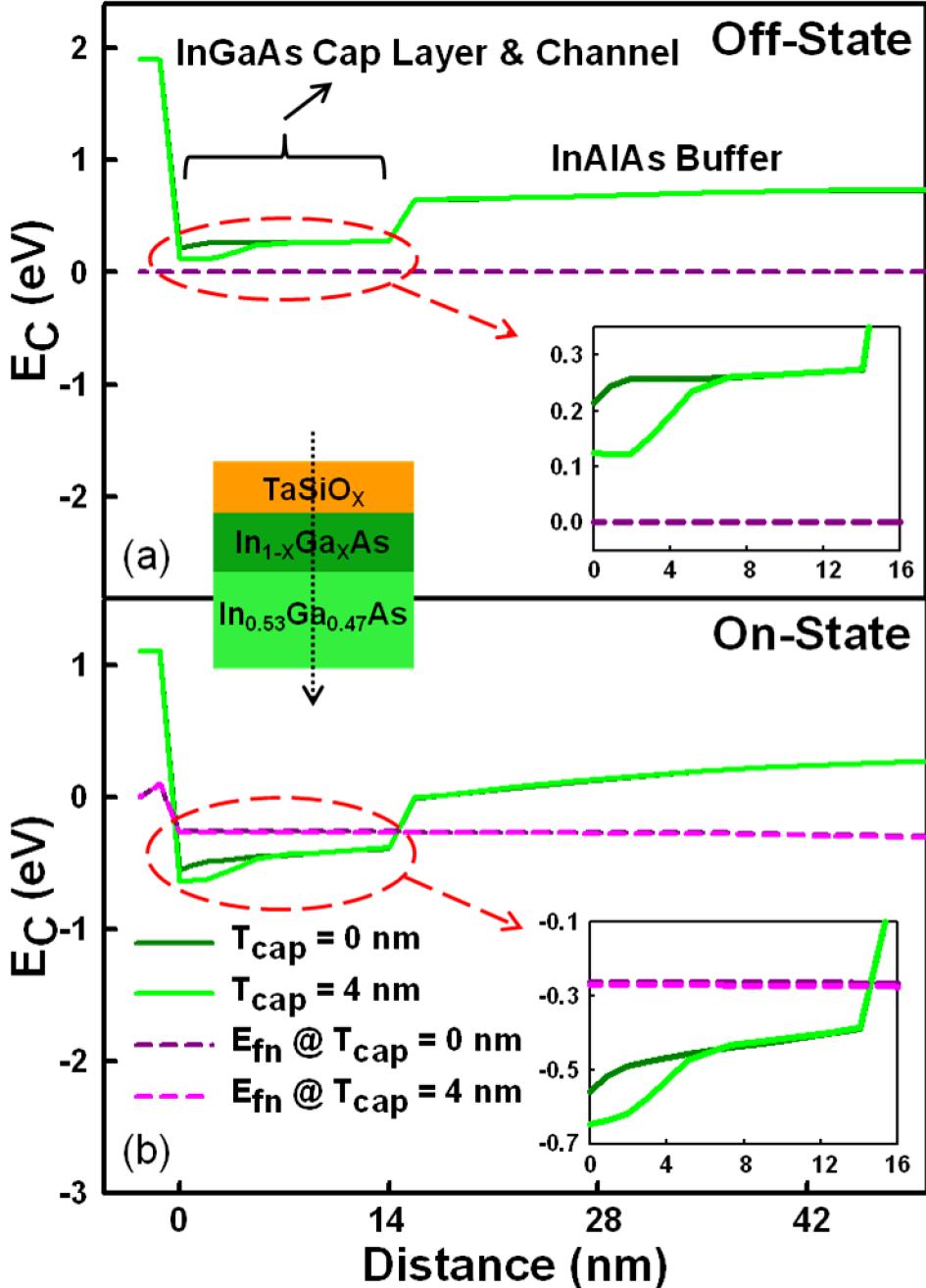

The energy band diagram, as shown in Fig. 3, is first simulated for both the on- and off-state from the channel surface to the substrate. Zoom-in plots of Figs. 3(a) and 3(b) clearly show that the conduction band energies of  $T_{cap} = 4$  nm are lower than that of  $T_{cap} = 0$  nm owing to the small energy band gap. All energies of the off-state are above Fermi level, so the III-V device is normally off. For the on-state, as shown in Fig. 3(b), the conduction bands and Fermi levels of electrons become negative. The electron's Fermi levels are above conduction bands, so the regions between electron's Fermi levels and conduction bands are filled with electrons. We can estimate the total electron concentration per unit volume in the conduction band by integrating the density of quantum states times the probability that a state is occupied by an electron over the conduction band energy. The conduction band energy is low, so the device with  $T_{cap} = 4$  nm has the large electron concentration and on-state current.

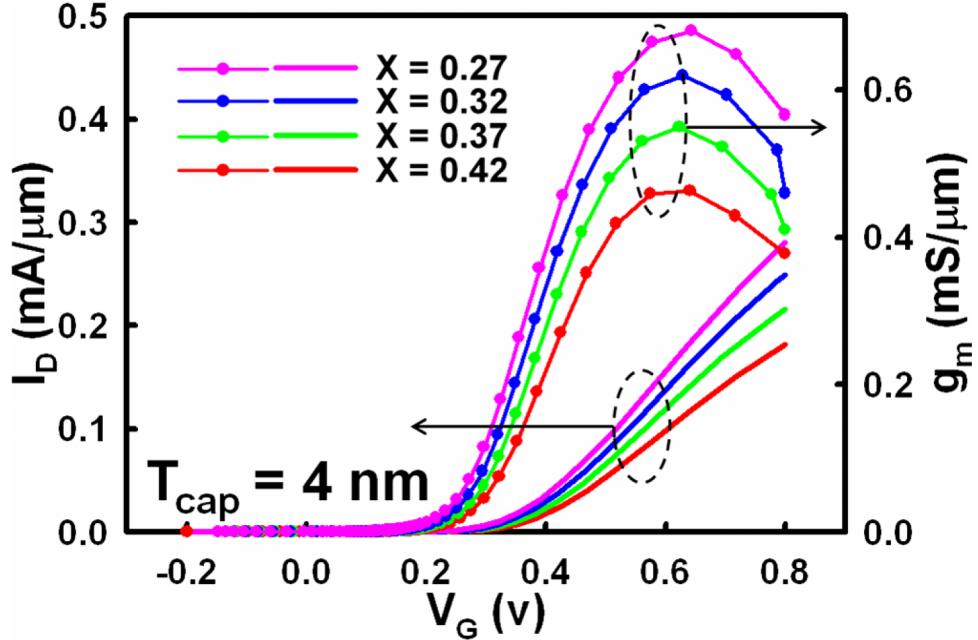

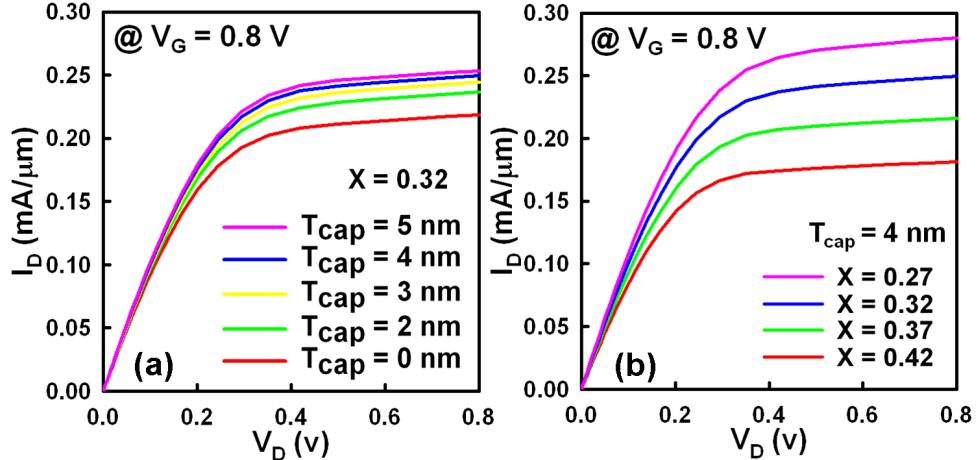

Figure 4 shows the  $I_D$ - $V_G$  and transconductance ( $g_m$ - $V_G$ ) curves with  $T_{cap} = 4$  nm and different Ga concentrations. Devices with low Ga concentration show high on-state current, resulting from improved carrier mobility. The lattice constant of  $In_{1-x}Ga_xAs$  with Ga mole fraction of 0.47 is about 0.586 nm, which matches with that of  $In_{0.52}Al_{0.48}As$ . For  $x < 0.47$ , the lattice constant of the capping layer is larger than 0.586 nm and the capping layer is subjected to a compressive strain. As the compressive strain increases, the alloy scattering decreases, resulting in improved electron mobility.<sup>41</sup> Furthermore, the mobility's reduction of the alloy scattering has its maximum effect at  $x = 0.7$ .<sup>42</sup> The reduction of the effective electron mass with the increasing indium concentration is also an important reason of mobility increasing, where the mobility is inversely proportional to the effective mass. As shown in Figs. 5(a) and 5(b), we plot the  $I_D$ - $V_D$  characteristics. The energy band gap of capping layer is smaller than that of channel layer. Because we fix the fin height, the fin channel will have the higher percentage of small energy band gap with increasing capping layer.

FIG. 3. (a) Off-state and (b) on-state energy band diagrams for the devices with  $x = 0.32$  and different  $T_{cap}$  of 0 and 4 nm. The energy near the channel surface for device with 4-nm-thick capping layer is smaller than that of device without capping layer.

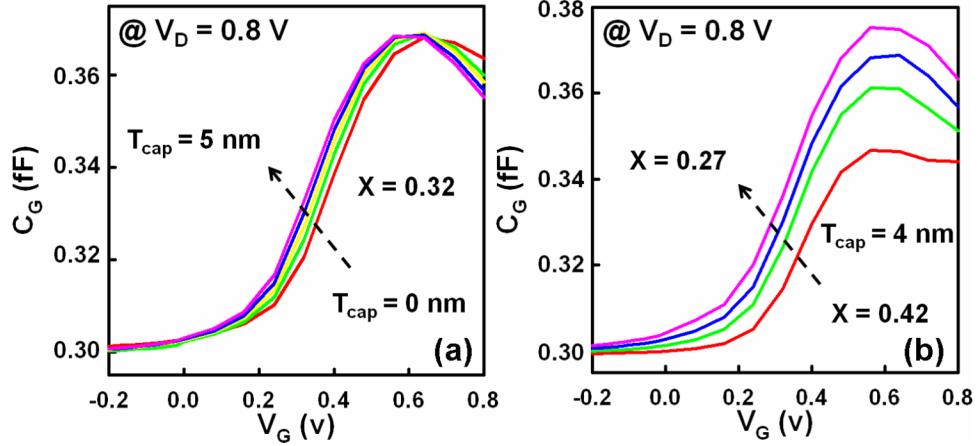

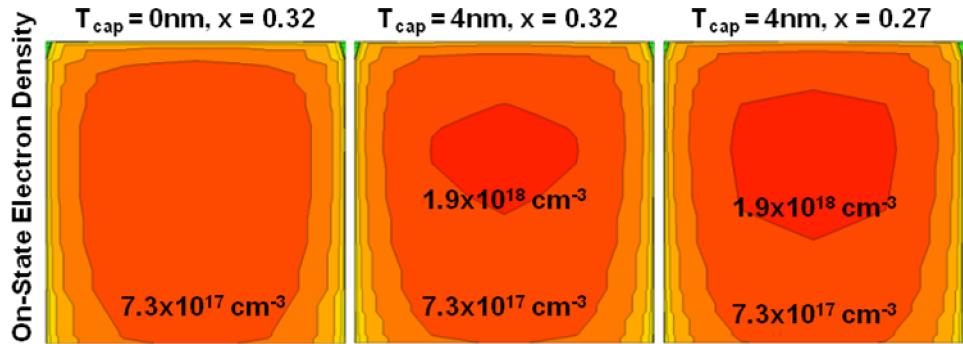

The mobility varies with capping layer composition that is similar for aforementioned reasons of Fig. 4. Hence, as the thickness of capping layer increases and the Ga mole fraction decreases, the device will possess large driving current due to relatively larger region of small band gap and high mobility. On the other hand, devices with a thick channel capping layer and a low Ga concentration have the large gate capacitance ( $C_G$ ), as shown in Figs. 6(a)-6(b). Large  $C_G$  will induce large inversion charge thereby enhancing the current density which can also be explained by using the results in Fig. 8. Therefore, devices with thick  $T_{cap}$  and low  $x$  possess the enhanced gate controllability

FIG. 4. Plots of  $I_D$ - $V_G$  and  $g_m$ - $V_G$  with different  $x$  and  $T_{cap} = 4 \text{ nm}$ . A small  $x$  implies a low Ga concentration which may reduce the alloy scattering and effective mass and then increase the channel mobility. Thus, it has higher drive current.

FIG. 5. (a) The  $I_D$ - $V_D$  curves of the device with  $x = 0.32$  and different  $T_{cap}$ . (b) The  $I_D$ - $V_D$  curves of the device with  $T_{cap} = 4 \text{ nm}$  and different  $x$ .

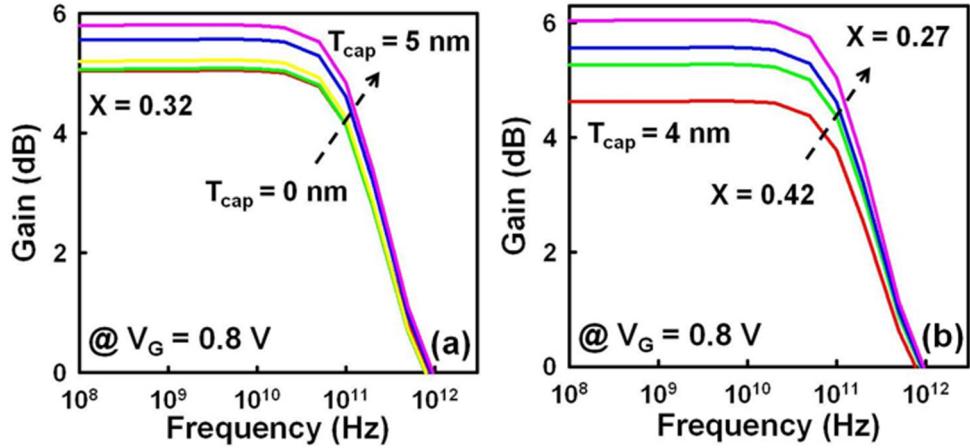

due to more carriers being sensitive to electrodes. Figures 7(a) and 7(b) even show the circuit gain versus operation frequency for different thickness and Ga mole fraction, respectively. We can obtain the wide unity-gain bandwidth by  $T_{cap}$  increasing and  $x$  decreasing. The unity-gain bandwidth is proportional to  $g_m/C_G$ ,<sup>43</sup> and the variations of  $g_m$  are relatively larger than  $C_G$  under the conditions of different  $T_{cap}$  and  $x$ . Therefore,  $g_m$  dominates the influence of unity-gain bandwidth, and the result is corresponding to Fig. 4.

Figure 8 shows the electron density profiles at the on-state for different  $x$  and  $T_{cap}$ . No matter increasing the thickness of capping layer or decreasing the gallium concentration, the centroid of the inversion charge density in the channel is pulled toward the gate oxide interface; consequently, they will induce high electron density and increase the on-state current. It also explains the tendency of transport current in Fig. 5. Notably, this phenomenon increases the gate control over the channel

FIG. 6. (a) The  $C_G$ - $V_G$  curves of the device with  $x = 0.32$  and different  $T_{cap}$ . (b) The  $C_G$ - $V_G$  curves of the device with  $T_{cap} = 4$  nm and different  $x$ .

FIG. 7. The curves of gain versus operation frequency for (a)  $x = 0.32$  and different  $T_{cap}$  and (b)  $T_{cap} = 4$  nm and different  $x$ .

FIG. 8. The on-state electron density.  $T_{cap}$  increasing and  $x$  decreasing not only induce high electron density but also pull the centroid of inversion charge density in the channel toward the gate oxide interface.

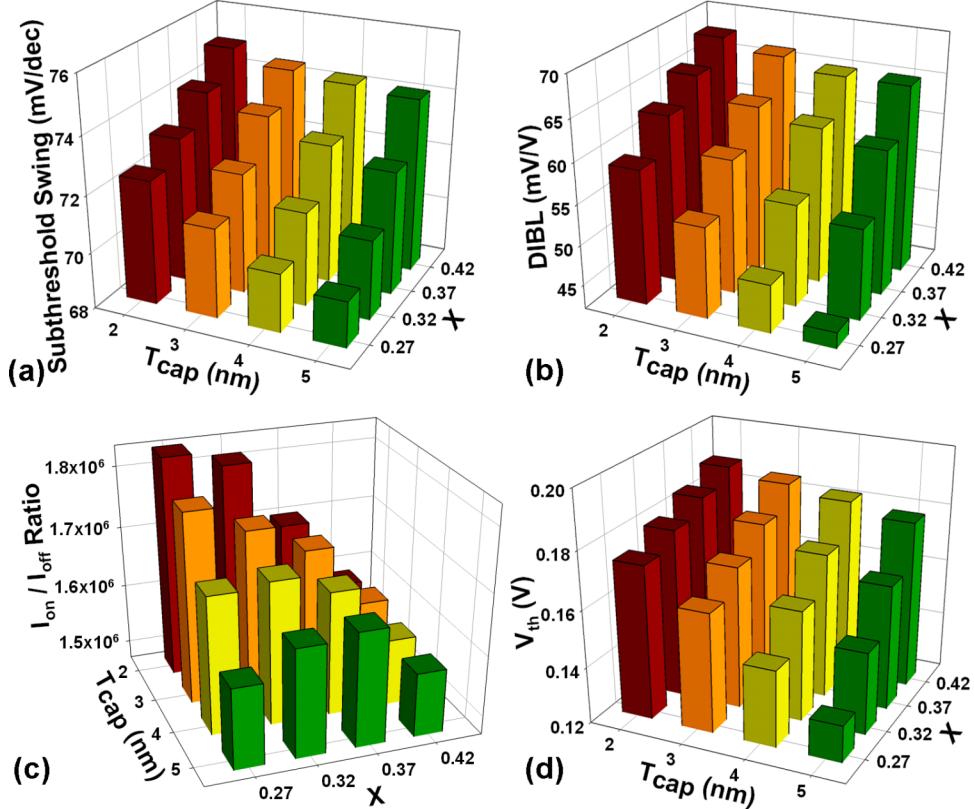

thereby reducing the impact of SCEs. Thus, to suggest the optimal design of channel capping layer, we plot the SS, DIBL,  $I_{on}/I_{off}$  and  $V_{th}$  versus the  $x$  and  $T_{cap}$  to observe the trends, as shown in Fig. 9. Both SS and DIBL decrease with  $T_{cap}$  increasing and  $x$  decreasing, as plotted in Figs. 9(a)-9(b). However, although the on-state current increases due to small band gap and high mobility, the off-state current also increases; thereby, a trade-off exists for the on-/off-state current ratio, as shown

FIG. 9. Plots of (a) SS, (b) DIBL, (c)  $I_{on}/I_{off}$  ratio, and (d)  $V_{th}$  versus the  $x$  and  $T_{cap}$ , respectively. Increasing  $T_{cap}$  and decreasing  $x$  of  $In_{1-x}Ga_xAs$  will reduce the  $V_{th}$  and improve the SS and DIBL; however, there is a trade-off for the variation of  $I_{on}/I_{off}$  ratio.

in Fig. 9(c). Finally, if a  $V_{th}$  of 160 mV is considered for high-performance device applications, a 4-nm thickness of  $In_{1-x}Ga_xAs$  channel capping layer with  $x = 0.32$  could be used accordingly.

Under the optimized parameters above, as shown in Fig. 2, the devices with trapezoidal-shaped channels where the channel fin angle varying from  $70^\circ$  to  $90^\circ$  are simulated. We calibrate all simulation cases having the same threshold voltage to explore the characteristic degradations. Table IV lists the extracted values of  $I_{on}$ ,  $I_{off}$ ,  $I_{on}/I_{off}$ , SS, and DIBL with different channel fin angles and the same  $V_{th}$  which equals to 160 mV. As channel fin angle decreases, the on-state current density decreases owing to fewer electrons to be inverted in the bottom channel. The on-off-state current ratio also decreases with angle decreasing due to decreasing of on-state current and increasing of off-state current. Because we fix the top-fin width at 14 nm, when we decrease the channel fin angle, the bottom-fin width will increase. The region of bottom fin increasing causes the worse gate control over the channel. Therefore, the smaller the channel fin angle is, the less the SCEs can be suppressed. Notably, the critical angle for the case of  $SS < 75$  mV/dec and  $DIBL < 75$  mV/V is around  $80^\circ$ , as summarized in Tab. IV.

TABLE IV. Characteristics with respect to different channel fin angles.

| Channel fin angle | $I_{on}$ (A/ $\mu$ m) | $I_{off}$ (A/ $\mu$ m) | $I_{on}/I_{off}$   | SS (mV/dec) | DIBL (mV/V) |

|-------------------|-----------------------|------------------------|--------------------|-------------|-------------|

| $70^\circ$        | $1.58 \times 10^{-4}$ | $3.32 \times 10^{-10}$ | $4.74 \times 10^5$ | 79.58       | 92          |

| $75^\circ$        | $1.94 \times 10^{-4}$ | $2.85 \times 10^{-10}$ | $6.83 \times 10^5$ | 77.60       | 82.67       |

| $80^\circ$        | $2.11 \times 10^{-4}$ | $2.45 \times 10^{-10}$ | $8.59 \times 10^5$ | 75.78       | 74.67       |

| $85^\circ$        | $2.45 \times 10^{-4}$ | $2.43 \times 10^{-10}$ | $1.01 \times 10^6$ | 73.72       | 65.33       |

| $90^\circ$        | $2.49 \times 10^{-4}$ | $1.46 \times 10^{-10}$ | $1.71 \times 10^6$ | 71.33       | 54.67       |

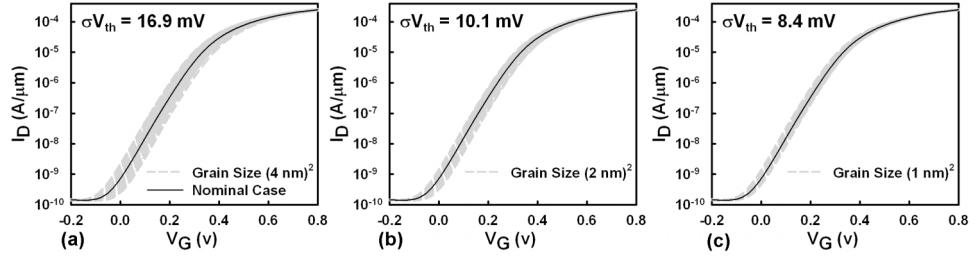

FIG. 10. (a)–(c) The fluctuation of drain currents with respect to different grain sizes. In the subthreshold region, the fluctuation is the largest due to being greatly affected with potential barrier.

Figures 10(a)–10(c) show the fluctuation of drain currents with respect to different sizes of metal grain for the device with an ideal channel fin (i.e., fin angle = 90°). When we apply negative bias voltage to the device ( $V_G = -0.2$  V), holes will accumulate at the channel thereby reducing the effect of external electric field on the inside (so-called the screening effect); hence, the fluctuation of  $I_{off}$  is small (its magnitude of normalized fluctuations < 2%) for all cases of different grain sizes. In the subthreshold region, the gate voltage is small below the threshold voltage, so electrons are difficult to go through the channel and will be greatly affected with potential barrier. For the case of  $4 \times 4 \text{ nm}^2$  grain size, the magnitude of surface potential fluctuation is large and is governed by local work function which results in significant fluctuation of subthreshold region; for example, the normalized  $\sigma I_{off}$  is about 50%. As we applying large gate voltage above the threshold voltage, inversion charges will fill the interface state of the channel and enhance the electron's screening effect. As shown in Fig. 10 and Fig. 12, the value of normalized  $\sigma V_{th}$  is reduced from 10.56% to 5.25% when the grain size is reduced from  $4 \times 4$  to  $1 \times 1 \text{ nm}^2$ . Thus, when  $V_G = 0.8$  V, the fluctuation of  $I_{on}$  is suppressed and

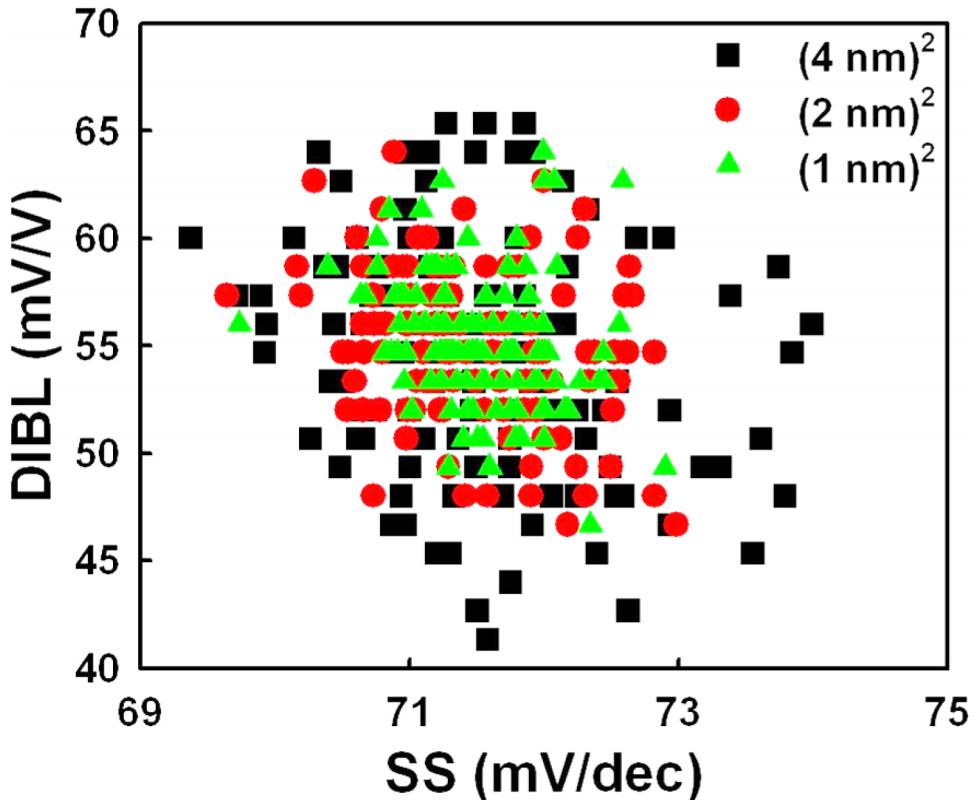

FIG. 11. The scatter plot of DIBL versus SS. The distribution region of  $4 \times 4 \text{ nm}^2$  grain size is the largest.

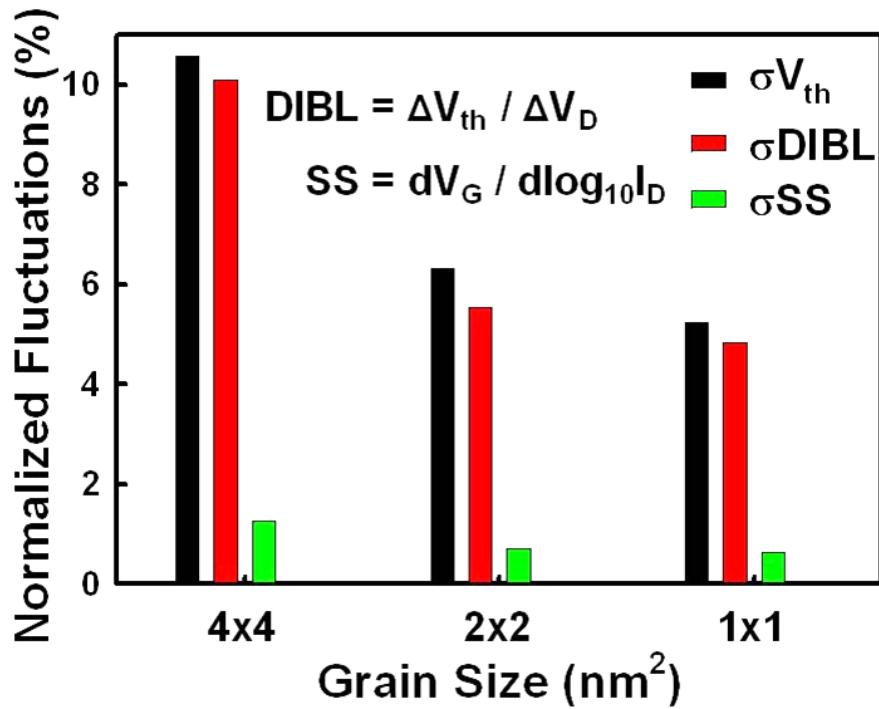

FIG. 12. The bar charts for standard deviations of  $V_{\text{th}}$ , DIBL and SS. All are normalized by the values of nominal case. As the grain size decreases, the fluctuation decreases.

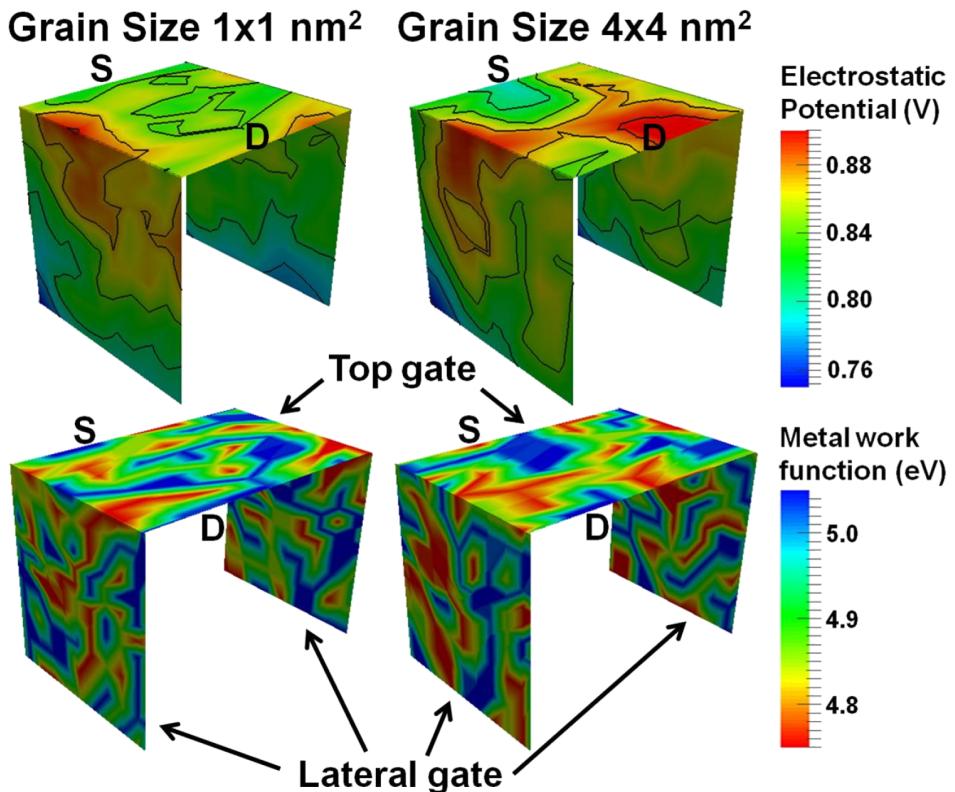

FIG. 13. The electrostatic potential with different grain sizes and the corresponding metal work function distribution under the same bias condition ( $V_G = V_D = 0.8$  V).  $1 \times 1 \text{ nm}^2$  grain size has the smaller difference drop of the surface potentials.

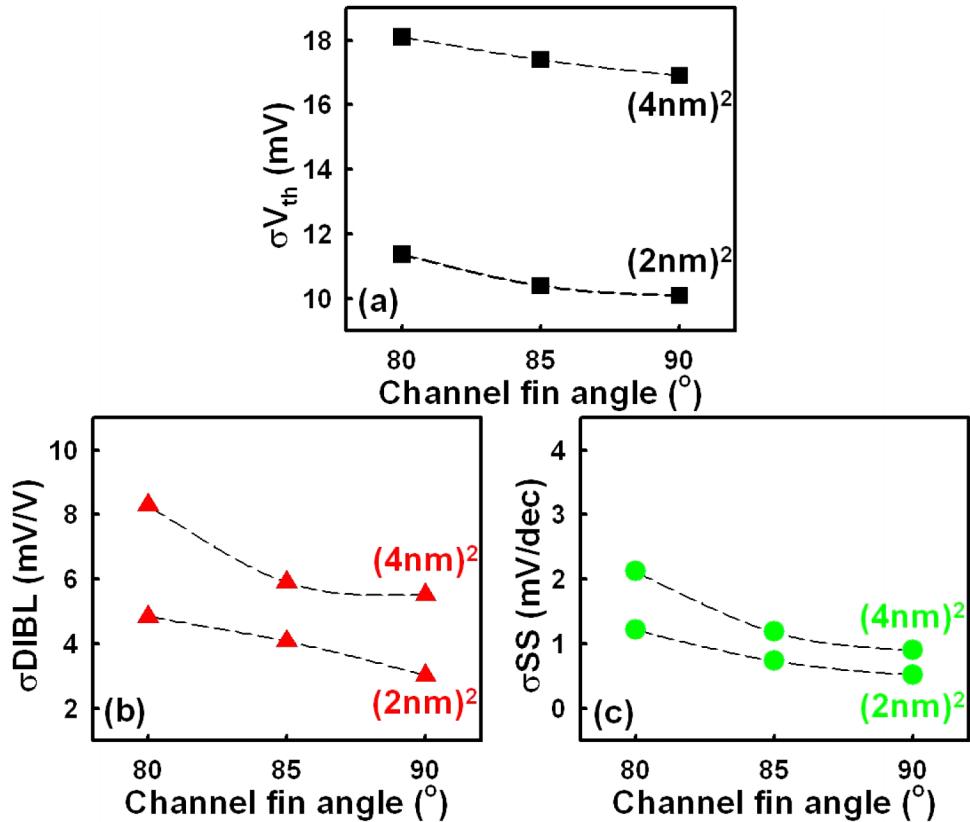

FIG. 14. Plots of the standard deviations of (a)  $V_{th}$ , (b) DIBL and (c) SS. The upper lines are for  $4 \times 4 \text{ nm}^2$  grain size, and the lower lines are for  $2 \times 2 \text{ nm}^2$  grain size. To maintain small fluctuation of  $V_{th}$ , DIBL and SS (for example, the normalized  $\sigma V_{th}$ ,  $\sigma SS$  and  $\sigma DIBL$  are within 7%), the channel fin angle should be between  $85^\circ$  and  $90^\circ$ .

the normalized fluctuation is within 3% owing to strongest screening effect. The  $\sigma V_{th}$  of  $4 \times 4 \text{ nm}^2$  grain size is greater than twice the  $\sigma V_{th}$  of  $1 \times 1 \text{ nm}^2$  grain size. Because the  $I_{off}$  ( $V_G = 0 \text{ V}$ ) has an exponentially increasing relation with  $V_{th}$ , the increment of  $\sigma I_{off}$  is more significant with grain size increasing. Figure 11 shows the distribution of DIBL versus SS with respect to different grain sizes. The random distribution region of  $4 \times 4 \text{ nm}^2$  grain size is the largest among three different grain sizes, so the large size of metal grain will cause serious characteristic fluctuation. Furthermore, from Fig. 11, we can see that DIBL is more sensitive to the variation of metal grain size. The distribution of metal work function will strongly affect the electrostatic potential of the channel, and the variation of potential in the channel even directly decides the magnitude of threshold voltage. Therefore, DIBL's variation can significantly reflect the degree of WKF. Then, the bar charts for the normalized standard deviation of  $V_{th}$ , DIBL, and SS ( $\sigma V_{th}$ ,  $\sigma DIBL$ , and  $\sigma SS$ ) are shown in Fig. 12. They are all normalized by their values of nominal case. The  $\sigma SS$  is quite small that shows a stable switching characteristic. There is a significant reduction on the  $\sigma DIBL$  when the size of metal grain is reduced from  $4 \times 4$  to  $2 \times 2 \text{ nm}^2$ . However, the difference of standard deviation between the cases of  $2 \times 2$  and  $1 \times 1 \text{ nm}^2$  is small. To clarify it, as the grain size decreases, as shown in Fig. 13, the variation of surface potential of  $1 \times 1 \text{ nm}^2$  grain becomes smoother and relatively has the smaller potential difference (the maximum potential difference on the top fin is about 80 mV), compared with the case of  $4 \times 4 \text{ nm}^2$  grain (its maximum difference is 130 mV) thereby reducing the impact of fluctuation. From a device fabrication point of view, metal deposition at a low temperature or adding composite materials could be considered to obtain small size of metal grains.

We further explore the magnitude of WKF with respect to channel fin angles varying from  $80^\circ$  to  $90^\circ$ , according to the discussion above. As shown in Fig. 14, the magnitudes of  $\sigma V_{th}$ ,  $\sigma DIBL$ , and  $\sigma SS$  increase with decreasing the channel fin angle, and the fluctuations are more obvious from  $85^\circ$

TABLE V. Comparison of recent works about InGaAs channel.

|                          | Ref. 44                        | Ref. 41                      | Ref. 41            | Ref. 26           | In this work              |

|--------------------------|--------------------------------|------------------------------|--------------------|-------------------|---------------------------|

| Structure                | QWFET                          | MOSFET                       | MOSFET             | FinFET            | Trigate MOSFET            |

| Channel                  | InGaAs with InP layer above it | InGaAs with Barrier above it | InGaAs             | InGaAs            | InGaAs with capping layer |

| L <sub>g</sub> (nm)      | 75                             | 40                           | 40                 | 14                | 14                        |

| V <sub>DD</sub> (V)      | 0.5                            | 1.0                          | 1.0                | 0.6               | 0.8                       |

| V <sub>th</sub> (V)      | 0.2 <sup>a</sup>               | -0.3                         | -0.01              | 0.2               | 0.16                      |

| I <sub>on</sub> (mA/μm)  | 0.49                           | 0.11 <sup>b</sup>            | 0.045 <sup>a</sup> | 0.35 <sup>b</sup> | 0.249                     |

| I <sub>off</sub> (nA/μm) | 30 <sup>a</sup>                | <sup>b</sup>                 | <sup>b</sup>       | 0.4 <sup>a</sup>  | 0.146                     |

| g <sub>m</sub> (mS/μm)   | 1.75                           | 0.3 <sup>a</sup>             | 0.15 <sup>a</sup>  | <sup>b</sup>      | 0.6248                    |

| f <sub>T</sub> (GHz)     | <sup>b</sup>                   | 24 <sup>a</sup>              | 11 <sup>a</sup>    | <sup>b</sup>      | 282.67                    |

| SS (mV/dec)              | 90 <sup>a</sup>                | <sup>b</sup>                 | <sup>b</sup>       | 70                | 71                        |

| DIBL (mV/V)              | <sup>b</sup>                   | <sup>b</sup>                 | <sup>b</sup>       | 37                | 54                        |

| σV <sub>th</sub> (mV)    | <sup>b</sup>                   | <sup>b</sup>                 | <sup>b</sup>       | 68 <sup>a</sup>   | 12.2                      |

| σSS (mV/dec)             | <sup>b</sup>                   | <sup>b</sup>                 | <sup>b</sup>       | 1.0               | 0.95                      |

| σDIBL (mV/V)             | <sup>b</sup>                   | <sup>b</sup>                 | <sup>b</sup>       | <sup>b</sup>      | 5.5                       |

<sup>a</sup>Estimated from the figures.<sup>b</sup>Not available in the work.

to 80°. By normalizing these fluctuations to the value of nominal case with channel fin angle of 90°, we find that the change of σV<sub>th</sub> of 4x4 nm<sup>2</sup> metal grain is larger than 10% for all the channel fin angles, as shown in Fig. 14(a), so it will not be suitable for device application if the averaged grain size is about 4x4 nm<sup>2</sup>. For the case of the grain size below 4x4 nm<sup>2</sup>, such as the 2x2 nm<sup>2</sup> grain size, the change of σDIBL is still large for the channel fin angle near 80°. Hence, as shown in Figs. 14(b) and 14(c), to suppress the fluctuation of SCEs (both the normalized σSS and σDIBL are with 7%) induced by the WKF, the device with vertical channel of channel fin angle between 85° and 90° could be adopted.

#### IV. CONCLUSIONS

In summary, we have studied the impact of T<sub>cap</sub> and x of In<sub>1-x</sub>Ga<sub>x</sub>As capping layer on 14-nm In<sub>1-x</sub>Ga<sub>x</sub>As / In<sub>0.53</sub>Ga<sub>0.47</sub>As / In<sub>0.52</sub>Al<sub>0.48</sub>As / InP trigate MOSFET. For the given specifications of SS < 72 mV/dec, DIBL < 55 mV/V, and I<sub>on</sub>/I<sub>off</sub> > 1.7x10<sup>6</sup> with V<sub>th</sub> = 160 mV, the device with a 4-nm-thick In<sub>0.68</sub>Ga<sub>0.32</sub>As channel capping layer can provide optimal characteristic for high-performance device applications. For the optimized device configuration, the simulation results suggest that the smaller the grain size is, the more the WKF can be suppressed. As a result, to effectively suppress the WKF-induced DC characteristic fluctuation, the averaged grain size should be smaller than 4x4 nm<sup>2</sup> and the channel fin angle could be between 85° and 90°.

In Table V, we do compare the recent works about the III-V transistors with various InGaAs channels with our results. We have achieved the larger on/off-state current ratio, the higher cut-off frequency, and the lower standard deviations of SCE parameters. We are currently studying the III-V MOSFET device with high aspect ratio (fin height / fin width) to obtain the better device characteristics including fluctuation suppression.

#### ACKNOWLEDGMENTS

This work was supported in part by Ministry of Science and Technology (MOST), Taiwan Under Contract No. MOST-103-2221-E-009-180.

<sup>1</sup> C.-S. Shin, W.-K. Park, SH. Shin, YD. Cho, DH. Ko, T.-W. Kim, D. H. Koh, HM. Kwon, R. J. W. Hill, P. Kirsch, W. Maszara, and D.-H. Kim, VLSI Symp. Tech. Dig. 1 (2014).

<sup>2</sup> J. A. del Alamo, *Nature* **479**, 317 (2011).

<sup>3</sup> S.-H. Chen, W.-S. Liao, H.-C. Yang, S.-J. Wang, Y.-G. Liaw, H. Wang, H. Gu, and M.-C. Wang, *Nanoscale Res. Lett.* **7**, 431 (2012).

<sup>4</sup> J. P. Colinge, A. Krantib, R. Yanb, I. Ferainb, N. D. Akhavanb, P. Razavic, C.-W. Leec, R. Yud, and C. Colinge, *ECS Trans.* **35**, 63 (2011).

<sup>5</sup> J. H. Seo, S. Cho, and I. M. Kang, *Semicond. Sci. Technol.* **28**, 105007 (2013).

<sup>6</sup> I.-H. Ahn and H. Joung, *Jpn. J. Appl. Phys.* **49**, 084303 (2010).

<sup>7</sup> D.-H. Kim, T.-W. Kim, R.H. Baek, P. D. Kirsch, W. Maszara, J. A. del Alamo, D. A. Antoniadis, M. Urteaga, B. Brar, H.M. Kwon, C.-S. Shin, W.-K. Park, Y.-D. Cho, SH. Shin, DH. Ko, and K.-S. Seo, *IEDM Tech. Dig.* 25.2.1 (2014).

<sup>8</sup> Y. Takano, K. Kobayashi, T. Uraniishi, and S. Fuke, *Jpn. J. Appl. Phys.* **49**, 105502 (2010).

<sup>9</sup> H.-C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y.-C. Yeo, *IEEE Electron Device Lett.* **32**, 146 (2011).

<sup>10</sup> Y. Li and W.-H. Chen, *J. Comput. Electron.* **5**, 255 (2006).

<sup>11</sup> F. Xue, H. Zhao, Y.-T. Chen, Y. Wang, F. Zhou, and J. C. Lee, *Appl. Phys. Lett.* **99**, 033507 (2011).

<sup>12</sup> C. Fiegn, Y. Yang, E. Sangiorgi, and A. G. O'Neill, *IEEE Trans. Electron Devices* **55**, 233 (2008).

<sup>13</sup> X. Xu, R. Wang, R. Huang, J. Zhuge, G. Chen, Xing Zhang, and Y. Wang, *IEEE Trans. Electron Devices* **55**, 3246 (2008).

<sup>14</sup> Y. Li, H. M. Chou, and J. W. Lee, *IEEE Trans. Nanotechnol.* **4**, 510 (2005).

<sup>15</sup> Y. Li and C.-H. Hwang, *Jpn. J. Appl. Phys.* **47**, 2580 (2008).

<sup>16</sup> Y. Li and C.-H. Hwang, *Microelectron. Eng.* **84**, 2093 (2007).

<sup>17</sup> Y. Li, C.-H. Hwang, and H.-W. Cheng, *Microelectron. Eng.* **86**, 277 (2009).

<sup>18</sup> Y. Li, H.-W. Chenga, and M.-H. Han, *Comput. Phys. Commun.* **182**, 96 (2011).

<sup>19</sup> Y. Li, C.-H. Hwang, and M.-H. Han, *Nanotechnology* **21**, 095203 (2010).

<sup>20</sup> H. F. Dadgour, K. Endo, V. K. De, and K. Banerjee, *IEEE Trans. Electron Devices* **57**, 2504 (2010).

<sup>21</sup> H. F. Dadgour and K. Endo, *IEEE Trans. Electron Devices* **57**, 2515 (2010).

<sup>22</sup> J. Hicks, D. Bergstrom, M. Hattendorf, J. Jopling, J. Maiz, S. Pae, C. Prasad, and J. Wiedemer, *Intel Technology Journal* **12**, 131 (2008).

<sup>23</sup> M. M. Hussain, M. A. Quevedo-Lopez, H. N. Alshareef, H. C. Wen, D. Larison, B. Gnade, and M. El-Bouanani, *Semicond. Sci. Technol.* **21**, 1437 (2006).

<sup>24</sup> H.-W. Cheng, F.-H. Li, M.-H. Han, C.-Y. Yiu, C.-H. Yu, K.-F. Lee, and Y. Li, *IEDM Tech. Dig.* **379** (2010).

<sup>25</sup> J. L. Heu, Y. Setsuhara, I. Shimizu, and S. Miyake, *Surface and Coatings Tech.* **137**, 38 (2001).

<sup>26</sup> N. Seoane, G. Indalecio, E. Comesañ, M. Aldegunde, A. J. García-Loureiro, and K. Kalna, *IEEE Trans. Electron Devices* **61**, 466 (2014).

<sup>27</sup> J. Mohseni and J. D. Meindl, *IEEE Green Technol. Conf.* **204** (2013).

<sup>28</sup> M.-D. Ko, C.-W. Sohn, C.-K. Baek, and Y.-H. Jeong, *IEEE Trans. Electron Devices* **60**, 2721 (2013).

<sup>29</sup> Y. Li and C.-H. Hwang, *J. Appl. Phys.* **102**, 084509 (2007).

<sup>30</sup> R. E. Nahory, M. A. Pollack, W. D. Johnston, Jr., and R. L. Barns, *Appl. Phys. Lett.* **33**, 659 (1978).

<sup>31</sup> C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, *IEEE Transactions on CAD* **7**, 1164V1171 (1988).

<sup>32</sup> C. Canali, G. Majni, R. Minder, and G. Ottaviani, *IEEE Trans. Electron Devices* **22**, 1045V1047 (1975).

<sup>33</sup> F. Xue, A. Jiang, H. Zhao, Y.-T. Chen, Y. Wang, F. Zhou, and J. Lee, *IEEE Electron Device Lett.* **33**, 32 (2012).

<sup>34</sup> N. M. Shrestha, Y. Li, and E. Y. Chang, *Jpn. J. Appl. Phys.* **53**, 04EF08 (2014).

<sup>35</sup> K. C. Sahoo, C.-I. Kuo, Y. Li, and E. Y. Chang, *IEEE Trans. Electron Devices* **57**, 2594 (2010).

<sup>36</sup> Y. Li, S. M. Sze, and T.-S. Chao, *Eng. Comput.* **18**, 124 (2002).

<sup>37</sup> T.-W. Tang, X. Wang, and Y. Li, *J. Comput. Electron.* **1**, 389 (2002).

<sup>38</sup> Y. Li and S.-M. Yu, *Comput. Phys. Commun.* **169**, 309 (2005).

<sup>39</sup> B. Murugan, S. K. Saha, and R. Venkat, *J. Semicond. Tech. Sci.* **7**, 51 (2007).

<sup>40</sup> Y. Li, C.-Y. Chen, and Y.-Y. Chen, *Int. J. of Nanotechnology* **11**, 1029 (2014).

<sup>41</sup> S. Tewari, A. Biswas, and A. Mallik, *IEEE Trans. Electron Devices* **60**, 1584 (2013).

<sup>42</sup> V. W. L. Chin and T. L. Tansley, *Solid-State Electron.* **34**, 1055 (1991).

<sup>43</sup> Y. Li and C.-H. Hwang, *IEEE Trans. Microw. Theory Tech.* **56**, 2726 (2008).

<sup>44</sup> M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, *IEDM Tech. Dig.* 13.1.1 (2009).