# The CMP Process and Cleaning Solution for Planarization of Strain-Relaxed SiGe Virtual Substrates in MOSFET Applications

Ming-Shan Shieh, az Pang-Shiu Chen, M.-J. Tsai, and Tan Fu Lei

<sup>a</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, HsinChu. Taiwan

The effects of different polishing pads and slurry solid contents on the SiGe chemical mechanical polish (CMP) process were investigated. By optimizing the polishing conditions, a smooth strained-Si surface on a flattened  $Si_{0.8}Ge_{0.2}$  buffer layer of 0.6 nm can be achieved. The novel cleaning solutions with various surfactants and chelating agents for post-CMP SiGe were studied. There was about 10% current enhancement of the optimal cleaning conditions, showing high performance in particle removal, metallic cleaning, and electrical characteristics.

© 2005 The Electrochemical Society. [DOI: 10.1149/1.2149291] All rights reserved.

Manuscript submitted February 22, 2005; revised manuscript received October 11, 2005. Available electronically December 30, 2005.

Strained silicon on relaxed silicon–germanium (SiGe) substrates is a promising candidate for transistor performance enhancement. Strain splits the degeneracy in the conduction and valence bands of Si, enhances the transport properties of electrons and holes, and provides transistor speed enhancement. High-quality strainedrelaxed buffer layers are required for high-performance devices, but the relaxed SiGe layers tend to have threading dislocations and rough surfaces. Several methods such as the graded buffer layers and low-temperature buffer<sup>4</sup> methods have been studied. Relaxation during the growth of the visual substrate results in a crosshatch (misfit dislocations) which increases surface roughness. The chemical mechanical polishing (CMP) process has become the mainstream of global planarization techniques in fabrication of deep submicrometer integrated circuits. To reduce surface roughness, the CMP process is being applied to the grown layers. A few researchers have introduced it into polishing SiGe buffer layers. <sup>5-9</sup> The high crystalline quality of the regrowth layer with a smooth interface makes it possible to fabricate high-performance SiGe devices with low surface roughness scattering. However, the wafer surface after the CMP process is seriously contaminated with particles and metallic impurities from the polishing slurry. In addition, the metallic impurities induce many crystal defects in the Si wafers during thermal processing, <sup>10</sup> and planarized SiGe buffer layer roughness is increased due to the etching effect. <sup>11</sup> Our previous studies have found that the novel post-CMP cleaning solution can significantly reduce contamination retention. <sup>12,13</sup> The surfactant tetramethylammonium hydroxide (TMAH) and the chelating agent ethylenediaminetetraacetic acid (EDTA) were used to enhance the removal efficiency of particle and metal impurities. We found that removal efficiency of particle and metallic impurities was enhanced by post-poly-Si CMP cleaning. The electrical characteristics can be also improved by the novel post-CMP solution. In this paper, we applied the post-CMP cleaning on SiGe buffer layers. Furthermore, the capacitor and metal oxide semiconductor field effect transistor (MOSFET) electrical characteristics of strained-Si regrowth on the substrate treated with various solutions were also evaluated.

## Experimental

The SiGe epitaxy layers on 6-in.-diam Si(100) substrates were prepared by ultrahigh-vacuum chemical vapor deposition (UHV-CVD). The novel relaxed 700-nm-thick SiGe buffer with a 50-nm-thick Si inserted layer was used in this work. <sup>14</sup> For measuring the SiGe layer thickness, we used the electron cyclotron resonance (ECR) etcher to form a trench on the SiGe buffer layer and a surface profiler to measure the height of the trench in order to moni-

tor thickness. The CMP experiment was carried out on a Westech model 372M CMP processor consisting of a Rodel IC 1400 pad and Politex buffering pad with diluted CABOT SS-25 slurry. The solid content of the experimental slurry was diluted by deionized (DI) water at volume ratios of 1:9 and 1:18. The downforce pressure was fixed at 3 psi for studying the time effects. In the following, it was varied from 3 to 7 psi for 1 min to investigate the effects of the downforce pressure and removal rate. Surface morphologies were characterized by atomic force microscopy (AFM).

In the post-CMP cleaning experiment, wafers were sprayed with diluted NH<sub>4</sub>OH solution with megasonic, followed by dispensing the cleaning solution with a poly(vinyl alcohol) (PVA) brush after the CMP process. There were four kinds of cleaning solution separated as following: (SC1) diluted 29% NH<sub>4</sub>OH, (SC1 + T) 29% NH<sub>4</sub>OH + 2.38% TMAH (volume ratio to NH<sub>4</sub>OH is 1%), (SC1 + E) 29% NH<sub>4</sub>OH + EDTA (100 ppm), and (SC1 + TE) 29%  $NH_4OH + 2.38\% + TMAH (1\%) + EDTA (100 ppm)$ . The particle number was counted by the TENCOR surface scan model 4500 system. Total refection X-ray fluorescence spectrometry (TXRF), Atomika model 8030W, was used to determine the metallic impurity. After the post-CMP cleaning process, 20-nm strained-Si film was form on the CMP SiGe buffer layer. For verifying the clean solution effect, a 20-nm TEOS oxide formed a capacitor and MOS-FET structures. The electrical properties of the capacitor, i.e., current-voltage and time-dependent dielectric breakdown (TDDB) characteristics, were measured using the Hewlett-Packard (HP) 4156 semiconductor parameter analyzer.

### **Results and Discussion**

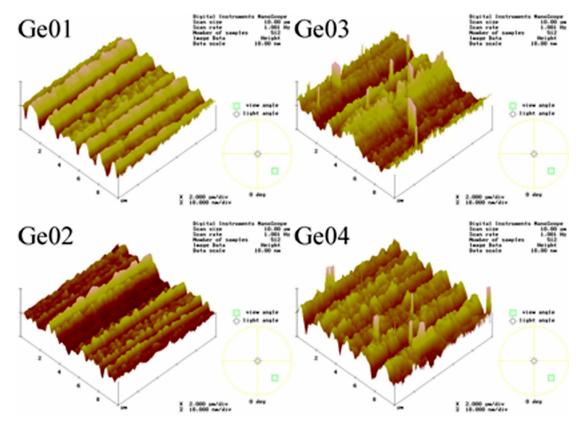

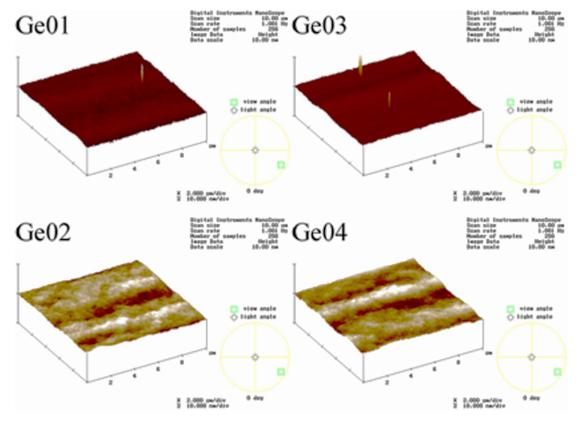

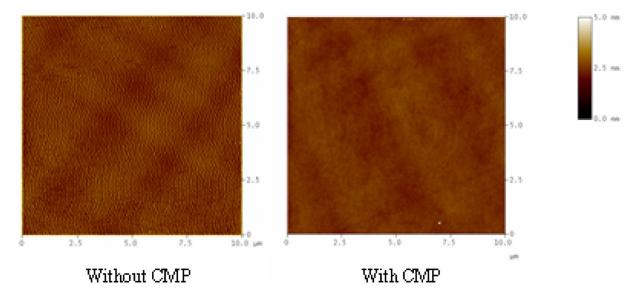

Various slurry solids containing different pad properties are shown in Table I. Figures 1 and 2 show the SiGe AFM image of the as-grown buffer layer before and after planarization. There are four kinds of conditions. The effects of polishing pad properties on the

Table I. Different slurry and pad conditions for Ge01, Ge02, Ge03, and Ge04 samples.

| Slurry condition  Pad condition | Slurry : H <sub>2</sub> O<br>1 : 9 | Slurry : H <sub>3</sub> O<br>1 : 18 |

|---------------------------------|------------------------------------|-------------------------------------|

| Politex pad                     | Ge01 (AFM RMS)<br>20.6 Å → 2.52 Å  | Ge03 (AFM RMS)<br>25.3 Å → 3.39 Å   |

| IC1400 pad                      | Ge02 (AFM RMS)<br>22.1 Å → 2.69 Å  | Ge04 (AFM RMS)<br>22.3 Å → 3.59 Å   |

<sup>&</sup>lt;sup>b</sup>Electronics Research and Service Organization, Industrial Technology Research Institute, Hsinchu, Taiwan

<sup>&</sup>lt;sup>z</sup> E-mail: anderson.ee88g@nctu.edu.tw

Figure 1. AFM images of strained-relaxed SiGe buffer layers before CMP processing.

Figure 2. AFM images of strained-relaxed SiGe buffer layers after CMP processing.

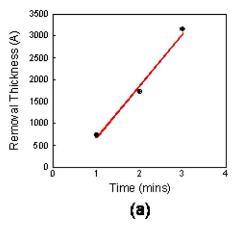

**Figure 3.** Removal rate of (a) time-dependence and (b) pressure-dependence in SiGe layers.

process characteristics were studied. The IC 1400 pad was compared with the Politex polishing pad regarding surface roughness. By polishing with the Politex pad, a better uniformity was achieved. As shown in Fig. 2, Ge01 and Ge03 samples almost have no crosshatch pattern. The softer Politex pad is a composite of the porous polymer and it could have uniformly distributed the polish particles. No differences in the pad influenced the geometry effects, which can be explained with the same near-surface layer affecting the interaction between pad and wafer. The hardness of the IC 1400 allows the material to planarize across wide areas with minimal dishing and good planarity, but the Politex polishing pad improves resilience and compressibility of the pad and enhances global uniformity in the polish removal. For the different solid content, a volume ratio of 1:9 shows better surface morphology in the AFM root-mean-square (rms) results of Table I. In order to have the controllable removal rate, different periods of time from 1 to 3 min in 3 psi are shown in Fig. 3a. The removal rate is a linear distribution time scale, but the time extrapolation is not zero. As we started to polish the surface, a thin oxide covered the SiGe buffer layer and slowed the polish rate. Figure 3b shows that the pressure-dependent removal rate is saturated at a higher pressure. Compared to the conditions of 5 and 7 psi, the 3-psi condition has a higher removal thickness difference. When applied at higher pressure on the exitaxy SiGe surface, it could introduce some mechanical stress on the initial surface. We use a low-pressure condition to avoid the additional stress. The conditions of stable removal rate and smooth surface interface are

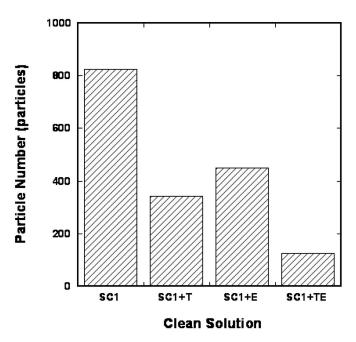

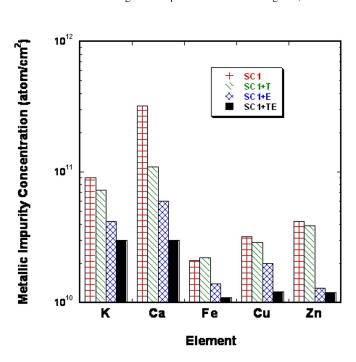

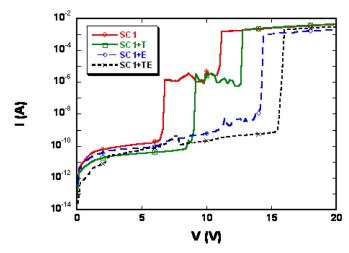

achieved by a Politex pad polish and a 1:9 solid content ratio for 1 min and 3 psi. As Fig. 4 illustrates, the samples with and without the CMP process were followed by strained-Si regrowth. The rms values with and without CMP are 0.6 and 1.8 nm, respectively. The surface roughness and crosshatch pattern were eliminated by CMP. Figure 5 shows residual particles on the post-CMP cleaning surface with different solutions. It is found that the SC1 + TE sample exhibits the highest efficiency. The slight surface etching of the wafer and electrical repulsion between the wafer surface and the particle can enhance removal of particles. It has been shown that the hydrophobic surface resides more heavily on particles on the wafer surface than the hydrophilic surface. <sup>15</sup> Figure 6 shows the metallic impurity concentration measured by TXRF. The metallic contaminants are significantly removed by the SC1 + E and SC1 + TE solution. EDTA can trap the potassium ions to reduce solution ionic strength and enhance the electric double-layer repulsion between the particle and wafer surface. 16 In our previous study, 13 it seems that combination of TMAH and EDTA play important roles in contamination removal and results in the best efficiency. The metallic contaminants are removed significantly, and the chelating agent reacts with metallic ion in the form of a metal-chelating complex. <sup>17,18</sup> In Fig. 7, the current vs electric voltage of the metal oxide semiconductor (MOS) capacitor cleaned by four solutions is shown. The MOS capacitor using SC1 + TE solution depicts the lowest leakage current and highest breakdown voltage among these four samples. It

Figure 4. AFM images of strained-Si surfaces without and with the CMP process. The rms values are 0.6 and 1.8 nm, respectively.

**Figure 5.** Particle residual number on post-CMP cleaning surfaces of SiGe buffer layers in different solutions.

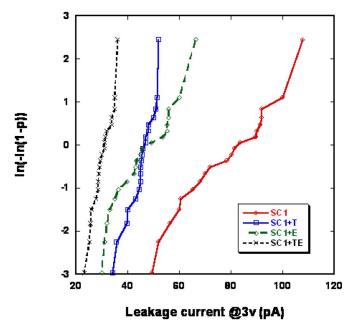

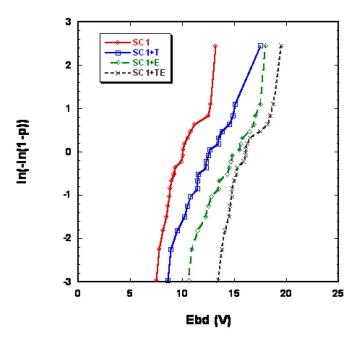

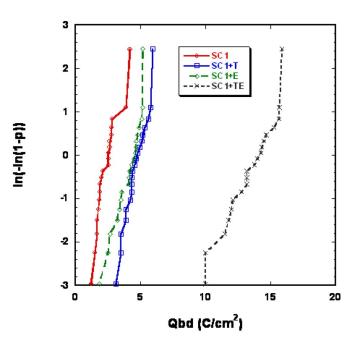

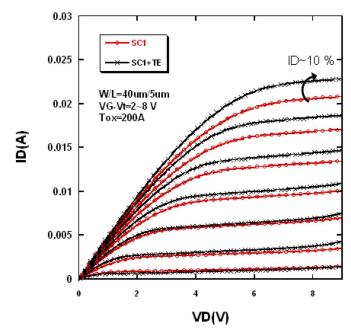

is obviously seen that SC1 and SC1 + T samples exhibit the second breakdown effect, possibly due to the metallic and particle containment shown in Fig. 5 and 6. Figure 8 shows the Weibull plot of leakage current measured at 3 V. The breakdown voltage distribution is shown in Fig. 9. A constant current stressing is used to investigate the gate oxide integration. The charge to breakdown ( $Q_{\rm bd}$ ) measurements were performed on the post-CMP cleaning samples (see Fig. 10). The distribution for solution SC1 + TE shows high  $Q_{\rm bd}$  that can be attributed to efficient removal of the particle and metal contaminations on strained-Si MOS capacitors. We also applied it in MOSFET fabrications. The output characteristics of devices with channel length of 5  $\mu$ m are shown in Fig. 11, and the

**Figure 6.** The metallic contaminant concentration on SiGe buffer layers by TXRF.

**Figure 7.** The current vs voltage characteristic of MOS capacitors with 20 -nm TEOS oxide on the strained Si with different cleaning methods.

drain current increased about 10% between SC1 and SC1 + TE samples. The novel cleaning solutions with TMAH and EDTA showed the improvements which indicated that this solution for post-CMP on SiGe virtual substrates is a critical technique for developing high-performance strained-Si MOSFETs.

#### Conclusions

We have investigated planarization of rough surfaces of strain-relaxed  $\mathrm{Si_{0.8}Ge_{0.2}}$  buffer layers by CMP and post-CMP cleaning. It was found that a softened polish pad can eliminate SiGe surface roughness. The optimum conditions can achieve a strained-Si surface roughness of 0.6 nm. For the post-CMP cleaning process, various cleaning solutions were applied to the SiGe buffer layer. By adding the surfactant (TMAH) and chelating agent (EDTA) into the diluted ammonium solution, removal efficiency of particles and metallic impurities is increased. The electrical performances of capacitors such as breakdown voltage, leakage current, and  $Q_{\rm bd}$  are significantly improved for post-CMP cleaning. Furthermore, the

**Figure 8.** The cumulative distribution of leakage current of MOS capacitors with different cleaning methods.

Figure 9. The breakdown voltage distribution of MOS capacitors.

optimal condition of the SC1 + TE sample increased about 10% in drive current. This post-CMP cleaning process is useful for planarization of strain-relaxed SiGe virtual substrates in MOSFET applications.

## Acknowledgment

This work was supported by the joint project of Electronics Research and Service Organization and the Industrial Technology Re-

**Figure 10.** The charge-to-breakdown of MOS capacitors under constant current stress in four kinds of different solutions.

Figure 11. The 10% current enhancement between SC1 and SC1 + TE samples.

search Institute of Taiwan through contract no. C93079.

National Chiao Tung University assisted in meeting the publication costs of this article.

## References

- J. L. Hoyt, H. M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E. A. Fitzgerald, and D. A. Antoniadis, Tech. Dig. - Int. Electron Devices Meet., 2002, 23.

- B. S. Meyerson, K. J. Uram, and F. K. LeGoues, Appl. Phys. Lett., 53, 2555 (1988).

- P. M. Mooney, J. L. Jordan-Sweet, K. Ismail, J. O. Chu, R. M. Feestra, and F. K. LeGoues, Appl. Phys. Lett., 67, 2373 (1995).

- T. Ueno, T. Irisawa, Y. Shiraki, A. Uedono, and S. Tanigawa, *Thin Solid Films*, 369, 320 (2000).

- K. Sawano, K. Kawaguchi, T. Ueno, S. Koh, K. Nakagawa, and Y. Shiraki, *Mater. Sci. Eng., B*, 89, 406 (2002).

- K. Sawano, K. Arimoto, Y. Hirose, S. Koh, N. Usami, K. Nakagawa, T. Hattori, and Y. Shiraki, J. Cryst. Growth, 251, 693 (2003).

K. Sawano, S. Koh, Y. Shiraki, Y. Hirose, T. Hattori, and K. Nakagawa, Appl. Phys.

- K. Sawano, S. Koh, Y. Shiraki, Y. Hirose, T. Hattori, and K. Nakagawa, *Appl. Phys. Lett.*, 82, 412 (2003).

N. Sugii, D. Hisamoto, K. Washio, N. Yokoyama, and S. Kimura, *IEEE Trans.*

- Electron Devices, 49, 2237 (2002).

M. T. Currie, C. W. Leitz, T. A. Langdo, G. Taraschi, E. A. Fitzgerald, and D. A. Antoniadis, J. Vac. Sci. Technol. B, 19, 2268 (2001).

- Antoniadis, J. Vac. Sci. Technol. B, 19, 2268 (2001).

N. Miyashita, M. Shimomura, Y. Minami, I. Katakabe, H. Nojo, H. Ohashi, and M. Abe, in *Proceedings of ISMIC'96*, p. 161 (1996).

- K. Sawano, K. Kawaguchi, S. Koh, Y. Hirose, T. Hattori, K. Nakagawa, and Y. Shiraki, J. Electrochem. Soc., 150, G376 (2003).

- T. P. Pan, T. F. Lei, T. S. Chao, M. C. Liaw, F. H. Ko, and C. P. Lu, J. Electrochem. Soc., 148, G315 (2001).

- T. P. Pan, T. F. Lei, C. C. Chen, T. S. Chao, M. C. Liaw, W. L. Yang, M. S. Tsai, C. P. Lu, and W. H. Chang, *IEEE Electron Device Lett.*, 21, 338 (2000).

- S. W. Lee, P. S. Chen, M.-J. Tsai, C. T. Chia, C. W. Liu, and L. J. Chen, *Thin Solid Films*, 447–448, 302 (2004).

- 15. W. Kern, *Handbook of Semiconductor Wafer Cleaning Technology*, p. 152, Noyes Publications, Park Ridge, NJ (1993).

- J. M. Steigerwald, S. P. Murarka, and R. J. Gutmann, Chemical Mechanical Planarization of Microelectronic Materials, p. 294, Wiley, New York (1997).

- A. Ringbom, Complexation in Analytical Chemistry, p. 52, Wiley, New York (1963).

- H. Morinaga, , M. Aoki, T. Maeda, , M. Fujisue, H. Tanaka, and M. Toyoda, *Mater. Res. Soc. Symp. Proc.*, 477, 35 (1997).