# A Quantum Trap MONOS Memory Device Using AlN

C. H. Lai, a C. H. Wu, b Albert Chin, a,z S. J. Wang, and S. P. McAlister Chin, a,z

<sup>a</sup>Nano Science Technology Center, Department of Electronics Engineering, National Chiao-Tung University, University System of Taiwan, Hsinchu, Taiwan

<sup>b</sup>Institute of Microelectronics, Department of Electrical Engineering, National Cheng Kung University, Hsinchu 30050, Taiwan

<sup>c</sup>National Research Council of Canada, Ottawa, Canada

We report a  $IrO_2$ -HfAlO-AlN-SiO $_2$ -Si MONOS device that displays excellent characteristics in terms of speed (100  $\mu$ s at  $\pm 13$  V for program/erase) and memory window (3.7 V) at 85 °C operation. This device also shows good 10-year extrapolated data retention with a large 1.9 V window at 85 °C. The achieved performance compares well with the best reported memory device data.

© 2006 The Electrochemical Society. [DOI: 10.1149/1.2208742] All rights reserved.

Manuscript submitted July 19, 2005; revised manuscript received April 12, 2006. Available electronically June 12, 2006.

The [poly-Si/metal]-oxide-nitride-oxide-silicon (SONOS/MONOS) device  $^{1-6}$  is a promising nonvolatile memory suitable for downscaling below 20 nm. Discrete quantum traps are used rather than the continuous charge storage in poly-Si floating gate flash memory, which gives better data retention and is useful for 2 bits/cell. The high density and small size of such traps in SONOS/MONOS may have an advantage over quantum dot memory where the dots are nonuniform and have typical dimensions of  $\sim$ 5 to 10 nm. Goals for improving memory device performance include better program/erase (P/E) speed, memory window, and data retention. A large memory window is important in multilevel data storage, which is beyond the current 2 bits/cell technology.

In this paper, we demonstrate an IrO2-HfAlO-AlN-SiO2-Si MONOS memory device to meet the requirements mentioned above. At an elevated temperature of 85°C, a large memory window of 3.7 V was initially obtained along with a speed of 100  $\mu s$ and ±13 V P/E. The data suggested a 1.9 V window from 10year extrapolated data retention. Good endurance was evident from the small 0.3 V threshold voltage (V<sub>th</sub>) increase, within a 3.7 V memory window, after 10,000 P/E cycles. Therefore, fast 100 µs speed, large memory window, good data retention, and cycling endurance can be simultaneously obtained in the SiO<sub>2</sub>/ AlN/HfAlO/IrO2 memory device. Such excellent device performance is among the best in the literature.<sup>2-4</sup> The good memory device performance is primarily due to the deeper energy charge trapping in the AlN layer, 7-9 which yields a large memory window and good data retention together with low leakage through the thin 2.8 nm SiO<sub>2</sub> barrier. The fast erase speed, which is the bottleneck for P/E and is much slower than the program speed, is due to the high- $\kappa$  property of the AlN ( $\kappa=10)$  trapping layer  $^{7\text{-}9}$  and the HfAlO ( $\kappa = 17$ ) barrier, which gives higher electric field across the SiO<sub>2</sub> tunnel layer. The high work function of 5.1 eV IrO<sub>2</sub> metal-gate<sup>10</sup> also plays an important role in enabling a fast erase function by reducing the leakage current through the thin HfAlO barrier.

## Experimental

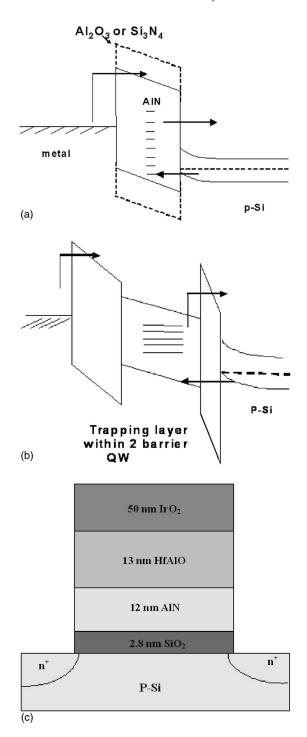

We have studied the trapping capability of various high- $\kappa$  dielectrics such as  $\mathrm{Si}_3\mathrm{N}_4$  and  $\mathrm{AlN}$ . After device isolation, the 16 nm AlN was deposited by physical vapor deposition (PVD). For comparison, the capacitor with the same thickness (16 nm)  $\mathrm{Si}_3\mathrm{N}_4$  was also fabricated. A 400°C anneal under  $\mathrm{N}_2$  ambient was used to reduce the leakage current via defects. After standard process steps the Al-metal/high- $\kappa$ /Si metal—insulator—semiconductor (MIS) capacitors were formed, shown schematically in Fig. 1a. For the

$IrO_2$ –HfAlO–AlN–SiO $_2$ –Si MONOS devices (Fig. 1b), a 2.8 nm thermal SiO $_2$  was first grown at 850°C in dilute O $_2$ .Then a 12 nm AlN trapping layer was deposited by PVD, followed by 13 nm HfAlO deposition by atomic layer chemical vapor deposition (ALCVD), and 50 nm  $IrO_2$  deposition by PVD.  $^{10}$  After standard processing, the MONOS device was created by self-aligned phosphorous ion implantation and 950°C rapid thermal anneal (RTA) activation to form the source/drain (S/D) region of an n-type metal oxide semiconductor field effect transistor (n-MOSFET). The resulting structure is shown in Fig. 1c. The memory devices were characterized by different P/E times, retention tests, and cycling endurance at 25 or 85°C.

## Results and Discussion

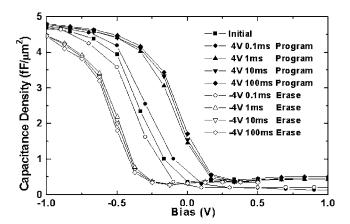

Single trapping layer MIS capacitor.— Figures 2 and 3 show the measured capacitance–voltage (C–V) characteristics of high- $\kappa$  AlN and  $\rm Si_3N_4$  MIS capacitors, respectively, after applying +4 or –4 V for 0.1–100 ms. For AlN MIS devices the memory function was obtained from the positive and negative shifts of the C–V curves, corresponding to the different polarities of the applied voltages. The shift of C–V curves saturates as the P/E time is increased >1 ms, suggesting a 1 ms switching time. A memory window of 0.5 V was obtained at  $\pm 4$  V P/E for 1 ms, which can be increased using the MONOS structure with additional quantum well (QW) confinement from the two barriers, as depicted in Fig. 1b.

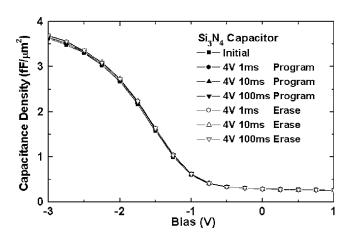

In contrast, an Al/Si<sub>3</sub>N<sub>4</sub>/Si MIS capacitor, fabricated with the same thermal cycle process as the AlN MIS device, showed only a few millivolt changes in the C–V curves. It is well known that good memory functions can be obtained in Si<sub>3</sub>N<sub>4</sub> MONOS devices through additional programmed charge confinement within the Si<sub>3</sub>N<sub>4</sub> QW formed by two SiO<sub>2</sub> barriers. Therefore the poor memory capability in the single-layer Si<sub>3</sub>N<sub>4</sub> MIS capacitor may be due to the charge leakage out to the metal–gate and Si substrate, after removing the applied voltages. Note that the equivalent oxide thickness (EOT) of the Si<sub>3</sub>N<sub>4</sub> is larger than for the AlN layer due to the smaller  $\kappa$  value and capacitance density (3.5 fF/ $\mu$ m² vs 4.5 fF/ $\mu$ m² for AlN capacitor). This suggests that the traps in Si<sub>3</sub>N<sub>4</sub> are either shallower, in energy, or lower in density than those for AlN but are still the most important properties for the trapping layer in a MONOS device.

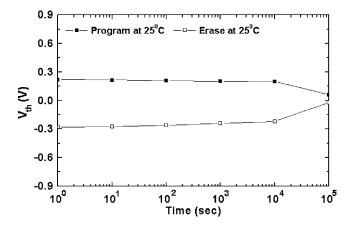

We also measured the retention characteristics of a single-layer AlN MIS capacitor. As shown in Fig. 4, a good retention time of 10,000 s is shown with a small change in the memory window, after the 1 ms  $\pm 4$  V P/E. This simple AlN capacitor, fabricated with only a 400°C thermal budget, can be integrated into very large scale integration (VLSI) as a backend process. The high capacitance density of  $\sim 5$  fF/ $\mu m^2$  is useful for analog/radio frequency (r/f) applications and is  $\sim 5$  times larger than capacitors currently provided in

z E-mail: achin@cc.nctu.edu.tw

**Figure 1.** Schematic structures for (a) a metal-gate/high- $\kappa$ /Si MIS capacitor and (b) an IrO<sub>2</sub>–HfAlO–AlN–SiO<sub>2</sub>–Si MONOS device with discrete quantum traps.

an integrated circuit (IC) foundry. The  $10^4\ s$  retention time in the high-density AlN capacitors can be used as devices intermediate between static and dynamic RAM.

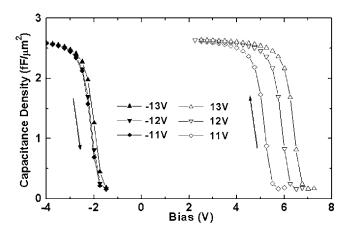

MONOS memory device.— To increase the memory window and data retention further, a MONOS device structure is required, having additional quantum confinement within high energy barriers as in Fig. 1b. Figure 5 shows the C–V hysteresis characteristics of the MONOS capacitor. A large memory window of 7–9 V was obtained with applied P/E voltages of ±11 to ±13 V. Such a memory window is significantly larger than that of a single-layer AlN MIS device due

**Figure 2.** C–V characteristics of an Al/AlN/Si MIS capacitor. The memory device function is obtained by applying program and erase voltages of +4 and –4 V, respectively.

**Figure 3.** C–V characteristics of an Al/Si $_3$ N $_4$ /Si MIS capacitor. In contrast, a small C–V shift was shown after applying voltages of +4 and –4 V to an Al/AlN/Si device, which suggests shallower trap energy or lower trap density in the Si $_3$ N $_4$  MIS device.

Figure 4. The retention characteristics of an Al/AlN/Si MIS capacitor obtained from C–V curves. The data was measured after  $\pm 4$  V P/E voltages were applied for 1 ms.

**Figure 5.** The C–V hysteresis characteristics of an IrO<sub>2</sub>–HfAlO–AlN–SiO<sub>2</sub>–Si MONOS memory device.

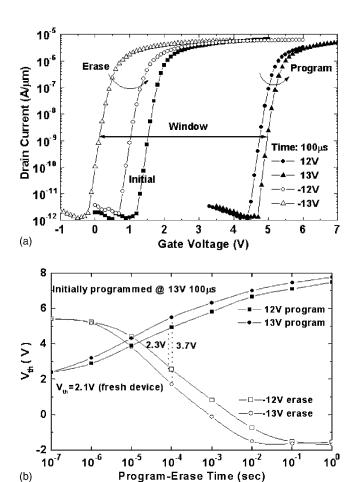

to the charge confinement in the AlN traps within the HfAlO and  ${\rm SiO_2}$  barriers. In addition, use of a thinner 12 nm AlN trapping layer in MONOS memory devices is to give a smaller EOT and lower operation voltage. Figures 6a and b show the  $I_{\rm d}{-}V_{\rm g}$  characteristics of a MONOS device with 10  $\mu$ m gate length and the threshold voltage ( $V_{\rm th}$ ) as a function of P/E time from the peak  $g_{\rm m}$  of the linear  $I_{\rm d}{-}V_{\rm g}$ , respectively. Therelative large initial  $V_{\rm th}$  of 2.1 V may be due to intrinsic properties or process-induced charges in the AlN layer,

**Figure 6.** (a) The measured  $I_{\rm d}$ – $V_{\rm g}$  characteristics of a MONOS device and (b) the detailed threshold voltage ( $V_{\rm th}$ ) program and erase characteristics from the peak  $g_{\rm m}$  of an  $I_{\rm d}$ – $V_{\rm g}$  plot.

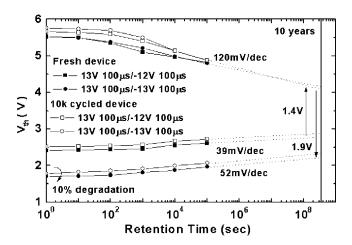

Figure 7. The data retention of fresh and 10 K-cycled AlN MONOS memory devices at  $85\,^{\circ}\text{C}$ .

because  $V_{th}$  of an n-MOSFET is only 0.2 V.  $V_{th}$  changes almost linearly with increasing program and erase times, although the  $V_{th}$  saturates when the erase time reaches 10–100 ms. This is due to the limited charge storage for the initial programming at 13 V for 100  $\mu$ s. The large memory window of 2.3 or 3.7 V appears when the P/E time reaches 100  $\mu$ s at  $\pm$ 12 or  $\pm$ 13 V. This is comparable with the best erase times in the literature,  $^{2-4}$  and is important because of the large memory window and low P/E voltage. The operation speed of a nonvolatile Flash memory device is limited by the slow erase time, because programming can be achieved rapidly through the hot-carrier injection with a large current. The fast erase time arises from the high electric field across the thin 2.8 nm tunnel SiO<sub>2</sub> due to the high- $\kappa$  HfAlO ( $\kappa$  = 17) and AlN ( $\kappa$  = 10) and the continuity of D ( $\epsilon_0 \kappa E$ ). The fast erase speed is also related to the high work function IrO<sub>2</sub> metal gate and low charge injection over the thin HfAlO barrier.

Figure 7 shows the retention behavior of an AlN MONOS device at  $85\,^{\circ}\mathrm{C}$ . Initially  $\Delta V_{th}$  was 3.1 or 3.7 V under  $100~\mu s$  13 V program and -12 V or -13 V erase, and gave a good 10-year memory window of 1.4 or 1.9 V, respectively, and a decay rate of 120~(1-state) and only 39~mV/dec (0-state). The good data retention arises from the ionic-bond-related trapping capabilities of Al–N.  $^{7.9}$  The good retention is also due to the fast ( $100~\mu s$ ) switching speed; this helps to reduce the stress degradation of the 2.8~nm tunnel oxide which is involved in confining the stored charge in the QW. Table I summarizes the important memory device characteristics. The AlN MONOS device shows a fast erase time, a good 10-year retention memory window at  $85\,^{\circ}\mathrm{C}$ , and retention decay rates comparable with published data.  $^{2.3}$  These excellent device characteristics are due to high trapping abilities of AlN, the high work function  $IrO_2$  gate, and the low voltage drop across the high- $\kappa$  HfAlO barrier.

## Conclusion

We have demonstrated a novel AIN MONOS memory which uses an IrO $_2$  metal gate and shows a large initial memory window of 3.7 V at ±13 V and a 100  $\mu s$  P/E time. Extrapolated data suggests good 10-year data retention and only 10%  $\Delta V_{\rm th}$  degradation after 10 $^4$  P/E cycles at 85°C.

#### Acknowledgment

The authors from Taiwan, ROC, acknowledge the support of the Nano Science and Technology Center at National Tsing Hua University.

National Chiao Tung University assisted in meeting the publication costs of this article.

Table I. Comparison of memory characteristics of this work with published data.

|                                                                                                                           | P/E condition for retention |        | $V_{\rm th}$ at 85°C (V) |          |                          |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|--------------------------|----------|--------------------------|

|                                                                                                                           | Program                     | Erase  | Initial                  | 10 years | 85°C decay rate (mV/dec) |

| This work                                                                                                                 | 13 V                        | 13 V   | 3.7                      | 1.9      | 172                      |

|                                                                                                                           | 100 μs                      | 100 μs |                          |          |                          |

| Tri-gate SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> /poly                                         | 11.5 v                      | 11.5 V | 1.2                      | 1.1      | 25                       |

| Tri-gate SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> /poly (Infineon, VLSI'04 <sup>2</sup> )       | 3 ms                        | 100 ms |                          | (25°C)   | (25°C)                   |

| MONOS                                                                                                                     | 13.5 V                      | -13 V  | 4.4                      | 2.07     | 215                      |

| SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /Al <sub>2</sub> O <sub>3</sub> /TaN<br>(Samsung, IEDM'03 <sup>3</sup> ) | 100 μs                      | 10 μs  |                          |          |                          |

#### References

- 1. M. H. White, D. A. Adams, and J. Bu, IEEE Circuits Devices Mag., 16, 22 (2000).

- 2. M. Specht, R. Kommling, L. Dreeskornfeld, W. Weber, F. Hofmann, D. Alvarez, J. Kretz, R. J. Luyken, W. Rosner, H. Reisinger, E. Landgraf, T. Schulz, J. Hartwich, M. Stadele, V. Klandievski, E. Hartmann, and L. Risch, Symposium on VLSI Tech-

- nology, p. 244 (2004).

3. C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, Tech. Dig. Int. Electron Devices Meet., 2003, 613.

- 4. Y. K. Lee, S. K. Sung, J. S. Sim, C. J. Lee, T. H. Kim, S. H. Lee, J. D. Lee, B. G.

- Park, D. H. Lee, and Y. W. Kim, Symposium on VLSI Technology, p. 208 (2002).

T. Sugizaki, M. Kobayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, Symposium on VLSI Technology, p. 27

- 6. A. J. Walker, S. Nallamothu, E.-H. Chen, M. Mahajani, S. B. Herner, M. Clark, J. M. Cleeves, S. V. Dunton, V. L. Eckert, J. Gu, S. Hu, J. Knall, M. Konevecki, C. Petti, S. Radigan, U. Raghuram, J. Vienna, and M. A. Vyvoda, Symposium on  $\textit{VLSI Technology}, \, p. \, \, 29 \, \, (2003).$

- 7. A. Chin, C. H. Lai, B. F. Hung, C. F. Cheng, S. P. McAlister, C. X. Zhu, M.-F. Li, and D. L. Kwong, 5th Non-Volatile Memory Technology Symposium Digest, p. 18 (2004).

- 8. C. H. Lai, C. F. Lee, A. Chin, C. Zhu, M. F. Li, S. P. McAlister, and D. L. Kwong, IEEE RF IC Symposium Digest, p. 259 (2004).

- 9. C. H. Lai, B. F. Hung, Albert Chin, C. Zhu, M. F. Li, S. P. McAlister, and D. L.

- Kwong, IEEE Electron Device Lett., 26, 148 (2005).

D. S. Yu, A. Chin, C. C. Laio, C. F. Lee, C. F. Cheng, W. J. Chen, C. Zhu, M.-F. Li, S. P. McAlister, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet., 2004, p. 181.