# Short-Channel Metal-Gate TFTs With Modified Schottky-Barrier Source/Drain

Chih-Feng Huang and Bing-Yue Tsui, Senior Member, IEEE

Abstract—A thin active layer, a fully silicided source/drain (S/D), a modified Schottky-barrier, a high dielectric constant (high- $\kappa$ ) gate dielectric, and a metal gate are integrated to realize high-performance thin-film transistors (TFTs). Devices with 0.1- $\mu$ m gate length were fabricated successfully. Low threshold voltage, low subthreshold swing, high transconductance, low S/D resistance, high on/off current ratio, and negligible threshold voltage rolloff are demonstrated. It is thus suggested for the first time that the short-channel modified Schottky-barrier TFT is a solution to carrier out three-dimension integrated circuits and system-on-panel.

Index Terms—Thin-film transistor (TFT), Schottky-barrier (SB), silicide.

### I. INTRODUCTION

SILICON based thin-film transistors (TFTs) are widely used for the active-matrix liquid crystal display (AMLCD) as drivers of the liquid crystal. Furthermore, TFTs will help to carry out the three-dimensional integrated circuits (3D-ICs) or multilayer Si ICs for system-on-chip (SoC) applications and fully functional system-on-panels (SoPs) in the future [1]–[3]. In order to improve the performance of TFTs, lots of effort has been devoted to the thin-film crystallization technology [4]–[6]. Suppressing channel defects by a thinner gate dielectric is another approach [7]–[9]. On the other hand, gate length  $(L_g)$  scale down is a straightforward approach. However, serious short-channel effects and the performance nonuniformity of short-channel TFTs retard their applications [6], [7].

Recently, Schottky-barrier (SB) MOSFETs have been investigated for the nanoscale devices due to their simple processing, low temperature, low thermal budget, compatibility with conventional MOSFETs, and easy scaling [10]–[13]. The SB MOSFETs utilize metal–silicide or metal-like materials instead of heavily doped silicon to form source/drain (S/D). Metal silicides are formed at low temperature with low thermal budget so that the high temperature activation of source/drain dopant can be eliminated. For electrical aspect, a fixed potential barrier of source junction exists at the silicide/silicon Schottky contact and is insensitive to the electric field coming from the drain so that

Manuscript received September 16, 2005. This work is supported by the National Science Council, Taiwan, R.O.C., under Contract NSC-93-2215-E-009-004. The review of this letter was arranged by Editor J. Sin.

C.-F. Huang is with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: jeffhuang.ee90g@nctu.edu.tw).

B.-Y. Tsui is with the Department of Electronics Engineering, National Chiao-Tung University Hsinchu 300, Taiwan, R.O.C., and also with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LED.2005.860378

the drain-induced barrier lowering (DIBL) is suppressed and the roll-off of threshold voltage is alleviated [12].

In this letter, we combine the factors of the SB source/drain, metal gate, and thin effective gate oxide thickness (EOT) to fabricate deep-submicrometer TFTs. Low threshold voltage, low subthreshold swing, high transconductance, low S/D resistance, high on/off current ratio, and good control of threshold voltage down to 0.1- $\mu$ m gate length are demonstrated.

### II. EXPERIMENTS

The starting material was a 6-in Si wafer. After standard RCA clean, 150-nm thermal oxide was grown as the bottom oxide layer (BOX) followed by an amorphous silicon (a-Si) layer of 50 nm deposition in a low-pressure chemical-vapor-deposition (LPCVD) system at 550 °C. The a-Si active layer was then recrystallized by a solid-phase crystallization (SPC) process at 600 °C in N<sub>2</sub> ambient for 24 h. The grain size is distributed in the range of 0.1 to 0.5  $\mu$ m. The active layer was patterned by E-beam lithography and dry etching. The high- $\kappa$  gate dielectric, HfO<sub>2</sub>, film was deposited immediately after a diluted HF dip to a thickness of 10 nm at 500 °C in a metal-organic chemical vapor deposition (MOCVD) system. Ta/Pt alloy was selected as the metal gate electrode because of its thermal stability on HfO<sub>2</sub> dielectric and tunable work function [14]. The metal gate electrode was patterned by liftoff process. After gate patterning, HfO<sub>2</sub> layer on S/D region was removed by wet etching.

After a 50-nm-thick SiO<sub>2</sub> spacer formation, the active layer at the S/D region was fully converted to Ni silicide by a twostep annealing technique. A 22-nm Ni layer was deposited and wafers were annealed at 300 °C for 1 h in a vacuum to form Ni<sub>2</sub>Si at first. At this temperature, Ni does not react with the TaPt gate. Then, the unreacted Ni was removed selectively by sulfuric acid. A second annealing at 600 °C for 30 s was performed in a rapid thermal annealing (RTA) system to transform Ni<sub>2</sub>Si to NiSi. After the NiSi SB S/D formation, some wafers were implanted by BF<sub>2</sub><sup>+</sup> at 10 keV to a dose of  $1 \times 10^{15}$  cm<sup>-2</sup> followed by an RTA at 600 °C for 90 s in N2 ambient to form a modified SB (MSB) junction [10]. Finally, interlayer dielectric deposition and aluminum interconnect patterning completed the device fabrication. Before measurement, an NH<sub>3</sub> plasma treatment was performed at 300 °C for 1 h to passivate the crystalline defects.

### III. RESULTS AND DISCUSSIONS

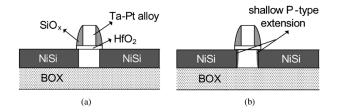

Fig. 1(a) and (b) shows the schematic device structures of SB TFT and MSB TFT, respectively. The corresponding energy band diagrams are shown in Fig. 2(a) and (b). The present of

Fig. 1. Cross-sectional drawings of (a) the SB S/D TFT and (b) the MSB S/D TFT.

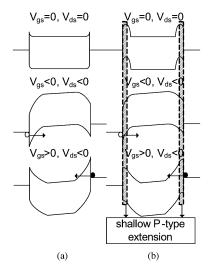

Fig. 2. Band diagrams of p-channel (a) SB TFT and (b) MSB TFT operated at various gate voltages. Replacing the p-type extension by n-type extension, n-channel devices can be obtained.

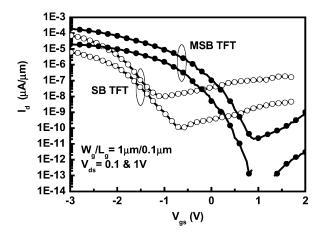

NiSi/Si SB junction at the source/body boundary offers a potential barrier for holes of about 0.5 eV. Under a sufficiently high gate bias which can plenty narrow the potential barrier width, carriers can tunnel through the SB. At the positive gate bias, the tunneling current will be electron dominant, while at negative gate bias it will be hole dominant. Since the NiSi has a work function slightly lower than the midgap of Si, hole tunneling is easier than electron tunneling. Therefore, the NiSi SB TFT tends to be p-type devices. Comparing with the energy bands of SB TFTs, the shallow p-type extension of MSB TFTs further modifies the width of NiSi/Si SB so that at negative gate bias the width of potential barrier is thinner for hole while at positive gate bias the width is thicker for electron. This means that the shallow p-type extension can increase the hole tunneling current and suppress the electron tunneling current. This mechanism is confirmed by the  $I_d$ – $V_{\rm gs}$  characteristics of SB TFT and p-type MSB TFT as shown in Fig. 3. This is the first time that the  $I_{\rm on}/I_{\rm off}$  ratio of TFT with a gate length of 0.1  $\mu m$  can be higher than  $10^6$  and the minimum  $I_{\rm off}$  is lower than  $10^{-11}$  A/ $\mu$ m at  $V_{\rm ds} = -1$  V. The subthreshold swing is also improved to 0.28 V/dec by the MSB junction. The hole mobility is about 10 cm<sup>2</sup>/V·s. This is the typical value that can be obtained by the SPC method.

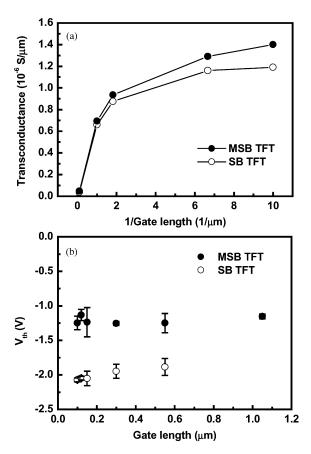

To verify the effect of the SB junction, the maximum transconductance  $(G_m)$  at linear region is investigated at first. The linear region  $G_m$  is basically determined by the channel resistance and tunneling resistance of the SB junction [12]. As shown in Fig. 4(a), the  $G_m$  increases rapidly with the decrease

Fig. 3. Transfer characteristics  $(I_d - V_{\rm gs})$  of SB TFT and p-channel MSB TFT. The gate length and channel width are 0.1 and 1  $\mu$ m, respectively.

Fig. 4. (a) Maximum transconductance  $(G_m)$  and (b) threshold voltage  $(V_{\rm th})$  of SB TFTs and MSB TFTs as a function of gate length measured at  $V_{\rm ds}=-0.1$ .

of gate length and then tends to be saturated. It is known that the channel resistance is linearly proportional to the gate length while the resistance of the SB junction is almost independent of the gate length. The measured  $G_m$  changes from linearly dependent to independent on the gate length. This implies that the  $G_m$  of long-channel SB TFTs ( $L_g > 1~\mu m$ ) is mainly determined by the channel resistance and the  $G_m$  of short-channel SB TFTs is mainly determined by the SB junction. This observation is in agreement for both SB TFTs and MSB TFTs. For the long-channel devices, the  $G_m$  is determined by the channel

resistance so that the  $G_m$  of SB TFTs and MSB TFTs are almost the same. On the other hand, the  $G_m$  of short-channel TFTs is dependent upon the resistance of SB junction so that the MSB TFTs have higher  $G_m$  than that of the SB TFTs.

Similar effects are observed in the threshold voltage  $(V_{\rm th})$  as shown in Fig. 4(b). The  $V_{\rm th}$  is almost independent upon gate length. The low  $V_{\rm th}$  of MSB TFTs is the result of the shallow p-type extension which causes thinner barrier width. As the gate length becomes close to or smaller than the grain size, the numbers of grain boundary in channel region becomes few. The magnitude of  $V_{\rm th}$  deviation would increase with the decrease of gate length if the  $V_{\rm th}$  is determined by the potential barrier of grain boundary. The fact of the  $V_{\rm th}$  deviation does not degrade even if the gate length is reduced to 0.1  $\mu$ m also supports the inference that the  $V_{\rm th}$  is controlled by the SB.

Due to the low threshold voltage  $(V_{\rm th})$ , the  $I_{\rm off}$  at  $V_{\rm gs}=0$  V and  $V_{\rm ds}=-1$  V is about  $1\times 10^{-8}$  A/ $\mu \rm m$ . This value is higher than that of the conventional TFTs but is lower than the specification of high-performance circuits [15]. If lower  $I_{\rm off}$  is required, thinner gate dielectric (better swing), higher channel concentration (higher  $V_{\rm th}$ ), or a new gate electrode with lower work function (higher  $V_{\rm th}$ ) may be adapted.

## IV. CONCLUSION

Gate length scaling offers a notable benefit on device performance improvement. The issues of the threshold voltage rolloff and  $I_{\rm off}$  increase of the short channel device are solved by the MSB S/D junction. The effects of channel defects are suppressed by the thin active layer and thin gate dielectric layer. By integrating these advanced features, a 0.1  $\mu$ m gate length TFT is demonstrated with low threshold voltage, low subthreshold swing, high transconductance, low S/D resistance, high on/off current ratio, and negligible threshold voltage roll-off. These observations imply that the MSB TFTs fabricated with low temperature processes are a potential solution to carry out high performance TFTs for 3-D integrated circuit and SoP applications.

# ACKNOWLEDGMENT

The authors would like to thank M. J. Yang, R. H. Hao, and Dr. C. H. Chien for  $HfO_2$  deposition.

### REFERENCES

- K. Banerjee, S. J. Souri, P. Kapur, and K. C. Saraswat, "3-D ICs: A novel chip design for improving deep sub-micrometer interconnect performance and system-on-chip integration," *Proc. IEEE*, vol. 89, no. 5, pp. 602–633, May 2001.

- [2] T. Ikeda, Y. Shionoiri, T. Atsumi, A. Ishikawa, H. Miyake, Y. Kurokawa, K. Kato, J. Koyama, S. Yamazaki, K. Miyata, T. Matsuo, T. Nagai, Y. Hirayama, Y. Kubota, T. Muramatsu, and M. Katayama, "Full-functional system liquid crystal display using CG-silicon technology," in *Proc. SID*, 2004, pp. 860–863.

- [3] D. S. Yu, A. Chin, C. C. Laio, C. F. Lee, C. F. Cheng, W. J. Chen, C. Zhu, M.-F. Li, W. J. Yoo, S. P. McAlister, and D. L. Kwong, "3D GOI CMOSFETs with novel IrO<sub>2</sub>(Hf) dual gates and high-κ dielectric on 1P6M-0.18 μm-COMS," in *IEDM Tech. Dig.*, 2004, pp. 181–184.

- [4] T. Mizuki, J. S. Matsuda, Y. Nakamura, J. Takagi, and T. Yoshida, "Large domains of continuous grain silicon on glass substrate for high-performance TFTs," *IEEE Trans. Electron Devices*, vol. 51, no. 2, pp. 204–211, Feb. 2004.

- [5] H. Wang, M. Chan, S. Jagar, Y. wang, and P. K. Ko, "Submicron super TFTs for 3-D VLSI applications," *IEEE Electron Device Lett.*, vol. 21, no. 9, pp. 439–441, Sep. 2000.

- [6] K. I. Kamins and P. J. Marcoux, "Hydrogenation of transistors fabricated in polycrystalline silicon films," *IEEE Electron Device Lett.*, vol. EDL-1, pp. 159–161, 1980.

- [7] P.-S. Lin and T. S. Li, "The impact of scaling-down oxide thickness on poly Si thin-film transistors' *I–V* characteristics," *IEEE Electron Device Lett.*, vol. 15, pp. 138–140, Apr. 1994.

- [8] C.-F. Huang and B.-Y. Tsui, "Short channel schottky barrier TFTs with metal gate and high dielectric constant gate dielectric," in *Proc. ECS*, 2005, pp. 376–382.

- [9] J. Kedzierski, P. Xuan, V. Subramanian, J. Bokor, T.-J. King, and C. Hu, "A 20 nm gate-length ultrathin body p-MOSFET with silicide source/drain," *Superlatt. Microstruct.*, vol. 28, pp. 445–452, Nov. 2000.

- [10] B.-Y. Tsui and C.-P. Lin, "A novel 25-nm modified schottky-barrier FinFET with high performance," *IEEE Electron Device Lett*, vol. 25, no. 6, pp. 430–432, Jun. 2004.

- [11] J. R. Tucker, C. Wang, and P. S. Carney, "Silicon field-effect transistor based on quantum tunneling," *Appl. Phys. Lett.*, vol. 65, pp. 618–620, Aug. 1994.

- [12] W. Saitoh, A. Itoh, S. Yamagami, and M. Asada, "Analysis of short-channel schottky source/drain metal-oxide-semiconductor field-effect transistor on silicon-on-insulator substrate and demonstration of sub-50-nm n-type device with metal gate," *Jpn. J. Appl. Phys.*, vol. 38, pp. 6226–6231, Nov. 1999.

- [13] A. Kinoshita, Y. Tsuchiya, A. Yagishita, K. Uchida, and J. Koga, "Solution for high-performance schoyyky-source/drain MOSFETs: Schottky barrier height engineering with dopant segregation technique," in *Symp. VLSI Tech. Dig.*, 2004, pp. 168–169.

- [14] B.-Y. Tsui and C.-F. Huang, "Wide range work function modulation of binary alloys for MOSFET application," *IEEE Electron Device Lett.*, vol. 24, no. 3, pp. 153–155, Mar. 2003.

- [15] International Technology Roadmap for Semiconductors (ITRS) [Online]. Available: http://public.itrs.net