# A Novel Wafer Reclaim Method for Amorphous SiC and Carbon Doped Oxide Films

Bing-Yue Tsui, Senior Member, IEEE, and Kuo-Lung Fang, Student Member, IEEE

Abstract—Amorphous SiC (a-SiC) films are the most promising dielectric diffusion barriers to replace silicon nitride in Cu-interconnect technology. However, reclaim of wafers with a-SiC films is a challenge issue for mass production. In this paper, a novel wafer reclaim method is proposed. It is observed that a-SiC can be oxidized to SiO2 in both dry O2 and steam ambients at temperatures as low as 550 °C. The oxidation mechanism can be described by the Deal-Grove model that is traditionally used to describe oxidation of Si. Experiments prove that the oxidation process is clean and uniform. It is also observed that carbon doped oxide (CDO) films can be oxidized easily, too. Therefore, oxidation followed by HF etching could be a universal process to reclaim wafers deposited with a-SiC or CDO films. Since the oxidation rate of Si substrates at medium temperatures is much lower than that of a-SiC and CDO films, the oxidation process is virtually self-limiting. Compared with a traditional reclaim method based on wafer polishing, this universal oxidation-etching method exhibits great benefits in terms of low cost, high throughput, and the ability to perform nearly unlimited numbers of reclaim cycles.

Index Terms—Amorphous silicon carbide, low dielectric constant, wafer reclaim.

## I. INTRODUCTION

S FEATURE sizes of integrated circuits continue to be scaled down, new interconnect materials such as Cu and low-dielectric constant (low-K) films have been used to minimize crosstalk and signal resistance-capacitance (RC) delay [1]-[3]. It is expected that amorphous SiC (a-SiC) films deposited by chemical vapor deposition will replace Si<sub>3</sub>N<sub>4</sub> in the Cu dual-damascene structure as a Cu diffusion barrier and/or etch-stop layer in order to further reduce circuit delay and thus improve circuit performance [4], [5]. The a-SiC films are chemically inert and hard to etch in wet processing environments. These properties are benefits from the process point of view. However, they are liabilities from the wafer reclaim point of view. On the other hand, large numbers of low-K materials are developed every year. Carbon doped oxide (CDO) and porous carbon doped oxide are very promising low-K materials for future Cu interconnect applications [6]–[11].

Manuscript received August 12, 2003; revised May 11, 2005. This work was supported by the National Science Council, R.O.C. under Contract NSC-91-2215E-009-048.

B.-Y. Tsui is with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: bytsui@cc.nctu.edu.tw).

K.-L. Fang is with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C., and also with the Semiconductor and Microsystems Technology Laboratory, Dresden University of Technology, 64 Dresden, Germany (e-mail: klfang@homer.wh12.tu-dresden.de).

Digital Object Identifier 10.1109/TSM.2005.858501

In the back-end-of-line (BEOL) process, fabrication parameters, such as film thickness, thickness uniformity, film composition, and particle counts must be carefully and precisely controlled. Therefore, large numbers of monitor wafers are required to optimize the film deposition conditions during process development and to monitor the process stability during manufacturing. Wafers deposited with a-SiC or low-K films must be reclaimed to reduce wafer cost. Unfortunately, there is no universal chemical solution that can etch a-SiC or various low-K films. Polishing becomes the only method to reclaim these wafers, but the cost of wafer polishing is high. Furthermore, the over polish of the Si substrate limits the numbers of reclaim cycles.

In this work, we report the phenomenon and kinetics of thermal oxidation of a-SiC and CDO thin films at moderate temperatures. We also propose a universal wafer recycling method consisting of thermal oxidation followed by HF etching, for stripping a-SiC and CDO films.

## II. EXPERIMENTAL PROCEDURE

Blanket wafers deposited with thin dielectric films were used in this study. The substrates were (100)-oriented, 8-in-diameter Si wafers. The a-SiC films of thickness between 50 nm and 100 nm were deposited on Si wafers in a plasma-enhanced chemical vapor deposition system from organosilicon precursors. Two kinds of a-SiC:N films with various nitrogen contents were prepared to check the effect of nitrogen on the oxidation rate. The SiC:N (9.3%) samples were deposited in the presence of N<sub>2</sub> carrier gas flowing at 5000 sccm. SiC:N (5%) samples were deposited with N<sub>2</sub> flow rates of 2500 sccm and He flow rates of 2500 sccm. Both dry O<sub>2</sub> oxidation and steam oxidation were performed in a simple furnace system at medium temperatures ranging from 550 °C to 950 °C. To examine the efficiency of the oxidation method to reclaim wafers with a-SiC films, some wafers were oxidized in a vertical furnace with H<sub>2</sub> flow rate of 4 SLM and  $O_2$  flow rate of 4 SLM. The particles in this furnace are well controlled to mass-production levels. Plasma oxidation of a-SiC films was also evaluated at the conditions of  $O_2$  flow rate 900 sccm, radio frequency (RF) power 300 W, and substrate temperature 250 °C. Finally, two kinds of CDO films with K-values of 2.6 and 2.2 were prepared to evaluate if the oxidation method can be adapted to general CDO films.

The thickness of dielectric layer was measured with an N&K 1200 spectrophotometer. Thermal desorption spectroscopy (TDS) was use to analyze the thermal stability of a-SiC films. Auger electron spectroscopy (AES) and Fourier-transformed infra-red (FTIR) spectroscopy were used to analyze the chemical composition and chemical bonding of the oxidized a-SiC

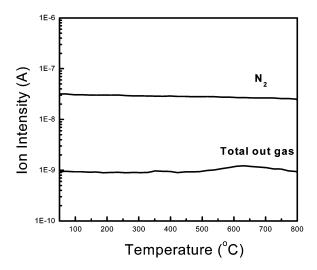

Fig. 1. Thermal desorption spectroscopy of a-SiC film in N2 ambient.

film. Surface roughness after stripping the oxidized layer was monitored with an atomic force microscope (AFM). The particle counts of post etched and cleaned wafer surfaces were measured with a KLA-Tencor SP1.

#### III. RESULTS AND DISCUSSION

# A. Oxidation Phenomenon of SiC

SiC shows thermal stability in N<sub>2</sub> ambient that is as good as that of  $\mathrm{Si_3N_4}$ . Fig. 1 shows that the TDS analysis on a-SiC films in N<sub>2</sub> ambient up to 800 °C does not produce any desorbed species. Even though the films have been annealed at 950 °C in  $N_2$  ambient for 1 h, the thickness shrinkage is only 1 nm, i.e., less than 2%. However, unlike Si<sub>3</sub>N<sub>4</sub>, a-SiC films do not dissolve in HF solution or boiling H<sub>3</sub>PO<sub>4</sub>. Adding oxidants such as H<sub>2</sub>O<sub>2</sub>, H<sub>2</sub>SO<sub>4</sub>, or HOCl<sub>4</sub> does not cause dissolution. As a result, no chemical solutions have been demonstrated for removal of a-SiC films from monitor wafers in a production environment. Therefore, physical polishing is the only solution to stripping a-SiC films, but consumption of Si due to the unavoidable over-polishing limits the number of times a monitor wafer can be reclaimed. Fortunately, it is observed that although it is hard to oxidize crystalline SiC at temperatures lower than 1100 °C [12]-[14], a-SiC films can be oxidized at much lower temperature in oxygen containing ambients.

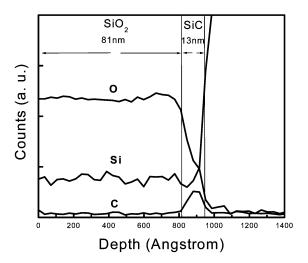

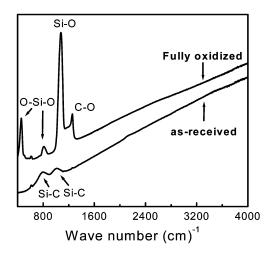

Fig. 2 shows the AES depth profile of a partially oxidized a-SiC film. The original SiC film thickness was 94 nm. The oxidation was performed in dry  $\rm O_2$  ambient at 850 °C for 60 min. A high purity  $\rm SiO_2$  layer is formed and a clear  $\rm SiO_2/SiC$  interface is observed. These observations indicate that the a-SiC film is oxidized to  $\rm SiO_2$  from the top surface uniformly. Fig. 3 exhibits the FTIR spectrum of a fully oxidized a-SiC film. Before oxidation, only Si-C peaks can be detected. After steam oxidation at 950 °C for 1 h, Si-C peaks disappear and Si-O peaks are evident. The small C-O peak indicates that some carbon atoms remain in the oxide [15]. The a-SiC has a density of about 1.5 g/cm³, which is less than that of crystalline SiC [16]. Knowing that the density of the  $\rm SiO_2$  film is 2.2 g/cm³, the volume transformation ratio from a-SiC to  $\rm SiO_2$  can be calculated to be around

Fig. 2. Atomic depth profile of a partially oxidized a-SiC film analyzed by AES

Fig. 3. FTIR spectrum of a fully oxidized a-SiC film. Small C-O peak indicates that some carbon atoms exist in the oxide layer.

1 to 1. This ratio is very close to the experimental observation in Fig. 2 that the total dielectric thickness of the partially oxidized  $\mathrm{SiC/SiO}_2$  stack is close to the original SiC thickness determined by N&K analyzer measurement.

### B. Oxidation Kinetics

Both dry oxidation and steam oxidation can convert a-SiC to  $\mathrm{SiO}_2$ . Equations (1) and (2) express the stoichiometries for reaction of a-SiC with  $\mathrm{O}_2$  and  $\mathrm{H}_2\mathrm{O}$ . Most of the carbon in SiC film reacts with oxygen to form  $\mathrm{CO}_2$  and diffuses into the ambient. The oxidation model for a-SiC follows the Deal–Grove analysis of the oxidation of Si [17]–[19]. The Deal–Grove model assumes that oxidation proceeds in following three steps: 1) the oxidants are adsorbed to the outer surface where they may react; 2) oxidants are transported through grown oxide film toward the  $\mathrm{SiO}_2/\mathrm{SiC}$  interface; and 3) oxidant reacts at the SiC surface to form  $\mathrm{SiO}_2$ .

$$SiC + 2O_2 \rightarrow SiO_2 + CO_2 \tag{1}$$

$$SiC + 2H_2O \rightarrow SiO_2 + CO_2 + 4H_2.$$

(2)

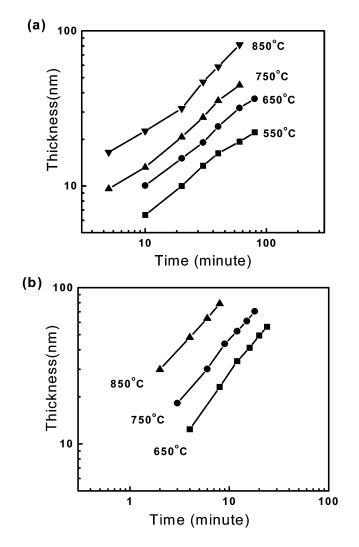

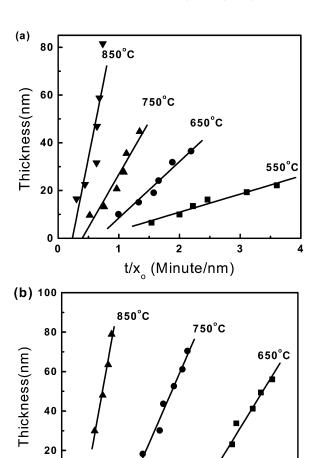

Fig. 4. Oxide thickness versus oxidation time of a-SiC film oxidized in (a) dry  $\rm O_2$  ambient and (b) steam ambient.

Fig. 4(a) and (b) show the grown oxide thickness on an a-SiC film in dry  ${\rm O}_2$  and steam ambients at various temperatures. Similar to Si, the oxidation rate of a-SiC film in a steam ambient is much faster than that in a dry  ${\rm O}_2$  ambient. According to the Deal–Grove model, the correlation between grown oxide thickness and oxidation time can be expressed as  $X_0^2 + AX_0 \to Bt$ , where  $X_O$  and t represent grown oxide thickness and oxidation time.

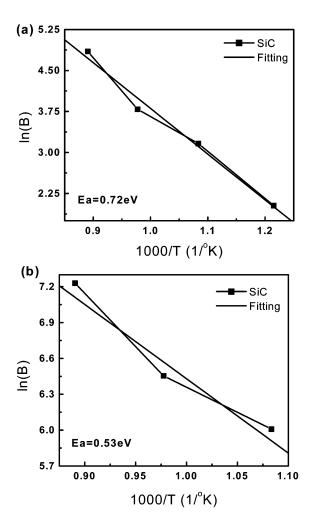

By plotting  $X_O$  versus  $t/X_O$ , The coefficients of A and B can be extracted, as shown in Fig. 5(a) and (b), respectively. Tables I and II summarize the rate constants in dry  $O_2$  and steam. The temperature dependence of B is plotted in Fig. 6. The activation energy  $(E_a)$  of B is 0.72 eV in dry  $O_2$  and 0.53 eV in steam. The  $E_a$  value of B for Si oxidation is about 1.1 eV in dry  $O_2$  and 0.7 eV in steam [16]. By comparison with Si oxidation, the  $E_a$  values for a-SiC oxidation are smaller than those of Si oxidation but the trend that  $E_a$  in dry ambient is higher than that in steam ambient is consistent. It is known that B is related to the diffusion of oxidants in grown  $SiO_2$ . The low  $E_a$  of a-SiC oxidation might result from the fact that the  $SiO_2$  grown on a-SiC at the temperatures studied here is not as dense as that grown on Si because of residual carbon in the oxide. It should

Fig. 5. Extraction of oxidation rate constants of a-SiC in (a) dry  $\rm O_2$  ambient and (b) steam ambient according to the Deal–Grove model.

t/x (Minute/nm)

0.48

0.16

0.00

$\label{eq:table_interpolation} \textbf{TABLE} \ \ \textbf{I}$  Oxidation Rate Constants of SiC in Dry  $\mathrm{O}_2$  Ambient

| SiC | 550°C | 650°C | 750°C | 850°C  |

|-----|-------|-------|-------|--------|

| A   | 4.28  | 15.17 | 17.57 | 30.05  |

| В   | 7.60  | 23.64 | 44.31 | 127.56 |

TABLE II

OXIDATION RATE CONSTANTS OF SIC IN STEAM AMBIENT

| SiC | 650°C  | 750°C  | 850°C   |

|-----|--------|--------|---------|

| A   | 116.18 | 78.47  | 64.27   |

| В   | 406.73 | 574.53 | 1379.29 |

be noted that the refractive index of the  $SiO_2$  grown on SiC is about 1.45, which is slightly smaller than that grown on Si.

The properties of a-SiC films such as adhesion, thermal stress, barrier ability, and etch rate change with the addition of nitrogen atoms to the films [5], [20], [21]. Two kinds of a-SiC:N films with various nitrogen contents were oxidized in steam at 950 °C for 1 h. For the SiC:N(5%) sample, 80.3 nm

Fig. 6. Arrhenius plot of parabolic rate constant of a-SiC oxidation in (a) dry  $\rm O_2$  ambient and (b) steam ambient. Activation energy is 0.72 eV and 0.55 eV in (a) and (b), respectively.

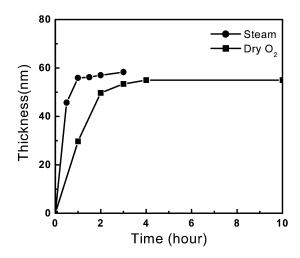

of SiC was consumed while for the SiC:N(9.3%) sample, only 43.6 nm of SiC:N was consumed. This result shows that higher nitrogen content results in higher oxidation resistance. It is postulated that a Si-N bonds would be formed in a-SiC:N films, and the oxidation rate is reduced due to the stronger Si-N bond (470 KJ/mole) in comparison with the Si-C bond (450 KJ/mole) [22]. Although a-SiC and a-SiC:N could be oxidized easily at moderate or high temperature, for the purpose of wafer reclaim it is not preferred to over-oxidize the silicon substrate. Fortunately, Si oxidizes very slowly at temperatures lower than 800 °C. Thus, it is expected that the oxidation process will almost self-stop when the a-SiC or a-SiC:N film is consumed. Fig. 7 shows the grown oxide thickness of a 54-nm-thick a-SiC on Si substrate at 600 °C. As the a-SiC film was oxidized completely, the oxide thickness increased very slightly because of the low the oxidation rate of Si at 600 °C, independent of whether the ambient was dry  $O_2$  or steam.

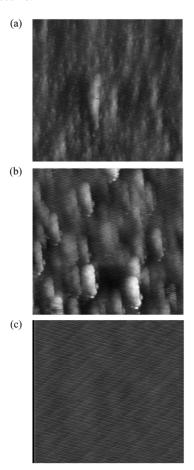

Fig. 8(a)–(c) show the surface image of (a) as-deposited a-SiC; (b) partially oxidized a-SiC; and (c) fully oxidized a-SiC after removal of the  $\mathrm{SiO}_2$  layer. The oxidation was performed in dry  $\mathrm{O}_2$  at 800 °C. For the partially oxidized wafer [Fig. 8(b)], the post-etched surface is relatively rough

Fig. 7. Grown oxide thickness of wafer capped with 54 nm thick a-SiC film and oxidized at 600 °C.

Fig. 8. Atomic force microscope surface images of (a) as-deposited SiC surface, (b) partially oxidized, and (c) fully oxidized a-SiC deposited wafer after oxidation and etching of the oxidized layer.

with root-mean-square (rms) roughness of 1.27 nm. The column-like morphology comes from the nonuniformity of the as-deposited a-SiC surface, as shown in Fig. 8(a). Meanwhile, the fully oxidized wafer [Fig. 8(c)] shows a very smooth Si surface with rms roughness of 0.23 nm, which is similar to the background noise level. This result also implies that Si does not oxidize as easily as SiC at lower temperatures. All of these results indicate the SiC oxidation is clean and self-stopped.

| TABLE III            |        |

|----------------------|--------|

| RESULTS OF RECLAIMED | WAFERS |

| Mean                           | SiC#1 | SiC#2 | SiC#3 | SiC#4 | Si   |

|--------------------------------|-------|-------|-------|-------|------|

| SiC thickness(nm)              | 70    | 70    | 70    | 70    | 0    |

| SiO <sub>2</sub> thickness(nm) | 377   | 390   | 410   | 391   | 351  |

| Deviation(nm)                  | 3.37  | 6.41  | 6.7   | 7.89  | 12.4 |

TABLE IV

PARTICLE COUNTS AFTER CLEANING

| Particle radius      | SiC#1 | SiC#2 | SiC#3 | SiC#4 | Si  |

|----------------------|-------|-------|-------|-------|-----|

| 0.2um                | 24    | 27    | 68    | 44    | 58  |

| 0.3um                | 1     | 6     | 28    | 13    | 10  |

| 0.4um                | 2     | 6     | 6     | 6     | 10  |

| 0.5um                | 3     | 2     | 6     | 2     | 21  |

| Total counts(>0.2µm) | 36    | 43    | 112   | 73    | 132 |

# C. Examples of Oxidation Application

The most direct application of a-SiC oxidation is wafer reclaim. To demonstrate the efficiency of wafer reclaim with this process, four 200-mm wafers capped with a 70-nm-thick a-SiC film were oxidized in an ASM advance 400 vertical furnace with a  $H_2$  flow rate of 4 SLM and an  $O_2$  flow rate of 4 SLM at 950 °C for 2 h. Bare Si wafers were processed simultaneously as references. Table III lists the grown oxide thickness. Because of the high temperature and long oxidation period, the a-SiC films were consumed very quickly and then the Si substrate was also oxidized. The thicker  $SiO_2$  layers on the a-SiC deposited wafers compared to the SiO2 layers on the Si reference wafer confirm that the oxidation rate of a-SiC is faster than that of Si. The small thickness deviation (1%-2%) indicates that the a-SiC was oxidized uniformly. In this experiment, only the five wafers were processed in the oxidation furnace and the other slots were not filled with dummy wafers. The Si control wafer is the first wafer so that the uniformity is the poorest among the five wafers. Particle counts after removing the SiO2 layer in diluted HF followed by standard RCA-clean processing are summarized in Table IV. The particle counts of all four a-SiC deposited wafers are close to or lower than that of the Si reference wafer. These results show that the oxidation followed by HF etching is a viable technique to reclaim a-SiC deposited wafers.

On the basis of the a-SiC oxidation results, it is supposed that CDO films could be oxidized in the same manner. Wafers with 360-nm-thick CDO (K=2.6) or 180-nm-thick porous-CDO (K=2.2) were oxidized in dry  $O_2$  at 950 °C for 1 h followed by dilute HF etching and standard clean. No CDO or porous-CDO films were left on the Si wafer. It should be mentioned that CDO films not only oxidized but also suffered thickness shrinkage due to thermal decomposition under such a thermal process [11], [15]. It is hard to describe the oxidation processes for these films with the Deal–Grove model. However, since the thermal stability of CDO films is worse than that of a-SiC films, CDO films can be oxidized and removed easily.

We also observed that a-SiC films could be oxidized in general  $O_2$  plasma systems. For example, an approximately 10-nm-

thick a-SiC layer is converted to  $\mathrm{SiO}_2$  after 2 h  $\mathrm{O}_2$  plasma treatment at room temperature in a parallel plate plasma chamber with an RF power of 300 W. The oxidation of a-SiC and CDO films provides an answer to prior observations reported in the literature [23]: why is there a new layer formed at outer CDO surface after  $\mathrm{O}_2$  plasma treatment. This new layer should be  $\mathrm{SiO}_2$  and it should be carefully controlled in Cu damascene process because a photoresist removal process is commonly incorporated with  $\mathrm{O}_2$  plasma ashing. During the  $\mathrm{O}_2$  plasma process, the dielectric properties and surface layer of a-SiC and CDO films would change [24].

#### IV. CONCLUSION

This work documents that a-SiC films can be oxidized to  $\mathrm{SiO}_2$  at medium temperatures. The oxidation process can be described with the Deal–Grove model. Experiments prove that the oxidation process is clean and uniform. This may provide a simple method to reclaim a-SiC film deposited wafers. It is also observed that CDO films can be oxidized. Therefore, oxidation followed by HF etching could be a universal process to reclaim wafers with a-SiC or CDO films. Since the oxidation rate of Si substrates at medium temperature is much lower than that of the a-SiC and CDO films, the oxidation process is almost a self-stopped process. Comparing with traditional wafer polishing reclaim methods, this universal oxidation-etching method exhibits great benefits of low cost, high throughput, and almost unlimited reclaim lifetimes.

Finally, because a-SiC and CDO films are easily oxidized in  $\rm O_2$  plasma, photoresist stripping processes must be carefully controlled to minimize the dielectric degradation or surface change of a-SiC and CDO films. These changes may affect the integration of Cu/Low-K integration and the designed circuit performance.

#### ACKNOWLEDGMENT

The authors would like to express their great appreciation to C.-H. Wu, and Dr. Y.-H. Li for technical supports. Most of the experiments were performed in the National Nano Device Laboratories.

#### REFERENCES

- T. Ohmi, T. Hoshi, T. Yoshie, T. Takewaki, M. Otsuki, T. Shibata, and T. Nitta, "Large-electromigration-resistance copper interconnect technology for sub-half- micron ULSI's," in *IEDM Tech. Dig.*, 1991, pp. 285–288

- [2] "The national technology roadmap for semiconductors," Semiconductor Industry Association, San Jose, CA, 2003.

- [3] D. Edelstein, J. Heidenreich, R. Goldblatt, W. Cote, C. Uzoh, N. Lustin, P. Roper, T. McDevitt, W. Motsiff, A. Simon, J. Dukovic, R. Wachnik, H. Rathore, R. Schulz, L. Su, S. Luce, and J. Slattery, "Full copper wiring in a sub-0.25 μm CMOS ULSI technology," in *IEDM Tech. Dig.*, 1997, pp. 773–776.

- [4] P. Xu, K. Huang, A. Patel, S. Rathi, B. Tang, J. Ferguson, J. Huang, C. Ngai, and M. Loboda, "BLOK-a low-k dielectric barrier/etch stop film for copper damascene applications," in *Proc. Int. Interconnect Technol. Conf.*, 1999, pp. 109–111.

- [5] B. Y. Tsui, K. L. Fang, and S. D. Lee, "Electrical instability of low dielectric constant diffusion barrier film (a-SiC:H) for copper interconnect," *IEEE Trans. Electron Devices*, vol. 48, no. 10, pp. 2375–2383, Oct. 2001.

- [6] M. Tada, Y. Harada, K. Hijioka, H. Ohtake, T. Takeuchi, S. Saito, T. Onodera, M. Hiroi, N. Furutake, and Y. Hayashi, "Cu dual damascene interconnects in porous organosilica film with organic hard-mask and etchstop layers for 70 nm-node ULSIs," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 12–15.

- [7] J. C. Lin, R. Augur, S. L. Shue, C. H. Yu, M. S. Liang, A. Vijayendran, T. S. de Felipe, and M. Danek, "CVD barriers for Cu with nanoporous ultra low-k: Integration and reliability," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 21–23.

- [8] H. J. Lee, Y. H. Kim, J. Y. Kim, E. K. Lin, B. J. Bauer, W. I. Wu, and H. J. Kim, "Structural characterization of porous low-k SiOC thin films using x-ray porosimetry," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 54–56.

- [9] C. Waldfried, Q. Han, O. Escorica, A. Margolis, R. Albano, and I. Berry, "Single wafer rapidcuring/spl trade/ of porous low-k materials," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 226–228.

- [10] K. Buchanan, K. Beekmann, K. Giles, J.-C. Yeoh, and H. Donohue, "Characterization and integration of CVD ultra low k films (k < 2.2) for dual damascene IMD applications," in *Proc. Adv. Metallization Conf.*, 2001, pp. 73–78.

[11] K. L. Fang, B. Y. Tsui, C. C. Yang, M. C. Chen, S. D. Lee, K. Beekmann,

- [11] K. L. Fang, B. Y. Tsui, C. C. Yang, M. C. Chen, S. D. Lee, K. Beekmann, T. Wilby, K. Giles, and S. Ishaq, "Electrical and material stability of orion CVD ultra low-k dielectric film for copper interconnection," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 60–63.

- [12] D. M. Brown, M. Ghezzo, J. Kretchmer, E. Downey, J. Primbley, and J. Palmour, "SiC MOS interface characteristics," *IEEE Trans. Electron Devices*, vol. 41, no. 4, pp. 618–620, Apr. 1994.

- [13] H. Yaho, F. Katafuchi, T. u. Kimoto, and H. Matsunami, "Effects of wet oxidation/anneal on interface properties of thermally oxidized SiO<sub>2</sub>/SiC MOS system and MOSFET's," *IEEE Trans. Electron Devices*, vol. 46, no. 3, pp. 504–510, Mar. 1999.

- [14] J. Champi, Y. Shi, Y. Luo, F. Yan, and J. H. Zhao, "Study of interface state density and effective oxide charge in post-metallization annealed SiO<sub>2</sub>/SiC structures," *IEEE Trans. Electron Devices*, vol. 46, no. 3, pp. 511–519, Mar. 1999.

- [15] X. Jun, C. S. Yang, H. R. Jang, and C. K. Choi, "Chemical structure evolution of SiOCH films with low dielectric constant during PECVD and postannealing," *J. Electrochem. Soc.*, vol. 150, no. 12, pp. F206–F210, 2003.

- [16] S. G. Lee, Y. J. Kim, S. P. Lee, H. S. Oh, S. J. Lee, M. Kim, I. G. Kim, J. H. Kim, H. J. Shin, J. G. Hong, H. D. Lee, and H. K. Kang, "Low dielectric constant 3MS α-SiC:H as Cu diffusion barrier layer in Cu dual damascene process," *Jpn. J. Appl. Phys.*, vol. 40, no. 4B, pp. 2663–2668, 2001.

- [17] B. E. Deal and A. S. Grove, "Relationship for the thermal oxidation of Si," *J. Appl. Phys.*, vol. 36, no. 12, pp. 3770–3778, 1965.

- [18] H. Z. Massoud, J. D. Plummer, and E. A. Irene, "Thermal oxidation of silicon in dry oxidation—Growth rate enhancement in the Thin Regime, I experiment results," *J. Electrochem. Soc.*, vol. 132, no. 11, pp. 2685–2693, 1985.

- [19] ——, "Thermal Oxidation of Silicon in Dry Oxidation—Growth Rate Enhancement in the Thin Regime, II Physical Mechanisms," *J. Electrochem. Soc.*, vol. 132, no. 11, pp. 2694–2699, 1985.

- [20] C. C. Chiang, M. C. Chen, Z. C. Wu, L. J. Li, S. M. Jang, C. H. Yu, and M. S. Liang, "TDDB reliability improved in Cu damascene by using a bilayer-structured PECVD SiC dielectric barrier," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 200–203.

- [21] M. Fayolle, J. Torres, G. Passemard, F. Fusalba, G. Fanget, D. Louis, L. Arnaud, V. Girault, J. Cluzel, H. Feldis, M. Rivoire, O. Louveau, T. Mourier, and L. Broussous, "Integration of Cu/SiOC in dual damascene interconnect for 0.13 μm technology using a new SiC material as dielectric barrier," in *Proc. Int. Interconnect Technol. Conf.*, 2002, pp. 39–41.

- [22] D. R. Lide, CRC Handbook of Chemistry and Physics, 83rd ed. Boca Raton, FL: CRC, 2002–2003, pp. 9–53.

- [23] Y. H. Wang, D. Gui, R. Kumar, and P. D. Foo, "Reduction of oxygen plasma damage by postoxidaiton Helium Plasma Treatment for carbondoped silicon oxide low dielectric constant films," *Electrochem. Solid-State Lett.*, vol. 6, no. 1, pp. F1–F3, 2003.

- [24] H. Cui, H. Lu, I. Bhat, S. Murarka, W. Lanford, and W. Li, "Characterization of methyl-doped silicon oxide film for inter-layer dielectrics application," in *Proc. Int. Interconnect Technol. Conf.*, 2001, pp. 45–47.

**Bing-Yue Tsui** (S'87–M'93–SM'01) was born in Chiayi, Taiwan, R.O.C., in 1963. He received the B.S., M.S., and Ph.D. degrees from the National Chiao-Tung University, Hsinchu, Taiwan, in 1985, 1987, and 1992, respectively, all in electrical engineering.

He joined the Electronics Research and Service Organization, Industrial Technology Research Institute (ERSO/ITRI), Hsinchu, Taiwan, R.O.C., in October 1992. From 1992 to 1994, he worked on 0.5  $\mu$ m/16 Mb DRAM process integration.

Since 1995, he led the Sub-micron Device Technology Group to develop sub-quarter-micron MOSFETs. Since 1997, he was Project Leader and Section Manager of etching technology. Since 1998, he led the Etching and Process Integration Department to develop the deep sub-micron Al-interconnect and Cu/low K interconnect technologies. Currently, he is an Associate Professor at the National Chiao-Tung University, Hsinchu, Taiwan. He is now interested in the Cu/low K dielectric integration, metal gate/high K dielectric integration, nano-scale Si devices, and carbon nano-tube devices. He has authored and co-authored more than 40 journal papers and 50 conference papers. He also owns 14 R.O.C. patents and 10 U.S. patents. Another 16 patents are pending.

Dr. Tsui was awarded the Research Paper Award by the Industrial Technology Research Institute and the Outstanding Young Electrical Engineer by the Institute of Chinese Engineer, both in 1998. He is a Member of Phi Tau Phi and his name is listed in Who's Who in the World, Who's Who in Finance and Industry, Who's Who in Science and Engineering, and Who's Who in Asia and the Pacific Nations.

**Kuo-Lung Fang** (S'01) was born in Hsinchu, Taiwan, R.O.C., in 1976. He received the B.S. degree in electronics engineering, in 1998, from National Chiao-Tung University, Hsinchu, Taiwan, R.O.C., where he is currently working toward the Ph.D. degree.

His current research topic is the integration issues of Cu and low dielectric constant materials. He is now a Visiting Scholar in the Semiconductor and Microsystems Technology Laboratory, Dresden University of Technology, Dresden, Germany.