# RSC Advances

Accepted Manuscript

This article can be cited before page numbers have been issued, to do this please use: P. Liu, C. Chang and C. Fuh, RSC Adv., 2016, DOI: 10.1039/C6RA22423G.

This is an Accepted Manuscript, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about Accepted Manuscripts in the **author guidelines**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the ethical guidelines, outlined in our <u>author and reviewer resource centre</u>, still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this Accepted Manuscript or any consequences arising from the use of any information it contains.

Published on 03 November 2016. Downloaded by Newcastle University on 07/11/2016 07:10:24

DOI: 10.1039/C6RA22423G

### **RSC Advances**

Paper

## **Enhancement of Reliability and Stability for Transparent Amorphous Indium-Zinc-Tin-Oxide thin film transistors**

Received 00th January 20xx, Accepted 00th January 20xx

DOI: 10.1039/x0xx00000x

www.rsc.org/

Po-Tsun Liu, Chih-Hsiang Chang and Chur-Shyang Fuh

We studied the influence of the backchannel passivation layer (BPL) on the ambient stability of amorphous Indium-Zinc-Tin-Oxide thin-film transistors (a-IZTO TFTs), in which atomic layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> film and plasma-enhanced chemical vapor deposited (PECVD) SiO<sub>2</sub> film was separately used to be the channel passivation layers. It was observed that the BPL deposition process strongly affects device performance and stability. From the results of extracted activation energy (E<sub>act</sub>), the Al<sub>2</sub>O<sub>3</sub> passivation layer can reduce the trap density in localized tail states, which improves the mobility of a-IZTO TFTs. Compared with SiO<sub>2</sub> passivation layer, the Al<sub>2</sub>O<sub>3</sub> passivation process effectively suppresses the H injection into the underneath a-IZTO channel layer with secondary ion mass spectrometer analysis. In addition, it is found that the a-IZTO TFT with Al<sub>2</sub>O<sub>3</sub> passivation layer can enhance the resistance against negative bias illumination stress (NBIS), making it reliable for the realistic operation in flat panel displays.

#### 1. Introduction

Recently, the amorphous indium zinc tin oxide (a-IZTO) has attracted a lot of attention to compete with the amorphous indium gallium zinc oxide (a-IGZO) as the channel layer material of thin film transistor (TFT) for next generation flatpanel displays. According to its material characteristics, the higher carrier mobility can be obtained due to the better conductive path for electrons by replacing the tin cation from gallium cation. According to the previous studies, oxide TFTs including a-IGZO TFTs are sensitive to the oxygen or moisture during the bias stability test, resulting in threshold voltage shift. For example, the oxygen species absorbed from ambient atmosphere can capture electrons in the metal oxide based active layer to generate the negatively charged species, by the following equation:

$$O_{2(g)} + e^- \leftrightarrow O_{2(s)}^- \tag{1}$$

, where e- denotes electrons, and  $O_{2(g)}$  and  $O_{2(s)}$  represent the neutral and charge oxygen molecules in back channel of a-IGZO TFTs. While the negative space charges  $O_{2(s)}$  generate, the positively shift of threshold voltage can be observed. Hence, the backchannel passivation layer (BPL) for oxide TFTs is necessary to suppress environmental factors. Besides, the materials and BPL deposition processes are another important topics and should be optimized for oxide TFTs technology. Choiat el. reported that silicon dioxide (SiO<sub>2</sub>) and silicon nitride (SiN<sub>x</sub>) deposited by plasma-enhanced chemical vapor

In the present work, the effect of backchannel passivation layer on a-IZTO TFT has been well discussed. The  $SiO_2$  and  $Al_2O_3$  passivation layers were fabricated by PECVD and plasmaenhanced atomic layer deposition (PE-ALD), respectively. The electrical characteristic of a-IZTO TFTs with BPL have been optimized through adjusting process parameters such as reaction precursors, gas flow rate and deposition temperatures. From secondary ion mass spectrometer (SIMS) analysis, the proposed mechanism of device performance degradation for the passivated a-IZTO TFT can be confirmed. In addition, the environment stability and bias reliability of passivated a-IZTO TFTs have also been well discussed with the corresponding mechanism.

#### 2. Experiment

The inverted-staggered a-IZTO TFT devices with passivation layer were fabricated for this study with following procedures.

deposition (PECVD) may cause the degradation of a-IGZO TFTs due to plasma-induced radiation damage at the back channel surface. In this case, the TFT devices perform lower mobility and larger hysteresis window. In addition, the remaining of the hydrogen from the incompletely dissociated precursor may diffuse into the a-IGZO channel as the shallow donor states resulting in the conducting electrical performance or thermal instability of TFT devices. However, even though there are some literatures showed that the a-IZTO TFTs could deposit at room temperature and exhibit good electrical performance and reliability, the study on environment stability is still lacking. The influence of passivation layer on this high carrier concentration material of IZTO thin film is unclear.

<sup>&</sup>lt;sup>a</sup> Department of Photonics and Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu 30010, Taiwan. Email:ptliu@mail.nctu.edu.tw; beachyboys.eo96@a2.nctu.edu.tw; Tel:+886-3-5712121-52994

b. Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan. Email: churshyang@amail.com

Si wafer

**ARTICLE**

Published on 03 November 2016. Downloaded by Newcastle University on 07/11/2016 07:10:24

DOI: 10.1039/C6RA22423G **Journal Name**

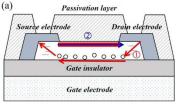

SiO2 or Al2O3 Passivation layer ITO Source electrode Drain electrode a-IZTO Active layer Thermal oxide (SiO<sub>2</sub>) Gate electrode

Fig. 1. Schematic structure of a-IZTO TFT device with backchannel passivation layer.

For the first step, a 100-nm-thick thermal oxide as the gate insulator layer was firstly grown on the n+ heavily doped silicon substrates by a horizontal thermal furnace after a RCA clean process. Then, the 30-nm-thick a-IZTO channel layers were deposited by using RF magnetron sputtering at 70 W using IZTO target of In:Sn:Zn:O =4:4:1:15 at.%. The sputtering process pressure was carried out at 3 mTorr with the argon and oxygen flow rate of 10 sccm and 0.1 sccm, respectively. The source and drain electrodes of 100-nm-thick ITO were formed by RF magnetron sputtering at 50 W in argon atmosphere with a flow rate of 10 sccm. The process pressure was also carried out at 3 mTorr. After the fabrication of bottom gate a-IZTO TFTs, the SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> thin films were sequentially capped on the devices to act as the passivation layer. The 50-nm-thick SiO<sub>2</sub> passivation layers were deposited by PECVD at 25 W with silane (SiH<sub>4</sub>) and nitrous oxide ( $N_2O$ ) flow rate of 9 sccm and 710 sccm, respectively. The pressure and temperature was fixed at 1000 mTorr and 300 °C. In order to reduce the remaining hydrogen in SiO2 layers, another deposition condition was adopted with the mixture precursor of tetraethyl orthosilicate (TEOS) and oxygen (O2), where the gas flow rate was fixed at 50 sccm and 300 sccm, respectively. For better TEOS dissociation, the process temperature was raised to 350 °C with a power of 40W. The 15-nm-thick Al<sub>2</sub>O<sub>3</sub> passivation layers were deposited under the plasma environment composed of trimethylaluminum (TMA) and O<sub>2</sub> by ALD process at 250 °C. The reaction pressure was carried out at 10mTorr. The via to the source/drain electrodes were patterned and then etched by high density plasma reactive etching (HDPRIE) with mixture gases of Ar/CF4 for SiO2 and  $Ar/BCl_3/Cl_2$  for  $Al_2O_3$ . Figure 1 illustrates the cross-sectional schematic diagrams of the fabricated a-IZTO devices. Finally, all of devices were thermally annealed under the oxygen atmosphere with flow rate of 80 sccm at several temperatures for an hour. Both the channel width and length of devices were varied from 1000 to 200  $\mu m$ . The electrical properties were measured using Keithley SCS 4200 semiconductor parameter analyzer in the dark chamber at room temperature. In addition, the 30-nm-thick a-IZTO thin films capped by the passivation layers were deposited on the SiO<sub>2</sub>/Si substrate with different annealing conditions to analyze the chemical composition by secondary ion mass spectrometer (SIMS).

#### 3. Results and discussion

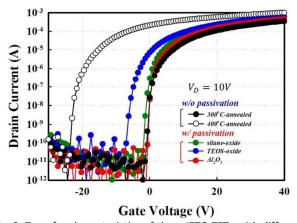

To compare the backchannel passivation effects on the a-IZTO TFTs, the transfer characteristic (I<sub>D</sub>-V<sub>G</sub> curve) of TFT

Fig. 2. Transfer characteristics of the a-IZTO TFTs with different types of passivation layers for comparison. The curve with black and white symbol shows the un-passivated a-IZTO TFTs after annealing process at 300 °C and 400 °C, respectively.

Table 1. Summary of the electrical parameters extracted from a-IZTO TFT devices with and without backchannel passivation

| 147010                             |                     |                       |                 |

|------------------------------------|---------------------|-----------------------|-----------------|

| Optimized condition                | V <sub>th</sub> (V) | Mobility<br>(cm²/V.s) | s.s. (V/decade) |

| Passivation<br>free (300°C)        | -0.72               | 20.46                 | 0.32            |

| Passivation<br>free (400°C)        | -22.76              | 37.9                  | 0.40            |

| Silane SiO <sub>2</sub>            | -1.92               | 27.51                 | 0.41            |

| TEOS SiO <sub>2</sub>              | -6.48               | 27.09                 | 0.51            |

| ALD Al <sub>2</sub> O <sub>3</sub> | -0.88               | 30.16                 | 0.34            |

devices with different kinds of BPL processes are shown in Fig. 2. The electrical parameters extracted from each device are shown in Table 1. The black and white circle symbol shows the performance of the a-IZTO TFT without BPL annealed at 300 °C and 400 °C for 30 min, respectively. In our previous study, 6 the higher annealing temperature can improves both electrical characteristic and reliability of devices, however, leading to a significant V<sub>th</sub> shift negatively. This issue can be released in the BPL a-IZTO TFT devices with a more positive  $V_{th}$  around 0 V.

The BPL thin film, including SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>, can play a role to prevent weakly bonding oxygen from desorbing out to the environment from a-IZTO channel during annealing. Among these devices with BPL, the Al<sub>2</sub>O<sub>3</sub>-passivated a-IZTO TFTs perform the superior electrical characteristics with mobility of 30.16 cm<sup>2</sup>/Vs and subthreshold slope (s.s.) of 0.34 V/decade. This result can be attributed to the reduction of local tail states in a-IZTO channel layer from around  $10^{18} eV^{-1}cm^{-3}$  to around  $10^{17} \mbox{eV}^{-1} \mbox{cm}^{-3}$  , extracted from  $\mbox{I}_{\mbox{\scriptsize D}}\mbox{-V}_{\mbox{\scriptsize G}}$  curve at various measurement temperatures. In addition, the  $I_D\text{-}V_G$  curve is nearly overlapped with that of the one without BPL annealed at 300 °C with the similar  $V_{\text{th}}$  of -0.88 V, which indicates the ALD process provides the radiation-free damage without forming oxygen vacancies at the back a-IZTO channel. On the other hand, the effect of ion bombardment from PECVD process makes the V<sub>th</sub> shifted to a negative value, especially

Published on 03 November 2016. Downloaded by Newcastle University on 07/11/2016 07:10:24

20

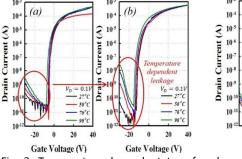

Fig. 3. Temperature-dependent transfer characteristics of a-IZTO TFT with (a) silane-SiO<sub>2</sub>-passivated backchannel layer, (b) TEOS-SiO<sub>2</sub>-passivated backchannel layer, and (c) ALD-Al<sub>2</sub>O<sub>3</sub>passivated backchannel layer.

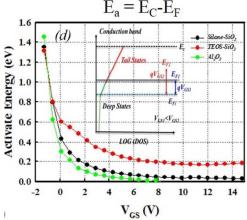

Fig. 3 (d) The plot of activated energy (Eact) versus gate voltage (Vg) for a-IZTO TFTs with different types of backchannel passivation layers

significant for the case of TEOS-SiO<sub>2</sub> BPL. The cause of obvious negative shift can be excluded from the hydrogen incorporation due to the fewer residual hydrogen contained in the TEOS-SiO<sub>2</sub> process.

Fig. 3(a), (b) and (c) show the transfer characteristic of a-IZTO TFTs with BPL measured at 25°C, 50 °C, 70 °C and 90 °C. The  $V_{th}$  value shifts negatively and the off-current ( $I_{off}$ ) increases with increasing measurement temperatures from 25°C to 90 °C. This phenomenon can be described by the thermally activated Arrhenius model, where it is assumed that thermally activated electrons from deep level trap sites into the conduction band move quickly toward the drain electrode due to a lateral electrical field. The drain current (ID) is activated thermally and described as following equation8:

$$I_D = I_O \exp\left(\frac{-E_{act}}{kT}\right) \tag{2}$$

where the Io is the pre-factor, k is the Boltzmann constant, T is the absolute temperature K,  $E_{\text{act}}$  is the activated energy which is defined as  $E_{act}$  =  $E_{c}$  - $E_{f}$ . The conductance activation energy (Eact) calculated from the Arrhenius plot is used to approximately

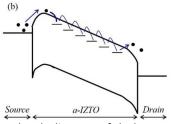

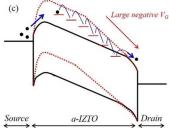

Fig. 4(a) The schematic mechanism for leakage current of a-IZTO TFT with backchannel passivation layer at turn-off region.

Fig. 4(b)Energy band diagram of leakage conduction for temperature-dependent

Fig. 4(c) bias-dependent behavior

Table 2. The value of slope Eact verse V<sub>G</sub> for a-IZTO TFT devices with backchannel passivation layers

| Passivation Type                | Silane-SiO <sub>2</sub> | TEOS-SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> |

|---------------------------------|-------------------------|-----------------------|--------------------------------|

| Slope                           |                         | 2                     |                                |

| ( ΔE <sub>2</sub>  / ΔVoltage ) | 0.29                    | 0.25                  | 0.38                           |

track the position of Fermi level ( $E_{act}$  =  $E_c$  - $E_f$ ) in the energy band gap, where E<sub>c</sub> and E<sub>f</sub> are defined as conduction band edge and Fermi energy, respectively. Therefore, the activation energy can be determined from the curve of In(ID) versus reciprocal of temperature (1/T) by measuring the drain-source current at different temperature with the same drain-source voltage, the activation energy can be extracted with the following equation:

$$\ln(I_{D2}) - \ln(I_{D1}) = \frac{-E_{act}}{kT} \cdot \left(\frac{1}{T_2} - \frac{1}{T_1}\right)$$

(3)

For TFT operation, most of the charge induced by the gate voltage goes into the tail states with a small fraction going into the conduction band, and the E<sub>F</sub> moves closer to the edge of the conduction band with increasing gate voltage. Hence, the ease of the E<sub>F</sub> movement is determined by the distribution of the tail states. The faster moving E<sub>F</sub> with gate voltage means total trap density is lower due to less shallow trap in tail states. 10 The E<sub>act</sub> versus gate voltage of passivated a-IZTO TFTs is shown in Fig.

**ARTICLE**

Published on 03 November 2016. Downloaded by Newcastle University on 07/11/2016 07:10:24

DOI: 10.1039/C6RA22423G

Journal Name

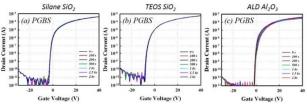

Fig. 5 Transfer characteristics of a-IZTO TFT with (a) silnae-SiO<sub>2</sub>passivated backchannel passivation layer, (b) TEOS-SiO<sub>2</sub>passivatedand backchannel passivation layer passivated backchannel passivation layer under positive gate bias stress (PGBS).

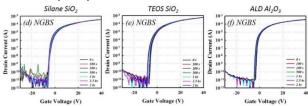

Fig. 5 Transfer characteristics of a-IZTO TFT with (d) silnae-SiO<sub>2</sub>-passivated backchannel passivation layer, (e) TEOS-SiO<sub>2</sub>passivatedand backchannel passivation layer passivated backchannel passivation layer under negative gate bias stress (NGBS).

3(d). Table 2 shows the slope of  $E_{\text{act}}$  change verse  $V_{\text{G}}$ . The average declined slopes of E<sub>act</sub> for Al<sub>2</sub>O<sub>3</sub>-passivated a-IZTO TFTs is steeper than others, in other words, E<sub>F</sub> can approach E<sub>C</sub> easily due to the lower shallow trap in tail states indicated that a-IZTO thin film with Al<sub>2</sub>O<sub>3</sub> passivation layer can reduced the trap density more than others. Furthermore, the bias and temperature dependence on the leakage current was observed in a-IZTO TFTs with PECVD-processed BPL. In general, the leakage conduction paths in the bottom-gate TFT devices are formed at the front and backchannel layers, respectively, shown in Fig. 4(a). The conduction path occurred at the front channel can be attributed to the Poole-Frenkel leakage current through the accumulated holes with high negative V<sub>G</sub> bias and high positive V<sub>D</sub> bias as shown in the path 1 in Fig. 4(a). The holes are generated at the gate-drain overlap region by Poole-Frenkel field enhanced thermionic emission. 11 From previous literatures, however, the amount of the hole carriers in oxide semiconductors is negligible due to the atomic configuration and electronic structure. 12 This indicates the path 1 might not be the leakage path in this study. We speculate the conduction path for the leakage current to be from the back channel with large defect states, as shown in the path 2 of Fig. 4(a). In the plasma-related BPL process, a lot of subgap states are easily formed at bakchannel layer due to the ion bombardment effect and resultantly trapping electrons which could be thermally excited to the conduction band and hopping to the drain electrode, as shown in Fig. 4(b). With higher measuring temperature, the more thermal electrons could be generated thermally and conductive along the path 2. Especially, a higher electric field across the gate-drain overlap region will even enhance the leakage conduction, as the negative V<sub>G</sub> bias increased and raised up the potential energy of a-IZTO layer, as shown in Fig. 4(c).

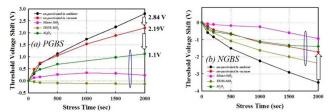

Fig. 6  $V_{\text{th}}$  shift of a-IZTO TFTs with backchannel passivation layers as a function of gate bias stress durations for (a) PGBS test and (b) NGBS.

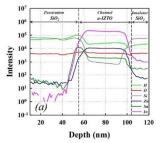

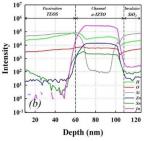

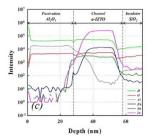

Fig. 7 SIMS depth profiles of a-IZTO films capped by (a) silnae-SiO<sub>2</sub> thin film,

Fig. 7(b) TEOS-SiO<sub>2</sub> thin film,

and Fig. 7(c) Al<sub>2</sub>O<sub>3</sub> thin films on Si substrate.

The bias reliability test of the a-IZTO TFTs with BPL was also conducted in this study. Figures 5(a)-(c) and (d)-(f) show the transfer characteristic of a-IZTO TFT devices with BPL under positive gate bias stress (PGBS) and negative gate bias stress (NGBS), respectively. The device parameters including the mobility and s.s. all perform a similar value after bias reliability test, indicating no additional defect states created. The V<sub>th</sub> shift is shown in Fig. 6. In this measurement, an electric field of ±2.5MV/cm was applied to gate electrode and source/drain electrodes were grounded for 2000 sec at ambient environment.

RSC Advances Accepted Manuscript

Threshold Voltage Shift (V) -6 -8 -10 Under dark O- Passivation free -12 Silane SiO Under illumination -14 O- TEOS SiO O- ALD Al2O3 Silane SiO, -16 - TEOS SiO -18 - ALD Al,O -20 500 1000 1500 2000 **Stressing Time (Sec)**

Fig. 8 The  $V_{th}$  shifts versus stress time of a-IZTO TFTs with backchannel layers under NBIS test.

The gate bias stress measurement results for the passivationfree sample were under the atmosphere ambient and vacuum environment, while all TFT devices with passivation layers were measured under atmosphere ambient environment. It is clearly observed that the V<sub>th</sub> shift of the a-IZTO TFTs with BPL was smaller than the one without BPL with 2.84 V<sub>th</sub> shift. These results indicated that the BPL can effectively isolate the influences from the ambient. When the positive gate bias stress was applied, the absorption of oxygen species from ambient atmosphere occurs and then captures electrons in the a-IZTO channel layer to form negative charges, described by Eqn. (1). The additional generation of negative space charges will result in the positive V<sub>th</sub> shift. On the contrary, the effect of moisture absorption dominates the NBGS behavior by releasing electron and then forming positive space charges (H2O<sup>+</sup>) as well as leading to a negative V<sub>th</sub> shift. In PGBS test, the V<sub>th</sub> shift of a-IZTO TFT without BPL measured in vacuum is slightly smaller than that in ambient, indicating that the absorption of oxygen molecules from the atmosphere is certainly reduced in vacuum. Also, in Al<sub>2</sub>O<sub>3</sub>-passivated a-IZTO TFTs the  $O_{2(s)}$  species can also be isolated effectively by the backchannel passivation layer with a much smaller V<sub>th</sub> shift of 1.12 V. The similar result is also observed in NGBS test. The passivation layer can also prevent the influence of moisture in the environment from shifting the  $V_{th}$  to a negative value. We believe that the IZTO device with TEOS SiO<sub>2</sub> suffered from a certain extent water vapor absorption from the ambient environment. In other words, the TEOS SiO<sub>2</sub> compared with silane SiO2 is not suitable to be the passivation layer of IZTO TFTs to isolate the moisture from the ambient. As a result, the passivation-free sample stressed under the vacuum need not to have the biggest threshold voltage shift under negative bias stress because the moisture absorption in vacuum hardly occurs. However, under PGBS, the slightly negative  $V_{\text{th}}$  shift is observed for the SiO2-passivated a-IZTO TFTs by PECVD process. This negative V<sub>th</sub> shift of SiO<sub>2</sub>-passivated TFT devices may be attributed to the hydrogen diffusion into the a-IZTO channel and explained by following equation: 12

,where H° is the neutral hydrogen atom from the PECVD process environment. The SiO<sub>2</sub> passivation layer tends to combine with oxygen atom in the a-IZTO channel to release a free carrier because of the stronger O-H bonds. During PGBS, the hydrogen incorporation at the back channel and reduce the energy difference between E<sub>F</sub> and E<sub>C</sub>. In addition, the E<sub>F</sub> is subjected to be pinned due to the interface states within the a-IZTO and this energy bands are modified due to the Fermi level pinning not being recovered even when the PBGS is terminated.<sup>13</sup> This phenomenon can be ignored in the Al<sub>2</sub>O<sub>3</sub>passivated a-IZTO TFTs with fewer hydrogen diffusions from passivation layer. SIMS analysis can be performed to confirm the proposal, as shown in Fig. 7. It is observed that the signal intensity of hydrogen in the SiO<sub>2</sub>-passivated TFT sample is half order of magnitude higher than that in Al<sub>2</sub>O<sub>3</sub>-passivated sample at the interface between a-IZTO channel and the passivation layer.

The negative bias illumination stress (NBIS) of a-IZTO TFTs with BPL is also further studied. A gate bias stresses of -25 V and blue light ( $\lambda = 465 \text{ nm}$ ) at a power density of 0.2 mW/cm<sup>2</sup> were applied to TFT devices in the NBIS testing. Figure 8 shows the V<sub>th</sub> shift of a-IZTO TFTs versus stress time during the NBIS test. It is found the V<sub>th</sub> shift of TFT devices under NBIS is much larger than NBS. The electrical degradation mechanism is related to high density of oxygen deficiencies (Vo) corresponded to the deep level states located near the VBM. These defect states can be photo-excited to the ionized oxygen deficiencies (Vo+, Vo2+) and accumulated to the interface by gate electrical field. 14 Another mechanism for NBIS degradation is about the photo-desorption of oxygen species at the surface of channel layer. <sup>15</sup> Under the light illumination, the oxygen species donates the free electron in the conduction band, which enhances the conductivity. It is obviously that the passivated a-IZTO TFTs have a superior NBIS reliability with less than 10 V of negative V<sub>th</sub> shift compared to the un-passivated devices, which indicates the deep level defect states of channel can be eliminated by backchannel passivation process. As for the sample of Al<sub>2</sub>O<sub>3</sub>-passivated a-IZTO TFT, O<sub>2</sub> plasma during the passivation layer deposition re-oxidizes the a-IZTO channel layer and reduces the oxygen deficiencies. In addition, the Al<sub>2</sub>O<sub>3</sub> passivation layer could effectively isolate the oxygen absorption on the a-IZTO surface and prevent photodesorption behavior. Therefore, a-IZTO TFT with Al<sub>2</sub>O<sub>3</sub> shows the most stable electrical characteristics than others. This can be inferred the ALD method can provide a damage-free process avoiding the ion bombardment during film deposition and maintains the in-diffusion of radical oxygen species into the back surface region of the IZTO channel.1

#### 4. Conclusions

The characteristics of a-IZTO TFTs with passivation layers have been studied in this work. The electrical degradation of TFT devices after using PECVD  ${\rm SiO_2}$  as passivation layer is dominated by oxygen vacancy near the back channel interface, which is created by ion bombardment effect. Besides, PECVD  ${\rm SiO_2}$  process will cause hydrogen incorporation into a-IZTO

**ARTICLE**

DOI: 10.1039/C6RA22423G Journal Name

channel layer and results in the negative threshold voltage shift under gate bias stressing test. The a-IZTO TFT with PE-ALD Al<sub>2</sub>O<sub>3</sub> passivation layer can prevent from effects of ion bombardment and hydrogen diffusion to the backchannel interface. From the results of extracted activation energy (Eact), the Al<sub>2</sub>O<sub>3</sub> passivation layers can effectively reduce the trap density in localized tail states, which enhanced the mobility of a-IZTO TFTs. Furthermore, ambient stability and electrical reliability under light illumination can be thereby enhanced.

#### **Acknowledgements**

The authors would like to thank the Ministry of Science and Technology of the Republic of China, Taiwan for financially supporting this research under Contract No. MOST 103-2221-E-009-010-MY3. Also, this work was performed at National Nano Device Laboratories, Taiwan, R.O.C.

#### Notes and references

Published on 03 November 2016. Downloaded by Newcastle University on 07/11/2016 07:10:24

- 1. J. S. Park, J. K. Jeong, H.-J. Chung, Y. G. Mo, and H. D. Kim, Appl. Phys. Lett., 2008, 92, 072104.

- 2. S. H. Choi, J. H. Jang, J. J. Kim, and M. K. Han, Electron Device Lett., 2012, 33, 381.

- 3. H. Godo, D. Kawae, S. Yoshitomi, T. Sasaki, S. Ito, H. Ohara, H. Kishida, M. Takahashi, A. Miyanaga, and S. Yamazaki, Japanese Journal of Applied Physics, 2010, 49, 03CB04.

- 4. C. Y. Lin, C. W. Chien, C.-H. Wu, H. H. Hsieh, C.-C. Wu, Y. H. Yeh, C.-C. Cheng, C.-M. Lai, and M.-J. Yu, Transactions On Electron Devices, 2012, 59, 1701.

- 5. J. H. Song, K. S. Kim, Y. G. Mo, R. Choi, and J. K. Jeong, Electron Device Letters, 2014, 35, 853.

- 6. C. S. Fuh, P. T. Liu, W. H. Huang, and Simon M. Sze, Electron Device Letters, 2014, 35, 1103.

- 7. K. Hwan Ji, J. I. Kim, H. Y. Jung, S. Y. Park, Y.-G. Mo, J. H. Jeong, J.-Y. Kwon, M. K. Ryu, S. Y. Lee, R. Choi, and J. K. Jeong, Journal of the Electrochemical Society, 2010, 157, H983.

- 8. A. Sato, K. Abe, R. Hayashi, H. Kumomi, K. Nomura, T. Kamiya, M. Hirano, and H. Hosono, Applied Physics Letters, 2009, 94,

- 9. C. T. Tsai, P. T. Liu, T. C. Chang, C. W. Wang, P. Y. Yang and F. S. Yeh, Electron Device Lett., 2007, 28, 584.

- 10. K. Takechi, M. Nakata, T. Eguchi, H. Yamaguchi, and S. Kaneko, Japanese Journal of Applied Physics, 2009, 48, 011301.

- 11. Y. Kuo, Thin Film Transistors-Material and Processes, vol. 1, Kluwer Academic Publishers, U.S.A., 2004.

- 12. T. Kamiya, K. Nomura, and H. Hosono, Journal of Display Technology, 2009, 5, 468.

- 13. M. K. Ryu, S. H. K. Park, C. S. Hwang, and S. M. Yoon, Solid-State Electronics, 2013, 89, 171.

- 14. K. Nomura, T. Kamiy, and H. Hosono, Thin Solid Films, 2012,

- 15. S. Yang, D.-H. Cho, M. K. Ryu, S. H. K. Park, C. S. Hwang, J. Jang, and J. K. Jeong, Applied Physics Letters, 2010, 96, 213511.

- 16. S. Yang, K. H. Ji, U. K. Kim, C. S. Hwang, S. H. K. Park, C.-S.

- Hwang, J. Jang, and J. K. Jeong, 2011, 99, 102103.