# Investigation of Electrical Characteristics on Surrounding-Gate and Omega-Shaped-Gate Nanowire FinFETs

Yiming Li, Member, IEEE, Hung-Mu Chou, and Jam-Wem Lee

Abstract-In this paper, electrical characteristics of small nanowire fin field-effect transistor (FinFET) are investigated by using a three-dimensional quantum correction simulation. Taking several important electrical characteristics as evaluation criteria, two different nanowire FinFETs, the surrounding-gate and omega-shaped-gate devices, are examined and compared with respect to different ratios of the gate coverage. By calculating the ratio of the on/off current, the turn-on resistance, subthreshold swing, drain-induced channel barrier height lowing, and gate capacitance, it is found that the difference of the electrical characteristics between the surrounding-gate (i.e., the omega-shaped-gate device with 100% coverage) and the omega-shaped-gate nanowire FinFET with 70% coverage is insignificant. The examination presented here is useful in the fabrication of small omega-shaped-gate nanowire FinFETs. It clarifies the main difference between the surrounding-gate and omega-shaped-gate nanowire FinFETs and exhibits a valuable result that the omega-shaped-gate device with 70% coverage plays an optimal candidate of the nanodevice structure when we consider both the device performance and manufacturability.

Index Terms—Coverage ratio, device structure, fabrication, fin field-effect transistor (FinFET), gate capacitance, nanodevice, nanowire, omega-shaped-gate, on/off ratio, process technique, quantum correction model, semiconductor devices, subthreshold swing (SS), surrounding gate, three-dimensional (3-D) simulation, turn-on resistance.

# I. INTRODUCTION

SILICON-ON-INSULATOR (SOI) devices have recently been of great interest and relatively present better scaling-down properties than that of conventional bulk metal—oxide—semiconductor field-effect transistors (MOSFETs) [1]—[4]. Double-gate SOI devices have been proposed and found more attractive electrical characteristics than that of single-gate SOI devices [5]—[21]. They inherently have good suppression of short-channel effects (SCEs), high transconductance, and ideal subthreshold swing (SS). In order

Manuscript received August 15, 2004; revised January 10, 2005. This work was supported in part by the National Science Council of Taiwan under Contract NSC-93-2215-E-429-008 and Contract NSC-94-2752-E-009-003-PAE, by the Ministry of Economic Affairs, Taiwan, R.O.C., under Contract 93-EC-17-A-07-S1-0011, and by the Taiwan Semiconductor Manufacturing Company under a 2004–2005 grant. An earlier version of this paper was presented at the 2004 IEEE Conference on Nanotechnology.

Y. Li and H.-M. Chou are with the Department of Communication Engineering and the Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymli@faculty.nctu.edu.tw).

J.-W. Lee is with the Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TNANO.2005.851410

to further reduce the SCEs, promising device structures, such as the fin field-effect transistor (FinFET), multiple-gate FinFETs, and surrounding-gate nanowire FinFETs have been proposed, fabricated, and demonstrated their fascinating device characteristics [5]–[21]. However, these structures cannot be directly fabricated with advanced fabrication processes and have inherently encountered several difficulties [7], [8], [11]. Considering issues of the mass production, omega-shaped-gate nanowire FinFET structures [5], [6], [9], [20] have been proposed to make a compromise between the device performance and manufacturability. Device simulation with different physical aspects and computational models has been widely proposed and used in studying diverse semiconductor nanodevices [14], [18], [19], [21]–[58]. However, theoretical calculation and comparison of the surrounding-gate and omega-shaped-gate nanowire Fin-FETs using a unified simulation model have never been well drawn. In addition, a quantitative evaluation of the difference on these devices' performance is still unclear. We believe that any theoretical examinations on the surrounding-gate and omega-shaped-gate nanowire FinFETs will provide interesting information for designing any novel structures and benefits the fabrication of integrated circuits with using these advanced nanodevices.

In this paper, electrical characteristics of ultrasmall nanowire FinFETs are numerically explored using a developed quantum correction simulation. Based on a multidimensional device simulation [41]–[54], the ratio of the on/off current, turn-on resistance  $(R_{\text{out}})$ , SS, drain induced barrier lowering (DIBL), and gate capacitance  $C_G$  [59], [60] are calculated and compared for a 5-nm nanowire FinFET with the surrounding-gate and omega-shaped-gate structures, respectively. Device with the surrounding-gate structure means it has 100% ratio of the gate coverage. The coverage changing from 70% to 80% for the device with the omega-shaped-gate structure is comprehensively explored in this study. The diameter of the 5-nm nanowire field-effect transistor (FET) is set to be 10 nm and the thickness of the gate oxide is with 1 nm. According to our calculation, it is found that the characteristic difference between the surrounding-gate and omega-shaped-gate FinFETs with 70% coverage is insignificant. However, the first structure possesses slightly better DIBL effect than that the latter one with different coverage ratios. Taking the thickness of the silicon film into consideration, the omega-shaped-gate device with 70% gate coverage provides an attractive alternative in considering both the device performance and manufacturability. Overall, the omega-shaped-gate FinFET with a coverage that

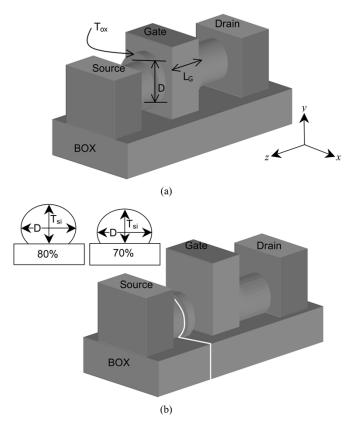

Fig. 1. Illustrations of the cylindrical nanowire FinFET with: (a) the surrounding-gate structure and (b) the omega-shaped-gate structure.  $L_G$  is the channel length,  $T_{\rm ox}$  is the thickness of oxide, and D is the diameter of the nanowire FinFET. The two insets, cutting along the white line in (b), show the cross sections of the structure with 70% and 80%, respectively, where  $T_{\rm si}$  is the thickness of the channel film.

is larger than 70% may demonstrate a similar performance to the surrounding-gate FinFET. Our examination presented here clarifies the geometric effects on the characteristic difference between the surrounding-gate and omega-shaped-gate FinFETs. It is useful to develop new fabrication techniques for ultrasmall omega-shaped-gate nanowire FinFETs.

This paper is organized as follow. In Section II, we state the investigated device structure and simulation. In Section III, we calculate several important electrical characteristics of the studied device structures. Comparison and discussion between the different device structures with various coverage ratios are included in this section. Section IV draws conclusions and suggests future works.

## II. DEVICE STRUCTURE AND COMPUTATIONAL MODEL

Computationally experimental structures are shown in Fig. 1. These two devices are the surrounding-gate and omega-shaped-gate nanowire FinFETs, respectively. An omega-shaped-gate nanowire FinFET with 100% gate coverage is automatically equivalent to the surrounding-gate nanowire FinFET. To simplify the investigated problem and clarify the main effect of the geometric variation on the electrical characteristics for the small nanowire FinFET, the simulated FinFETs are with the same diameter D=10 nm, the gate length  $L_G=5$  nm, the channel is with an uniform doping  $10^{18} {\rm cm}^{-3}$ , the source/drain doping is with  $5\times 10^{19} {\rm cm}^{-3}$  uniformly, the oxide thickness  $T_{\rm ox}=1$  nm,

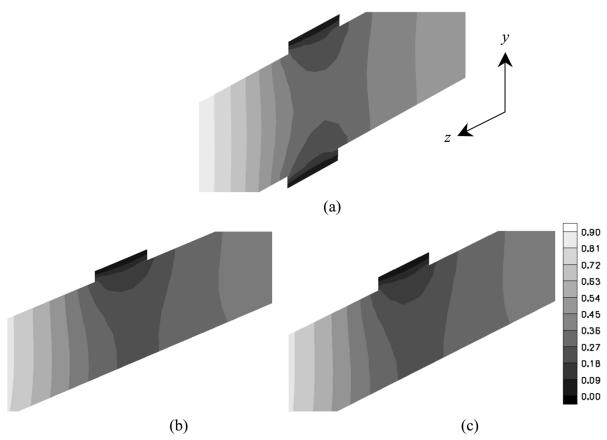

Fig. 2. Electrostatic potential on the channel region of the 5-nm nanowire FinFET with: (a) the surrounding-gate structure (b) the 80% omega-shaped-gate structure, and (c) the 70% omega-shaped-gate structure, respectively. The bias condition is  $V_G=0.8~{\rm V}$  and  $V_D=0.05~{\rm V}$ .

and the midgap material, such as TiN, is chosen as the gate material. Today, the channel length of semiconductor devices is in the nanoscale regime; it becomes necessary to include quantum mechanical effects when modeling any FET's terminal property [14], [18], [19], [21]–[55], [58]. There have been several approaches to the modeling of quantum mechanical effects, such as quantum mechanical methodologies and quantum corrections to the classical transport models [18], [19], [21]–[55], [58]. A full quantum mechanical model physically provides one of the most accurate ways to simulate nanodevices, but it is costly in the technology computer-aided design (TCAD) simulation of multidimensional deep submicrometer and nanoscale devices [22].

To focus on exploring the fluctuation problem of the electrical characteristics for optimal nanodevice structures, phenomenological quantum correction model, a density-gradient equation [41]–[54] together with the classical three-dimensional (3-D) drift-diffusion model [56], [57] is adopted and solved numerically in this study. A carefully calibrated density-gradient model [43]-[47] has attracted more and more attention and successfully demonstrates its validity for efficient modeling of the quantum mechanical effects in a TCAD simulator using first-order quantum corrections [41]-[54]. This simulation quantitatively predicts the main tendency of electrical and physical properties for the examined device structures. Full quantum mechanical methodologies definitely will input more accurate estimation on the characteristics, but it is believed that our simulation will not be significantly altered. The density-gradient modeling approach is computationally effective for incorporating the quantum mechanical effect in a multidimensional nanodevice TCAD simulation [22], [49], [51], [52].

Fig. 3. Electrostatic potential on channel regions from the source to drain for the 5-nm nanowire FinFET with: (a) the surrounding-gate structure, (b) the 80% omega-shaped-gate structure, and (c) the 70% omega-shaped-gate structure, respectively. The bias condition is  $V_G=0.0~{\rm V}$  and  $V_D=0.8~{\rm V}$ .

To calculate the numerical solution of the multidimensional density-gradient model [41]–[52] for the studied device structures, shown in Fig. 1, a robust two-dimensional (2-D)/3-D device simulation program is developed. Developing this computational prototype is mainly based on our recent work on nanodevice simulations [53]–[57]. Firstly, we decouple the coupled partial differential equations (PDEs); each decoupled PDE is approximated with the finite volume method over nonuniform mesh [51]–[57]. The corresponding system of the nonlinear algebraic equations is then solved with the mixed monotone iteration and Newton's iteration methods [57]. Iterations will be terminated and postprocesses will be performed when the specified stopping criteria for inner and outer iteration loops are satisfied, respectively.

### III. RESULTS AND DISCUSSION

Figs. 2(a)–(c) and 3(a)–(c) are the computed electrostatic potential for the simulated nanowire FinFET with the surrounding gate, omega-shaped gate with a coverage ratio of 80%, and (c) omega-shaped gate with a coverage ratio of 70%, respectively. The difference of the on state is observed in the channel region when  $V_G=0.8~\rm V$  and  $V_D=0.05~\rm V$  is shown in Fig. 2(a)–(c). Moreover, for  $V_G=0.0~\rm V$  and  $V_D=0.8~\rm V$ , the contours of the off-state potential are shown in Fig. 3(a)–(c). It is found from those figures that gate electrodes of the omega-shaped-gate devices have a good controllability at the undercut region. Owing to the good controlling of the undercut regime, the on-current degradation of the omega-shaped-gate device does not follow

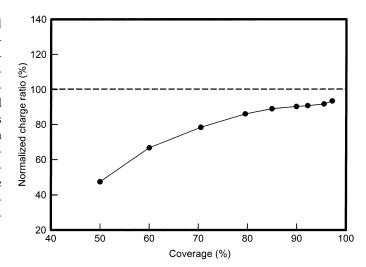

Fig. 4. Normalized ratio of the inversion charge versus the gate coverage. The coverage ratio varies from 50% to 97%. The normalization is with respect to the charge of the surrounding-gate nanowire FinFET under  $V_D=0.05~\rm V$  and  $V_G=0.8~\rm V$ .

the reduction of the gate coverage ratio. That is a reduction on the coverage ratio of the omega-shaped-gate nanowire Fin-FETs, which can only slightly influence the electrical characteristics of devices. As shown in Fig. 4, the plot of the charge ratio versus the coverage of the gate confirms the calculation results, as shown in Figs. 2 and 3. The devices are with  $V_D=0.0~\rm V$  and  $V_G=0.8~\rm V$ , where the calculated total charge is normalized with respect to the total charge of the surrounding-gate nanowire

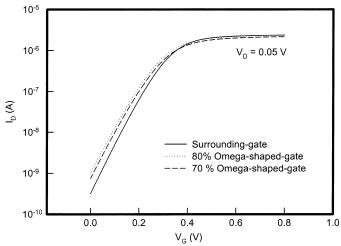

Fig. 5.  $I_D-V_G$  curves of the simulated 5-nm nanowire FinFET with the surrounding-gate and the omega-shaped-gate structures. The solid line is the result of the surrounding-gate device and the dotted and dashed lines are the results of the omega-shaped-gate device with 80% and 70% coverage ratios, respectively.

FinFET. It is found when the gate coverage varies from 50% to 70% that the slope of the normalized charge ratio is approximately 2 times larger than that of the gate coverage varying from 70% to 97%.

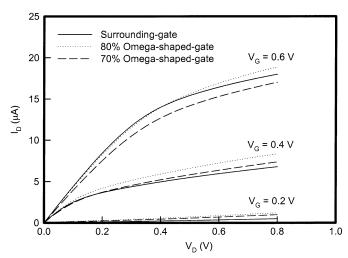

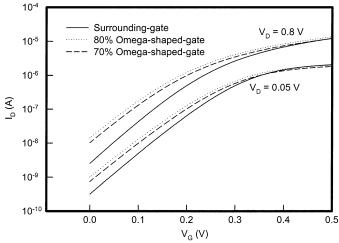

The potential distributions explain the  $I_D - V_G$  and  $I_D$  –  $V_D$  characteristics for both the surrounding-gate and the omegashaped-gate nanowire FinFETs, shown in Figs. 5 and 6, respectively. The  $I_D - V_G$  characteristics for the structures with different coverage ratios are shown in Fig. 5. Although the surrounding-gate nanowire FinFET has better characteristics over the off-state and the subthreshold condition, the on-state current for all the simulated structures are almost similar with respect to different coverage ratios. Moreover, the difference on the  $I_D\!-\!V_G$ and  $I_D - V_D$  characteristics between the surrounding-gate and omega-shaped-gate devices are quite small, e.g., the largest variation of the  $I_D - V_D$  characteristics at  $V_G = 0.6$  V and  $V_D = 0.8$ is approximately 10%, as shown in Fig. 6. The fluctuation of the drain current is acceptable when we take the difficulty of the fabrication into consideration. The ratio of the on/off current calculated from the transfer curves is summarized in Table I. The calculation is done by dividing the on-current level (i.e.,  $I_D$  at  $V_G = 0.8$  V and  $V_D = 0.05 \text{ V}$ ) to the off current level (i.e.,  $I_D$  at  $V_G = 0.0 \text{ V}$  and  $V_D = 0.8 \,\mathrm{V}$ ). The ratio of the on/off current is a major concerned factor in modern gigascale integrated-circuit design. The on current is strongly related to the switching speed and the off current is directly corresponding to the power consumption. Therefore, a higher ratio of the on/off current is preferred for improving the circuitry performance. According to the summarized data shown in Table I, it is found that the surrounding-gate nanowire FinFET has a slightly higher ratio of the on/off current than that of the omega-shaped-gate structures. Similarly, this can be explained due to the channel controllability for these structures, as shown in Figs. 2 and 3.

Based on numerical simulation, the SS property is also extracted and shown in Table I. The SS is defined as the gate voltage that has to be increased for enlarging a decade of subthreshold current [56], [57]. This property is highly correlated with the switching speed and the noise margin of the designed

Fig. 6.  $I_D-V_D$  curves of the simulated 5-nm nanowire FinFET with the surrounding-gate and the omega-shaped-gate structures.

circuit. It has been found that the SS of the surrounding-gate device is insignificantly lower than that of the others. That is, without considering the fabrication stability, the surroundinggate structure merely contributes a slight improvement on designing the digital circuit. The SS of the bulk devices traditionally is around 100 mV/decade. However, the SS of all explored devices shown here is much less than that of the bulk devices. The significant improvement will be mainly contributed to the fully depleted effects. We note that the SS is not simply proportional to the coverage ratio of the omega-shaped-gate structure. It is also affected by the thickness of the channel film. For device with a smaller coverage, it implies a thinner channel film thickness. For example, for an omega-shaped-gate structure with 80% coverage, its channel film thickness is equal to 9 nm. For the 70% coverage, it is 8 nm. Therefore, according to the argument of the channel film thickness, the omega-shaped-gate structure with 70% coverage has a smaller SS than that of the structure with 80% coverage. Furthermore, owing to the fully depleted effect, the threshold voltage of the nanowire FinFET devices is hardly to be adjusted by changing the channel doping concentration. Altering the work function will be one of the efficient ways for the modification of the threshold voltage. The midgap material will be the candidate for gate formation.

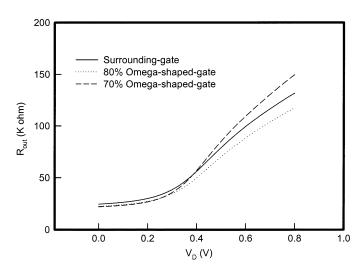

Output characteristics of the simulated structures with different coverage ratios could be explored from the results shown in Figs. 6 and 7, respectively. It can be found that the difference between the simulated structures with different coverage rations is very limited. Moreover, in comparing both the on current and output resistance, it will be concluded that the higher gate coverage ratio will result in better device characteristics. To make it more clear, the omega-shaped-gate device with a coverage ratio of 80% has a higher on-state current, but a lower output resistance than that of the 70% one. The on-state current discussed above is directly related to the operation speed of the digital circuit. On the other hand, the output resistance is an important element in designing the analog circuit, i.e., the higher the output resistance, the better the analog performance. Accordingly, we can summarize that the omega-shaped-gate devices with a different coverage ratio will be a promising approach to a different application category and should be subject

TABLE I COMPARISON OF THE CALCULATED ELECTRICAL CHARACTERISTICS FOR THE SIMULATED 5-nm Nanowire FinFET With two Different Gate Structures. DIBL Is Calculated as the Shift of  $V_t$ , Where  $V_t$  is the Threshold Voltage.  $C_G$  is Calculated When  $V_G=0.8~{\rm V}$

|                                   | Device with the            | Device with the             |                          |

|-----------------------------------|----------------------------|-----------------------------|--------------------------|

|                                   | surrounding-gate structure | omega-shaped-gate structure |                          |

| Gate coverage ratio               | 100%                       | 80%                         | 70%                      |

| SS                                | 87 mV                      | 97 mV                       | 93 mV                    |

| DIBL                              | 0.09 V                     | 0.115 V                     | 0.10 V                   |

| Log (Ratio of the on/off current) | 2.96                       | 2.21                        | 2.32                     |

| $C_{G}$                           | 4.28x10 <sup>-18</sup> F   | 3.8x10 <sup>-18</sup> F     | 3.68x10 <sup>-18</sup> F |

Fig. 7. Calculated characteristics of  $R_{\rm out}$  for the simulated 5-nm nanowire FinFET with the surrounding-gate and the omega-shaped-gate structures where  $V_G=0.6~{\rm V}$ .

to further optimization for the nanodevice fabrication. The effect of the drain induced channel barrier height lowering in the simulated structures with different coverage ratios are shown in Fig. 8 and also summarized in Table I. It is known that the DIBL effect will make the devices harder to be turned off at high drain biased situations. Additionally, this effect will also suffer the development of the corresponding equivalent-circuit compact model for integrated-circuit simulation and degrades the performance of analog integrated circuits. We are found that the surrounding-gate device has a better ability in suppressing the DIBL effect. Nevertheless, the improvement is still unpronounced in comparison with the difficulty coming from the manufacturability point-of-view.

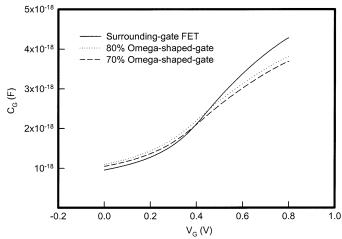

The plot of the  $C_G - V_G$  curve for the simulated structures is reported in Fig. 9 and the corresponding extracted output is listed in Table I. The simulation of  $C_G - V_G$  confirms the preliminary consistence of the electrical and physical properties of the surrounding-gate and omega-shaped-gate nanowire Fin-

Fig. 8. DIBL effects for the simulated 5-nm nanowire FinFET with the surrounding-gate and omega-shaped-gate structures.

Fig. 9. Plot of  $C_G$  versus  $V_G$  for the simulated 5-nm nanowire FinFET with the surrounding-gate and the omega-shaped-gate structures where the  $V_D=0.05~{

m V}$ .

FETs. Based on a rough estimation form the CV calculation shown in Fig. 9 and Table I, the capacitance reduction ratio is

only a half of the decrement on the gate coverage ratio. Those results also can be verified from the results shown in Fig. 4. It confirms that our previous simulations on the difference of electrical characteristics between the surrounding-gate and omegashaped-gate nanowire FinFETs are very subtle. It could be summarized that the degradation of the electrical characteristics on the omega-shaped-gate nanowire FinFETs is far less than the reduction of the coverage ratio. Consequently, in order to obtain both device performance and manufacturability of the nanowire devices, the omega-shaped-gate devices with 70% coverage will be an attractive candidate.

### IV. CONCLUSION

In this paper, we have preliminarily explored the difference of the electrical characteristics between the surrounding-gate and omega-shaped-gate (with different coverage ratios) nanowire FinFETs. Different simulation has been performed on a 5-nm nanowire FinFET with the developed simulation program, which is mainly based on a calibrated density-gradient equation together with the 3-D drift-diffusion model. According to our theoretical investigation, it has been found that the gate coverage ratio only contributes a small reduction on the output device performance. A higher gate coverage ratio does not necessarily promise better output characteristics. We believe that the work presented here is useful in the fabrication of the omega-shaped-gate nanowire FinFETs [7], [8], [61]. It exhibits a valuable result, which is that the omega-shaped-gate FinFET with 70% coverage is an optimal candidate of the nanodevice structure when we consider both device performance and manufacturability.

However, the physical model considered in the developed device simulation prototype can be improved and extended by using full quantum mechanical techniques. It is believed that full quantum mechanical modeling and simulation [58] will quantitatively provide more accurate estimation. We are currently developing a multidimensional full quantum mechanical simulation and also calibrating the developed 3-D quantum correction simulation with the fabricated 5- and 10-nm nanowire CMOS devices. Optimization of the geometric ratio of the strained omega-shaped-gate nanowire FinFETs with respect to the device's diameter and channel length is under investigation.

# REFERENCES

- [1] H. Wakabayashi, S. Yamagami, N. Ikezawa, A. Ogura, M. Narihiro, K. Arai, Y. Ochiai, K. Takeuchi, T. Yamamoto, and T. Mogami, "Sub-10-nm planar-bulk-CMOS devices using lateral junction control," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 7–10, 2003, pp. 20.7.1–20.7.4.

- [2] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, and D. Kyser, "FinFET scaling to 10 nm gate length," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 2002, pp. 251–254.

[3] X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski,

- [3] X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Sub 50-nm FinFET: PMOS," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 5–8, 1999, pp. 67–70.

- [4] M. V. Fischetti, "Scaling MOSFET's to the limit: A physicists's perspective," J. Comput. Electron., vol. 2, no. 2–4, pp. 73–79, Dec. 2003.

- [5] T. Park et al., "PMOS body-tied FinFET (omega MOSFET) characteristics," in Proc. Device Research Conf., Jun. 23–25, 2003, pp. 33–34.

- [6] T. Park et al., "Fabrication of body-tied FinFET's (omega MOSFET's) using bulk Si wafers," in VLSI Technology Tech. Symp. Dig., Jun. 10–12, 2003, pp. 135–136.

- [7] S. Xiong and J. Bokor, "Sensitivity of double-gate and FinFET devices to process variations," *IEEE Trans. Electron Devices*, vol. 50, no. 11, pp. 2255–2261, Nov. 2003.

- [8] B.-Y. Nguyen et al., "Integration challenges of new materials and device architectures for IC applications," in Proc. Int. Integrated Circuit Design and Technology Conf., May 17–20, 2004, pp. 237–243.

- [9] F.-L. Yang et al., "25 nm CMOS omega FETs," in Int. Electron Devices Meeting Tech. Dig., Dec. 8–11, 2002, pp. 255–258.

- [10] S. Watanabe, "Impact of three-dimensional transistor on the pattern area reduction for ULSI," *IEEE Trans. Electron Devices*, vol. 50, no. 10, pp. 2073–2080, Oct. 2003.

- [11] J.-T. Park and J.-P. Colinge, "Multiple-gate SOI MOSFETs: Device design guidelines," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2222–2229, Dec. 2002.

- [12] S. Monfray et al., "50 nm-gate all around (GAA)-silicon on nothing (SON)-devices: A simple way to co-integration of GAA transistors within bulk MOSFET process," in VLSI Technology Tech. Symp. Dig., Jun. 11–13, 2002, pp. 108–109.

- [13] J. P. Colinge, M. H. Gao, A. Romano-Rodriguez, H. Maes, and C. Claeys, "Silicon-on-insulator 'gate-all-around device'," in Int. Electron Devices Meeting Tech. Dig., Dec. 9–12, 1990, pp. 595–598.

- [14] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET's," *IEEE Electron Device Lett.*, vol. 18, no. 2, pp. 74–76, Feb. 1997.

- [15] J.-P. Colinge, "Multiple gate SOI MOSFETs," Solid State Electron., vol. 48, no. 6, pp. 897–905, Jun. 2004.

- [16] B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, and R. Chau, "High-performance fully depleted tri-gate CMOS transistors," *IEEE Electron Device Lett.*, vol. 24, no. 4, pp. 263–265, Apr. 2003.

- [17] R. Chau, B. Doyle, M. Doczy, S. Datta, S. Hareland, B. Jin, J. Kavalieros, and M. Metz, "Silicon nano-transistors and breaking the 10 nm physical gate length barrier," in *Proc. Device Research Conf.*, Jun. 23–25, 2003, pp. 123–126.

- [18] H. Majima, Y. Saito, and T. Hiramoto, "Impact of quantum mechanical effects on design of nanoscale narrowchannel n- and p-type MOS-FETs," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 3–5, 2001, pp. 051–054

- [19] M. J. Gilbert and D. K. Ferry, "Efficient quantum three-dimensional modeling of fully depleted ballistic silicon-on-insulator metal-oxide-semiconductor field-effect-transistors," J. Appl. Phys., vol. 95, no. 12, pp. 7954–7960, Jun. 2004.

- [20] J.-T. Park, J.-P. Colinge, and C. H. Diaz, "Pi-gate SOI MOSFET," IEEE Electron Device Lett., vol. 22, no. 8, pp. 405–406, Aug. 2001.

- [21] S. N. Balaban, E. P. Pokatilov, V. M. Fomin, V. N. Gladilin, J. T. Devreese, W. Magnus, and W. Schoenmaker, "Quantum transport in a cylindrical sub-0.1 μm silicon-based MOSFET," *Solid State Electron.*, vol. 46, no. 3, pp. 435–444, Mar. 2002.

- [22] T. Grasser and S. Selberherr, "Technology CAD: Device simulation and characterization," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 20, no. 1, pp. 407–413, 2002.

- [23] N. Sano, A. Hiroki, and K. Matsuzawa, "Device modeling and simulations toward sub-10 nm semiconductor devices," *IEEE Trans. Nanotechnol.*, vol. 1, no. 1, pp. 63–71, Dec. 2002.

- [24] A. Svizhenko and M. P. Anantram, "Role of scattering in nanotransistors," *IEEE Trans. Electron Devices*, vol. 50, no. 6, pp. 1459–1466, Jun. 2003.

- [25] M. Ogawa, H. Tsuchiya, and T. Miyoshi, "Quantum transport modeling in nano-scale devices," in *Proc. IEEE Int. Simulation* of Semiconductor Processes and Devices Conf., Sep. 4–6, 2002, pp. 261–266.

- [26] R. Venugopal, S. Goasguen, S. Datta, and M. S. Lundstrom, "Quantum mechanical analysis of channel access geometry and series resistance in nanoscale transistors," *J. Appl. Phys.*, vol. 92, no. 1, pp. 292–305, Jan. 2004.

- [27] J. Wang and M. S. Lundstrom, "Does source-to-drain tunneling limit the ultimate scaling of MOSFETs?," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 8–11, 2002, pp. 707–710.

- [28] J. H. Rhew, Z. Ren, and M. S. Lundstrom, "A numerical study of ballistic transport in a nanoscale MOSFET," *Solid State Electron.*, vol. 46, no. 11, pp. 1899–1906, Nov. 2002.

- [29] R. Venugopal, Z. Ren, S. Datta, M. S. Lundstrom, and D. Jovanovic, "Simulating quantum transport in nanoscale transistors: Real versus mode-space approaches," *J. Appl. Phys.*, vol. 92, no. 7, pp. 3730–3739, Oct. 2002.

- [30] H. Kawaura, T. Sakamoto, and T. Baba, "Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal-oxide-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 76, no. 25, pp. 3810–3812, Jun. 2000.

- [31] V. A. Sverdlov, T. J. Walls, and K. K. Likharev, "Nanoscale silicon MOS-FETs: A theoretical study," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1926–1033, Sep. 2003.

- [32] T. J. Walls, V. A. Sverdlov, and K. K. Likharev, "Quantum mechanical modeling of advanced sub-10 nm MOSFETs," in *Proc. IEEE Nanotech*nology Conf., vol. 1, Aug. 12–14, 2003, pp. 28–31.

- [33] —, "MOSFET's below 10 nm: Quantum theory," *Phys. E*, vol. 19, no. 1–2, pp. 23–27, Jul. 2003.

- [34] Y. Naveh and K. K. Likharev, "Modeling of 10-nm-scale ballistic MOSFET's," *IEEE Electron Devices Lett.*, vol. 21, no. 5, pp. 242–244, May 2000.

- [35] D. K. Ferry, "The onset of quantization in ultra-submicron semiconductor devices," *Superlattices and Microstructures*, vol. 27, no. 2/3, pp. 61–66, Feb. 2000.

- [36] Y. Li, T.-W. Tang, and X. Wang, "Modeling of quantum effects for ultrathin oxide MOS structures with an effective potential," *IEEE Trans. Nanotechnol.*, vol. 1, no. 4, pp. 238–242, Dec. 2002.

- [37] Y. Li and S.-M. Yu, "A unified quantum correction model for nanoscale single- and double-gate MOSFET's under inversion conditions," *Nanotechnology*, vol. 15, no. 8, pp. 1009–1016, Aug. 2004.

- [38] H. Kosina, M. Nedjalkov, and S. Selberherr, "A Monte Carlo method seamlessly linking quantum and classical transport calculations," *J. Comput. Electron.*, vol. 2, no. 2–4, pp. 147–151, Dec. 2003.

- [39] H. Kosina, G. Klimeck, M. Nedjalkov, and S. Selberherr, "Comparison of numerical quantum device models," in *Proc. Int. Simulation of Semi*conductor Processes and Devices Conf., Sep. 3–5, 2003, pp. 171–174.

- [40] T. Ezaki, P. Werner, and M. Hane, "70 nm MOSFET device simulation considering two dimensional channel quantization and self-consistent nonequilibrium carrier transport," in *Extended Abstracts Int. Solid State Devices and Materials Conf.*, Sep. 26–28, 2001, pp. 382–383.

- [41] M. G. Ancona, "Equations of state for silicon inversion layers," *IEEE Trans. Electron Devices*, vol. 47, no. 7, pp. 1449–1456, Jul. 2000.

[42] M. G. Ancona and H. F. Tiersten, "Macroscopic physics of the silicon

- [42] M. G. Ancona and H. F. Tiersten, "Macroscopic physics of the silicon inversion layer," *Phys. Rev. B, Condens. Matter*, vol. 35, no. 15, pp. 7959–7965, 1987.

- [43] A. R. Brown, A. Asenov, and J. R. Watling, "Intrinsic fluctuations in sub 10-nm double-gate MOSFET's introduced by discreteness of charge and matter," *IEEE Trans. Nanotechnol.*, vol. 1, no. 4, pp. 195–200, Dec. 2002

- [44] A. Asenov, J. R. Watling, A. R. Brown, and D. K. Ferry, "The use of quantum potentials for confinement and tunnelling in semiconductor devices," *J. Comput. Electron.*, vol. 1, no. 4, pp. 503–513, Dec. 2002.

- [45] J. R. Watling, A. R. Brown, A. Asenov, A. Svizhenko, and M. P. Anantram, "Simulation of direct source-to-drain tunnelling using the density gradient formalism: Non-equilibrium greens function calibration," in *Proc. Int. Simulation of Semiconductor Processes and Devices Conf.*, Sep. 4–6, 2002, pp. 267–270.

- [46] J. R. Watling, A. R. Brown, and A. Asenov, "Can the density gradient approach describe the source-drain tunnelling in decanano double-gate MOSFETs?," J. Comput. Electron., vol. 1, no. 1–2, pp. 289–293, Jul. 2002

- [47] A. Asenov, G. Slavcheva, A. R. Brown, J. H. Davies, and S. Saini, "Increase in the random dopant induced threshold fluctuations and lowering in sub-100 nm MOSFET's due to quantum effects: A 3-D density-gradient simulation study," *IEEE Trans. Electron Devices*, vol. 48, no. 4, pp. 722–729, Apr. 2001.

- [48] S. Jin, Y. J. Park, and H. S. Min, "A numerically efficient method for the hydrodynamic density-gradient model," in *Proc. Int. Simulation of Semi*conductor Processes and Devices Conf., Sep. 3–5, 2003, pp. 263–266.

- [49] T. Toyabe, "Two and three dimensional MOSFET's simulation with density gradient model," in *Proc. 4th Int. Junction Technology Workshop*, Mar. 15–16, 2004, pp. 317–320.

- [50] A. Schenk and A. Wettstein, "2D analysis of source-to-drain tunneling in decananometer MOSFET's with the density-gradient model," in *Proc. Int. Modeling and Simulation of Microsystems Tech. Conf.*, Apr. 2002, pp. 552–555.

- [51] A. Wettstein, A. Schenk, and W. Fichtner, "Quantum device-simulation with the density-gradient model on unstructured grids," *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 279–284, Feb. 2001.

- [52] S. Odanaka, "Multidimensional discretization of the stationary quantum drift-diffusion model for ultrasmall MOSFET structures," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 23, no. 6, pp. 837–842, Jun. 2004.

- [53] Y. Li, J.-W. Lee, T.-W. Tang, T.-S. Chao, T.-F. Lei, and S. M. Sze, "Numerical simulation of quantum effects in high-κ gate dielectrics MOS structures using quantum mechanical models," *Comput. Phys. Commun.*, vol. 147, no. 1–2, pp. 214–217, Aug. 2002.

[54] T.-W. Tang, X. Wang, and Y. Li, "Discretization scheme for the den-

- [54] T.-W. Tang, X. Wang, and Y. Li, "Discretization scheme for the density-gradient equations and effect of boundary conditions," *J. Comput. Electron.*, vol. 1, no. 3, pp. 389–393, Oct. 2002.

- [55] Y. Li and S.-M. Yu, "A two-dimensional quantum transport simulation of nanoscale double-gate MOSFET's using parallel adaptive technique," *IEICE Trans. Inform. Syst.*, vol. E87-D, no. 7, pp. 1751–1758, Jul. 2004.

- [56] Y. Li, S. M. Sze, and T. S. Chao, "A practical implementation of parallel dynamic load balancing for adaptive computing in VLSI device simulation," *Eng. Comput.*, vol. 18, no. 2, pp. 124–137, Aug. 2002.

- [57] Y. Li, "A parallel monotone iterative method for the numerical solution of multidimensional semiconductor Poisson equation," *Comput. Phys. Commun.*, vol. 153, no. 3, pp. 359–372, Jul. 2003.

- [58] S. Datta, "Electrical resistance: An atomistic view," *Nanotechnology*, vol. 15, no. 7, pp. S433–S451, Jul. 2004.

- [59] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. New York: Cambridge Univ. Press, 1998.

- [60] S. M. Sze, *Physics of Semiconductor Devices*. New York: Wiley, 1981.

- [61] F.-L. Yang, D.-H. Lee, H.-Y. Chen, C.-Y. Chang, S.-D. Liu, C.-C. Huang, T.-X. Chung, H.-W. Chen, C.-C. Huang, Y.-H. Liu, C.-C. Wu, C.-C. Chen, S.-C. Chen, Y.-T. Chen, Y.-H. Chen, C.-J. Chen, B.-W. Chan, P.-F. Hsu, J.-H. Shieh, H.-J. Tao, Y.-C. Yeo, Y. Li, J.-W. Lee, P. Chen, M.-S. Liang, and C. Hu, "5 nm-gate nanowire FinFET," in VLSI Technology Symp. Tech. Dig., Jun. 15–17, 2004, pp. 196–197.

Yiming Li (M'02) received the B.S. degrees in applied mathematics and electronics engineering, M.S. degree in applied mathematics, and Ph.D. degree in electronics from the National Chiao Tung University (NCTU), Taiwan, R.O.C., in 1996, 1998, and 2001, respectively.

In 2001, he joined the National Nano Device Laboratories (NDL), Taiwan, R.O.C., as an Associate Researcher, and the Microelectronics and Information Systems Research Center, NCTU, as an Assistant Professor, where he has been engaged in

the field of computational science and engineering, particularly in modeling, simulation, and optimization of nanoelectronics and very large scale integration (VLSI) circuits. In Fall 2002, he was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts at Amherst. From 2003 to 2004, he was the Research Consultant of the System on a Chip (SOC) Technology Center, Industrial Technology Research Institute (ITRI), Hsinchu, Taiwan, R.O.C. From 2003 to 2005, he was the Director of the Departments of Nanodevice and Computational Nanoelectronics, NDL, and an Associate Professor with the Microelectronics and Information Systems Research Center, NCTU since Fall 2004. He is currently an Associate Professor with the Department of Communication Engineering and the Microelectronics and Information Systems Research Center, NCTU. He conducts the Nanodevice Modeling and Simulation Laboratory and the Parallel and Scientific Computing Laboratory at the NDL and NCTU. His current research areas include computational electronics and physics, physics of semiconductor nanostructures, device modeling, parameter extraction, circuit simulation, development of TCAD and electronic computer-aided design (ECAD) tools and SOC applications, bioinformatics and computational biology, and advanced numerical methods, parallel and scientific computation, and computational intelligence. He has authored or coauthored over 120 research papers appearing in international book chapters, journals, and conferences. He has served as a reviewer for Microelectronic Engineering, the Journal of Computational Electronics, the Springer Series Books of Mathematics in Industry, Biotechnology Progress, Computational Materials Science, etc. He has also served as a Guest Associated Editor of special issues of Integration, the VLSI Journal, and Microelectronic Engineering in 2004. He currently serves as a Guest Editor-in-Chief of a special issue of the International Journal of Computational Science and Engineering and is a member of the Editorial Board of the International Journal of Computational Intelligence.

Dr. Li is a member of Phi Tau Phi, Sigma Xi, the American Physical Society, the Association for Computing Machinery, the Institute of Electronics, Information and Communication Engineers (IEICE), Japan, and the Society for Industrial and Applied Mathematics. He has organized and served on several international conferences and was an editor of the "Proceedings of the 2005 International Conference on Computer Design." He has served as a reviewer for international conferences and for the IEEE TRANSACTIONS ON NANOTECHNOLOGY, the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, and the IEEE TRANSACTIONS ON ELECTRON DEVICES. He was the recipient of the 2002 Research Fellowship Award presented by the Pan Wen-Yuan Foundation, Taiwan, R.O.C.

Hung-Mu Chou, photograph and biography not available at time of publication.

Jam-Wem Lee, photograph and biography not available at time of publication.