## A Comparative Study of Electrical Characteristic on Sub-10-nm Double-Gate MOSFETs

Yiming Li and Hong-Mu Chou

Abstract—We explore the structure effect on electrical characteristics of sub-10-nm double-gate metal-oxide-semiconductor field-effect transistors (DG MOSFETs). To quantitatively assess the nanoscale DG MOSFETs' characteristics, the on/off current ratio, subthreshold swing, threshold voltage  $(V_{\rm th})$ , and drain-induced barrier-height lowering are numerically calculated for the device with different channel length (L) and the thickness of silicon film  $(T_{

m si})$ . Based on our two-dimensional density gradient simulation, it is found that, to maintain optimal device characteristics and suppress short channel effects (SCEs) for nanoscale DG MOSFETs,  $T_{\rm si}$  should be simultaneously scaled down with respect to L. From a practical fabrication point-of-view, a DG MOSFET with ultrathin  $T_{\rm si}$  will suppress the SCE, but suffers the fabrication process and on-state current issues. Simulation results suggest that  $L/T_{

m si} \geq 1$  may provide a good alternative in eliminating SCEs of double-gate-based nanodevices.

Index Terms—Adaptive computation, channel length, density gradient drift-diffusion model, double-gate MOSFET, drain-induced barrier height lowering, numerical simulation, on/off current ratio, quantum correction transport model, sub 10 nm, subthreshold swing, system-on-a-chip (SOC), thickness of silicon film, threshold voltage, very large scale integration (VLSI).

OUBLE-GATE silicon-on-insulator (DG SOI) devices have recently been of great interest, particularly for the investigation of sub-10-nm field-effect transistors [1]-[5]. These structures suppress short channel effects (SCEs), have high transconductance, and produce ideal subthreshold swing (SS). Compared with conventional single-gate metal-oxide-semiconductor field-effect transistor (MOSFETs) [1]-[3], they have superior channel-control properties so drain-induced barrier-height lowering (DIBL),  $V_{\rm th}$  rolloff, and off-state leakage can be greatly suppressed [1]-[11]. The on/off current ratio is directly related to the high-frequency performance and power consumption. Circuits with a higher on/off current ratio have a better high-frequency performance versus power consumption tradeoff. SS reflects the switch speed of the devices; a lower SS sustains a digital circuit with a high switching speed and high noise margin.  $V_{

m th}$  rolloff and DIBL effects will direct

Manuscript received September 8, 2004; revised March 17, 2005. This work was supported in part by the National Science Council of Taiwan, R.O.C., under Contract NSC-93-2215-E-429-008 and Contract NSC-94-2752-E-009-003-PAE, by the Ministry of Economic Affairs under Contract 93-EC-17-A-07-S1-0011, and by the Taiwan Semiconductor Manufacturing Company under a 2004–2005 grant. An earlier version of this paper was presented at the 2004 IEEE Silicon Nanoelectronics Workshop.

The authors are with the Department of Communication Engineering and the Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu City, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymli@faculty.nctu.edu.tw).

Digital Object Identifier 10.1109/TNANO.2005.851440

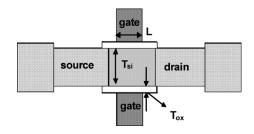

Fig. 1. Schematic diagram of the simulated DG MOSFET.

influence the uniformity of designed circuit. A large  $V_{\rm th}$  results in a significant variation of the designed circuit, which downgrades the circuit performance. Under specified conditions, the structure of nanoscale DG SOI devices can be subject to further optimization for sustaining more physical and electrical benefit.

By considering: 1) the on/off current ratio; 2) the SS; 3) the threshold voltage; and 4) and the DIBL, we theoretically investigate the electrical characteristics of sub-10-nm double-gate MOSFETs (DG MOSFETs) with respect to different L and  $T_{si}$ . To have optimal device structure and corresponding electrical characteristic, the aforementioned four characteristics are calculated and quantitatively compared utilizing two-dimensional (2-D) density gradient simulation [9]-[12]. There have been several approaches to the modeling of quantum mechanical (QM) effects in nanoscale devices such as full QM and quantum correction models [6]-[13]. To focus on the problem of structure optimization, a set of 2-D density gradient drift-diffusion equations is adopted in the simulation of nanoscale DG MOS-FETs [9], [11], [13]. To validate the density gradient model, we have referred to the simulation reported in [6], and [9]–[12] to calibrate the model in both the confinement and source/drain tunneling by using different effective masses along the normal and parallel directions with respect to the device channel [9]-[12]. This approach is computationally efficient for incorporating quantum corrections in 2-D/three-dimensional (3-D) technology computer-aided design (TCAD) simulation of the device. To solve the 2-D density gradient drift-diffusion model, we use the adaptive computational technique [13].

Shown in Fig. 1,  $T_{\rm ox}$  is equal to 1 nm for the symmetric DG MOSFET. The source (and drain) overlapping the gate is 0.5 nm and the gate edge to the source/drain contact edge is 150 nm. This setting is referring to as the realistic device structure for having a better result in calibration. The source/drain doping used in our simulation is an n<sup>+</sup> Gaussian profile with is peak value of  $5 \times 10^{19}$  cm<sup>-3</sup>. The channel is with a  $10^{18}$  cm<sup>-3</sup> constant doping. The channel length L is defined in a physical

Fig. 2. Comparison of the  $I_D$ – $V_G$  characteristics for the DG MOSFETs with L where: (a)  $T_{\rm si}=10$  nm (b) and  $T_{\rm si}=20$  nm, respectively.

meaning; it means that it is taken as the real length of the gate pattern. The gate material is with an n+ polysilicon gate, where the doping level is  $10^{20}$  cm<sup>-3</sup> and its thickness is 30 nm. Considering the fabrication accessibility and process fluctuation [2], [3], a thinnest thickness of silicon film is taken as 10 nm in this study.

Fig. 2(a) shows that the gate length reduction will cause a worse DIBL characteristic; moreover, the SS is simultaneously becoming large for the short gate-length devices. These characteristics, from the fabrication engineering point-of-view, will be important issues for the scaling down of devices. Without considering the poor SCEs for short channel devices, it could be concluded that the length of gate does not significantly modulate the on-state current of double-gate devices. This should be caused from the fact that the parasitic resistance is relatively high; therefore, it limits the on-state current of these thin device's film. The  $I_D$ – $V_G$  transfer curves of the 10-nm thicken silicon film devices slightly shows DIBL effects, but the DG MOSFETs with  $T_{\rm si} = 20$  nm present significant DIBL effects, as shown in Fig. 2(b). Moreover, the off-state current level of the devices with the thicker silicon film is much higher than those with the thinner one. Those drawbacks are mainly caused from the fact that the device with a thicker silicon film weakens the controllability of gate electrodes. Owing to such poor gate controllability, devices with a thicker silicon film have a lower

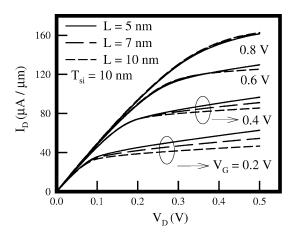

Fig. 3.  $I_D$ – $V_D$  characteristics simulated from the DG MOSFETs with different L where  $T_{\rm si}=10$  nm is fixed.

TABLE I EFFECT OF CHANNEL DOPING CONCENTRATION ON THE THRESHOLD VOLTAGE FOR THE SIMULATED DG MOSFET WITH  $T_{

m si}=L=10$  nm

| Doping level (cm <sup>-3</sup> )             |        | 10 <sup>15</sup> | 1016       | 1017       | 1018       |

|----------------------------------------------|--------|------------------|------------|------------|------------|

| $\mathbf{V}_{\scriptscriptstyle \mathrm{D}}$ | 0.05 V | -0.00561 V       | -0.05675 V | -0.04052 V | -0.06352 V |

|                                              | 0.45 V | -0.03809 V       | -0.08739 V | -0.09059 V | -0.09083 V |

channel barrier height, encounter a higher leakage current level, and get a worse result for DIBL effects.

Besides, the on-state current is another important factor for evaluating the operation of novel devices; for example, a large on-state current will result in a high operation frequency. Fig. 3 shows the  $I_D$ – $V_D$  characteristics of the simulated DG MOSFETs with  $T_{\rm si}=10$  nm. The short channel devices do slightly enhance the on-state current. However, owing to a very poor performance in the threshold voltage and the off-state current, the benefit of the on-state current relatively becomes minor in the optimization of DG MOSFETs. The higher on-state current level is caused from the DIBL effect that the drain voltage modulates the current for the shorter gate-length devices. Nevertheless, the current modulation will cause a drawback for the analog circuit applications, such as a small output resistance will greatly degrade the gain of the device.

Due to the full depletion of the channel region, the threshold voltage of the thin body devices is relatively low and hardly needs to be adjusted by increasing the channel doping. It is clearly found from Table I that a four-orders increase of channel doping could only make approximately a 0.1-V shift of  $V_{\rm th}$ . Consequently, it is becoming a more important course in fine tuning the work function of the metal semiconductor. For the simulated DG MOSFET with  $T_{\rm si}=L=10$  nm, Table I exhibits the effects of channel-doping concentration on the threshold voltage. Channel doping is often considered a parameter for the threshold voltage adjustment in the bulk devices, but it does not work well for double-gate devices. Therefore, directly tuning the work function of the gate metal provides an alternative to obtain a required threshold voltage. According to our studies, a midgap metal may provide suitable material for the design

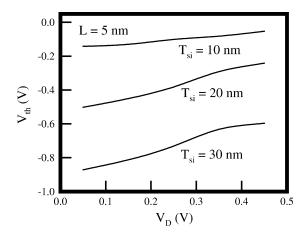

Fig. 4.  $V_{\rm th}$  versus the drain bias with respect to different  $T_{\rm si}$  where L=5 nm and  $T_{\rm si}$  varies from 10 to 30 nm.

and fabrication of double-gate nanodevices. For a more accurate estimation, effects of the random doping fluctuation should also be included [10], [12]. The  $V_{\rm th}$  rolloff characteristic is an important issue for modern very large scale integration (VLSI) circuit design including system-on-a-chip (SOC) application; a significant  $V_{\rm th}$  rolloff will greatly increase the difficulty in both the VLSI circuit design and SOC manufacturing. The thickness of silicon film correlated threshold voltage rolloff properties are calculated and shown in Fig. 4. It is found that the devices with the thinner silicon films will sustain a good rolloff behavior. Additionally, a thinner silicon film will result in a larger threshold voltage. These good characteristics improve the scalability of nanoscale DG MOSFETs.

In conclusion, by solving a unified 2-D density gradient model, we have simulated sub-10-nm DG MOSFETs and found that DG MOSFETs with thinner silicon films greatly suppress the SCE, but the on-state current issue suffers. A compromise between silicon film thickness and gate channel length should be maintained at the same time so that an optimal device characteristic could be obtained. It is known that  $L/T_{\rm si}>1$  (i.e., 1.5 or 2) has been reported for double-gate devices. However, according to our investigations,  $L/T_{\rm si}=1$  may provide a good compromise between the elimination

of SCEs and uniformity of fabrication in double-gate-based nanodevices. This investigation is useful for the fabrication of nanodevice and SOC application.

## REFERENCES

- [1] H. Wakabayashi, S. Yamagami, N. Ikezawa, A. Ogura, M. Narihiro, K. Arai, Y. Ochiai, K. Takeuchi, T. Yamamoto, and T. Mogami, "Sub-10-nm planar-bulk-CMOS devices using lateral junction control," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 7–10, 2003, pp. 20.7.1–20.7.4.

- [2] D. M. Fried, E. J. Nowak, J. Keidzierski, J. S. Duster, and K. T. Komegay, "A fin-type independent-double-gate NFET," in *Proc. Device Research Conf.*, Jun. 23–25, 2003, pp. 45–46.

- [3] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, and D. Kyser, "FinFET scaling to 10 nm gate length," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 2002, pp. 251–254.

- [4] M. Ieong, H.-S. P. Wong, E. Nowak, J. Kedzierski, and E. C. Jones, "High performance double-gate device technology challenges and opportunities," in *Proc. Int. Quality Electronic Design Symp.*, Mar. 18–21, 2002, pp. 492–495.

- [5] L. Wei, Z. Chen, and K. Roy, "Design and optimization of double-gate SOI MOSFET's for low voltage low power circuits," in *Proc. IEEE Int. Silicon-on-Insulator Conf.*, Oct. 5–8, 1998, pp. 69–70.

- [6] R. Venugopal, S. Goasguen, S. Datta, and M. S. Lundstrom, "Quantum mechanical analysis of channel access geometry and series resistance in nanoscale transistors," *J. Appl. Phys.*, vol. 92, no. 1, pp. 292–305, Jan. 2004.

- [7] V. A. Sverdlov, T. J. Walls, and K. K. Likharev, "Nanoscale silicon MOS-FETs: A theoretical study," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1926–1033, Sep. 2003.

- [8] Y. Li, T.-W. Tang, and X. Wang, "Modeling of quantum effects for ultrathin oxide MOS structures with an effective potential," *IEEE Tran. Nanotechnol.*, vol. 1, no. 4, pp. 238–242, Dec. 2002.

- [9] A. Asenov, A. R. Brown, and J. R. Watling, "Quantum corrections in the simulation of decanano MOSFETs," *Solid State Electron.*, vol. 47, pp. 1141–1145, Jul. 2003.

- [10] A. R. Brown, A. Asenov, and J. R. Watling, "Intrinsic fluctuations in sub 10-nm double-gate MOSFET's introduced by discreteness of charge and matter," *IEEE Trans. Nanotechnol.*, vol. 1, no. 4, pp. 195–200, Dec. 2002

- [11] J. R. Watling, A. R. Brown, and A. Asenov, "Can the density gradient approach describe the source-drain tunnelling in decanano double-gate MOSFETs?," J. Comput. Electron., vol. 1, no. 1–2, pp. 289–293, Jul. 2002

- [12] A. Asenov, G. Roy, C. Alexander, A. R. Brown, J. R. Watling, and S. Roy, "Quantum mechanical and transport aspects of resolving discrete charges in nano-CMOS device simulation," in *Proc. 4th IEEE Nanotechnology Conf.*, Sep. 17–19, 2004, pp. TH2\_3\_2-1-TH2\_3\_2-3.

- [13] Y. Li and S. M. Yu, "A two-dimensional quantum transport simulation of nanoscale double-gate MOSFET's using parallel adaptive technique," *IEICE Trans. Inform. Syst.*, vol. E87-D, no. 7, pp. 1751–1758, Jul. 2004.