# Optimizing the Match in Weakly Inverted MOSFET's by Gated Lateral Bipolar Action

Ming-Jer Chen, Member, IEEE, Jih-Shin Ho, and Dang-Yang Chang

Abstract—The on-chip n-type MOSFET current mirror circuit with different drawn gate widths and lengths has been fabricated, and has been characterized across the wafer with back gate slightly forward biased. The weakly inverted MOSFET device with a small back-gate forward bias represents equivalently the high-gain gated lateral bipolar transistor in low-level injection. Experimental results have exhibited a substantial improvement in the match of the drain current in weak inversion due to action of the gated lateral bipolar transistor, especially for the small size devices. The extensively measured mismatch of the weak inversion drain current has been successfully reproduced by an analytic statistical model with back-gate forward bias and device size both as input parameters. The experimentally extracted variations in process parameters such as the flat-band voltage and the body effect coefficient each have been found to follow the inverse square root of the device area. The mismatch model thus can serve as a quantitative design tool, and has been used to optimize the trade-off between the device area and the match with the forward back-gate bias as a parameter.

## I. INTRODUCTION

THERE are many advantages for operating MOSFET's in subthreshold or weak inversion region: extremely low power dissipation, low-voltage swing, and exponential dependence of drain current on gate-to-source voltage. The latter provides a very useful property for many applications such as analog computation [1], [2]. One of the major disadvantages associated with weakly inverted MOSFET's is the current mismatch between identically drawn devices [1]. Owing to exponential dependencies on the process variations, devices in subthreshold usually exhibit a dramatically large mismatch in current as compared with that in above-threshold [1]. This poor control over the current match in weak inversion can cause a number of unwanted effects in the circuit level. This situation would be made worse if the device area is further reduced for higher density requirement. On the other hand, there indeed exist nonzero back-gate or substrate (or bulk)-tosource biases in the present subthreshold CMOS circuits [1], [2] and thus the dependence of current mismatch in weakly inverted MOSFET's on the back-gate bias must be taken into account. With respect to the well-documented work concerning the mismatch analysis in above-threshold [3]-[5], the study of

Manuscript received September 25, 1995; revised December 11, 1995. The review of this paper was arranged by Editor K. Shenai. This work was supported by the National Science Council under Contract NSC 84-2215-E-009-043.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(96)03376-X.

mismatch in weak inversion is still limited [6]–[8]. In [6], the measured weak inversion current mismatch was observed to be proportional to the inverse square root of device area; however, the effect of back-gate bias on the mismatch was not simultaneously addressed. In [7] and [8], the back-gate reverse bias was judged to be responsible for significant degradation in match. In [8], it was also demonstrated that 1) the current match can be substantially improved by a small back-gate forward bias or equivalently the action of the high-gain gated lateral bipolar transistor in low-level injection [9]–[11]; and 2) the measured dependencies of the mismatch on the back-gate bias can be reproduced by a new statistical model. However, in [8] only a device of 2  $\mu$ m × 2  $\mu$ m was characterized and the dependence of the mismatch on the device area was not reported experimentally or theoretically.

In our work [8], a gated lateral bipolar action in low-level injection has been suggested as a new method of improving the transistor matching in weak inversion. To highlight this method in a more practical way, here we will establish a quantitative design tool that analytically expresses the weak inversion current mismatch as a function of both the device area and back-gate forward bias. First, experimental mismatch data from different drawn gate widths and lengths each measured at different back-gate forward biases will be given in detail. Then an analytic statistical model will be completely derived and employed to simultaneously reproduce a large amount of the mismatch data extensively measured across the wafer. Finally, from the mismatch model the work of optimizing the trade-off between the device area and the match with back-gate forward bias as a parameter will be reported.

## II. EXPERIMENT & RESULTS

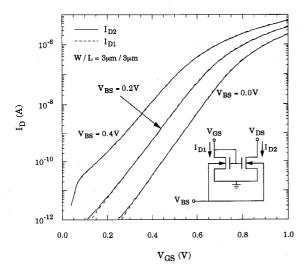

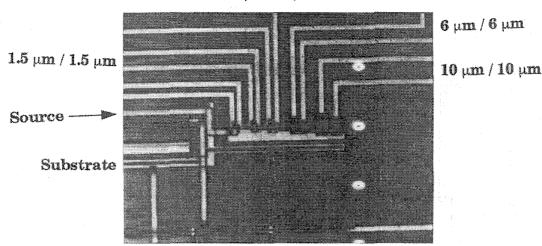

The measurement of current mismatch in this study was achieved through the n-type MOSFET current mirror circuit as schematically shown in the inset of Fig. 1. The transistors  $M_1$  and  $M_2$  with identical drawn gate size were placed in parallel and close to each other. The on-chip current mirror circuit with four different gate width to length ratios of 1.5  $\mu$ m/1.5  $\mu$ m, 3  $\mu$ m/3  $\mu$ m, 6  $\mu$ m/6  $\mu$ m, and 10  $\mu$ m/10  $\mu$ m was fabricated by a 0.8- $\mu$ m CMOS process. Fig. 2 shows the photograph of the test chip. First in the measurement, the backgate or substrate-to-source forward bias  $V_{\rm BS}$  was fixed when sweeping  $V_{\rm GS}$  and  $V_{\rm DS}$  simultaneously from 0 V to 2 V in the same steps of 20 mV. This procedure was repeated for each  $V_{\rm BS}$  varying from 0.4 V down to 0 V in steps of -100 mV. The choice for the maximum forward bias  $V_{\rm BS}$  of 0.4 V ensures the

Fig. 1. The drain currents versus gate-to-source voltage characteristics measured from one current mirror circuit with back-gate forward bias as parameter.

action of only the gated lateral bipolar transistor in low-level injection, as explained later. The total measurement of one current mirror circuit for these full ranges consumed about 13 min. Fig. 1 depicts typically the I-V characteristics with  $V_{\rm BS}$  as parameter measured from one single current mirror. In Fig. 1 the operating regime of interest in this study, i.e., the weak inversion, is around  $V_{\rm GS}>0$  and  $I_{D1}$  (or  $I_{D2}$ ) < 10 nA. From Fig. 1 we can observe a slight difference between the two drain current versus gate-to-source voltage curves for each given  $V_{\rm BS}$ .

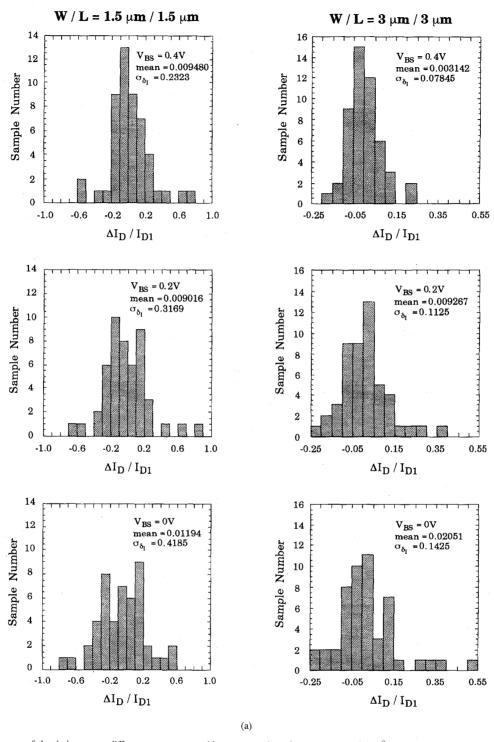

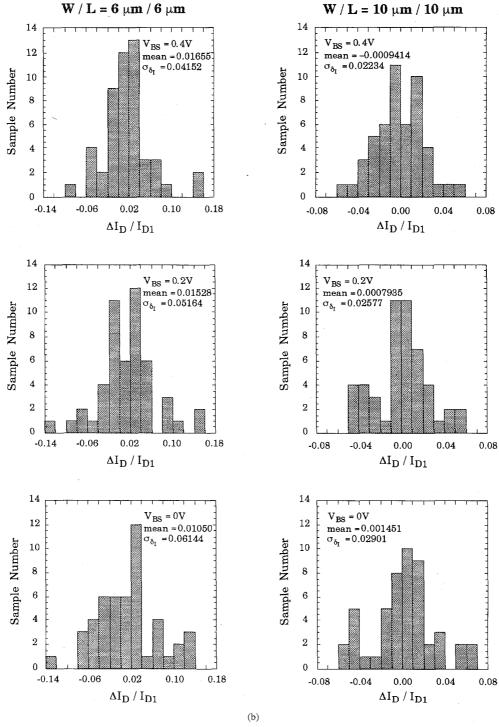

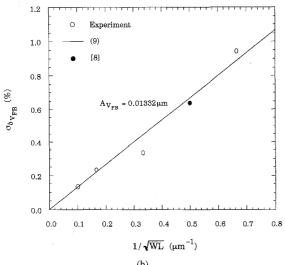

A total of 50 current mirror circuits for each gate width to length ratio have been measured across the same wafer. Fig. 3 shows in detail the histogram of the measured drain current mismatch measured with  $V_{\rm BS}$  as parameter for a specified reference current of  $10^{-9}$  A. Here, the current mismatch  $\delta_I$  is defined as

$$\delta_I = \frac{I_{D1} - I_{D2}}{I_{D1}} \tag{1}$$

where  $I_{D1}$  is regarded as the reference drain current and  $I_{D2}$ is the mirrored drain current. The strategy of calculating the  $\delta_I$ properly from the measured I-V data is described here. First, given a value of  $I_{D1}$ , the  $V_{GS}$  can be obtained from the  $I_{D1}$ versus  $V_{\rm GS}$  data using Lagrange interpolation; and then the corresponding  $I_{D2}$  can be found from the  $I_{D2}$  versus  $V_{GS}$  data accordingly. We can confidently calculate  $\delta_I$  at any specific current without any further measurement. From Fig. 3 we can observe that the mismatch distribution significantly broadens as either the device area is reduced or the  $V_{

m BS}$  increases negatively from 0.4 V to 0 V. We have also found that for given  $V_{\rm BS}$  the mismatch distributions measured from the same gate width to length ratio are comparable for other different reference currents in weak inversion. An important statistical parameter for another quantitative evaluation of the current mismatch,  $\sigma_{\delta_I}$ , i.e., the standard deviation of  $\delta_I$ , is defined as

$$\sigma_{\delta_I}^2 = \frac{m \sum_{i=1}^m \delta_{I_i}^2 - (\sum_{i=1}^m \delta_{I_i})^2}{m(m-1)}$$

(2)

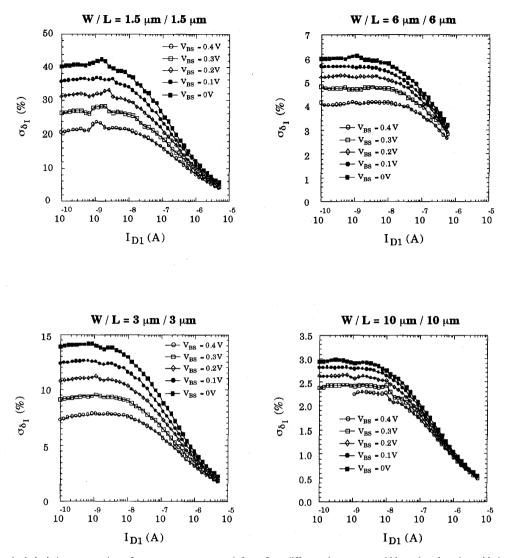

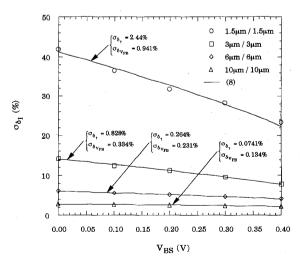

where m is the sample number. Fig. 4 shows the  $\sigma_{\delta_I}$  versus the reference current  $I_{D1}$  from each gate width to length ratio measured at five different back-gate forward biases. From Fig. 4 we can observe that for each  $V_{BS}$ , in the weak inversion region the mismatch is essentially independent of the current while as the current increases and enters into the transition and further above-threshold regions, the mismatch significantly rolls off. The mechanism for transition and then above-threshold regions is that the surface drift component begins to appear and gradually dominate, and simultaneously the dependency of the drain current variation on the threshold voltage variation due to process variation is transferred from exponential to polynomial. Physically speaking, the amount of the inverted carriers increases, thus increasing the ability of shielding the interface states. The data in Fig. 4 suggest two methods for improving the matching in weak inversion: increasing positively the back-gate forward bias and increasing the device area. To highlight these two methods, the measured mismatch data in terms of the standard deviation of the difference in the weak inversion drain current versus the bias  $V_{\rm BS}$  for four different gate width to length ratios is plotted in Fig. 5. From Fig. 5 we can observe that the current match for the small size devices can be substantially improved by increasing the back-gate forward bias, while for large devices it tends to be insensitive to the back-gate bias.

## III. MISMATCH MODEL

According to [12], the variance or standard deviation  $\sigma_{g(x,y)}$  of a function g(x,y) with two random variables x and y can be expressed as

$$\sigma_{g(x,y)}^{2} \cong \left(\frac{\partial g}{\partial x}\right)^{2} \sigma_{x}^{2} + \left(\frac{\partial g}{\partial y}\right)^{2} \sigma_{y}^{2} + 2\left(\frac{\partial g}{\partial x}\right)\left(\frac{\partial g}{\partial y}\right) C_{ov}(x,y)$$

(3)

where  $\sigma_x$  and  $\sigma_y$  are the variances of x and y, respectively; and  $C_{ov}(x,y)$  is the correlation coefficient between x and y. Thus the variance of the difference in the drain current  $I_D$  can be written as function of the variances in the associated process parameters

$$\sigma_{\delta_I}^2 \cong \left(\frac{\partial I_D}{\partial \gamma}\right)^2 \left(\frac{\gamma}{I_D}\right)^2 \sigma_{\delta_\gamma}^2 + \left(\frac{\partial I_D}{\partial V_{\rm FB}}\right)^2 \left(\frac{V_{\rm FB}}{I_D}\right)^2 \sigma_{\delta_{V_{\rm FB}}}^2 \tag{4}$$

where  $\sigma_{\delta_I}$ ,  $\sigma_{\delta_\gamma}$ , and  $\sigma_{\delta_{V_{\rm PB}}}$  are the standard deviation of the difference in the  $I_D$ , the body effect coefficient  $\gamma$ , and the flatband voltage  $V_{\rm FB}$ , respectively. To facilitate the analysis, we assume  $C_{ov}(V_{\rm FB},\gamma)=0$ . This is a basic assumption in the field [3]–[5] since the process variations are independent of each other in nature. Note that the variations in the gate oxide thickness  $t_{\rm ox}$  and channel effective doping concentration  $N_A$  are simultaneously reflected in the single parameter  $\gamma$  since  $\gamma$  includes both  $t_{\rm ox}$  and  $N_A$ , i.e.,  $\gamma=t_{\rm ox}\sqrt{2q\epsilon_{\rm si}N_A}/\epsilon_{\rm ox}$  where  $\epsilon_{\rm si}$  and  $\epsilon_{\rm ox}$  are the silicon and oxide permittivities, respectively. The following weak inversion current expression is considered

# $3 \mu m / 3 \mu m$

Fig. 2. The photograph of the test chip.

for derivation of the model [13]:

$$I_D = I_0 e^{\frac{q(V_{\rm GS} - V_{th})}{nkT}}$$

$$I_0 \propto \frac{\gamma}{2\sqrt{1.5\phi_f - V_{\rm BS}}} e^{-\frac{q\phi_f}{2kT}}$$

(5)

where the critical voltage  $V_{\rm th}=V_{\rm FB}+1.5\phi_f+\gamma\sqrt{1.5\phi_f-V_{\rm BS}};$  the Fermi level  $\phi_f=(kT/q)\ln(N_A/n_i);$  the slope  $n=1+\gamma/2\sqrt{1.5\phi_f-V_{\rm BS}};$  and  $n_i$  is the intrinsic concentration. From (5) the derivatives in (4) can easily be derived

$$\frac{\gamma}{I_D} \frac{\partial I_D}{\partial \gamma} = 1 - \frac{q\gamma\sqrt{1.5\phi_f - V_{\rm BS}}}{nkT} - \frac{q\gamma(V_{\rm GS} - V_{\rm th})}{2n^2kT\sqrt{1.5\phi_f - V_{\rm BS}}}$$

(6)

and

$$\frac{V_{\rm FB}}{I_D} \frac{\partial I_D}{\partial V_{\rm FB}} = -\frac{qV_{\rm FB}}{nkT}.$$

(7)

We have found that the first and third terms of the right-hand side of (6) can be neglected with respect to the second term, implying that the variation in  $V_{\rm th}$  contributes predominantly to the variation in  $I_D$ . Thus, we obtain a compact model

$$\sigma_{\delta_I} \cong \sqrt{\left(\frac{q\gamma}{nkT}\right)^2 (1.5\phi_f - V_{\rm BS})\sigma_{\delta_{\gamma}}^2 + \left(\frac{qV_{\rm FB}}{nkT}\right)^2 \sigma_{\delta_{V_{\rm FB}}}^2}.$$

(8)

Apparently, (8) analytically expresses the current mismatch in weak inversion as function of the standard deviation of the difference in  $V_{\rm FB}$  and  $\gamma$ . Note that (8) does not contain the reference current  $I_D$ , indicating that the weak inversion mismatch is independent of the current, as observed experimentally above.

The process parameters available from the foundry are:  $t_{\rm ox}=190$  Å,  $V_{\rm FB}=-0.76$  V, and  $N_A=5.6\times 10^{16}$  cm<sup>-3</sup>. By substituting these parameter values into (8), the data from

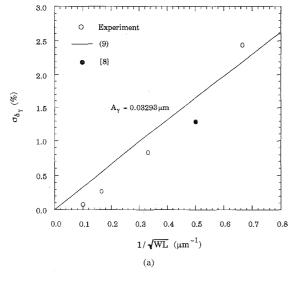

four different gate width to length ratios in Fig. 5 have been successfully reproduced over the back-gate forward bias range illustrated. The corresponding extracted variations in process parameters  $V_{\rm FB}$  and  $\gamma$  versus the inverse square root of the device area are plotted in Fig. 6. From Fig. 6 we can observe that the standard deviations of the difference in  $V_{\rm FB}$  and  $\gamma$  each effectively follow the inverse square root of the device area, in agreement with [3], [4]. Thus, empirically we have

$$\sigma_{\delta_{\gamma}} = \frac{A_{\gamma}}{\sqrt{WL}}$$

and  $\sigma_{\delta_{V_{\text{FB}}}} = \frac{A_{V_{\text{FB}}}}{\sqrt{WL}}$  (9)

where  $A_{\gamma}$  and  $A_{V_{\rm FB}}$  are the size proportionality constants for  $\sigma_{\delta_{\gamma}}$  and  $\sigma_{\delta_{V_{\rm FB}}}$ , respectively. The extracted values of  $A_{\gamma}=0.032\,93~\mu{\rm m}$  and  $A_{V_{\rm FB}}=0.013\,32~\mu{\rm m}$  lead to good agreement with experimental data as shown in Fig. 6. Further we add the data from the same foundry as cited in [8] to Fig. 6; surprisingly, these two data points each are close to the line of (9). Therefore, a combination of (8) and (9) can serve as an analytic design tool for properly calculating the mismatch with back-gate forward bias and device size both as input parameters.

# IV. OPTIMIZING THE MATCH

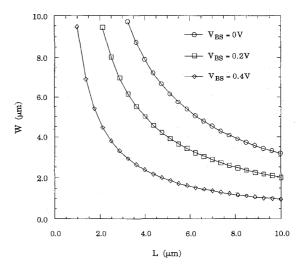

Here we demonstrate how to apply the above mismatch model in the work of optimizing the trade-off between the device size and the match with back-gate forward bias as design parameter. By means of (8) and (9) along with the above known and extracted parameter values, the calculation results in terms of gate length versus gate width with one specified mismatch value of  $\sigma_{\delta_I} = 10\%$  are plotted in Fig. 7 for three different back-gate biases of 0 V, 0.2 V, and 0.4 V. The area under each curve in Fig. 7 for a given  $V_{\rm BS}$  yields the mismatch value larger than the specification. From Fig. 7 we can observe that this area or equivalently the device size significantly decreases as the back-gate forward bias is increased. Apparently, the mismatch model can serve as

Fig. 3. The histogram of the drain current difference percentage with respect to the reference current of  $10^{-9}$  A measured from the drawn gate width to length ratio W/L of (a) 1.5  $\mu$ m/1.5  $\mu$ m and 3  $\mu$ m/3  $\mu$ m; and (b) 6  $\mu$ m/6  $\mu$ m and 10  $\mu$ m/10  $\mu$ m.

a design tool, i.e., the drawn gate width or length can be quantitatively minimized for a specified mismatch. In Fig. 7, for example, to maintain the same accuracy the minimum gate area of 9.5  $\mu \rm m^2$  at  $V_{\rm BS}=0.4$  V is needed to be increased to a large value of about 31  $\mu \rm m^2$  for a conventional zero back-gate bias.

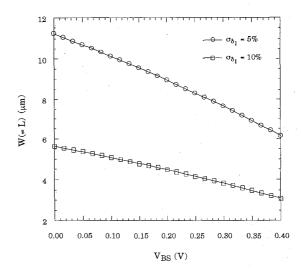

Again applying (8) and (9), the calculation results in terms of the back-gate forward bias versus the gate width or length for two different specified mismatch values of  $\sigma_{\delta_I}$  =5% and 10% are plotted in Fig. 8. In this figure, the gate width is made equal to the gate length. From Fig. 8 we can observe that the minimum gate width or length can be significantly

Fig. 3. (Continued.)

scaled down by increasing the back-gate forward bias from 0 V, i.e., an about 3.3 and 3.1 times reduction of gate area is obtained at  $V_{\rm BS}=0.4~\rm V$  for  $\sigma_{\delta_I}=5\%$  and 10%, respectively. One guideline for circuit design can be drawn from Fig. 8: if the specification of  $\sigma_{\delta_I}$  is strictly decreased from 10% to 5%, the original size of 5.6  $\mu \rm m \times 5.6~\mu m$  at  $V_{\rm BS}=0~\rm V$  must be significantly raised to a large value of 11.3  $\mu \rm m \times 11.3~\mu m$

while if the  $V_{\rm BS}=0.4~{\rm V}$  is imposed this value can be suppressed to a comparable magnitude of  $6.2~{\rm \mu m}\times 6.2~{\rm \mu m}$ . We have also additionally measured the match improvement for the  $V_{\rm BS}$  over 0.4 V; however, under such higher forward biases the parasitic bipolar far away the surface, which is primarily responsible for further improvement in the matching, is becoming activated, and may cause the undesirable effects

Fig. 4. The standard deviation versus the reference current measured from four different drawn gate width to length ratios with back-gate forward bias as parameter.

such as disturbing the nearby circuitry in the present bulk CMOS process. Thus in this study we limit the maximum  $V_{\rm BS}$ to 0.4 V. Under this situation, the MOSFET with back gate slightly forward biased plays equivalently a role of a high-gain gated lateral bipolar transistor in low-level injection [9]-[11], i.e., the base or substrate current is considerably small or the parasitic bipolar action is almost suppressed. The back-gate forward bias can be provided externally or generated on chip. The design of the on-chip back-gate forward bias generation circuit can be made easily by appropriate determination of the  $V_{\rm BS}$  value. For example, if the  $V_{\rm BS}$  is fixed at 0.3 V, the base or substrate current has been found to have an extremely low value at the order of pA or less [11]; thus the simple bandgap voltage references without the complicated regulator circuitry are enough since in this situation the load current sourcing capability becomes of less concern. It is worthy to note that even at a small  $V_{\rm BS}=0.3$  V, the gate area at  $\sigma_{\delta_I}=$ 5% or 10% can be reduced by a considerable factor of about 2.2 with respect to zero back-gate bias.

Fig. 5. The measured and calculated standard deviation of the difference in the drain current in weak inversion versus back-gate forward biases.

Fig. 6. (a) The measured and calculated standard deviation of the difference in the body effect coefficient  $\gamma$  versus the inverse square root of the device area; and (b) the measured and calculated standard deviation of the difference in the flat-band voltage  $V_{\rm FB}$  versus the inverse square root of the device area. The data from [8] are also plotted together.

Note that the pure lateral bipolar action in a MOS transistor with substrate-to-source junction forward biased has been well documented in [14], [15] for improving the transistor matching. However, our operating condition and the mechanism responsible both are completely different from those in [14], [15]; that is, in our work the maximum  $V_{\rm BS}$  for gated lateral bipolar action is limited to 0.4 V such that the parasitic bipolar far away from the surface is essentially inactive [9]–[11], implying a high current gain feature. Note that for  $V_{\rm BS}$  exceeding 0.5 V the gate loses its control over the current, that is, the pure lateral bipolar collector current dominates in the weak inversion and transition regimes [10], [11]. Accurate comparisons can be presented in the following: 1) in [14], [15] the polarity of the  $V_{\rm GS}$  is negative (i.e., the MOSFET is completely turned off) while in our work it is positive; and

Fig. 7. The calculated gate width versus gate length with back-gate forward bias as parameter for the specification of  $\sigma_{\delta_I}=10\%$ .

Fig. 8. The calculated back-gate forward bias versus gate width for two specified  $\sigma_{\delta_I}$  of 5 and 10%. Here the gate width is made equal to the gate length.

2) in [14] and [15] the pure lateral bipolar action occurs at  $V_{\rm BS} > 0.3$ –0.4 V while in our work the gated lateral bipolar action appears in low-level regime of 0 V <  $V_{\rm BS} < 0.4$  V.

# V. CONCLUSION

The on-chip n-type MOSFET current mirror circuits having four different drawn gate width to length ratios each with a large sample number of 50 have been extensively measured over a small back-gate forward bias range. The MOS transistor with substrate-to-source junction slightly forward biased acts as a high-gain gated lateral bipolar transistor in low-level injection. Experiment has exhibited that the drain current match in weak inversion can be substantially improved by action of the gated lateral bipolar in low-level injection, especially for the small size devices. An analytic mismatch

model has been developed and has successfully reproduced the extensively measured data. The extracted variations in the associated process parameters have been found to follow the inverse square root of the device area. The work of optimizing the trade-off between the match and the device size with backgate forward bias as design parameter has been demonstrated based on the model.

#### ACKNOWLEDGMENT

The authors would like to thank the Chip Implementation Center, National Science Council, for wafer fabrication and technology support.

#### REFERENCES

- E. A. Vittoz, "Micropower techniques," in *Design of MOS VLSI Circuits for Telecommunications*, Y. Tsividis and P. Antognetti, Eds. Englewood Cliffs, NJ: Prentice-Hall, 1985, pp. 104–144.

- C. A. Mead, Analog VLSI and Neural Systems. Reading, MA: Addison-Wesley, 1989.

- [3] K. R. Lakshmikumar, R. A. Hadaway, and M. A. Copeland, "Characterization and modeling of mismatch in MOS transistors for precision analog design," *IEEE J. Solid-State Circuits*, vol. SSC-21, pp. 1057–1066, Dec. 1986.

- [4] M. J. M. Pelgrom, A. C. J. Duinmaiger, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1433–1440, Oct. 1989.

- [5] C. Michael and M. Ismail, "Statistical modeling of device mismatch for analog MOS integrated circuit," *IEEE J. Solid-State Circuits*, vol. 27, pp. 154–165, Feb. 1992.

- [6] A. Pavasovic, "Subthreshold region MOSFET mismatch analysis and modeling for analog VLSI systems," Ph.D. Dissertation, The Johns Hopkins University, Baltimore, MD, 1990.

- [7] F. Forti and M. E. Wright, "Measurement of MOS current mismatch in the weak inversion region," *IEEE J. Solid-State Circuits*, vol. 29, pp. 138–142, Feb. 1994.

- [8] M. J. Chen, J. S. Ho, and T. H. Huang, "Dependence of current match on back-gate bias in weakly inverted MOS transistors and its modeling," *IEEE J. Solid-State Circuits*, vol. 31, no. 2, pp. 259–262, Feb. 1996.

[9] S. Verdonekt-Vandebroek, S. S. Wong, J. C. S. Woo, and P. K. Ko,

- [9] S. Verdonekt-Vandebroek, S. S. Wong, J. C. S. Woo, and P. K. Ko, "High-gain lateral bipolar action in a MOSFET structure," *IEEE Trans. Electron. Devices*, vol. 38, pp. 2487–2496, Nov. 1991.

[10] T. H. Huang and M. J. Chen, "Empirical modeling for gate-controlled

- [10] T. H. Huang and M. J. Chen, "Empirical modeling for gate-controlled collector current of lateral bipolar transistors in an n-MOSFET structure," *Solid-State Electronics*, vol. 38, pp. 115–119, Jan. 1995.

- [11] \_\_\_\_\_\_, "Base current reversal phenomenon in a CMOS compatible high-gain n-p-n gated lateral bipolar transistor," *IEEE Trans. Electron. Devices*, vol. 42, pp. 321–327, Feb. 1995.

- [12] A. Papoulis, Probability, Random Variable and Stochastic Processes. Kogakusha, Tokyo: McGraw-Hill, 1965.

- [13] Y. P. Tsividis, Operation and Modeling of the MOS Transistor. New York: McGraw-Hill, 1987.

- [14] E. A. Vittoz, "MOS transistors operated in the lateral bipolar mode and their application in CMOS technology," *IEEE J. Solid-State Circuits*, vol. SSC-18, pp. 273–279, June 1983.

[15] T. W. Pan and A. Abidi, "A 50-db variable gain amplifier using parasitic bipolar transistors in CMOS," *IEEE J. Solid-State Circuits*, vol. 24, pp. 951–961, Aug. 1989.

Ming-Jer Chen (S'77-M'86) was born in Taiwan, R.O.C., on April 1, 1954. He received the B.S. degree with highest honors from the National Cheng-Kung University in 1977, and the M.S. and Ph.D. degrees from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1979 and 1985, respectively, all in electrical engineering. His doctoral work involved the modeling and prediction of CMOS latch-up.

From 1979 to 1980, he worked at Telecommunication Laboratories, establishing a multiprocessor

distributed system. From 1985 to 1986, he conducted post-doctoral research on CMOS latch-up at NCTU. From 1986 to 1992, he was an Associate Professor and in 1993 became a Professor in the Department of Electronics Engineering, NCTU. From 1987 to 1992, he set up a series of design rules for the Taiwan Semiconductor Manufacturing Company. His current research interests include deep submicron reliability, low-power integrated circuits, and subthreshold CMC and BiCMOS technologies for new applications. He holds three patents in the above fields.

Dr. Chen has served as a reviewer for international journals such as IEEE ELECTRON DEVICE LETTERS, IEEE TRANSACTIONS ON ELECTRON DEVICES, Solid-State Electronics, and the Journal of the Chinese Instituite of Engineers. He is a member of Phi Tau Phi.

Jih-Shin Ho was born in Taiwan, R.O.C., on July 13, 1966. He received the B.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1988. He is currently working toward the Ph.D. degree at the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan. His research interests include the CMOS device modeling and mismatch analysis in subthreshold region and their application to low-power circuit design.

Dang-Yang Chang was born in Taiwan, R.O.C., on September 21, 1969. He received the B.S. degree in electronics engineering from the Feng-Chia University and the M.S. degree in electronics engineering from the National Chiao-Tung University.

He now serves in the Chinese Army.