# Channel Backscattering Characteristics of Uniaxially Strained Nanoscale CMOSFETs

Hong-Nien Lin, Hung-Wei Chen, Chih-Hsin Ko, Chung-Hu Ge, Horng-Chih Lin, Senior Member, IEEE, Tiao-Yuan Huang, Fellow, IEEE, and Wen-Chin Lee, Member, IEEE

Abstract—Channel backscattering characteristics of uniaxially strained nanoscale CMOSFETs are reported for the first time. Channel backscattering ratio increases and decreases under uniaxial tensile and compressive strain, respectively. It is found that in sub-100-nm devices, strain-induced modulation of carrier mean-free path for backscattering and reduction in  $k_BT$  layer thickness are responsible for the different behaviors of backscattering ratio. Nevertheless, the source-side injection velocity improves irrespective of the strain polarities. The impact of channel backscattering ratio on drive current is also analyzed in terms of ballistic efficiency and injection velocity.

Index Terms—MOSFETs, scattering, uniaxial strain.

## I. INTRODUCTION

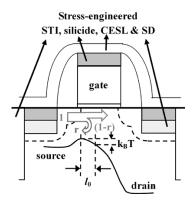

RECENTLY, various strain techniques are actively pursued to give the device performance a much-needed boost in 90-nm node and beyond [1]–[3]. Mobility enhancement induced by strain in the channel has been widely characterized, however, only half of the mobility enhancement is needed to account for the observed saturation drain current increase [4]. To reconcile with this discrepancy and to understand ballistic transport in a nanoscale transistor, carrier scattering theory has been proposed. As illustrated in the inset of Fig. 1, some of the injected carriers are backscattered near the source end of the channel region within a  $k_BT$  layer which has a potential drop of  $k_BT/q$ and a thickness of  $l_0$ . Since the transmitted carriers ultimately determine the drive current, carrier backscattering ratio r, and injection velocity  $v_{\rm inj}$  at the top of source-channel barrier are both critical in determining the drive current  $I_{\mathrm{dsat}}.$  For a higher  $I_{\rm dsat}$ , reducing r and increasing  $v_{\rm inj}$  are desirable [5]. It has been reported that biaxial tensile strain results in backscattering ratio reduction with Si<sub>0.7</sub>Ge<sub>0.3</sub> virtual substrate from simulation [6]. However, the influence of uniaxial strain on backscattering ratio has not been clarified yet. In this paper, we report the impact of uniaxial process-induced tensile and compressive strains on channel backscattering ratio for the first time. In addition, the

Manuscript received March 21, 2005; revised June 13, 2005. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC93-2215-E-009-078. The review of this letter was arranged by Editor E. Sangiorgi.

H.-N. Lin and T.-Y. Huang are with the Institute of Electronics, National Chiao-Tung University, Hsinchu 30050, Taiwan, R.O.C. (e-mail: hnlin.ee89g@nctu.edu.tw).

H.-W. Chen, C.-H. Ko, C.-H. Ge, and W.-C. Lee are with the Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu 30077, Taiwan, R.O.C.

H.-C. Lin is with the Institute of Electronics, National Chiao-Tung University, Hsinchu 30050, Taiwan, R.O.C. He is also with the National Nano Device Laboratories, Hsinchu 30050, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LED.2005.853640

Fig. 1. Schematic structure of PSS MOSFETs. Various stress -engineered processes are employed to achieve uniaxially tensile and compressive strains for nMOSFETs and pMOSFETs, respectively. The inset illustrates that carrier in  $k_BT$  layer region is with a backscattering ratio r where the thickness of  $k_BT$  layer is  $l_0$ .

impact of channel backscattering ratio on drive current is also analyzed in terms of mean-free path (MFP),  $k_BT$  layer thickness, ballistic efficiency, and injection velocity.

# II. EXPERIMENTAL

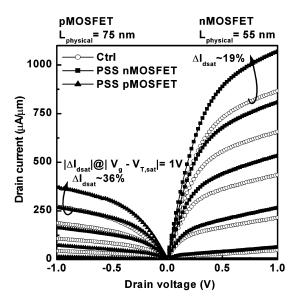

Process-strained Si (PSS) MOSFETs fabricated by state-of-the-art CMOS process are studied in this letter [2]. Schematic structure with uniaxial strain engineering is illustrated in Fig. 1, where uniaxial tensile strain for nMOSFETs and uniaxial compressive strain for pMOSFETs are achieved. To minimize barrier height modulation from drain-induced barrier lowering (DIBL), PSS, and control devices with nominally identical DIBL and subthreshold swing are characterized. Drain current improvement of both PSS devices relative to control devices is shown in Fig. 2, all devices with identical inversion C-V characteristics. From scattering theory in [7], drive current in saturation region ( $|V_d|=1$  V) can be expressed as

$$I_{\text{dsat}} = W v_{\text{inj}} \left[ \frac{1 - r_{\text{sat}}}{1 + r_{\text{sat}}} \right] C_{\text{eff}} \left( V_g - V_{T, \text{sat}} \right) \tag{1}$$

where  $v_{\rm inj}$ ,  $r_{\rm sat}$ , and  $V_{T,\rm sat}$  represent injection velocity, backscattering ratio, and threshold voltage, respectively. The ratio  $r_{\rm sat}$  is a function of carrier mean-free path for backscattering  $\lambda_0$  and  $k_BT$  layer thickness  $l_0$  ( $r_{\rm sat}=1/[1+\lambda_0/l_0]$ ) [5]. The  $V_{T,\rm sat}$  is determined by maximum transconductance ( $G_{\rm m,max}$ ) method with DIBL consideration ( $\Delta V_{\rm DIBL}=V_{T,\rm lin}@|V_d|=10~{\rm mV}-V_{T,\rm sat}@|V_d|=1~{\rm V}$ , where  $V_T$  is defined as the gate voltage when  $|I_d|=0.1~{\rm W/L}~\mu{\rm A}$ ), i.e.,  $V_{T,\rm sat}=V_{T,\rm lin}(G_{\rm m,max}@|V_d|=10~{\rm mV})-\Delta V_{\rm DIBL}$ .

Fig. 2.  $I_d$ – $V_d$  characteristics of control and PSS MOSFETs, where PSS nMOSFETs and pMOSFETs exhibit about 19% and 36% improvement of drive current at  $|V_g$ – $V_{T,\rm sat}| = |V_d| = 1$  V, respectively. The DIBLs of nMOSFETs are 161 mV/V (control) and 155 mV/V (PSS), and those of pMOSFETs are 114 mV/V (control) and 110 mV/V (PSS). The swings of nMOSFETs are 88 mV/dec (control) and 87 mV/dec (PSS), and those of pMOSFETs are 94 mV/dec (control) and 95 mV/dec (PSS).

Then, a temperature-dependent analytic model is employed to extract the  $\lambda_0/l_0$  ratio using the following analytic expression:

$$\frac{\partial I_{\text{dsat}}}{\partial T} = I_{\text{dsat}} \left[ \frac{1}{v_{\text{inj}}} \frac{\partial v_{\text{inj}}}{\partial T} + \frac{1 + r_{\text{sat}}}{1 - r_{\text{sat}}} \frac{\partial}{\partial T} \left( \frac{1 - r_{\text{sat}}}{1 + r_{\text{sat}}} \right) \right. \\

\left. + \frac{1}{V_g - V_{T,\text{sat}}} \frac{\partial (V_g - V_{T,\text{sat}})}{\partial T} \right] \\

= I_{\text{dsat}} \left[ \frac{1}{2T} - \left( \frac{1}{1 + r_{\text{sat}}} + \frac{1}{1 - r_{\text{sat}}} \right) \frac{\partial r_{\text{sat}}}{\partial T} \right. \\

\left. - \frac{\eta}{V_g - V_{T,\text{sat}}} \right] \\

= I_{\text{dsat}} \alpha \tag{2}$$

where  $\partial r_{\rm sat}/\partial T=[2r_{\rm sat}(1-r_{\rm sat})]/T$ . Then  $\alpha$  can be derived as follows:

$$\alpha = \frac{1}{T} \left[ \frac{1}{2} - \frac{4}{2 + \frac{\lambda_0}{l_0}} \right] - \frac{\eta}{V_g - V_{T,\text{sat}}}$$

(3)

where  $\alpha$  and  $\eta$  represent temperature sensitivity of  $I_{\rm dsat}$  and  $V_{T,{\rm sat}}$ , i.e.,  $\alpha=(I_{\rm dsat1}-I_{\rm dsat2})/[I_{\rm dsat2}(T_1-T_2)]$  and  $\eta=(V_{T,{\rm sat1}}-V_{T,{\rm sat2}})/(T_1-T_2)$  [8]. The measurement temperature is decreased from 298 K to 228 K at a step of 15 K.  $\alpha$  and  $\eta$  are extracted from the best-fitted slopes of  $\Delta I_{\rm dsat}$  and  $\Delta V_{T,{\rm sat}}$  at different temperatures. The  $\lambda_0/l_0$  ratio can then be calculated by (3). Lastly, backscattering ratio and ballistic efficiency  $B_{\rm sat}(=1-r_{\rm sat})/[1+r_{\rm sat}]$ ) can be deduced.

## III. RESULTS AND DISCUSSION

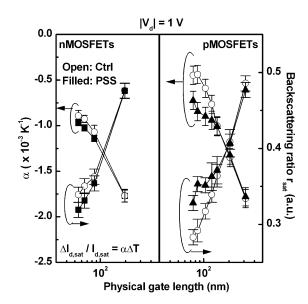

The gate length dependence of backscattering factors  $\alpha$  and  $r_{\rm sat}$  are shown in Fig. 3.  $\alpha$  is the dominant factor in determining  $\lambda_0/l_0$  of MOSFETs since the ratio  $|\eta/(V_g-V_{T,\rm sat})|$  ( $|\eta|=0.5$  to 0.9 mV/K) is smaller than  $|\alpha|$ . By deducing

Fig. 3. Effects of uniaxial strain on temperature sensitivity of drain current  $\alpha$ , and channel backscattering ratio  $r_{\rm sat}$  of control devices, PSS nMOSFETs, and pMOSFETs.

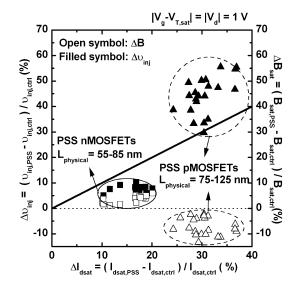

$\lambda_0/l_0$  from  $\alpha$ , PSS nMOSFETs demonstrate only a slight increase in  $\lambda_0/l_0$ , while PSS pMOSFETs show significant decrease. In the analytic model,  $\lambda_0/l_0$  can be obtained directly from experimental results, unlike the method in [9] in which  $v_{\rm inj}$  has to be calculated theoretically first before the deduction of  $\lambda_0/l_0$  from (1). In the nondegenerate case,  $\lambda_0$ can be written as  $\lambda_0 = (2k_BT/q) \mu_0/v_{\rm inj}$  [4] where  $\mu_0$  is extracted by the method in [10]. In addition,  $l_0$  is proportional to temperature. Thus, in the derivation of (2), the possible errors of  $r_{\rm sat}$  or  $B_{\rm sat}$  originate from the assumed temperature dependence of  $\mu_0$ . In this letter,  $\mu_0$  is assumed to be proportional to  $T^{-1.5}$  (i.e., theoretical value) [11]. Nonetheless, even by changing the power of temperature dependence to -1.75 (i.e., experimental value) [12], the resultant difference in  $\Delta B_{\rm sat} (= [B_{\rm sat,pss} - B_{\rm sat,ctrl}]/B_{\rm sat,pss})$  is negligible, confirming the insignificance in error caused by the assumed temperature dependence. As shown in Fig. 3, compared to  $r_{\rm sat}$ of control devices, the tensile-strained PSS nMOSFET has smaller  $r_{\rm sat}$  while compressive-strained PSS pMOSFET has larger  $r_{\rm sat}$ . This phenomenon indicates that injected electrons in tensile-strained nMOSFET exhibit less channel backscattering while injected holes in compressive-strained pMOSFET suffer more backscattering. The  $r_{\rm sat}$  difference between control and PSS devices becomes more dramatic as  $L_{\text{physical}}$  is shorter than  $0.1~\mu m$ . It implies that the ballistic efficiency of tensile-strained PSS nMOSFET is improved but that of compressive-strained PSS pMOSFET is degraded.  $Q_{\rm inv}$  for characterized devices is extracted from MOSFETs with an area of 100  $\mu$ m<sup>2</sup> under strong inversion, taking into account  $V_T$  roll-off and DIBL [13].  $v_{\rm inj}$  can then be calculated by  $I_{\rm dsat} = W v_{\rm inj} B_{\rm sat} Q_{\rm inv}$ . As shown in Fig. 4, the injection velocity is improved in both PSS devices, which is ascribed to process-strained induced reduction in carrier effective mass [1]. In addition,  $\Delta I_{\rm dsat}$  can be related to the sum of  $\Delta v_{\rm inj}$  and  $\Delta B_{\rm sat}$ . Slight underestimation of  $\Delta I_{\rm dsat}$  in nMOS is due to minor  $Q_{\rm inv}$  difference between PSS and control devices. To further investigate the

Fig. 4.  $\Delta v_{\rm inj}$  and  $\Delta B$  as a function of  $\Delta I_{\rm dsat}$  for PSS nMOSFETs (square symbol) and pMOSFETs (triangle symbol).  $\Delta B$  and  $\Delta v_{\rm inj}$  are represented by open and filled symbols, respectively. The solid line indicates that  $\Delta v_{\rm inj}$  (or  $\Delta B$ ) varies linearly with  $\Delta I_{\rm dsat}$ . For PSS nMOSFETs, both carrier injection velocity and ballistic efficiency are higher than control devices. While for PSS pMOSFETs, slightly lower B and much higher  $v_{\rm inj}$  are obtained.

mechanism of strain-induced backscattering modulation,  $l_0$  can be calculated from the ratio of  $\lambda_0/l_0$  when  $\lambda_0$  is derived. It is found that  $l_0$  of both PSS devices is reduced to about 90% of that of control devices, and the thinning of  $l_0$  may be due to the strain-induced bandgap shift causing sharper potential profile. In addition,  $\lambda_0$  is increased in PSS nMOSFETs, which is consistent with the simulation results of [14]. Contrary to nMOSFETs, PSS pMOSFETs exhibit smaller  $\lambda_0$  than that of control devices, which is probably due to the compressed lattice in the channel inducing much severe carrier scattering. Hence, it is essential to improve not only injection velocity but also ballistic efficiency in order to further enhance the performance of uniaxial-strained MOSFETs in nanoscale regime. Although  $I_{

m dsat}$  of PSS pMOSFETs is improved through the enhancement of injection velocity at the expense of ballistic efficiency loss, ultimate PSS performance boost should therefore be expected if one could conceive a clever method to enhance ballistic efficiency without sacrificing injection velocity.

## IV. CONCLUSION

In this letter, the influence of uniaxial strain on channel backscattering ratio in nanoscale MOSFETs is investigated. Channel backscattering ratio is reduced in tensile-strained nMOSFET but increased in compressive-strained pMOSFET, notwithstanding the increased carrier injection velocity in both cases. Drive current is determined not only by backscattering ratio but also injection velocity. Strain techniques or device structures with simultaneous enhancement of channel backscattering ratio and injection velocity are therefore favorable for ultimate performance boost in mesoscopic regime.

## REFERENCES

- [1] S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffmann, C.-H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, "A 90-nm logic technology featuring strained-silicon," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1790–1797, Nov. 2004.

- [2] C.-H. Ge, C.-C. Lin, C.-H. Ko, C.-C. Huang, Y.-C. Huang, B.-W. Chan, B.-C. Perng, C.-C. Sheu, P.-Y. Tasi, L.-G. Yao, C.-L. Wu, T.-L. Lee, C.-J. Chen, C.-T. Wang, S.-C. Lin, Y.-C. Yeo, and C. Hu, "Process-strained Si (PSS) CMOS technology featuring 3-D strain engineering," in *IEDM Tech. Dig.*, 2003, pp. 73–76.

- [3] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors," in *IEDM Tech. Dig.*, 2003, pp. 978–980.

- [4] M. Lundstrom, "On the mobility versus drain current relation for a nanoscale MOSFET," *IEEE Electron Device Lett.*, vol. 22, no. 6, pp. 293–295, Jun. 2001.

- [5] —, "Elementary scattering theory of the Si MOSFET," *IEEE Electron Device Lett.*, vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [6] T. Skotnicki, "Transistor scaling to the end of the roadmap," in Short Course of VLSI Tech., Honolulu, HI, Jun. 2004, p. 117.

- [7] A. Rahman and M. S. Lundstrom, "A compact scattering model for the nanoscale double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 481–489, Mar. 2002.

- [8] M.-J. Chen, H.-T. Huang, K.-C. Huang, P.-N. Chen, C.-S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, 2002, pp. 39–42.

- [9] F. Assad, Z. Ren, S. Datta, and M. Lundstrom, "Performance limits of silicon MOSFETs," in *IEDM Tech. Dig.*, 1999, pp. 547–550.

- [10] K. Rim, S. Narasimha, M. Longstreet, A. Mocuta, and J. Cai, "Low field mobility characteristics of sub-100 nm unstrained and strained Si MOS-FETs," in *IEDM Tech. Dig.*, 2002, pp. 43–46.

- [11] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley, 1981, pp. 28–28.

- [12] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFETs Part I-Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994.

- [13] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?," *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 95–97, Feb. 2001.

- [14] C. Jungemann and B. Meinerzhagen, "MC simulation of strained Si/SiGe devices," in *Proc. ESSDERC*, 2003, pp. 9–14.