# Formation of dual-phase Hf O 2 – Hf x Si 1 $\,$ x O 2 dielectric and its application in memory devices

Ying Qian Wang, Jing Hao Chen, Won Jong Yoo, Yee-Chia Yeo, Albert Chin, and An Yan Du

Citation: Journal of Applied Physics **98**, 013536 (2005); doi: 10.1063/1.1954870

View online: http://dx.doi.org/10.1063/1.1954870

View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/98/1?ver=pdfcov

Published by the AIP Publishing

#### Articles you may be interested in

Investigation of local charged defects within high-temperature annealed Hf Si O N Si O 2 gate stacks by scanning capacitance spectroscopy

J. Appl. Phys. **101**, 083704 (2007); 10.1063/1.2717600

Pd-nanocrystal-based nonvolatile memory structures with asymmetric Si O 2 Hf O 2 tunnel barrier Appl. Phys. Lett. **89**, 083109 (2006); 10.1063/1.2335677

Multibit memories using a structure of Si O 2 /partially oxidized amorphous Si Hf O 2 Appl. Phys. Lett. **89**, 033122 (2006); 10.1063/1.2219999

In situ low-angle x-ray scattering study of phase separation in initially mixed Hf O 2 – Si O 2 thin film interfaces Appl. Phys. Lett. **85**, 5884 (2004); 10.1063/1.1831554

Surface potential and morphology issues of annealed (HfO 2) x (SiO 2) 1x gate oxides J. Vac. Sci. Technol. B 22, 2113 (2004); 10.1116/1.1771673

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Formation of dual-phase $HfO_2-Hf_xSi_{1-x}O_2$ dielectric and its application in memory devices

Ying Qian Wang,<sup>a)</sup> Jing Hao Chen, Won Jong Yoo,<sup>b)</sup> and Yee-Chia Yeo Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, 4 Engineering Drive 3, Singapore 117576

#### Albert Chin

Nano Science Technology Center, Department of Electronics Engineering, National Chiao Tung University, University System of Taiwan, Hsinchu, Taiwan 300, Republic Of China

#### An Yan Du

Institute of Microelectronics, 11 Science Park Road, Singapore Science Park II, Singapore 117685

(Received 28 January 2005; accepted 20 May 2005; published online 13 July 2005)

In this paper, we studied the phase-separation phenomenon of  $Hf_{0.5}Si_{0.5}O_2$  film deposited on  $SiO_2$  or sandwiched by  $SiO_2$ , by x-ray photoelectron spectroscopy and transmission electron microscopy. The  $Hf_{0.5}Si_{0.5}O_2$  film underwent phase separation to form a doublet-phase  $HfO_2-Hf_xSi_{1-x}O_2$  (x < 0.5) film, and was used as a trapping layer in a metal-blocking oxide-silicon nitride-tunnel oxide-silicon-type memory structure, where the dual-phase  $HfO_2-Hf_xSi_{1-x}O_2$  (DPHSO) film replaces the conventional silicon nitride ( $Si_3N_4$ ) trapping layer. The charge storage properties of the DPHSO film were investigated and compared with  $HfO_2$  and  $Si_3N_4$ . It was found that for a given electric field applied to the tunnel oxide, the programming speed of memory devices using a DPHSO or  $HfO_2$  film as a trapping layer is faster than that using  $Si_3N_4$ . This indicates the higher electron-capture efficiency of the DPHSO and  $HfO_2$  films. In addition, the double-phase microstructure of the DPHSO film also provided better retention property than pure  $HfO_2$ . © 2005 American Institute of Physics. [DOI: 10.1063/1.1954870]

#### I. INTRODUCTION

The polycrystalline silicon- or metal-oxide-nitride-oxide-silicon (SONOS or MONOS, respectively) nonvolatile memory structure has received considerable attention for application in electrically erasable and programmable read only memory (EEPROM) devices. <sup>1–3</sup> The attractiveness of the MONOS flash memory, compared to the current commercial floating gate memory, lies in its low programming/erasing voltage, immunity to drain-induced turn on, <sup>4</sup> and improved retention and endurance properties because the local defect-related charge leakage can be significantly reduced. <sup>2,3</sup> Recently, materials such as high-permittivity (high *k*) dielectrics, e.g., Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>, have been explored to replace silicon nitride in the SONOS or MONOS structure to improve both the programming and retention properties. <sup>1–3</sup>

Hafnium silicate dielectric film is an attractive trapping material in MONOS memory application due to its process compatibility with the conventional complementary metaloxide semiconductor (CMOS) process. In addition, hafnium silicate is known to undergo phase separation<sup>5–8</sup> to form a crystalline hafnium oxide (HfO<sub>2</sub>) phase and an amorphous-silica-rich phase when annealed at temperatures above 900 °C, giving rise to a unique microstructure comprising HfO<sub>2</sub> nanocrystals that could be suitable for memory applications. Therefore, a memory device with a hafnium silicate trapping layer could combine the benefits of the MONOS

### **II. DEVICE FABRICATION**

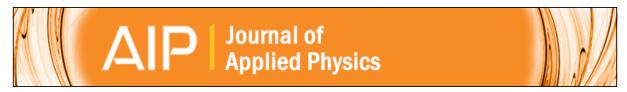

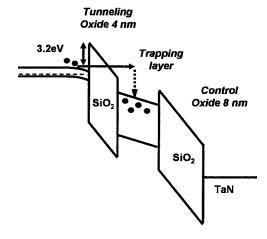

Memory devices with the  $TaN/SiO_2/X/SiO_2/Si$  structure were fabricated, where X represents the charge-trapping layer which can be DPHSO,  $HfO_2$ , or  $Si_3N_4$ . A schematic of the device structure is shown in Fig. 1. Tantalum nitride (TaN) is selected as the gate material, instead of  $n^+$  polysilicon, because the midgap work function of TaN has been reported to contribute to an enlarged memory window by reducing electron injection from the gate through the blocking oxide during erase operation. <sup>10</sup>

P-type Si (100) substrates were used as the starting materials. After a standard pre-gate clean, a 4-nm-thick SiO<sub>2</sub> tunnel oxide was grown by dry oxidation at a temperature of

structure and the nanocrystal memory. Recently, Lin *et al.*<sup>9</sup> demonstrated memory devices comprising HfO<sub>2</sub> dots formed by the phase separation of the hafnium silicate film. In this article, we focus on the materials analysis of the dielectric stack in the memory device structure (silicate film deposited on SiO<sub>2</sub> or sandwiched by SiO<sub>2</sub>) because the top and bottom SiO<sub>2</sub> may impact the thermal stability of the silicate film. We also provided experimental comparison of the trapping properties of the dual-phase HfO<sub>2</sub>-Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub> (DPHSO) film with those of the HfO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> films in MONOS-type memories, in order to better evaluate the advantage of each material in MONOS-type memory applications. The programming and retention properties are also compared. The relation between the device performance and material property is analyzed.

a)Electronic mail: g0203532@nus.edu.sg

b) Author to whom correspondence should be addressed; electronic mail: eleyoowj@nus.edu.sg

FIG. 1. Schematic diagram showing the cross section of the memory device. The inset shows the thicknesses of the trapping layer and the capacitance effective thickness ( $t_{\rm eff}$ ) of the entire dielectric stack which is calculated for the accumulation regime.

800 °C. On one wafer, a Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film was deposited on the SiO<sub>2</sub> tunnel oxide by the cosputtering of Hf and Si targets in an argon and oxygen  $(Ar+O_2)$  ambient at a pressure of 3 mTorr. On the first control wafer, the HfO<sub>2</sub> film was formed on the tunnel oxide by reactive sputtering of a Hf target in the Ar+O<sub>2</sub> ambient. On the second control wafer, a Si<sub>3</sub>N<sub>4</sub> film was formed on the tunnel oxide by sputtering Si in an ambient containing argon and nitrogen. The thicknesses of the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub>, HfO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub> films were controlled by adjusting the sputter-deposition rate. The physical thicknesses of the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub>, HfO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub> charge-trapping layers (Fig. 1) were measured by an ellipsometer and a profiler. The thicknesses were different as no process optimization to match the thicknesses was made. Next, all the chargetrapping layers were capped with an 8-nm-thick SiO<sub>2</sub> which was formed by low-pressure chemical vapor deposition (LPCVD) using a Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub> (TEOS) precursor at a deposition temperature of 700 °C. Subsequently, a 150-nm-thick TaN metal gate was formed by sputtering a Ta target in an Ar+N<sub>2</sub> ambient with a dc power of 450 W at a pressure of 3 mTorr, followed by gate patterning and etching. Finally, As<sup>+</sup> implantation and activation anneal at 1000 °C were performed to form the source/drain regions.

### III. MATERIALS CHARACTERIZATION

X-ray photoelectron spectroscopy (XPS) and transmission electron microscopy (TEM) were utilized to investigate the material properties of the  $Hf_{0.5}Si_{0.5}O_2$  film, paying particular attention to phase transformation and distribution.

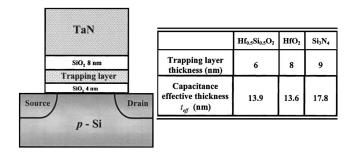

The  $Hf_{0.5}Si_{0.5}O_2$  film employed for XPS characterization was formed by the same process as that used for device fabrication. The  $Hf_{0.5}Si_{0.5}O_2$  film was then annealed at various temperatures in an inert ambient, and XPS was used to reveal the change of the chemical composition of the  $Hf_{0.5}Si_{0.5}O_2$  film as the anneal temperature increases. The ratio of Hf and Si in the film was found to be 1:1 from compositional XPS analysis. Figure 2 shows the spectra of the O 1s core level of the  $Hf_{0.5}Si_{0.5}O_2$  films as deposited and after annealing at 900 and 1000 °C. The O 1s binding energies of  $SiO_2$  and  $HfO_2$  are 533.4 and 530.6 eV, respectively, <sup>11</sup> as indicated in Fig. 2. The O 1s binding energy of an amorphous hafnium silicate with a composition of  $Hf_6Si_{29}O_{65}$  is about 532.4 eV, <sup>12</sup> and this is also indicated in Fig. 2. Considering the fact that Zr and Hf have similar elec-

FIG. 2. XPS spectra showing the O 1s core level of the as-deposited (As-Dep.)  $Hf_{0.5}Si_{0.5}O_2$  film after annealing at 900 and  $1000\,^{\circ}C$ . High-temperature anneal leads to the formation of two phases, including the  $HfO_2$  phase and the Hf-silicate phase.

tronic configurations, one may refer to Ref. 13 for an interpretation of the XPS spectra. Reference 13 gives a detailed analysis of the XPS spectra shape and peak positions of Zr silicate films. In our experiment, the difference between the XPS spectra of as-deposited samples and samples annealed at high temperatures confirms phase separation, showing two types of chemical composites in the annealed Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> films. By fitting the XPS spectra using two Gaussian profiles as shown in Fig. 2, it is determined that the two components in the annealed (900 or 1000 °C) samples are HfO<sub>2</sub> and hafnium silicate. The difference between the 900 and 1000 °C annealed samples is that the ratio of O atoms associated with HfO<sub>2</sub> is larger in the 1000 °C annealed sample, indicating further phase separation of Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film at 1000 °C. Hence, the XPS study reveals HfO<sub>2</sub> and silica-rich Hf silicate phases in the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film after hightemperature annealing.

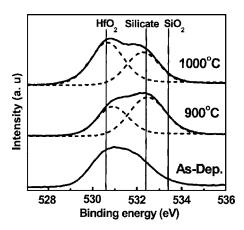

cross-sectional **TEM** picture SiO<sub>2</sub>/Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub>/SiO<sub>2</sub> sandwich structure annealed at 900 °C is shown in Fig. 3. Microstructures showing crystalline phases embedded in an amorphous matrix are clearly observed. The size of the crystals is in the range of 5-10 nm. Since the kinetic-energy barrier needed to form a crystalline hafnium silicate is large, the crystalline silicate phase can never be observed under normal annealing conditions,<sup>5–8</sup> thus we believe that the crystals in Fig. 3 should be HfO<sub>2</sub>. In addition, the lattice constant measured from TEM is about 0.31 nm, which is close to the (111) lattice constant of a monoclinic HfO<sub>2</sub> crystal. The amorphous phase in Fig. 3 is considered to be a hafnium silicate matrix with a significant brightness contrast from that of the underlying SiO<sub>2</sub>. For the sample which was annealed at 1000 °C, two phases were also observed in the trapping layer by TEM, but the size of the crystals is larger than that observed in the sample annealed at 900 °C, and the brightness constrast between the amorphous phase and the underlying SiO2 layer is also lower. This indicates that further phase separation had occurred with annealing at a higher temperature.

The XPS and TEM analyses consistently indicate that the following reaction occurred when the  $Hf_{0.5}Si_{0.5}O_2$  film was annealed at high temperatures:

FIG. 3. TEM image of a  $SiO_2/Hf_{0.5}Si_{0.5}O_2/SiO_2$  dielectric stack structure that was annealed at 900 °C, revealing the microstructure of crystals embedded in an amorphous matrix.

$$Hf_{0.5}Si_{0.5}O_2 \rightarrow \frac{0.5-x}{1-x}HfO_2 + \frac{0.5}{1-x}Hf_xSi_{1-x}O_2,$$

where 0 < x < 0.5. Lin *et al.* reported a phase separation of  $Hf_xSi_{1-x}O_2$  into crystalline  $HfO_2$  and amorphous  $SiO_2$ , which can be expressed by  $Hf_xSi_{1-x}O_2 \rightarrow xHfO_2 + (1-x)SiO_2$ , where the  $Hf_xSi_{1-x}O_2$  film was in contact with the Si substrate. Their different observations from the results of this work could be due to the different initial material compositions or the different layer structures employed in materials characterization.

# IV. MEMORY OPERATION AND RESULTS DISCUSSION

## A. Memory effect and programming characteristics

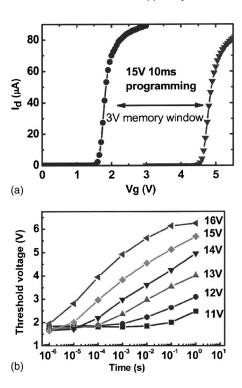

Figure 4(a) shows the memory effect of a MONOS-type device employing Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> as a trapping layer. Since the devices underwent a source-drain activation anneal at 1000 °C, the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film has a DPHSO structure. After applying a positive voltage pulse to the gate electrode while keeping the source, drain, and substrate terminals grounded, the threshold voltage  $(V_{th})$  shifts to a higher value since net negative charge is injected from the Si substrate. The threshold voltage was determined by the intercept of a tangent of the  $I_d$ - $V_g$  curve (measured at  $V_{ds}$ =0.2 V) at the point where the transconductance is the maximum. The threshold voltage as a function of stress time is shown in Fig. 4(b). According to the International Technology Roadmap for Semiconductors (ITRS) 2004, 14 the requirement of memory window for non-volatile flash memory is larger than 3 V. In our device, 3 V can be attained by stressing at 15 V for 10 ms.

FIG. 4. (a) Memory window and (b) threshold voltage change as a function of programming time and programming voltage of the memory device with the dual-phase  $HfO_2-Hf_xSi_{1-x}O_2$  (DPHSO) trapping layer.

The programming properties of the device with the DPHSO trapping layer were compared with devices employing  $HfO_2$  and  $Si_3N_4$  trapping layers. It was found that the devices with DPHSO and  $HfO_2$  trapping layers offer higher programming speeds with lower programming voltages than the device with  $Si_3N_4$  trapping layer.

Figure 1 lists the capacitance effective thickness  $(t_{\rm eff})$ , which was calculated using  $t_{\rm eff} = A\varepsilon_{\rm ox}/C_{\rm eff}$ , where  $C_{\rm eff}$  is the capacitance obtained from the capacitance-voltage (C-V) characteristics in the accumulation region,  $\varepsilon_{\rm ox}$  is the permittivity of SiO<sub>2</sub>, and A is the gate area. The  $t_{\rm eff}$  of the devices with HfO<sub>2</sub> and DPHSO trapping layers are about the same, but smaller than that of the device with a Si<sub>3</sub>N<sub>4</sub> trapping layer. This is partly due to the higher dielectric constants of HfO<sub>2</sub> and Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub>. The electric field in the tunneling oxide of the fresh device can be estimated by  $E_{\rm ox} = (V_g - V_{\rm fb} - \varphi_s)/t_{\rm eff}$ , where  $E_{\rm ox}$  is the electric field in the tunnel oxide and  $V_g$ ,  $V_{\rm fb}$ , and  $\varphi_s$  are the applied gate voltage, the flatband voltage, and the surface potential, respectively. Therefore, for a given electric field in the tunneling oxide, the applied gate voltage is smaller for the HfO<sub>2</sub> and DPHSO devices compared to the Si<sub>3</sub>N<sub>4</sub> device.

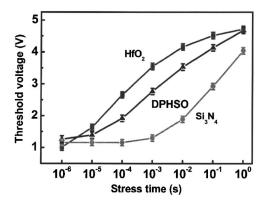

Figure 5 compares the programming properties of the three devices, with a  $V_g$  of 14 V applied to the devices with a HfO<sub>2</sub> or DPHSO trapping layer, and 18 V applied to the devices with a Si<sub>3</sub>N<sub>4</sub> trapping layer. At this bias condition, the value of  $E_{\rm ox}$  is about 10 MV/cm and electrons should be injected from the substrate to the trap layer via Fowler-Nordheim (FN) tunneling, as illustrated in Fig. 6. The FN tunneling current density is given by  $J_{\rm FN} = AE_{\rm ox}^2 \exp((-B/E_{\rm ox}))$ , where  $E_{\rm ox}$  is the electric field through the tunneling oxide, and A and B are constants as given by

FIG. 5. Comparison among memory devices with dual-phase DPHSO,  $HfO_2$ , and  $Si_3N_4$  as trapping layers. An electric field  $E_{ox}$  of 10 MV/cm was applied across the tunneling oxide in all three devices. Each data point was obtained by measuring five devices and the error is within 0.1 V across the chip.

$A=q^3(m/m_{\rm ox})/8\pi h\Phi_B$  and  $B=8\pi\sqrt{2m_{\rm ox}\Phi_B^3}/3qh$ . Hence the tunneling current is only determined by the electric field, and the injection current from substrate to trapping layer should be the same for all the three devices.

The programming speed was determined by  $d\Delta V_{th}/dt$  $= \eta J_{\rm inj} / C_g^{1,17}$  where  $\eta$  is the capture efficiency,  $J_{\rm inj}$  is the injection current,  $C_g$  is the capacitance between a centroid of a trapped charge and the gate, and  $C_g = \varepsilon_{ox}/d$ , where d is the equivalent oxide thickness (EOT) between the trapped charge and the gate electrode. If the centriod of the trapped charge is in the middle of the trapping layer, the values of d for the devices with DPHSO, HfO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub> trapping layers would be 9.0, 8.8, and 10.9 nm, respectively; thus  $C_{\varrho}(HfO_2) > C_{\varrho}(DPHSO) > C_{\varrho}(Si_3N_4)$ . As stated before, the injection currents of the three devices are nearly the same in Fig. 5. Therefore, the faster threshold voltage shift  $(d\Delta V_{th}/dt)$  of the devices with a HfO<sub>2</sub> or DPHSO trapping layer compared with the device with a Si<sub>3</sub>N<sub>4</sub> trapping layer at the early stage of the programming indicates that the HfO<sub>2</sub> and DPHSO films have a higher capture efficiency  $(\eta)$  than  $Si_3N_4$ .

### B. Retention properties

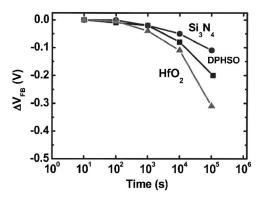

It is reported that although employing HfO<sub>2</sub> as a trapping layer can lower the programming voltage in comparison

FIG. 6. Energy-band diagram of the MONOS-type device during programming.

FIG. 7. Retention characteristics of memory devices with  $\mathrm{Si}_3\mathrm{N}_4$ , dual-phase DPHSO, and  $\mathrm{HfO}_2$  trapping layers.

with  $\mathrm{Si_3N_4}$ , the retention property of  $\mathrm{HfO_2}$  is poor.<sup>3</sup> The lateral migration of electrons in  $\mathrm{HfO_2}$  degrades the retention property, because the grain boundaries can act as lateral conduction paths.<sup>3</sup> In our experiment, we compared the retention properties of the  $\mathrm{Si_3N_4}$ ,  $\mathrm{HfO_2}$ , and DPHSO films by tracing the flatband voltage ( $V_{\mathrm{fb}}$ ) shift of the programmed device as a function of time. Figure 7 shows the gradual shift of the flatband voltage of the three devices with time.  $\mathrm{Si_3N_4}$  shows the best retention. DPHSO retains the charge slightly better than  $\mathrm{HfO_2}$ , showing a 0.1-V-smaller decay in  $V_{\mathrm{fb}}$  after  $10^5$  s. The improvement of DPHSO over  $\mathrm{HfO_2}$  is attributed to the presence of the amorphous phase in the film. The amorphous structure does not contain any grain boundaries and could effectively suppress lateral migration of trapped charges.

#### V. CONCLUSION

The phase separation of the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film in the SiO<sub>2</sub>/Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub>/SiO<sub>2</sub> sandwich dielectric structure was demonstrated. A dual-phase structure comprising crystalline HfO<sub>2</sub> and amorphous Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub> was observed after the Hf<sub>0.5</sub>Si<sub>0.5</sub>O<sub>2</sub> film was annealed at 900 and 1000 °C. The HfO<sub>2</sub>-Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub> trapping layer was found to provide a faster programming speed at a lower programming voltage than Si<sub>3</sub>N<sub>4</sub> because of its higher dielectric constant and higher trap efficiency. Meanwhile, the HfO<sub>2</sub>-Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub> also provided better retention property than HfO<sub>2</sub> because the presence of the amorphous phase suppressed the formation of grain boundary effectively, thereby reducing lateral migration. This dual-phase HfO<sub>2</sub>-Hf<sub>x</sub>Si<sub>1-x</sub>O<sub>2</sub> film with good trapping properties is a promising trapping material for the MONOS-type flash memory application.

#### **ACKNOWLEDGMENTS**

This work was supported by the Grant No. R-263-000-266-305 from the Agency for Science, Technology, and Research, Singapore.

<sup>&</sup>lt;sup>1</sup>X. Wang, J. Liu, W. Bai, and D. L. Kwong, IEEE Trans. Electron Devices **51**, 597 (2004).

<sup>&</sup>lt;sup>2</sup>T. Sugizaki *et al.*, 2003 Symposis on VLSI Technology and Circuits, Kyoto, Japan, 12–14 June 2003 (unpublished), p. 27.

<sup>&</sup>lt;sup>3</sup>Y. N. Tan, W. K. Chim, B. J. Cho, and W. K. Choi, IEEE Trans. Electron Devices **51**, 1143 (2004).

<sup>&</sup>lt;sup>4</sup>M. K. Cho and D. Kim, IEEE Electron Device Lett. **21**, 399 (2000).

- <sup>5</sup>D. A. Neumayer and E. Cartier, J. Appl. Phys. **90**, 1801 (2001).

- <sup>6</sup>S. Stemmer, Y. Li, B. Foran, P. S. Lysaght, S. K. Streiffer, P. Fuoss, and S. Seifert, Appl. Phys. Lett. 83, 3141 (2003).

- <sup>7</sup>S. Stemmer, Z. Chen, C. Levi, P. Lysaght, B. Foran, J. Gisby, and J. Taylor, Jpn. J. Appl. Phys., Part 1 42, 3593 (2003).

- <sup>8</sup>S. Ramanathan, P. C. Mcintyre, J. Luning, P. S. Lysaght, Y. Yang, Z. Chen, and S. Stemmer, J. Electrochem. Soc. 150, F173 (2003).

- <sup>9</sup>Y. H. Lin, C. H. Chien, C. T. Lin, C. W. Chen, C. Y. Chang, and T. F. Lei, 2004 IEEE International Devices Meeting, San Francisco, Califonia, 13-15 December 2004 (unpublished), p. 1080.

- 10C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, 2003 IEEE International Devices Meeting, Washington, D.C., 7-10 December 2003 (unpublished), p. 26.5.1.

- <sup>11</sup>S. J. Wang et al., Appl. Phys. Lett. **82**, 2047 (2003).

- <sup>12</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **87**, 484

- <sup>13</sup>G. B. Rayner, Jr., D. Kang, Y. Zhang, and G. Lucovsky, J. Vac. Sci. Technol. B 20, 1748 (2002).

- <sup>14</sup>International Technology Roadmap for Semiconductors. [On-line] http://

- public.itrs.net/

S. S. Chung, P. Y. Chiang, G. Chou, C. T. Huang, P. Chen, C. H. Chu, and C. C. H. Hsu, 2003 IEEE International Devices Meeting, Washington, D.C., 7-10 December 2003 (unpublished), p. 26.6.1.

- <sup>16</sup>D. K. Schroder, Semiconductor Material and Device Characterization (Wiley, New York, 1998).

- <sup>17</sup>K. Nomoto, I. Fujiwara, H. Aozasa, T. Terano, and T. Kobayashi, 2001 IEEE International Devices Meeting, Washington, D.C., 3-5 December 2001 (unpublished), p. 301.